Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                             |

| Number of I/O              | 67                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87j90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

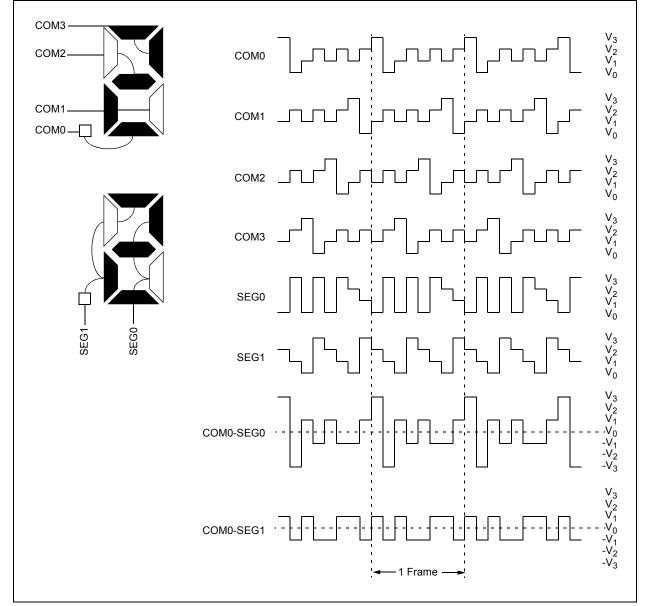

# 1.2 LCD Driver

The on-chip LCD driver includes many features that make the integration of displays in low-power applications easier. These include an integrated voltage regulator with charge pump that allows contrast control in software and display operation above device VDD.

# 1.3 Other Special Features

- Communications: The PIC18F87J90 family incorporates a range of serial communication peripherals, including an Addressable USART, a separate Enhanced USART that supports LIN/J2602 specification 1.2, and one Master SSP module capable of both SPI and I<sup>2</sup>C<sup>™</sup> (Master and Slave) modes of operation.

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules. Up to four different time bases may be used to perform several different operations at once.

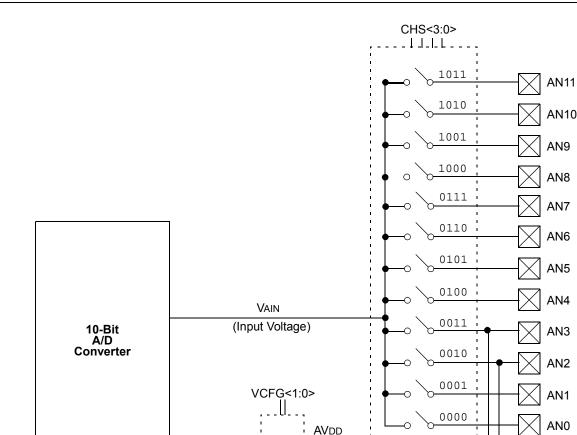

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Charge Time Measurement Unit (CTMU): The CTMU is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation.

Together with other on-chip analog modules, the CTMU can precisely measure time, measure capacitance or relative changes in capacitance, or generate output pulses that are independent of the system clock.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 28.0 "Electrical Characteristics" for time-out periods.

- Real-Time Clock and Calendar Module (RTCC): The RTCC module is intended for applications requiring that accurate time be maintained for extended periods of time with minimum to no intervention from the CPU.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

## 1.4 Details on Individual Family Members

Devices in the PIC18F87J90 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in four ways:

- Flash program memory (two sizes, 64 Kbytes for PIC18FX6J90 devices and 128 Kbytes for PIC18FX7J90 devices).

- 2. Data RAM (3,923 bytes RAM for both PIC18FX6J90 and PIC18FX7J90 devices).

- I/O ports (7 bidirectional ports on PIC18F6XJ90 devices, 9 bidirectional ports on PIC18F8XJ90 devices).

- LCD Pixels: 132 pixels (33 SEGs x 4 COMs) can be driven by 64-pin devices; 192 pixels (48 SEGs x 4 COMs) can be driven by 80-pin devices.

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

# 3.3.1 CLOCK SOURCE SELECTION

The System Clock Select bits, SCS<1:0> (OSCCON<1:0>), select the clock source. The available clock sources are the primary clock defined by the FOSC<2:0> Configuration bits, the secondary clock (Timer1 oscillator) and the internal oscillator. The clock source changes after one or more of the bits is written to, following a brief clock transition interval.

The OSTS (OSCCON<3>) and T1RUN (T1CON<6>) bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in Primary Clock modes. The T1RUN bit indicates when the Timer1 oscillator is providing the device clock in Secondary Clock modes. In power-managed modes, only one of these bits will be set at any time. If neither of these bits is set, the INTRC is providing the clock, or the internal oscillator has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the  ${\tt SLEEP}$  instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

# 3.3.1.1 System Clock Selection and Device Resets

Since the SCS bits are cleared on all forms of Reset, this means the primary oscillator defined by the FOSC<2:0> Configuration bits is used as the primary clock source on device Resets. This could either be the internal oscillator block by itself or one of the other primary clock source (HS, EC, HSPLL, ECPLL1/2 or INTPLL1/2).

In those cases when the internal oscillator block, without PLL, is the default clock on Reset, the Fast RC oscillator (INTOSC) will be used as the device clock source. It will initially start at 1 MHz; the postscaler selection that corresponds to the Reset value of the IRCF<2:0> bits ('100').

Regardless of which primary oscillator is selected, INTRC will always be enabled on device power-up. It serves as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSC Configuration bits are read and the oscillator selection of the operational mode is made.

Note that either the primary clock source, or the internal oscillator, will have two bit setting options for the possible values of the SCS<1:0> bits at any given time.

## 3.3.2 OSCILLATOR TRANSITIONS

PIC18F87J90 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

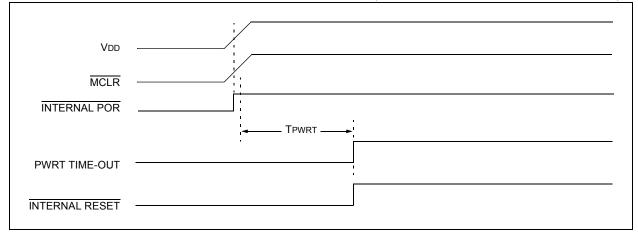

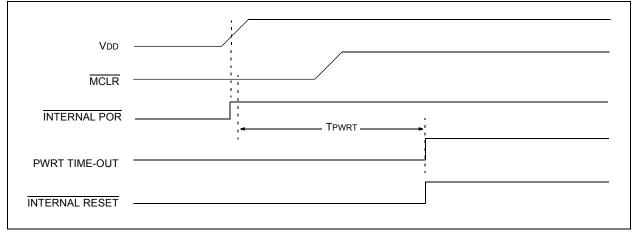

# 5.6 Power-up Timer (PWRT)

PIC18F87J90 family devices incorporate an on-chip Power-up Timer (PWRT) to help regulate the Power-on Reset process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F87J90 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

#### 5.6.1 TIME-OUT SEQUENCE

If enabled, the PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5 and Figure 5-6 all depict time-out sequences on power-up with the Power-up Timer enabled.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the PWRT will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

## FIGURE 5-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

# FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

| TABLE 6-3: | PIC18F87J90 FAMILY REGISTER FILE SUMMARY |

|------------|------------------------------------------|

|            |                                          |

| File Name | Bit 7                        | Bit 6          | Bit 5                 | Bit 4         | Bit 3          | Bit 2          | Bit 1           | Bit 0          | Value on<br>POR, BOR | Details on page |

|-----------|------------------------------|----------------|-----------------------|---------------|----------------|----------------|-----------------|----------------|----------------------|-----------------|

| TOSU      | _                            | _              | _                     | Top-of-Stack  | Upper Byte (T  | OS<20:16>)     |                 |                | 0 0000               | 59, 67          |

| TOSH      | Top-of-Stack                 | High Byte (TO  | S<15:8>)              |               |                |                |                 |                | 0000 0000            | 59, 67          |

| TOSL      | Top-of-Stack                 | Low Byte (TO   | S<7:0>)               |               |                |                |                 |                | 0000 0000            | 59, 67          |

| STKPTR    | STKFUL                       | STKUNF         | _                     | Return Stack  | Pointer        |                |                 |                | uu-0 0000            | 59, 68          |

| PCLATU    | _                            | _              | bit 21 <sup>(1)</sup> | Holding Regi  | ster for PC<20 | ):16>          |                 |                | 0 0000               | 59, 67          |

| PCLATH    | Holding Regis                | ster for PC<15 | 5:8>                  |               |                |                |                 |                | 0000 0000            | 59, 67          |

| PCL       | PC Low Byte                  | (PC<7:0>)      |                       |               |                |                |                 |                | 0000 0000            | 59, 67          |

| TBLPTRU   | _                            | —              | bit 21                | Program Mer   | nory Table Poi | nter Upper By  | te (TBLPTR<     | 20:16>)        | 00 0000              | 59, 92          |

| TBLPTRH   | Program Mer                  | nory Table Poi | inter High Byt        | e (TBLPTR<1   | 5:8>)          |                |                 |                | 0000 0000            | 59, 92          |

| TBLPTRL   | Program Mer                  | nory Table Poi | inter Low Byte        | e (TBLPTR<7:  | 0>)            |                |                 |                | 0000 0000            | 59, 92          |

| TABLAT    | Program Mer                  | nory Table Lat | ch                    |               |                |                |                 |                | 0000 0000            | 59, 92          |

| PRODH     | Product Regi                 | ster High Byte |                       |               |                |                |                 |                | XXXX XXXX            | 59, 99          |

| PRODL     | Product Regi                 | ster Low Byte  |                       |               |                |                |                 |                | XXXX XXXX            | 59, 99          |

| INTCON    | GIE/GIEH                     | PEIE/GIEL      | TMR0IE                | <b>INTOIE</b> | RBIE           | TMR0IF         | INT0IF          | RBIF           | 0000 000x            | 59, 103         |

| INTCON2   | RBPU                         | INTEDG0        | INTEDG1               | INTEDG2       | INTEDG3        | TMR0IP         | INT3IP          | RBIP           | 1111 1111            | 59, 104         |

| INTCON3   | INT2IP                       | INT1IP         | INT3IE                | INT2IE        | INT1IE         | INT3IF         | INT2IF          | INT1IF         | 1100 0000            | 59, 105         |

| INDF0     | Uses content                 | s of FSR0 to a | address data r        | nemory – valu | e of FSR0 not  | changed (not   | a physical re   | gister)        | N/A                  | 59, 83          |

| POSTINC0  | Uses content                 | s of FSR0 to a | address data r        | nemory – valu | e of FSR0 pos  | st-incremented | d (not a physic | al register)   | N/A                  | 59, 84          |

| POSTDEC0  | Uses content                 | s of FSR0 to a | ddress data r         | nemory – valu | e of FSR0 pos  | st-decremente  | d (not a physi  | cal register)  | N/A                  | 59, 84          |

| PREINC0   | Uses content                 | s of FSR0 to a | address data r        | memory – valu | e of FSR0 pre  | -incremented   | (not a physica  | al register)   | N/A                  | 59, 84          |

| PLUSW0    | Uses content<br>value of FSR |                | address data r        | memory – valu | e of FSR0 pre  | -incremented   | (not a physica  | al register) – | N/A                  | 59, 84          |

| FSR0H     | —                            | _              | _                     | _             | Indirect Data  | Memory Addr    | ess Pointer 0   | High Byte      | xxxx                 | 59, 83          |

| FSR0L     | Indirect Data                | Memory Addr    | ess Pointer 0         | Low Byte      |                |                |                 |                | xxxx xxxx            | 59, 83          |

| WREG      | Working Regi                 | ister          |                       |               |                |                |                 |                | xxxx xxxx            | 59              |

| INDF1     | Uses content                 | s of FSR1 to a | address data r        | memory – valu | e of FSR1 not  | changed (not   | a physical re   | gister)        | N/A                  | 59, 83          |

| POSTINC1  | Uses content                 | s of FSR1 to a | address data r        | memory – valu | e of FSR1 pos  | st-incremented | d (not a physic | cal register)  | N/A                  | 59, 84          |

| POSTDEC1  | Uses content                 | s of FSR1 to a | address data r        | memory – valu | e of FSR1 pos  | st-decremente  | d (not a physi  | cal register)  | N/A                  | 59, 84          |

| PREINC1   | Uses content                 | s of FSR1 to a | address data r        | memory – valu | e of FSR1 pre  | -incremented   | (not a physica  | al register)   | N/A                  | 59, 84          |

| PLUSW1    | Uses content<br>value of FSR |                | address data r        | memory – valu | e of FSR1 pre  | -incremented   | (not a physica  | al register) – | N/A                  | 59, 84          |

| FSR1H     | —                            | —              | —                     | —             | Indirect Data  | Memory Addr    | ess Pointer 1   | High Byte      | xxxx                 | 60, 83          |

| FSR1L     | Indirect Data                | Memory Addr    | ess Pointer 1         | Low Byte      |                |                |                 |                | XXXX XXXX            | 60, 83          |

| BSR       | —                            | —              | —                     | —             | Bank Select F  | Register       |                 |                | 0000                 | 60, 72          |

| INDF2     | Uses content                 | s of FSR2 to a | address data r        | memory – valu | e of FSR2 not  | changed (not   | a physical re   | gister)        | N/A                  | 60, 83          |

| POSTINC2  | Uses content                 | s of FSR2 to a | address data r        | memory – valu | e of FSR2 pos  | st-incremented | d (not a physic | cal register)  | N/A                  | 60, 84          |

| POSTDEC2  | Uses content                 | s of FSR2 to a | address data r        | memory – valu | e of FSR2 pos  | st-decremente  | d (not a physi  | cal register)  | N/A                  | 60, 84          |

| PREINC2   | Uses content                 | s of FSR2 to a | address data r        | memory – valu | e of FSR2 pre  | -incremented   | (not a physica  | al register)   | N/A                  | 60, 84          |

| PLUSW2    | Uses content<br>value of FSR |                | address data r        | memory – valu | e of FSR2 pre  | -incremented   | (not a physica  | al register) – | N/A                  | 60, 84          |

| FSR2H     |                              | _              | _                     | —             | Indirect Data  | Memory Addr    | ess Pointer 2   | High Byte      | xxxx                 | 60, 83          |

| FSR2L     | Indirect Data                | Memory Addr    | ess Pointer 2         | Low Byte      |                |                |                 |                | xxxx xxxx            | 60, 83          |

| STATUS    | _                            | _              | _                     | N             | OV             | Z              | DC              | С              | x xxxx               | 60, 81          |

$\label{eq:Legend: Legend: Legend: u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modify a set of the transformation of transformation of the transformation of t$

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: These registers and/or bits are available only on 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset states shown are for 80-pin devices.

3: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C<sup>™</sup> Slave mode. See Section 18.4.3.2 "Address Masking" for details.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.4.3 "PLL Frequency Multiplier" for details.

5: RA<7:6> and their associated latch and direction bits are configured as port pins only when the internal oscillator is selected as the default clock source (FOSC2 Configuration bit = 0); otherwise, they are disabled and these bits read as '0'.

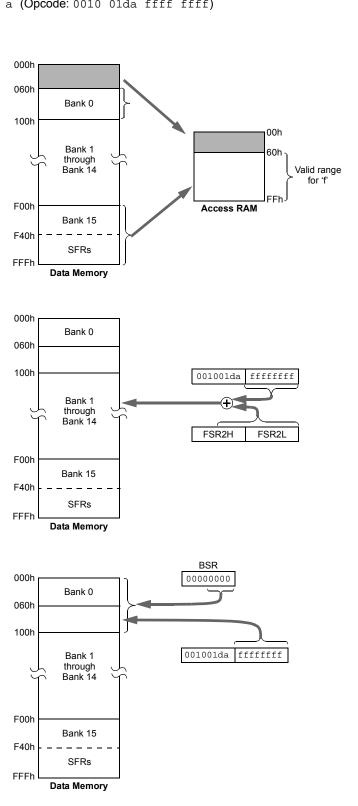

#### FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

#### **EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When a = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and FFFh. This is the same as locations, F60h to FFFh (Bank 15), of data memory.

Locations below 060h are not available in this addressing mode.

#### When a = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When a = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

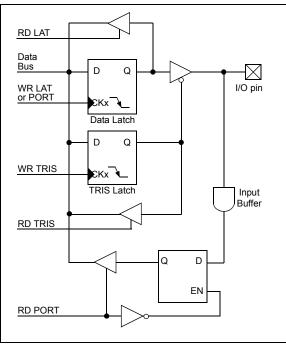

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to nine ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three memory mapped registers for its operation:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

Reading the PORT register reads the current status of the pins, whereas writing to the PORT register writes to the Output Latch (LAT) register.

Setting a TRIS bit (= 1) makes the corresponding port pin an input (i.e., puts the corresponding output driver in a high-impedance mode). Clearing a TRIS bit (= 0) makes the corresponding port pin an output (i.e., puts the contents of the corresponding LAT bit on the selected pin).

The Output Latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving. Read-modify-write operations on the LAT register read and write the latched output value for the PORT register.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

FIGURE 10-1: GENERIC I/O PORT OPERATION

# 10.1 I/O Port Pin Capabilities

When developing an application, the capabilities of the port pins must be considered. Outputs on some pins have higher output drive strength than others. Similarly, some pins can tolerate higher than VDD input levels.

# 10.1.1 INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages up to 5.5V, a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should be avoided.

Table 10-1 summarizes the input voltage capabilities. Refer to **Section 28.0 "Electrical Characteristics"** for more details.

#### TABLE 10-1: INPUT VOLTAGE TOLERANCE

| PORT or Pin               | Tolerated<br>Input | Description                        |

|---------------------------|--------------------|------------------------------------|

| PORTA<7:0>                |                    | Only VDD input levels              |

| PORTC<1:0>                | Voo                | tolerated.                         |

| PORTF<7:1>                | VUU                |                                    |

| PORTG<3:2>                |                    |                                    |

| PORTB<7:0>                |                    | Tolerates input                    |

| PORTC<7:2>                |                    | levels above VDD,                  |

| PORTD<7:0>                |                    | useful for most<br>standard logic. |

| PORTE<7:3>                | 5.5V               | otariaara logio.                   |

| PORTG<4,1>                |                    |                                    |

| PORTH<7:0> <sup>(1)</sup> |                    |                                    |

| PORTJ<7:0> <sup>(1)</sup> |                    |                                    |

Note 1: Not available on PIC18F6XJ90 devices.

# 10.1.2 PIN OUTPUT DRIVE

When used as digital I/O, the output pin drive strengths vary for groups of pins intended to meet the needs for a variety of applications. In general, there are three classes of output pins in terms of drive capability.

PORTB and PORTC, as well as PORTA<7:6>, are designed to drive higher current loads, such as LEDs. PORTD, PORTE and PORTJ can also drive LEDs but only those with smaller current requirements. PORTF, PORTG and PORTH, along with PORTA<5:0>, have the lowest drive level but are capable of driving normal digital circuit loads with a high input impedance. Regardless of which port it is located on, all output pins in LCD Segment or Common mode have sufficient output to directly drive a display.

Table 10-2 summarizes the output capabilities of the ports. Refer to the "Absolute Maximum Ratings" in Section 28.0 "Electrical Characteristics" for more details.

# 10.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISB and LATB. All pins on PORTB are digital only and tolerate voltages up to 5.5V.

#### EXAMPLE 10-2: INITIALIZING PORTB

| CLRF      | PORTB | ; Initialize PORTB by<br>; clearing output |

|-----------|-------|--------------------------------------------|

| 67. D. D. |       | ; data latches                             |

| CLRF      | LATB  | ; Alternate method<br>; to clear output    |

|           |       | ; data latches                             |

| MOVLW     | OCFh  | ; Value used to                            |

|           |       | ; initialize data                          |

|           |       | ; direction                                |

| MOVWF     | TRISB | ; Set RB<3:0> as inputs                    |

|           |       | ; RB<5:4> as outputs                       |

|           |       | ; RB<7:6> as inputs                        |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Wait one instruction cycle (such as executing a NOP instruction).

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared after one TCY delay.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB<3:2> are multiplexed as CTMU edge inputs.

RB<5:0> are also multiplexed with LCD segment drives, controlled by bits in the LCDSE1 and LCDSE3 registers. I/O port functionality is only available when the LCD segments are disabled.

## 11.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-2 increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 11.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 11.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before re-enabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values |

|--------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|-----------------|

| TMR0L  | Timer0 Reg            | ister Low By          | te     |        |        |        |        |        | on page<br>60   |

| TMR0H  | Timer0 Reg            | ister High By         | /te    |        |        |        |        |        | 60              |

| INTCON | GIE/GIEH              | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 59              |

| T0CON  | TMR0ON                | T08BIT                | TOCS   | T0SE   | PSA    | T0PS2  | T0PS1  | T0PS0  | 60              |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 62              |

TABLE 11-1:

REGISTERS ASSOCIATED WITH TIMER0

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA<7:6> and their associated latch and direction bits are configured as port pins only when the internal oscillator is selected as the default clock source (FOSC2 Configuration bit = 0); otherwise, they are disabled and these bits read as '0'.

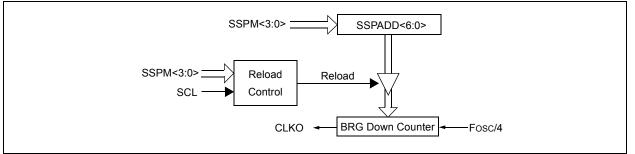

#### 18.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPADD register (Figure 18-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 18-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

# 18.4.7.1 Baud Rate Generation in Power-Managed Modes

When the device is operating in one of the power-managed modes, the clock source to the BRG may change frequency, or even stop, depending on the mode and clock source selected. Switching to a Run or Idle mode from either the secondary clock or internal oscillator is likely to change the clock rate to the BRG. In Sleep mode, the BRG will not be clocked at all.

## FIGURE 18-19: BAUD RATE GENERATOR BLOCK DIAGRAM

#### TABLE 18-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|---------|-----------|------------------------------|

| 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 1 MHz  | 2 MHz   | 00h       | 1 MHz                        |

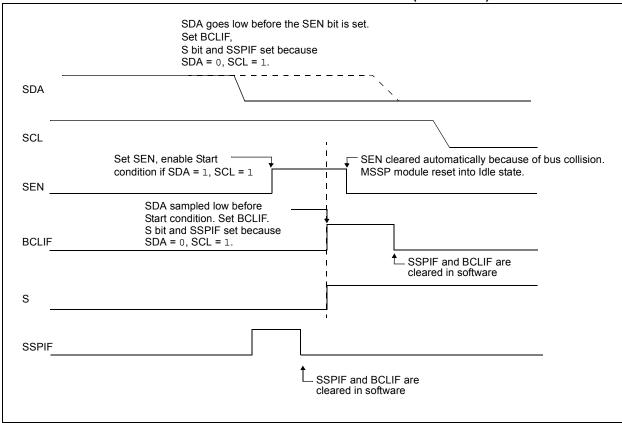

#### 18.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 18-28).

- b) SCL is sampled low before SDA is asserted low (Figure 18-29).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted;

- the BCLIF flag is set; and

- the MSSP module is reset to its Idle state (Figure 18-28).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 18-30). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0. If the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 18-28: BUS COLLISION DURING START CONDITION (SDA ONLY)

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (AVDD and AVSS), or the voltage level on the RA3/AN3/VREF+ and RA2/AN2/VREF- pins.

The A/D Converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's Internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

Each port pin associated with the A/D Converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of

#### FIGURE 21-1: A/D BLOCK DIAGRAM<sup>(1,2)</sup>

the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0<1>) is cleared and the A/D Interrupt Flag bit, ADIF, is set.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted. The value in the ADRESH:ADRESL register pair is not modified for a Power-on Reset. These registers will contain unknown data after a Power-on Reset.

The block diagram of the A/D module is shown in Figure 21-1.

Note 1: Channels, AN15 through AN12, are not available on PIC18F6XJ90 devices.2: I/O pins have diode protection to VDD and Vss.

O

$\cap$

0

AVss

VREF+

VREF-

Reference

Voltage

L

| R/W-0         | R/W-0        | R/W-0                              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

|---------------|--------------|------------------------------------|-----------------|-------------------|------------------|-----------------|----------|

| EDG2POL       | EDG2SEL1     | EDG2SEL0                           | EDG1POL         | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| DG2POL        | EDG25ELT     | EDG25ELU                           | EDGIPOL         | EDGISELI          | EDGISELU         | EDG25TAT        |          |

|               |              |                                    |                 |                   |                  |                 | bit 0    |

| Legend:       |              |                                    |                 |                   |                  |                 |          |

| R = Readable  | bit          | W = Writable                       | hit             | II = I Inimplem   | nented bit, read | l as 'O'        |          |

| -n = Value at |              | '1' = Bit is set                   |                 | '0' = Bit is clea |                  | x = Bit is unkr |          |

|               |              |                                    |                 |                   | area             |                 | 10111    |

| bit 7         | EDG2POI : F  | dge 2 Polarity                     | Select bit      |                   |                  |                 |          |

|               |              | rogrammed for                      |                 | le response       |                  |                 |          |

|               |              | rogrammed for                      |                 |                   |                  |                 |          |

| bit 6-5       | EDG2SEL<1:   | : <b>0&gt;:</b> Edge 2 So          | urce Select bit | s                 |                  |                 |          |

|               | 11 = CTEDG   | 1 pin                              |                 |                   |                  |                 |          |

|               | 10 = CTEDG   |                                    |                 |                   |                  |                 |          |

|               |              | pecial Event Tr<br>pecial Event Tr |                 |                   |                  |                 |          |

| bit 4         |              | dge 1 Polarity                     |                 |                   |                  |                 |          |

| bit 4         |              | rogrammed for                      |                 | le response       |                  |                 |          |

|               | • .          | rogrammed for                      |                 |                   |                  |                 |          |

| bit 3-2       | EDG1SEL<1:   | :0>: Edge 1 So                     | urce Select bit | S                 |                  |                 |          |

|               | 11 = CTEDG   | 1 pin                              |                 |                   |                  |                 |          |

|               | 10 = CTEDG   |                                    |                 |                   |                  |                 |          |

|               |              | pecial Event Tr<br>pecial Event Tr |                 |                   |                  |                 |          |

| bit 1         |              | Edge 2 Status b                    |                 |                   |                  |                 |          |

| bit i         |              | vent has occur                     |                 |                   |                  |                 |          |

|               | U U          | vent has not or                    |                 |                   |                  |                 |          |

| bit 0         | EDG1STAT: E  | Edge 1 Status b                    | oit             |                   |                  |                 |          |

|               |              | vent has occur                     |                 |                   |                  |                 |          |

|               | 0 = Edge 1 e | vent has not or                    | curred          |                   |                  |                 |          |

|               |              |                                    |                 |                   |                  |                 |          |

#### REGISTER 24-2: CTMUCONL: CTMU CONTROL LOW REGISTER

# 25.6 Program Verification and Code Protection

For all devices in the PIC18F87J90 family of devices, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, CP0. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

#### 25.6.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against untoward changes or reads in two ways. The primary protection is the write-once feature of the Configuration bits which prevents reconfiguration once the bit has been programmed during a power cycle. To safeguard against unpredictable events, Configuration bit changes resulting from individual cell-level disruptions (such as ESD events) will cause a parity error and trigger a device Reset.

The data for the Configuration registers is derived from the Flash Configuration Words in program memory. When the CP0 bit set, the source data for device configuration is also protected as a consequence.

# 25.7 In-Circuit Serial Programming

PIC18F87J90 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 25.8 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 25-4 shows which resources are required by the background debugger.

#### TABLE 25-4: DEBUGGER RESOURCES

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

| BTFSC                                                      | Bit Test File                                                                 | , Skip if Clear                                                                                                             |                                                                  | BTFSS          |                                                       | Bit Test File                                                                  | , Skip if Set                                                                                                                       |                                                         |

|------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------|-------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Syntax:                                                    | BTFSC f, b                                                                    | {,a}                                                                                                                        |                                                                  | Syntax:        |                                                       | BTFSS f, b {                                                                   | ,a}                                                                                                                                 |                                                         |

| Operands:                                                  | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                         |                                                                                                                             |                                                                  | Operand        | ls:                                                   | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                          |                                                                                                                                     |                                                         |

| Operation:                                                 | skip if (f <b>)</b>                                                           | = 0                                                                                                                         |                                                                  | Operatio       | n:                                                    | skip if (f <b>)</b>                                                            | = 1                                                                                                                                 |                                                         |

| Status Affected:                                           | None                                                                          |                                                                                                                             |                                                                  | Status A       | ffected:                                              | None                                                                           |                                                                                                                                     |                                                         |

| Encoding:                                                  | 1011                                                                          | bbba ff                                                                                                                     | ff ffff                                                          | Encodin        | g:                                                    | 1010                                                                           | bbba ffi                                                                                                                            | ff ffff                                                 |

| Description:                                               | instruction is<br>the next inst<br>current instru<br>and a NOP is             | gister 'f' is '0', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>executed instruction.                      | 'b' is '0', then<br>during the<br>in is discarded<br>ead, making | Descript       | ion:                                                  | instruction is<br>the next instruction<br>current instruction<br>and a NOP is  | gister 'f' is '1', t<br>skipped. If bit<br>uction fetched<br>iction execution<br>executed inste<br>cle instruction.                 | 'b' is '1', then<br>during the<br>n is discarded        |

|                                                            |                                                                               | e Access Banł<br>BSR is used to                                                                                             | k is selected. If<br>a select the                                |                |                                                       |                                                                                | e Access Bank<br>BSR is used to                                                                                                     |                                                         |

|                                                            | is enabled, t<br>Indexed Lite<br>whenever f ≤<br>Section 26.2<br>Bit-Oriented | d the extended<br>his instruction<br>ral Offset Addr<br>95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | essing mode<br>ented and<br>in Indexed                           |                |                                                       | set is enable<br>Indexed Liter<br>whenever f ≤<br>Section 26.2<br>Bit-Oriented | d the extended<br>d, this instruction<br>ral Offset Addro<br>95 (5Fh). See<br>2.3 "Byte-Orient<br>I Instructions<br>of Mode" for de | on operates in<br>essing mode<br>nted and<br>in Indexed |

| Words:                                                     | 1                                                                             |                                                                                                                             |                                                                  | Words:         |                                                       | 1                                                                              |                                                                                                                                     |                                                         |

| Cycles:                                                    | •                                                                             | cles if skip and<br>2-word instruc                                                                                          |                                                                  | Cycles:        |                                                       |                                                                                | vcles if skip and<br>a 2-word instru                                                                                                |                                                         |

| Q Cycle Activity:                                          |                                                                               |                                                                                                                             |                                                                  | Q Cycle        | e Activity:                                           |                                                                                |                                                                                                                                     |                                                         |

| Q1                                                         | Q2                                                                            | Q3                                                                                                                          | Q4                                                               |                | Q1                                                    | Q2                                                                             | Q3                                                                                                                                  | Q4                                                      |

| Decode                                                     | Read                                                                          | Process                                                                                                                     | No                                                               |                | Decode                                                | Read                                                                           | Process                                                                                                                             | No                                                      |

| lf skip:                                                   | register 'f'                                                                  | Data                                                                                                                        | operation                                                        | lf skip:       |                                                       | register 'f'                                                                   | Data                                                                                                                                | operation                                               |

| li skip.<br>Q1                                             | Q2                                                                            | Q3                                                                                                                          | Q4                                                               | li skip.       | Q1                                                    | Q2                                                                             | Q3                                                                                                                                  | Q4                                                      |

| No                                                         | No                                                                            | No                                                                                                                          | No                                                               |                | No                                                    | No                                                                             | No                                                                                                                                  | No                                                      |

| operation                                                  | operation                                                                     | operation                                                                                                                   | operation                                                        | C              | peration                                              | operation                                                                      | operation                                                                                                                           | operation                                               |

| If skip and followe                                        | ,                                                                             |                                                                                                                             |                                                                  | lf skip a      |                                                       | by 2-word inst                                                                 |                                                                                                                                     |                                                         |

| Q1                                                         | Q2                                                                            | Q3                                                                                                                          | Q4                                                               |                | Q1                                                    | Q2                                                                             | Q3                                                                                                                                  | Q4                                                      |

| No<br>operation                                            | No<br>operation                                                               | No<br>operation                                                                                                             | No<br>operation                                                  |                | No<br>peration                                        | No<br>operation                                                                | No<br>operation                                                                                                                     | No<br>operation                                         |

| No                                                         | No                                                                            | No                                                                                                                          | No                                                               |                | No                                                    | No                                                                             | No                                                                                                                                  | No                                                      |

| operation                                                  | operation                                                                     | operation                                                                                                                   | operation                                                        | c              | peration                                              | operation                                                                      | operation                                                                                                                           | operation                                               |

| Example:                                                   | HERE BI<br>FALSE :<br>TRUE :                                                  | IFSC FLAG                                                                                                                   | ;, l, O                                                          | <u>Example</u> | <u>::</u>                                             | HERE BI<br>FALSE :<br>TRUE :                                                   | FSS FLAG                                                                                                                            | , 1, 0                                                  |

| Before Instruc<br>PC<br>After Instructio<br>If FLAG<<br>PC | = add<br>on<br>:1> = 0;                                                       | ress (HERE)                                                                                                                 |                                                                  |                | ore Instruct<br>PC<br>er Instructio<br>If FLAG<<br>PC | = add<br>n<br>1> = 0;                                                          | ress (HERE)                                                                                                                         |                                                         |

| If FLAG<<br>PC                                             |                                                                               | ress (False                                                                                                                 | )                                                                |                | If FLAG<<br>PC                                        | 1> = 1;                                                                        | ress (TRUE)                                                                                                                         |                                                         |

| Syntax:BZnOperands: $-128 \le n \le 127$ Operation:if Zero bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PCStatus Affected:NoneEncoding: $1110$ $0000$ nnnnDescription:If the Zero bit is '1', then the program<br>will branch.The 2's complement number '2n' is<br>added to the PC. Since the PC will ha<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2 n. This instruction is then<br>two-cycle instruction.Words:1Cycles:1(2)Q Cycle Activity:<br>If Jump:Q1Q1Q2Q3Q4NoNoNoNoNoNoNoQ1Q2Q3Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n<br>ave |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Operation:if Zero bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PCStatus Affected:NoneEncoding:1110 0000 nnnn nnnDescription:If the Zero bit is '1', then the program<br>will branch.The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n<br>ave |

| $\begin{array}{c c} (PC) + 2 + 2n \rightarrow PC \\ \hline \\ \mbox{Status Affected:} None \\ \hline \\ \mbox{Encoding:} & \hline 1110 & 0000 & nnnn & nnn \\ \hline \\ \mbox{Encoding:} & \hline 1110 & 0000 & nnnn & nnn \\ \hline \\ \mbox{Description:} & \mbox{If the Zero bit is '1', then the program will branch.} \\ \hline \\ \mbox{The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then two-cycle instruction. \\ \hline \\ \mbox{Words:} & 1 \\ \hline \\ \mbox{Cycles:} & 1(2) \\ \hline \\ \mbox{Q Cycle Activity:} \\ \mbox{If Jump:} \\ \hline \\ \hline \\ \hline \\ \mbox{No} & No & No \\ \hline \\ \hline \\ \mbox{No} & No & No \\ \hline \\ \mbox{operation operation operation} \\ \hline \\ \mbox{Jerminal operation operation} \\ \hline \\ \mbox{Jerminal operation operation} \\ \hline \\ \mbox{Jerminal operation operation} \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | n<br>ave |

| Encoding:       1110       0000       nnnn       nnn         Description:       If the Zero bit is '1', then the program will branch.         The 2's complement number '2n' is added to the PC. Since the PC will ha incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then two-cycle instruction.         Words:       1         Cycles:       1(2)         Q Cycle Activity:       If Jump:         Q1       Q2       Q3       Q4         Decode       Read literal       Process       Write to 'n'         No       No       No       No         No       No       No       No         If No Jump:       Unite No       Operation       Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n<br>ave |

| Description:       If the Zero bit is '1', then the program will branch.         The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then two-cycle instruction.         Words:       1         Cycles:       1(2)         Q Cycle Activity:       If Jump:         Q1       Q2       Q3       Q4         Decode       Read literal       Process       Write to 'n'         No       No       No       No         No       No       No       No         If No Jump:       Uncertain operation       Operation       Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n<br>ave |

| will branch.The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then<br>two-cycle instruction.Words:1Cycles:1(2)Q Cycle Activity:<br>If Jump:1Q1Q2Q3Q4Q4DecodeRead literal<br>'n'ProcessWrite to<br>'n'NoNoNooperationoperationIf No Jump:Image: Coloration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ave      |