Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                           |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | SH-2 DSP                                                                      |

| Core Size                  | 32-Bit Single-Core                                                            |

| Speed                      | 62.5MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, IrDA, FIFO, SCI, SIO                                       |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 29                                                                            |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | -                                                                             |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 208-LQFP                                                                      |

| Supplier Device Package    | 208-LQFP (28x28)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417616sfv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Revision (See Manual for Details)** Page

| 10.2.8             |

|--------------------|

| Transmit/Receive   |

| Status Copy Enable |

Register (TRSCER)

Item

#### Description amended

437

| •              |        |    |    |    |    |    |    |    |

|----------------|--------|----|----|----|----|----|----|----|

| Bit:           | 31     | 30 | 29 |    | 19 | 18 | 17 | 16 |

|                | —      | _  | _  |    | _  | _  | _  | —  |

| Initial value: | 0      | 0  | 0  |    | 0  | 0  | 0  | 0  |

| R/W:           | R      | R  | R  |    | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

| Bit:           | 15     | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|                | —      | _  | _  | —  | —  | —  | —  | —  |

| Initial value: | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R      | R  | R  | R  | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

| Bit:           | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|                | RMAFCE | —  | —  | —  | —  | —  | —  | —  |

| Initial value: | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R/W    | R  | R  | R  | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

Bits 31 to 8-Reserved These bits are always read as 0. The write value should always be 0.

Bit 7-Multicast Address Frame Receive (RMAF): Bit Copy Enable (RMAFCE)

| Bit 7: RMAFCE | Description                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------|

| 0             | Enables the RMAF bit status to be indicated in the RFS7 bit in the receive descriptor.                 |

| 1             | Disables occurrence of corresponding source to be indicated in the RFS7 bit in the receive descriptor. |

Bits 6 to 0-Reserved: These bits are always read as 0. The write value should always be 0.

10.3.1 Descriptor 450 List and Data Buffers

#### Description amended

Bit 27-Transmit Frame Error (TFE): Indicates that one or other bit of the transmit frame status indicated by bits 26 to 0 is set.

Transmit Descriptor 0 (TD0)

#### Bit 27: TFE Description 0

| 1 An error of some kind eccurred during transmission (see hits 26 to 0) | 0 | No error during transmission                                          |  |

|-------------------------------------------------------------------------|---|-----------------------------------------------------------------------|--|

|                                                                         | 1 | An error of some kind occurred during transmission (see bits 26 to 0) |  |

Bits 26 to 0-Transmit Frame Status 26 to 0 (TFS26 to TFS0): These bits indicate the error status during frame transmission.

- TFS26 to TFS9-Reserved

- TFS8—Teransmit Abort Detect

- Note: This bit is set to 1 wh any of Transmit Frame Status bits 4 to 0 is set. When this bit is set, the Transmit Frame Error bit (bit 27: TFE) is set to 1.

- TFS7 to TFS5—Reserved

| Туре      | Symbol    | I/O | Name         | Function                                    |

|-----------|-----------|-----|--------------|---------------------------------------------|

| I/O ports | PA0–PA13* | I/O | General port | General input/output port pins              |

|           |           |     |              | Input or output can be specified bit by bit |

|           | PB0–PB15  | I/O | General port | General input/output port pins              |

|           |           |     |              | Input or output can be specified bit by bit |

Note: \* PA3 cannot be used; CKPO is valid instead.

#### 1.3.3 Pin Multiplexing

#### Table 1.3 Pin Multiplexing

| No. | Function 1         | Function 2 | Function 3 | Function 4 | Туре           |

|-----|--------------------|------------|------------|------------|----------------|

| 12  | PLLV <sub>CC</sub> |            |            |            | Clocks         |

| 9   | PLLV <sub>SS</sub> |            |            |            |                |

| 11  | PLLCAP1            |            |            |            |                |

| 10  | PLLCAP2            |            |            |            |                |

| 19  | EXTAL              |            |            |            |                |

| 21  | XTAL               |            |            |            |                |

| 23  | CKIO               |            |            |            |                |

| 24  | CKPREQ/CKM         |            |            |            |                |

| 25  | CKPACK             |            |            |            | 9 pins         |

| 8   | RES                |            |            |            | System control |

| 13  | MD4                |            |            |            |                |

| 14  | MD3                |            |            |            |                |

| 15  | MD2                |            |            |            |                |

| 16  | MD1                |            |            |            |                |

| 17  | MD0                |            |            |            | 6 pins         |

| 5   | NMI                |            |            |            | Interrupts     |

| 1   | IRL3               |            |            |            |                |

| 2   | IRL2               |            |            |            |                |

| 3   | IRL1               |            |            |            |                |

| 4   | IRL0               |            |            |            |                |

| 27  | IVECF              |            |            |            | 6 pins         |

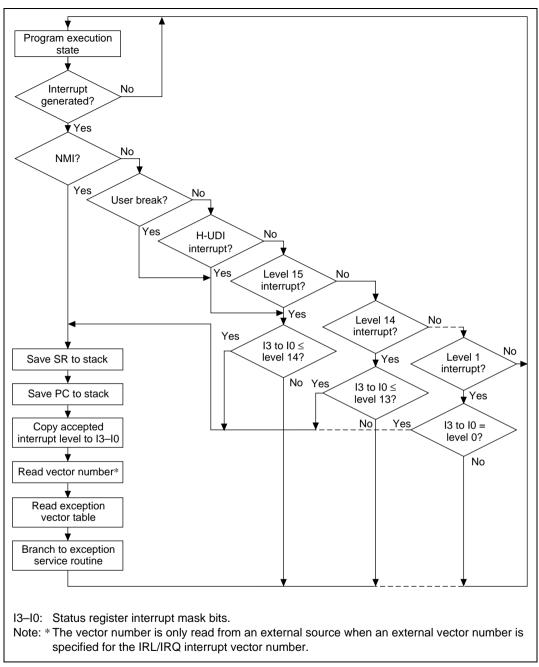

Figure 5.8 Interrupt Sequence Flowchart

## Section 6 User Break Controller (UBC)

## 6.1 Overview

The user break controller (UBC) provides functions that simplify program debugging. When break conditions are set in the UBC, a user break interrupt is generated according to the conditions of the bus cycle generated by the CPU or on-chip DMAC (DMAC or E-DMAC).

This function makes it easy to design a sophisticated self-monitoring debugger, enabling programs to be debugged with the chip alone, without using an in-circuit emulator.

#### 6.1.1 Features

The UBC has the following features:

- The following can be set as break conditions:

- Number of break channels: Four (channels A, B, C, and D)

- User break interrupts can be generated on independent or sequential conditions for channels A, B, C, and D.

- Sequential break settings

- $\bullet \quad \text{Channel } A \to \text{channel } B \to \text{channel } C \to \text{channel } D$

- $\bullet \quad \text{Channel } B \to \text{channel } C \to \text{channel } D$

- Channel  $C \rightarrow$  channel D

- 1. Address: 32-bit masking capability, individual address setting possible (cache bus (CPU), internal bus (DMAC, E-DMAC), X/Y bus)

- 2. Data (channels C and D only,): 32-bit masking capability, individual address setting possible (cache bus (CPU), internal bus (DMAC, E-DMAC), X/Y bus)

- 3. Bus master: CPU cycle/on-chip DMAC (DMAC, E-DMAC) cycle

- 4. Bus cycle: Instruction fetch/data access

- 5. Read/write

- 6. Operand cycle: Byte/word/longword

- User break interrupt generation on occurrence of break condition

A user-written user break interrupt exception routine can be executed.

- Processing can be stopped before or after instruction execution in an instruction fetch cycle.

- Break with specification of number of executions (channels C and D only) Settable number of executions: maximum 2<sup>12</sup> – 1 (4095)

- PC trace function

# Section 7 Bus State Controller (BSC)

## 7.1 Overview

The bus state controller (BSC) manages the address spaces and outputs control signals to allow optimum memory accesses to the five spaces. This enables memories like DRAM, and SDRAM, and peripheral chips, to be linked directly.

#### 7.1.1 Features

The BSC has the following features:

- Address space is managed as five spaces

- Maximum linear 32 Mbytes for each of the address spaces CS0 to CS4

- Memory type (DRAM, synchronous DRAM, burst ROM, etc.) can be specified for each space.

- Bus width (8, 16, or 32 bits) can be selected for each space.

- Wait state insertion can be controlled for each space.

- Control signals are output for each space.

- Cache

- Cache area and cache-through area can be selected by access address.

- In cache access, in the event of a cache access miss 16 bytes are read consecutively in 4byte units to fill the cache. Write-through mode/write-back mode can be selected for writes.

- In cache-through access, access is performed according to access size.

- Refresh

- Supports  $\overline{CAS}$ -before- $\overline{RAS}$  refresh (auto-refresh) and self-refresh.

- Refresh interval can be set by the refresh counter and clock selection.

- Intensive refreshing by means of refresh count setting (1, 2, 4, 6, or 8)

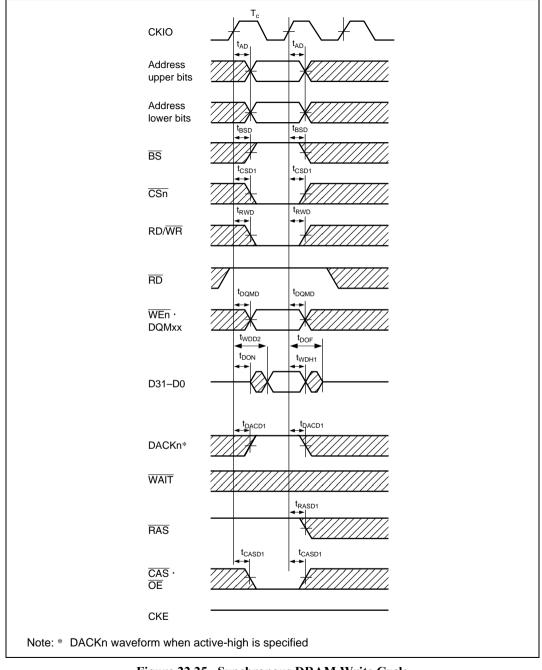

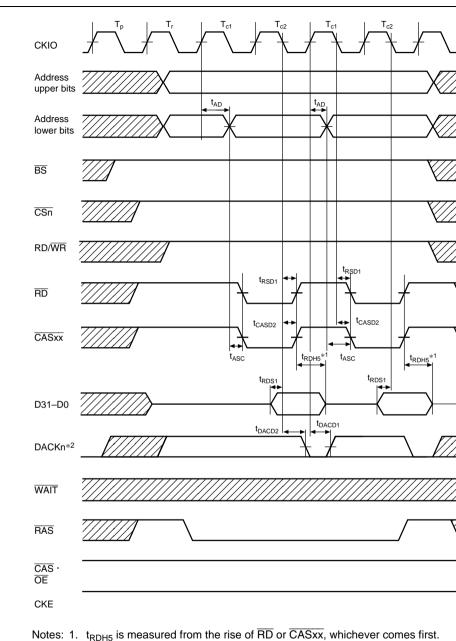

- Direct interface to DRAM

- Row/column address multiplex output.

- Burst transfer during reads, fast page mode for consecutive accesses.

- TP cycle generation to secure  $\overline{RAS}$  precharge time.

- EDO mode

- Direct interface to synchronous DRAM

- Row/column address multiplex output.

| Bit:           | 31     | 30     | 29     |        | 19     | 18     | 17    | 16    |

|----------------|--------|--------|--------|--------|--------|--------|-------|-------|

|                | —      | _      | —      |        |        | —      | _     | —     |

| Initial value: | 0      | 0      | 0      |        | 0      | 0      | 0     | 0     |

| R/W:           | R      | R      | R      |        | R      | R      | R     | R     |

|                |        |        |        |        |        |        |       |       |

| Bit:           | 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     |

|                | CEFC15 | CEFC14 | CEFC13 | CEFC12 | CEFC11 | CEFC10 | CEFC9 | CEFC8 |

| Initial value: | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| R/W:           | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   |

|                |        |        |        |        |        |        |       |       |

| Bit:           | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|                | CEFC7  | CEFC6  | CEFC5  | CEFC4  | CEFC3  | CEFC2  | CEFC1 | CEFC0 |

| Initial value: | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| R/W:           | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   |

#### 9.2.15 CRC Error Frame Counter Register (CEFCR)

CEFCR is a 16-bit counter that indicates the number of times a frame with a CRC error was received. When the value in this register reaches H'FFFF (65,535), the count is halted. The counter value is cleared to 0 by a write to this register (the write value is immaterial).

Bits 31 to 16—Reserved: These bits are always read as 0. The write value should always be 0.

Bits 15 to 0—CRC Error Frame Count 15 to 0 (CEFC15 to CEFC0): These bits indicate the count of CRC error frames received.

Note: When the Permit Receive CRC Error Frame bit (PRCEF) is set to 1 in the EtherC Mode Register (ECMR), CEFCR is not incremented by reception of a frame with a CRC error.

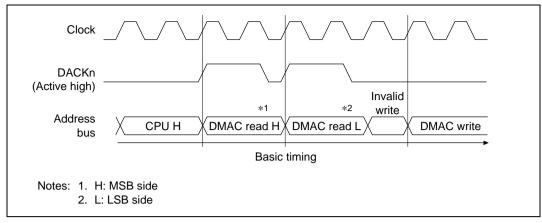

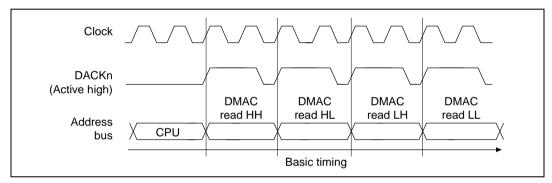

Figure 11.17 DACKn Output in Ordinary Space Accesses (AM = 0, Longword Access to 8-Bit External Device)

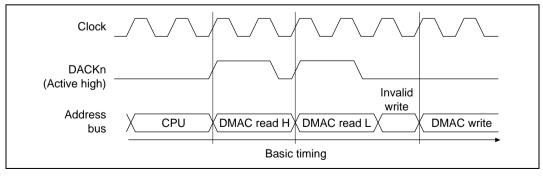

Figure 11.18 DACKn Output in Ordinary Space Accesses (AM = 0, Word Access to 8-Bit External Device)

Rev. 2.00 Mar 09, 2006 page 498 of 906 REJ09B0292-0200

#### 11.3.8 DMA Transfer End

The DMA transfer ending conditions vary when channels end individually and when both channels end together.

**Conditions for Channels Ending Individually:** When either of the following conditions is met, the transfer will end in the relevant channel only:

The DMA transfer count register (TCR) value becomes 0. The DMA enable bit (DE) of the DMA channel control register (CHCR) is cleared to 0.

• Transfer end when TCR = 0

When the TCR value becomes 0, the DMA transfer for that channel ends and the transfer-end flag bit (TE) is set in CHCR. If the IE (interrupt enable) bit has already been set, a DMAC interrupt (DEI) request is sent to the CPU. For 16-byte transfer, set the number of transfers × 4. Operation is not guaranteed if an incorrect value is set.

A 16-byte transfer is valid only in auto-request mode or in external request mode with edge detection. When using an external request with level detection or on-chip peripheral module request, do not specify a 16-byte transfer.

• Transfer end when DE = 0 in CHCR

When the DMA enable bit (DE) in CHCR is cleared, DMA transfers in the affected channel are halted. The TE bit is not set when this happens.

**Conditions for Both Channels Ending Simultaneously:** Transfers on both channels end when either of the following conditions is met:

The NMIF (NMI flag) bit or AE (address error flag) bit in DMAOR is set to 1. The DMA master enable (DME) bit is cleared to 0 in DMAOR.

• Transfer end when NMIF = 1 or AE = 1 in DMAOR

When an NMI interrupt or DMAC address error occurs and the NMIF or AE bit is set to 1 in DMAOR, all channels stop their transfers. The DMA source address register (SAR), destination address register (DAR), and transfer count register (TCR) are all updated by the transfer immediately preceding the halt. When this transfer is the final transfer, TE = 1 and the transfer ends. To resume transfer after NMI interrupt exception handling or address error exception handling, clear the appropriate flag bit. When the DE bit is then set to 1, the transfer on that channel will restart. To avoid this, keep its DE bit at 0. In dual address mode, DMA transfer will be halted after the completion of the following write cycle even when the address error occurs in the initial read cycle. SAR, DAR and TCR are updated by the final transfer.

Bit 4—Break Detect (BRK): Indicates that a receive data break signal has been detected.

| Bit 4: | BRK Description                                                                                                                                                              |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | A break signal has not been received (Initial value)                                                                                                                         |

|        | [Clearing conditions]                                                                                                                                                        |

|        | In a reset or in standby mode                                                                                                                                                |

|        | <ul> <li>When 0 is written to BRK after reading BRK = 1</li> </ul>                                                                                                           |

| 1      | A break signal has been received                                                                                                                                             |

|        | [Setting condition]                                                                                                                                                          |

|        | When data with a framing error is received, and a framing error also occurs in the next receive data (all space "0")                                                         |

| Note:  | When a break is detected, transfer to SCFRDR of the receive data (H'00) following detection is halted. When the break and and the receive signal returns to mark "1" receive |

detection is halted. When the break ends and the receive signal returns to mark "1", receive data transfer is resumed.

Bit 3—Framing Error (FER): Indicates a framing error in the data read from the receive FIFO data register (SCFRDR).

| Bit 3: FER | Description                                                                    |

|------------|--------------------------------------------------------------------------------|

| 0          | There is no framing error in the receive data read from SCFRDR (Initial value) |

|            | [Clearing conditions]                                                          |

|            | In a reset or in standby mode                                                  |

|            | When there is no framing error in SCFRDR read data                             |

| 1          | There is a framing error in the receive data read from SCFRDR                  |

|            | [Setting condition]                                                            |

|            | When there is a framing error in SCFRDR read data                              |

|            |                                                                                |

Bit 2—Parity Error (PER): In asynchronous mode, indicates a parity error in the data read from the receive FIFO data register (SCFRDR).

| Description                                                   |                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| There is no parity error in the receive data read from SCFRDR | (Initial value)                                                                                                                                                                                                                                                                          |

| [Clearing conditions]                                         |                                                                                                                                                                                                                                                                                          |

| In a reset or in standby mode                                 |                                                                                                                                                                                                                                                                                          |

| When there is no parity error in SCFRDR read data             |                                                                                                                                                                                                                                                                                          |

| There is a parity error in the receive data read from SCFRDR  |                                                                                                                                                                                                                                                                                          |

| [Setting condition]                                           |                                                                                                                                                                                                                                                                                          |

| When there is a parity error in SCFRDR read data              |                                                                                                                                                                                                                                                                                          |

|                                                               | <ul> <li>There is no parity error in the receive data read from SCFRDR</li> <li>[Clearing conditions]</li> <li>In a reset or in standby mode</li> <li>When there is no parity error in SCFRDR read data</li> <li>There is a parity error in the receive data read from SCFRDR</li> </ul> |

|                      |   |     |              |          |     | Ρφ (         | MHz)   | )   |              |   |     |              |

|----------------------|---|-----|--------------|----------|-----|--------------|--------|-----|--------------|---|-----|--------------|

|                      | 2 |     |              | 2.097152 |     |              | 2.4576 |     |              | 3 |     |              |

| Bit Rate<br>(Bits/s) | n | N   | Error<br>(%) | n        | N   | Error<br>(%) | n      | N   | Error<br>(%) | n | N   | Error<br>(%) |

| 110                  | 1 | 141 | 0.03         | 1        | 148 | -0.04        | 1      | 174 | -0.26        | 1 | 212 | 0.03         |

| 150                  | 1 | 103 | 0.16         | 1        | 108 | 0.21         | 1      | 127 | 0.00         | 1 | 155 | 0.16         |

| 300                  | 0 | 207 | 0.16         | 0        | 217 | 0.21         | 0      | 255 | 0.00         | 1 | 77  | 0.16         |

| 600                  | 0 | 103 | 0.16         | 0        | 108 | 0.21         | 0      | 127 | 0.00         | 0 | 155 | 0.16         |

| 1200                 | 0 | 51  | 0.16         | 0        | 54  | -0.70        | 0      | 63  | 0.00         | 0 | 77  | 0.16         |

| 2400                 | 0 | 25  | 0.16         | 0        | 26  | 1.14         | 0      | 31  | 0.00         | 0 | 38  | 0.16         |

| 4800                 | 0 | 12  | 0.16         | 0        | 13  | -2.48        | 0      | 15  | 0.00         | 0 | 19  | -2.34        |

| 9600                 | 0 | 6   | -6.99        | 0        | 6   | -2.48        | 0      | 7   | 0.00         | 0 | 9   | -2.34        |

| 19200                | 0 | 2   | 8.51         | 0        | 2   | 13.78        | 0      | 3   | 0.00         | 0 | 4   | -2.34        |

| 31250                | 0 | 1   | 0.00         | 0        | 1   | 4.86         | 0      | 1   | 22.88        | 0 | 2   | 0.00         |

| 38400                | 0 | 1   | -18.62       | 0        | 1   | -14.67       | 0      | 1   | 0.00         |   | —   | _            |

Table 14.3

Examples of Bit Rates and SCBRR Settings in Asynchronous Mode

Pφ (MHz)

|                      | - + ( |      |              |   |          |              |   |     |              |   |     |              |

|----------------------|-------|------|--------------|---|----------|--------------|---|-----|--------------|---|-----|--------------|

|                      |       | 3.68 | 364          |   | 4 4.9152 |              |   | 52  | 5            |   |     |              |

| Bit Rate<br>(Bits/s) | n     | N    | Error<br>(%) | n | N        | Error<br>(%) | n | N   | Error<br>(%) | n | N   | Error<br>(%) |

| 110                  | 2     | 64   | 0.70         | 2 | 70       | 0.03         | 2 | 86  | 0.31         | 2 | 88  | -0.25        |

| 150                  | 1     | 191  | 0.00         | 1 | 207      | 0.16         | 1 | 255 | 0.00         | 2 | 64  | 0.16         |

| 300                  | 1     | 95   | 0.00         | 1 | 103      | 0.16         | 1 | 127 | 0.00         | 1 | 129 | 0.16         |

| 600                  | 0     | 191  | 0.00         | 0 | 207      | 0.16         | 0 | 255 | 0.00         | 1 | 64  | 0.16         |

| 1200                 | 0     | 95   | 0.00         | 0 | 103      | 0.16         | 0 | 127 | 0.00         | 0 | 129 | 0.16         |

| 2400                 | 0     | 47   | 0.00         | 0 | 51       | 0.16         | 0 | 63  | 0.00         | 0 | 64  | 0.16         |

| 4800                 | 0     | 23   | 0.00         | 0 | 25       | 0.16         | 0 | 31  | 0.00         | 0 | 32  | -1.36        |

| 9600                 | 0     | 11   | 0.00         | 0 | 12       | 0.16         | 0 | 15  | 0.00         | 0 | 15  | 1.73         |

| 19200                | 0     | 5    | 0.00         | 0 | 6        | -6.99        | 0 | 7   | 0.00         | 0 | 7   | 1.73         |

| 31250                |       |      | _            | 0 | 3        | 0.00         | 0 | 4   | -1.70        | 0 | 4   | 0.00         |

| 38400                | 0     | 2    | 0.00         | 0 | 2        | 8.51         | 0 | 3   | 0.00         | 0 | 3   | 1.73         |

|                      |       |      |              |   |          |              |   |     |              |   |     |              |

| <b>Receive Error</b> | Abbreviation | Condition                                                                                        | Data Transfer                                        |

|----------------------|--------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Overrun error        | ORER         | Next serial receive operation is<br>completed while there are 16<br>receive data bytes in SCFRDR | Receive data is not transferred from SCRSR to SCFRDR |

| Framing error        | FER          | Stop bit is 0                                                                                    | Receive data is transferred from SCRSR to SCFRDR     |

| Parity error         | PER          | Received data parity differs<br>from that (even or odd) set in<br>SCSMR                          | Receive data is transferred from SCRSR to SCFRDR     |

#### Table 14.11 Receive Error Conditions

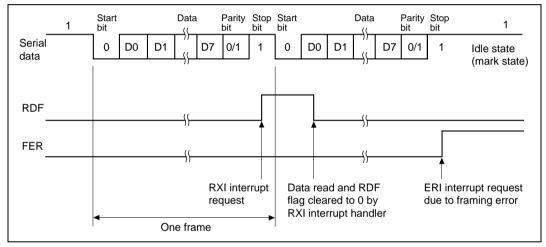

Figure 14.9 shows an example of the operation for reception in asynchronous mode.

#### Figure 14.9 Example of SCIF Receive Operation (Example with 8-Bit Data, Parity, One Stop Bit, LSB-First Transfer)

5. When modem control is enabled, the  $\overline{\text{RTS}}$  signal is output when SCFRDR is empty. When  $\overline{\text{RTS}}$  is 0, reception is possible. When  $\overline{\text{RTS}}$  is 1, this indicates that SCFRDR is full and reception is not possible.

Figure 14.10 shows an example of the operation when modem control is used.

#### 14.3.5 Use of Transmit/Receive FIFO Buffers

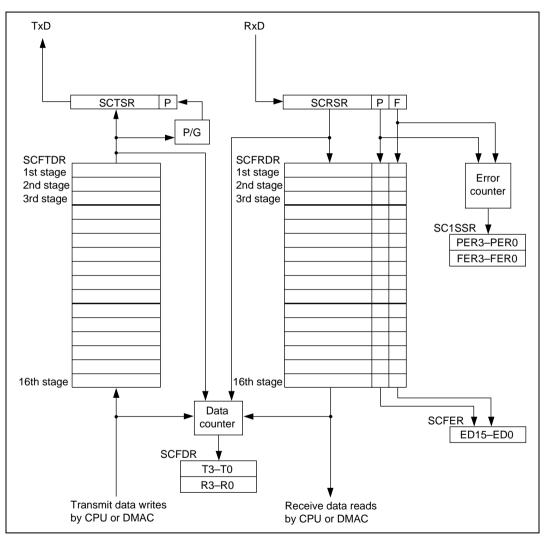

The SCIF has independent 16-stage FIFO buffers for transmission and reception. The configuration of these buffers is shown in figure 14.23.

Figure 14.23 Transmit/Receive FIFO Configuration

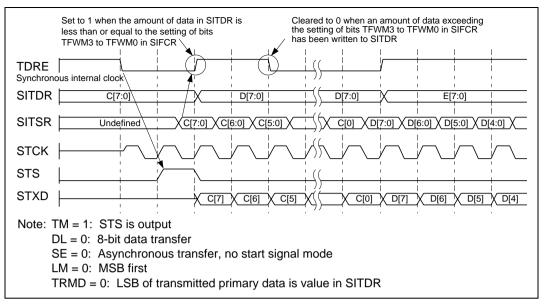

Figure 15.9 Transmission: Continuous Transfer Mode (TM = 1 Mode)/MSB First

Figure 15.10 shows interval transfer mode when TM is cleared to 0 in SICTR and with LSB first.

Figure 15.11 shows continuous transfer mode when TM is cleared to 0 in SICTR and with LSB first.

Figure 15.12 shows interval transfer mode when TM is set to 1 in SICTR and with LSB first.

Figure 15.13 shows continuous transfer mode when TM is set to 1 in SICTR and with LSB first.

| Item               | Channel 0                                                                                                                                     | Channel 1                                                                                                                             | Channel 2                                                                                                                             |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| DMAC activation    | TGR compare match or<br>input capture                                                                                                         | _                                                                                                                                     | _                                                                                                                                     |

| Interrupt sources  | <ul> <li>5 sources</li> <li>Compare match or input capture 0A</li> <li>Compare match or input capture 0B</li> <li>Compare match or</li> </ul> | <ul> <li>4 sources</li> <li>Compare match or input capture 1A</li> <li>Compare match or input capture 1B</li> <li>Overflow</li> </ul> | <ul> <li>4 sources</li> <li>Compare match or input capture 2A</li> <li>Compare match or input capture 2B</li> <li>Overflow</li> </ul> |

| Note: — : Not poss | input capture 0C Compare match or input capture 0D Overflow ible                                                                              | Underflow                                                                                                                             | Underflow                                                                                                                             |

#### 17.1.3 Pin Configuration

Table 17.2 shows the pin configuration of the TPU.

### Table 17.2Pin Configuration

| Channel | Name                                  | Abbreviation | I/O   | Function                                                                       |

|---------|---------------------------------------|--------------|-------|--------------------------------------------------------------------------------|

| All     | Clock input A                         | TCLKA        | Input | External clock A input pin<br>(Channel 1 phase counting mode A<br>phase input) |

|         | Clock input B                         | TCLKB        | Input | External clock B input pin<br>(Channel 1 phase counting mode B<br>phase input) |

|         | Clock input C                         | TCLKC        | Input | External clock C input pin<br>(Channel 2 phase counting mode A<br>phase input) |

|         | Clock input D                         | TCLKD        | Input | External clock D input pin<br>(Channel 2 phase counting mode B<br>phase input) |

| 0       | Input capture/output compare match A0 | TIOCA0       | I/O   | TGR0A input capture input/output<br>compare output/PWM output pin              |

|         | Input capture/output compare match B0 | TIOCB0       | I/O   | TGR0B input capture input/output<br>compare output/PWM output pin              |

|         | Input capture/output compare match C0 | TIOCC0       | I/O   | TGR0C input capture input/output<br>compare output/PWM output pin              |

|         | Input capture/output compare match D0 | TIOCD0       | I/O   | TGR0D input capture input/output compare output/PWM output pin                 |

| 1       | Input capture/output compare match A1 | TIOCA1       | I/O   | TGR1A input capture input/output<br>compare output/PWM output pin              |

|         | Input capture/output compare match B1 | TIOCB1       | I/O   | TGR1B input capture input/output<br>compare output/PWM output pin              |

| 2       | Input capture/output compare match A2 | TIOCA2       | I/O   | TGR2A input capture input/output compare output/PWM output pin                 |

|         | Input capture/output compare match B2 | TIOCB2       | I/O   | TGR2B input capture input/output compare output/PWM output pin                 |

| 62       D20       Input       269         Output       268         Output enable       267         63       D21       Input       266         Output enable       264         64       D22       Input       263         Output enable       261       262         Output enable       264       263         65       D23       Input       260         Output enable       261       269         04put enable       261       261         68       D24       Input       259         Output enable       255       255         70       D25       Input       255         71       D26       Input       251         Output enable       252       252         71       D26       Input       251         Output enable       249       249         72       D27       Input       248         Output enable       246       249         73       D28       Input       242         Output enable       243       243         74       D29       Input       242                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin No. | Pin Name | Input/Output  | Bit No. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|---------------|---------|

| $\begin{tabular}{ c c c c } \hline $1$ Output enable & $267$ \\ \hline $0$ Output & $266$ \\ \hline $0$ Output enable & $264$ \\ \hline $0$ Output enable & $264$ \\ \hline $0$ Output enable & $263$ \\ \hline $0$ Output enable & $261$ \\ \hline $0$ Output enable & $261$ \\ \hline $0$ Output enable & $261$ \\ \hline $0$ Output enable & $259$ \\ \hline $0$ Output enable & $258$ \\ \hline $68$ & $D24$ & $1$ nput & $257$ \\ \hline $0$ Output enable & $255$ \\ \hline $70$ & $D25$ & $1$ nput & $254$ \\ \hline $0$ Output enable & $252$ \\ \hline $71$ & $D26$ & $1$ nput & $251$ \\ \hline $0$ Output enable & $252$ \\ \hline $71$ & $D26$ & $1$ nput & $251$ \\ \hline $0$ Output enable & $252$ \\ \hline $71$ & $D26$ & $1$ nput & $251$ \\ \hline $0$ Output enable & $252$ \\ \hline $72$ & $D27$ & $1$ nput & $243$ \\ \hline $0$ Output enable & $249$ \\ \hline $73$ & $D28$ & $1$ nput & $244$ \\ \hline $0$ Output enable & $243$ \\ \hline $74$ & $D29$ & $1$ nput & $241$ \\ \hline $74$ & $D29$ & $1$ nput & $241$ \\ \hline $75$ & $0$ nput & $241$ \\ \hline $74$ & $D29$ & $1$ nput & $241$ \\ \hline $75$ & $0$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $241$ \\ \hline $75$ & $25$ & $1$ nput & $25$ & $25$ \\ \hline $75$ & $25$ & $1$ n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62      | D20      | Input         | 269     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |          | Output        | 268     |

| $ \begin{array}{ c c c c } \hline \begin{tabular}{ c c c } \hline \end{tabular} \\ \hline \en$                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |          | Output enable | 267     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63      | D21      | Input         | 266     |

| 64         D22         Input         263           Output         262         0utput enable         261           65         D23         Input         260           Output         259         0utput         259           Output enable         258         68         D24         Input         257           68         D24         Input         256         0utput enable         255           70         D25         Input         254         0utput enable         252           71         D26         Input         251         0utput enable         252           71         D26         Input         250         0utput enable         249           72         D27         Input         248         0utput         246           73         D28         Input         245         0utput         243           74         D29         Input         242         0utput         243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |          | Output        | 265     |

| $ \begin{array}{ c c c c c } \hline \mbox{Dutput} & 262 \\ \hline \mbox{Output enable} & 261 \\ \hline \mbox{Output enable} & 260 \\ \hline \mbox{Output} & 259 \\ \hline \mbox{Output enable} & 258 \\ \hline \mbox{68} & D24 & [nput & 257 \\ \hline \mbox{Output enable} & 255 \\ \hline \mbox{Output enable} & 252 \\ \hline \mbox{Output enable} & 251 \\ \hline \mbox{Output enable} & 249 \\ \hline \mbox{Output enable} & 249 \\ \hline \mbox{Output enable} & 249 \\ \hline \mbox{Output enable} & 248 \\ \hline \mbox{Output enable} & 248 \\ \hline \mbox{Output enable} & 246 \\ \hline \mbox{Output enable} & 244 \\ \hline \mbox{Output enable} & 245 \\ \hline \mbox{Output enable} & 243 \\ \hline \mbox{Output enable} & 241 \\ \hline \mbox{Output enable} &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |          | Output enable | 264     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64      | D22      | Input         | 263     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |          | Output        | 262     |

| $ \begin{array}{ c c c c c } \hline \hline Output & 259 \\ \hline Output enable & 258 \\ \hline \hline Output enable & 257 \\ \hline Output & 256 \\ \hline Output enable & 255 \\ \hline \hline O & D25 & Input & 254 \\ \hline Output & 253 \\ \hline Output enable & 252 \\ \hline \hline O & D26 & Input & 251 \\ \hline Output enable & 252 \\ \hline \hline 1 & D26 & Input & 251 \\ \hline Output enable & 259 \\ \hline Output enable & 249 \\ \hline \hline Output enable & 249 \\ \hline \hline O & Output enable & 249 \\ \hline \hline O & Output enable & 249 \\ \hline \hline O & Output enable & 248 \\ \hline Output & 247 \\ \hline Output & 248 \\ \hline Output & 248 \\ \hline Output enable & 249 \\ \hline \hline \hline O & Output enable & 249 \\ \hline \hline \hline 1 & D28 & Input & 248 \\ \hline \hline O & Output enable & 249 \\ \hline \hline \hline \hline O & Output enable & 249 \\ \hline \hline \hline \hline O & Output enable & 249 \\ \hline $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |          | Output enable | 261     |

| $ \begin{array}{ c c c c c } \hline \end{picture} \hline \hline pictu$ | 65      | D23      | Input         | 260     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |          | Output        | 259     |

| Output256 $\overline{Output enable}$ 25570D25Input $\overline{Output}$ 253 $\overline{Output}$ 253 $\overline{Output}$ 25271D26Input $\overline{Output}$ 250 $\overline{Output}$ 250 $\overline{Output}$ 24972D27Input $\overline{Output}$ 248 $\overline{Output}$ 24673D28Input $\overline{Output}$ 245 $\overline{Output}$ 24374D29Input $\overline{Output}$ 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |          | Output enable | 258     |

| Output enable25570D25Input25471D26Input25371D26Input25171D26Input25072D27Input24973D28Input24774D29Input24274D29Input242                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68      | D24      | Input         | 257     |

| $ \begin{array}{c cccc} \hline 70 & D25 & \begin{array}{c} lnput & 254 \\ \hline Output & 253 \\ \hline Output enable & 252 \\ \hline \\ \hline 71 & D26 & \begin{array}{c} lnput & 251 \\ \hline Output & 250 \\ \hline Output enable & 249 \\ \hline \\ \hline Output enable & 249 \\ \hline \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |          | Output        | 256     |