#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                      |

|---------------------------------|-------------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                    |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                |

| Speed                           | 190MHz                                                                        |

| Co-Processors/DSP               | -                                                                             |

| RAM Controllers                 | SDRAM, SRAM                                                                   |

| Graphics Acceleration           | No                                                                            |

| Display & Interface Controllers | LCD                                                                           |

| Ethernet                        | -                                                                             |

| SATA                            | -                                                                             |

| USB                             | USB 2.0 (2)                                                                   |

| Voltage - I/O                   | 3.0V, 3.3V                                                                    |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                             |

| Security Features               | -                                                                             |

| Package / Case                  | 217-LFBGA                                                                     |

| Supplier Device Package         | 217-LFBGA (15x15)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9261b-cu-999 |

|                                 |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal Name | Function                       | Туре         | Active Level | Comments                 |

|-------------|--------------------------------|--------------|--------------|--------------------------|

|             | Reset/7                        | est          |              |                          |

| NRST        | Microcontroller Reset          | I/O          | Low          | Pull-up resistor         |

| TST         | Test Mode Select               | Input        |              | Pull-down resistor       |

| BMS         | Boot Mode Select               | Input        |              |                          |

|             | Debug Unit                     | - DBGU       |              |                          |

| DRXD        | Debug Receive Data             | Input        |              |                          |

| DTXD        | Debug Transmit Data            | Output       |              |                          |

|             | Advanced Interrupt             | Controller   | - AIC        |                          |

| IRQ0–IRQ2   | External Interrupt Inputs      | Input        |              |                          |

| FIQ         | Fast Interrupt Input           | Input        |              |                          |

|             | PIO Controller - PIC           | A / PIOB /   | PIOC         |                          |

| PA0-PA31    | Parallel IO Controller A       | I/O          |              | Pulled up input at reset |

| PB0–PB31    | Parallel IO Controller B       | I/O          |              | Pulled up input at reset |

| PC0–PC31    | Parallel IO Controller C       | I/O          |              | Pulled up input at reset |

|             | External Bus In                | erface - EE  | BI           |                          |

| D0–D31      | Data Bus                       | I/O          |              | Pulled up input at reset |

| A0-A25      | Address Bus                    | Output       |              | 0 at reset               |

| NWAIT       | External Wait Signal           | Input        | Low          |                          |

|             | Static Memory Co               | ntroller - S | MC           |                          |

| NCS0-NCS7   | Chip Select Lines              | Output       | Low          |                          |

| NWR0-NWR3   | Write Signal                   | Output       | Low          |                          |

| NRD         | Read Signal                    | Output       | Low          |                          |

| NWE         | Write Enable                   | Output       | Low          |                          |

| NBS0-NBS3   | Byte Mask Signal               | Output       | Low          |                          |

|             | CompactFlas                    | h Support    |              |                          |

| CFCE1-CFCE2 | CompactFlash Chip Enable       | Output       | Low          |                          |

| CFOE        | CompactFlash Output Enable     | Output       | Low          |                          |

| CFWE        | CompactFlash Write Enable      | Output       | Low          |                          |

| CFIOR       | CompactFlash IO Read           | Output       | Low          |                          |

| CFIOW       | CompactFlash IO Write          | Output       | Low          |                          |

| CFRNW       | CompactFlash Read Not Write    | Output       |              |                          |

| CFCS0-CFCS1 | CompactFlash Chip Select Lines | Output       | Low          |                          |

|             | NAND Flash                     | Support      |              |                          |

| NANDOE      | NAND Flash Output Enable       | Output       | Low          |                          |

| NANDWE      | NAND Flash Write Enable        | Output       | Low          |                          |

| NANDCS      | NAND Flash Chip Select         | Output       | Low          |                          |

## Table 2-1. Signal Description by Peripheral (Continued)

## 6.4 Peripheral DMA Controller

- Transfers from/to peripheral to/from any memory space without intervention of the processor.

- Next Pointer Support, forbids strong real-time constraints on buffer management.

- Nineteen channels

- Two for each USART

- Two for the Debug Unit

- Two for each Serial Synchronous Controller

- Two for each Serial Peripheral Interface

- One for the Multimedia Card Interface

# 11.3 Application Examples

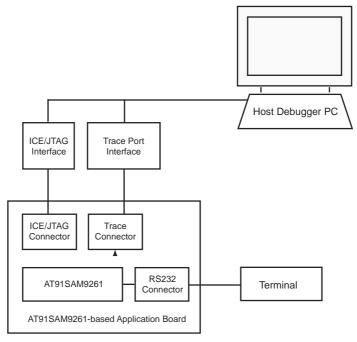

## 11.3.1 Debug Environment

Figure 11-2 shows a complete debug environment example. The ICE/JTAG interface is used for standard debugging functions, such as downloading code and single-stepping through the program. The Trace Port interface is used for tracing information. A software debugger running on a personal computer provides the user interface for configuring a Trace Port interface utilizing the ICE/JTAG interface.

## Figure 11-2. Application Debug and Trace Environment Example

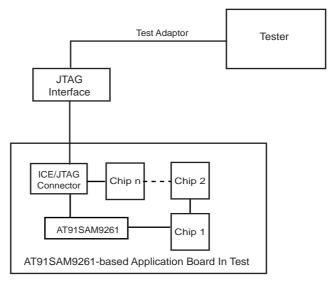

#### 11.3.2 Test Environment

Figure 11-3 shows a test environment example. Test vectors are sent and interpreted by the tester. In this example, the "board in test" is designed using a number of JTAG-compliant devices. These devices can be connected to form a single scan chain.

#### Figure 11-3. Application Test Environment Example

| Bit Number | Pin Name | Pin Type | Associated BSR Cells |

|------------|----------|----------|----------------------|

| 360        |          |          | INPUT                |

| 359        | PC25     | IN/OUT   | OUTPUT               |

| 358        |          | -        | CONTROL              |

| 357        |          | internal |                      |

| 356        |          |          | INPUT                |

| 355        | PC26     | IN/OUT   | OUTPUT               |

| 354        |          |          | CONTROL              |

| 353        |          | internal |                      |

| 352        |          |          | INPUT                |

| 351        | PC27     | IN/OUT   | OUTPUT               |

| 350        |          |          | CONTROL              |

| 349        |          | internal |                      |

| 348        |          |          | INPUT                |

| 347        | PC28     | IN/OUT   | OUTPUT               |

| 346        |          | -        | CONTROL              |

| 345        |          | internal |                      |

| 344        |          |          | INPUT                |

| 343        | PC29     | IN/OUT   | OUTPUT               |

| 342        |          |          | CONTROL              |

| 341        |          | internal |                      |

| 340        |          |          | INPUT                |

| 339        | PC0      | IN/OUT   | OUTPUT               |

| 338        |          | -        | CONTROL              |

| 337        |          | internal |                      |

| 336        |          |          | INPUT                |

| 335        | PC1      | IN/OUT   | OUTPUT               |

| 334        |          | -        | CONTROL              |

| 333        |          | internal |                      |

| 332        |          |          | INPUT                |

| 331        | PC2      | IN/OUT   | OUTPUT               |

| 330        |          |          | CONTROL              |

| 329        |          | internal |                      |

| 328        |          |          | INPUT                |

| 327        | PC3      | IN/OUT   | OUTPUT               |

| 326        |          |          | CONTROL              |

| 325        |          | internal |                      |

Table 11-3.

SAM9261 JTAG Boundary Scan Register (Continued)

## 16.6 Functional Description

The Shutdown Controller manages the main power supply. To do so, it is supplied with VDDBU and manages wakeup input pins and one output pin, SHDN.

A typical application connects the pin SHDN to the shutdown input of the DC/DC Converter providing the main power supplies of the system, and especially VDDCORE and/or VDDIO. The wakeup inputs (WKUP0) connect to any push-buttons or signal that wake up the system.

The software is able to control the pin SHDN by writing the Shutdown Control Register (SHDW\_CR) with the bit SHDW at 1. The shutdown is taken into account only 2 slow clock cycles after the write of SHDW\_CR. This register is password-protected and so the value written should contain the correct key for the command to be taken into account. As a result, the system should be powered down.

A level change on WKUP0 is used as wakeup. Wakeup is configured in the Shutdown Mode Register (SHDW\_MR). The transition detector can be programmed to detect either a positive or negative transition or any level change on WKUP0. The detection can also be disabled. Programming is performed by defining WKMODE0.

Moreover, a debouncing circuit can be programmed for WKUP0. The debouncing circuit filters pulses on WKUP0 shorter than the programmed number of 16 SLCK cycles in CPTWK0 of the SHDW\_MR. If the programmed level change is detected on a pin, a counter starts. When the counter reaches the value programmed in the corresponding field, CPTWK0, the SHDN pin is released. If a new input change is detected before the counter reaches the corresponding value, the counter is stopped and cleared. WAKEUP0 of the Status Register (SHDW\_SR) reports the detection of the programmed events on WKUP0 with a reset after the read of SHDW\_SR.

The Shutdown Controller can be programmed so as to activate the wakeup using the RTT alarm (the detection of the rising edge of the RTT alarm is synchronized with SLCK). This is done by writing the SHDW\_MR using the RTTWKEN fields. When enabled, the detection of the RTT alarm is reported in the RTTWK bit of the SHDW\_SR Status register. It is reset after the read of SHDW\_SR. When using the RTT alarm to wake up the system, the user must ensure that the RTT alarm status flag is cleared before shutting down the system. Otherwise, no rising edge of the status flag may be detected and the wakeup fails.

## 25.4 Functional Description

The Watchdog Timer can be used to prevent system lock-up if the software becomes trapped in a deadlock. It is supplied with VDDCORE. It restarts with initial values on processor reset.

The Watchdog is built around a 12-bit down counter, which is loaded with the value defined in the field WDV of the Mode Register (WDT\_MR). The Watchdog Timer uses the Slow Clock divided by 128 to establish the maximum Watchdog period to be 16 seconds (with a typical Slow Clock of 32.768 kHz).

After a Processor Reset, the value of WDV is 0xFFF, corresponding to the maximum value of the counter with the external reset generation enabled (field WDRSTEN at 1 after a Backup Reset). This means that a default Watchdog is running at reset, i.e., at powerup. The user must either disable it (by setting the WDDIS bit in WDT\_MR) if he does not expect to use it or must reprogram it to meet the maximum Watchdog period the application requires.

The Watchdog Mode Register (WDT\_MR) can be written only once. Only a processor reset resets it. Writing the WDT\_MR reloads the timer with the newly programmed mode parameters.

In normal operation, the user reloads the Watchdog at regular intervals before the timer underflow occurs, by writing the Control Register (WDT\_CR) with the bit WDRSTT to 1. The Watchdog counter is then immediately reloaded from WDT\_MR and restarted, and the Slow Clock 128 divider is reset and restarted. The WDT\_CR is write-protected. As a result, writing WDT\_CR without the correct hard-coded key has no effect. If an underflow does occur, the "wdt\_fault" signal to the Reset Controller is asserted if the bit WDRSTEN is set in the Mode Register (WDT\_MR). Moreover, the bit WDUNF is set in the Watchdog Status Register (WDT\_SR).

To prevent a software deadlock that continuously triggers the Watchdog, the reload of the Watchdog must occur while the Watchdog counter is within a window between 0 and WDD, WDD is defined in the WatchDog Mode Register WDT\_MR.

Any attempt to restart the Watchdog while the Watchdog counter is between WDV and WDD results in a Watchdog error, even if the Watchdog is disabled. The bit WDERR is updated in the WDT\_SR and the "wdt\_fault" signal to the Reset Controller is asserted.

Note that this feature can be disabled by programming a WDD value greater than or equal to the WDV value. In such a configuration, restarting the Watchdog Timer is permitted in the whole range [0; WDV] and does not generate an error. This is the default configuration on reset (the WDD and WDV values are equal).

The status bits WDUNF (Watchdog Underflow) and WDERR (Watchdog Error) trigger an interrupt, provided the bit WDFIEN is set in the mode register. The signal "wdt\_fault" to the reset controller causes a Watchdog reset if the WDRSTEN bit is set as already explained in the reset controller programmer Datasheet. In that case, the processor and the Watchdog Timer are reset, and the WDERR and WDUNF flags are reset.

If a reset is generated or if WDT\_SR is read, the status bits are reset, the interrupt is cleared, and the "wdt\_fault" signal to the reset controller is deasserted.

Writing the WDT\_MR reloads and restarts the down counter.

While the processor is in debug state or in idle mode, the counter may be stopped depending on the value programmed for the bits WDIDLEHLT and WDDBGHLT in the WDT\_MR.

Atmel

## 25.5.2 Watchdog Timer Mode Register

| Name:<br>Address: | WDT_MR<br>0xFFFFD44 |           |          |          |    |    |    |

|-------------------|---------------------|-----------|----------|----------|----|----|----|

| Access:           | Read-write Once     | е         |          |          |    |    |    |

| 31                | 30                  | 29        | 28       | 27       | 26 | 25 | 24 |

|                   |                     | WDIDLEHLT | WDDBGHLT |          | WI | DD |    |

| 23                | 22                  | 21        | 20<br>WI | 19<br>DD | 18 | 17 | 16 |

| 15                | 14                  | 13        | 12       | 11       | 10 | 9  | 8  |

| WDDIS             | WDRPROC             | WDRSTEN   | WDFIEN   |          | W  | DV |    |

| 7                 | 6                   | 5         | 4<br>WI  | 3<br>DV  | 2  | 1  | 0  |

### • WDV: Watchdog Counter Value

Defines the value loaded in the 12-bit Watchdog Counter.

## • WDFIEN: Watchdog Fault Interrupt Enable

- 0: A Watchdog fault (underflow or error) has no effect on interrupt.

- 1: A Watchdog fault (underflow or error) asserts interrupt.

### • WDRSTEN: Watchdog Reset Enable

- 0: A Watchdog fault (underflow or error) has no effect on the resets.

- 1: A Watchdog fault (underflow or error) triggers a Watchdog reset.

## WDRPROC: Watchdog Reset Processor

0: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates all resets.

1: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates the processor reset.

#### • WDD: Watchdog Delta Value

Defines the permitted range for reloading the Watchdog Timer.

If the Watchdog Timer value is less than or equal to WDD, writing WDT\_CR with WDRSTT = 1 restarts the timer. If the Watchdog Timer value is greater than WDD, writing WDT\_CR with WDRSTT = 1 causes a Watchdog error.

## • WDDBGHLT: Watchdog Debug Halt

0: The Watchdog runs when the processor is in debug state.

1: The Watchdog stops when the processor is in debug state.

## • WDIDLEHLT: Watchdog Idle Halt

- 0: The Watchdog runs when the system is in idle mode.

- 1: The Watchdog stops when the system is in idle state.

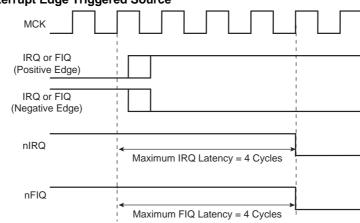

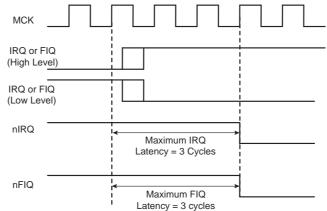

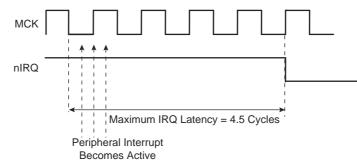

This section addresses only the hardware resynchronizations. It gives details of the latency times between the event on an external interrupt leading in a valid interrupt (edge or level) or the assertion of an internal interrupt source and the assertion of the nIRQ or nFIQ line on the processor. The resynchronization time depends on the programming of the interrupt source and on its type (internal or external). For the standard interrupt, resynchronization times are given assuming there is no higher priority in progress.

The PIO Controller multiplexing has no effect on the interrupt latencies of the external interrupt sources.

### 26.7.2.1 External Interrupt Edge Triggered Source

#### Figure 26-6. External Interrupt Edge Triggered Source

#### 26.7.2.2 External Interrupt Level Sensitive Source

Figure 26-7. External Interrupt Level Sensitive Source

#### 26.7.2.3 Internal Interrupt Edge Triggered Source

### Figure 26-8. Internal Interrupt Edge Triggered Source

## 26.8.18 AIC Fast Forcing Disable Register

| Name:    | AIC_FFDR   |       |       |       |       |       |       |  |  |

|----------|------------|-------|-------|-------|-------|-------|-------|--|--|

| Address: | 0xFFFF144  |       |       |       |       |       |       |  |  |

| Access:  | Write-only |       |       |       |       |       |       |  |  |

| 31       | 30         | 29    | 28    | 27    | 26    | 25    | 24    |  |  |

| PID31    | PID30      | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |  |  |

| 23       | 22         | 21    | 20    | 19    | 18    | 17    | 16    |  |  |

| PID23    | PID22      | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |  |  |

| 15       | 14         | 13    | 12    | 11    | 10    | 9     | 8     |  |  |

| PID15    | PID14      | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |  |  |

| 7        | 6          | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

| PID7     | PID6       | PID5  | PID4  | PID3  | PID2  | SYS   | —     |  |  |

## • SYS, PID2-PID31: Fast Forcing Disable

0: No effect.

1: Disables the Fast Forcing feature on the corresponding interrupt.

## 28.6.1 PIO Controller PIO Enable Register

Name: PIO\_PER

## Address: 0xFFFFF400 (PIOA), 0xFFFFF600 (PIOB), 0xFFFFF800 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: PIO Enable

0: No effect.

1: Enables the PIO to control the corresponding pin (disables peripheral control of the pin).

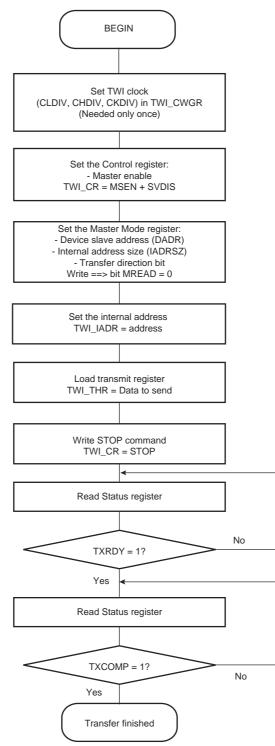

Figure 30-16. TWI Write Operation with Single Data Byte and Internal Address

Atmel

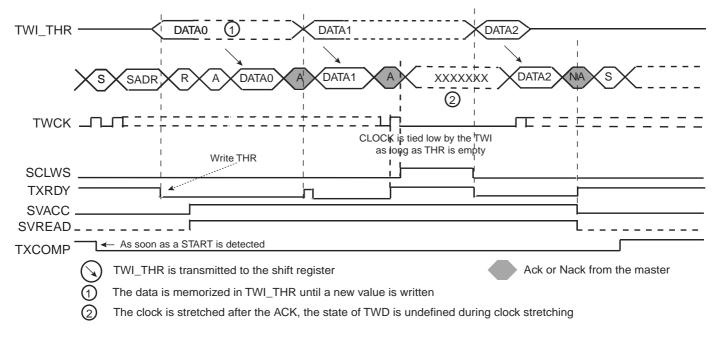

#### 30.10.5.4 Clock Synchronization

In both read and write modes, it may happen that TWI\_THR/TWI\_RHR buffer is not filled /emptied before the emission/reception of a new character. In this case, to avoid sending/receiving undesired data, a clock stretching mechanism is implemented.

#### **Clock Synchronization in Read Mode**

The clock is tied low if the shift register is empty and if a STOP or REPEATED START condition was not detected. It is tied low until the shift register is loaded.

Figure 30-28 describes the clock synchronization in Read mode.

#### Figure 30-28. Clock Synchronization in Read Mode

- Notes: 1. TXRDY is reset when data has been written in the TWI\_THR to the shift register and set when this data has been acknowledged or non acknowledged.

- 2. At the end of the read sequence, TXCOMP is set after a STOP or after a REPEATED\_START + an address different from SADR.

- 3. SCLWS is automatically set when the clock synchronization mechanism is started.

## 30.11.1 TWI Control Register

| Name:    | TWI_CR     |       |      |       |      |      |       |

|----------|------------|-------|------|-------|------|------|-------|

| Address: | 0xFFFAC000 |       |      |       |      |      |       |

| Access:  | Write-only |       |      |       |      |      |       |

| 31       | 30         | 29    | 28   | 27    | 26   | 25   | 24    |

| _        | —          | —     | —    | _     | _    | _    | —     |

|          | -          |       | -    |       |      |      |       |

| 23       | 22         | 21    | 20   | 19    | 18   | 17   | 16    |

| -        | -          | -     | -    | -     | -    | -    | -     |

|          | -          | -     | -    | -     |      | -    | -     |

| 15       | 14         | 13    | 12   | 11    | 10   | 9    | 8     |

| -        | -          | -     | -    | -     | -    | -    | -     |

|          |            |       |      |       |      |      |       |

| 7        | 6          | 5     | 4    | 3     | 2    | 1    | 0     |

| SWRST    | QUICK      | SVDIS | SVEN | MSDIS | MSEN | STOP | START |

### • START: Send a START Condition

0: No effect.

1: A frame beginning with a START bit is transmitted according to the features defined in the mode register.

This action is necessary when the TWI peripheral wants to read data from a slave. When configured in Master Mode with a write operation, a frame is sent as soon as the user writes a character in the Transmit Holding Register (TWI\_THR).

### • STOP: Send a STOP Condition

0: No effect.

1: STOP Condition is sent just after completing the current byte transmission in master read mode.

- In single data byte master read, the START and STOP must both be set.

- In multiple data bytes master read, the STOP must be set after the last data received but one.

- In master read mode, if a NACK bit is received, the STOP is automatically performed.

- In master data write operation, a STOP condition will be sent after the transmission of the current data is finished.

## MSEN: TWI Master Mode Enabled

0: No effect.

1: If MSDIS = 0, the master mode is enabled.

Note: Switching from Slave to Master mode is only permitted when TXCOMP = 1.

## MSDIS: TWI Master Mode Disabled

0: No effect.

1: The master mode is disabled, all pending data is transmitted. The shifter and holding characters (if it contains data) are transmitted in case of write operation. In read operation, the character being transferred must be completely received before disabling.

## SVEN: TWI Slave Mode Enabled

0: No effect.

1: If SVDIS = 0, the slave mode is enabled.

Note: Switching from Master to Slave mode is only permitted when TXCOMP = 1.

## • PAR: Parity Type

|   | 7 7   |   |                            |

|---|-------|---|----------------------------|

|   | Value |   | Parity Type                |

| 0 | 0     | 0 | Even parity                |

| 0 | 0     | 1 | Odd parity                 |

| 0 | 1     | 0 | Parity forced to 0 (Space) |

| 0 | 1     | 1 | Parity forced to 1 (Mark)  |

| 1 | 0     | х | No parity                  |

| 1 | 1     | х | Multidrop mode             |

### • NBSTOP: Number of Stop Bits

| Va | lue | Asynchronous (SYNC = 0) | Synchronous (SYNC = 1) |  |

|----|-----|-------------------------|------------------------|--|

| 0  | 0   | 1 stop bit              | 1 stop bit             |  |

| 0  | 1   | 1.5 stop bits           | Reserved               |  |

| 1  | 0   | 2 stop bits             | 2 stop bits            |  |

| 1  | 1   | Reserved                | Reserved               |  |

#### • CHMODE: Channel Mode

| Value |   | Mode Description                                                       |

|-------|---|------------------------------------------------------------------------|

| 0     | 0 | Normal Mode                                                            |

| 0     | 1 | Automatic Echo. Receiver input is connected to the TXD pin.            |

| 1     | 0 | Local Loopback. Transmitter output is connected to the Receiver Input. |

| 1     | 1 | Remote Loopback. RXD pin is internally connected to the TXD pin.       |

## • MSBF: Bit Order

0: Least Significant Bit is sent/received first.

1: Most Significant Bit is sent/received first.

#### • MODE9: 9-bit Character Length

0: CHRL defines character length.

1: 9-bit character length.

## CLKO: Clock Output Select

0: The USART does not drive the SCK pin.

1: The USART drives the SCK pin if USCLKS does not select the external clock SCK.

### OVER: Oversampling Mode

0: 16x Oversampling.

1: 8x Oversampling.

#### INACK: Inhibit Non Acknowledge

0: The NACK is generated.

1: The NACK is not generated.

## 32.8.14 SSC Interrupt Enable Register

| Name:    | SSC_IER                                        |       |       |        |       |         |       |  |  |

|----------|------------------------------------------------|-------|-------|--------|-------|---------|-------|--|--|

| Address: | 0xFFFBC044 (0), 0xFFFC0044 (1), 0xFFFC4044 (2) |       |       |        |       |         |       |  |  |

| Access:  | Write-only                                     |       |       |        |       |         |       |  |  |

| 31       | 30                                             | 29    | 28    | 27     | 26    | 25      | 24    |  |  |

| -        | -                                              | -     | -     | -      | -     | -       | —     |  |  |

| 23       | 22                                             | 21    | 20    | 19     | 18    | 17      | 16    |  |  |

| -        | -                                              | -     | -     | -      | -     | -       | -     |  |  |

| 15       | 14                                             | 13    | 12    | 11     | 10    | 9       | 8     |  |  |

| -        | -                                              | -     | -     | RXSYN  | TXSYN | CP1     | CP0   |  |  |

| 7        | 6                                              | 5     | 4     | 3      | 2     | 1       | 0     |  |  |

| RXBUFF   | ENDRX                                          | OVRUN | RXRDY | TXBUFE | ENDTX | TXEMPTY | TXRDY |  |  |

### • TXRDY: Transmit Ready Interrupt Enable

0: 0: No effect.

1: Enables the Transmit Ready Interrupt.

### • TXEMPTY: Transmit Empty Interrupt Enable

0: No effect.

1: Enables the Transmit Empty Interrupt.

## • ENDTX: End of Transmission Interrupt Enable

- 0: No effect.

- 1: Enables the End of Transmission Interrupt.

## • TXBUFE: Transmit Buffer Empty Interrupt Enable

0: No effect.

1: Enables the Transmit Buffer Empty Interrupt

#### • RXRDY: Receive Ready Interrupt Enable

0: No effect.

1: Enables the Receive Ready Interrupt.

## OVRUN: Receive Overrun Interrupt Enable

0: No effect.

1: Enables the Receive Overrun Interrupt.

## • ENDRX: End of Reception Interrupt Enable

- 0: No effect.

- 1: Enables the End of Reception Interrupt.

## 33.7.5 TC Channel Mode Register: Waveform Mode

**Name:** TC\_CMRx [x=0..2] (WAVE = 1)

## Address: 0xFFFA0004 (0)[0], 0xFFFA0044 (0)[1], 0xFFFA0084 (0)[2]

Access: Read/Write

| 31     | 30      | 29    | 28     | 27   | 26   | 25      | 24 |

|--------|---------|-------|--------|------|------|---------|----|

| BSV    | BSWTRG  |       | BEEVT  |      | BCPC |         | PB |

| 23     | 22      | 21    | 20     | 19   | 18   | 17      | 16 |

| ASV    | /TRG    | AEEVT |        | ACPC |      | ACPA    |    |

| 15     | 14      | 13    | 12     | 11   | 10   | 9       | 8  |

| WAVE   | WAV     | 'SEL  | ENETRG | EEVT |      | EEVTEDG |    |

| 7      | 6       | 5     | 4      | 3    | 2    | 1       | 0  |

| CPCDIS | CPCSTOP | BURST |        | CLKI |      | TCCLKS  |    |

|        |         |       |        |      |      |         |    |

## • TCCLKS: Clock Selection

| TCCLKS |   | ĸs | Clock Selected |

|--------|---|----|----------------|

| 0      | 0 | 0  | TIMER_CLOCK1   |

| 0      | 0 | 1  | TIMER_CLOCK2   |

| 0      | 1 | 0  | TIMER_CLOCK3   |

| 0      | 1 | 1  | TIMER_CLOCK4   |

| 1      | 0 | 0  | TIMER_CLOCK5   |

| 1      | 0 | 1  | XC0            |

| 1      | 1 | 0  | XC1            |

| 1      | 1 | 1  | XC2            |

## • CLKI: Clock Invert

0: Counter is incremented on rising edge of the clock.

1: Counter is incremented on falling edge of the clock.

### • BURST: Burst Signal Selection

| Value |   | Description                                   |  |  |  |  |

|-------|---|-----------------------------------------------|--|--|--|--|

| 0     | 0 | The clock is not gated by an external signal. |  |  |  |  |

| 0     | 1 | XC0 is ANDed with the selected clock.         |  |  |  |  |

| 1     | 0 | XC1 is ANDed with the selected clock.         |  |  |  |  |

| 1     | 1 | XC2 is ANDed with the selected clock.         |  |  |  |  |

## • CPCSTOP: Counter Clock Stopped with RC Compare

0: Counter clock is not stopped when counter reaches RC.

1: Counter clock is stopped when counter reaches RC.

## • CPCDIS: Counter Clock Disable with RC Compare

- 0: Counter clock is not disabled when counter reaches RC.

- 1: Counter clock is disabled when counter reaches RC.

## 34.10.9 MCI Transmit Data Register

| Name:    | MCI_TDR    |    |    |    |    |    |    |  |  |

|----------|------------|----|----|----|----|----|----|--|--|

| Address: | 0xFFFA8034 |    |    |    |    |    |    |  |  |

| Access:  | Write-only |    |    |    |    |    |    |  |  |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|          | DATA       |    |    |    |    |    |    |  |  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|          | DATA       |    |    |    |    |    |    |  |  |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|          | DATA       |    |    |    |    |    |    |  |  |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|          | DATA       |    |    |    |    |    |    |  |  |

• DATA: Data to Write

Atmel

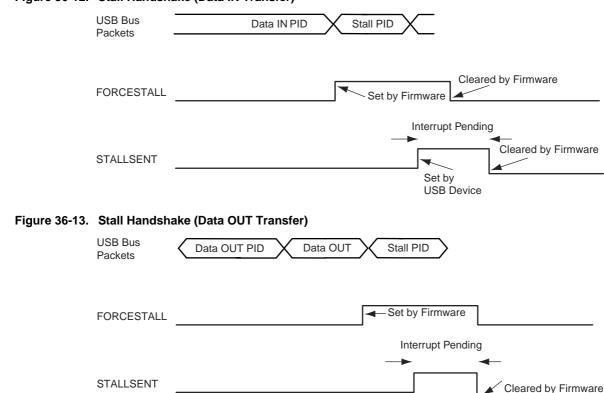

#### Figure 36-12. Stall Handshake (Data IN Transfer)

#### STALLSENT

## Set by USB Device

#### 36.6.2.9 Transmit Data Cancellation

Some endpoints have dual-banks whereas some endpoints have only one bank. The procedure to cancel transmission data held in these banks is described below.

To see the organization of dual-bank availability refer to Table 36-1 "USB Endpoint Description".

#### 36.6.2.10Endpoints Without Dual-Banks

There are two possibilities: In one case, TXPKTRDY field in UDP\_CSR has already been set. In the other instance, TXPKTRDY is not set.

- TXPKTRDY is not set:

- Reset the endpoint to clear the FIFO (pointers). (See Section 36.7.9 "UDP Reset Endpoint Register".)

- TXPKTRDY has already been set:

- Clear TXPKTRDY so that no packet is ready to be sent \_

- Reset the endpoint to clear the FIFO (pointers). (See Section 36.7.9 "UDP Reset Endpoint Register".) \_

#### 36.6.2.11Endpoints With Dual-Banks

There are two possibilities: In one case, TXPKTRDY field in UDP\_CSR has already been set. In the other instance, TXPKTRDY is not set.

- TXPKTRDY is not set: .

- Reset the endpoint to clear the FIFO (pointers). (See Section 36.7.9 "UDP Reset Endpoint Register".) \_

- TXPKTRDY has already been set:

- Clear TXPKTRDY and read it back until actually read at 0.

- Set TXPKTRDY and read it back until actually read at 1. \_

- Clear TXPKTRDY so that no packet is ready to be sent.

- Reset the endpoint to clear the FIFO (pointers). (See Section 36.7.9 "UDP Reset Endpoint Register".)

## 37.10.27 LCD Interrupt Disable Register

| Name:    | LCD_IDR    |       |        |    |       |         |      |

|----------|------------|-------|--------|----|-------|---------|------|

| Address: | 0x0060084C |       |        |    |       |         |      |

| Access:  | Write-only |       |        |    |       |         |      |

| 31       | 30         | 29    | 28     | 27 | 26    | 25      | 24   |

| -        | -          | _     | _      | _  | _     | -       | _    |

| 23       | 22         | 21    | 20     | 19 | 18    | 17      | 16   |

| -        | -          | -     | -      | -  | -     | -       | -    |

| 15       | 14         | 13    | 12     | 11 | 10    | 9       | 8    |

| -        | -          | -     | -      | -  | -     | -       | -    |

| 7        | 6          | 5     | 4      | 3  | 2     | 1       | 0    |

| -        | MERID      | OWRID | UFLWID | -  | EOFID | LSTLNID | LNID |

### • LNID: Line interrupt disable

- 0: No effect

- 1: Disable each line interrupt

## • LSTLNID: Last line interrupt disable

- 0: No effect

- 1: Disable last line interrupt

## • EOFID: DMA End of frame interrupt disable

- 0: No effect

- 1: Disable End Of Frame interrupt

## • UFLWID: FIFO underflow interrupt disable

- 0: No effect

- 1: Disable FIFO underflow interrupt

## • OWRID: FIFO overwrite interrupt disable

- 0: No effect

- 1: Disable FIFO overwrite interrupt

## • MERID: DMA Memory error interrupt disable

- 0: No effect

- 1: Disable DMA Memory error interrupt

#### 42.1.10.4 SPI: Chip Select and fixed mode

In FIXED Mode, if a transfer is performed through a PDC on a Chip Select different from the Chip Select 0, the output spi\_size sampled by the PDC will depend on the field SPI\_CSR0.BITS, whatever the selected Chip Select is. For example if SPI\_CSR0 is configured for a 10-bit transfer whereas the SPI\_CSR1 is configured for an 8-bit transfer, when a transfer is performed in Fixed mode through the PDC on Chip Select 1, the transfer is considered as a halfword transfer.

## **Problem Fix/Workaround**

If a PDC transfer has to be performed in 8 bits, on a Chip select y (y different from 0), the field SPI\_CSR0.BITS must be configured in 8 bits in the same way as the field BITS of the CSRy Register.

### 42.1.10.5 SPI: Baud rate set to 1

When SPI\_CSRx.SCBR (baud rate) = 1 (i.e., when serial clock frequency equals the system clock frequency), and when the field BITS (number of bits to be transmitted) equals an ODD value (in this case 9, 11, 13 or 15), an additional pulse is generated on output SPCK. No problem occurs if BITS field equals 8, 10, 12, 14 or 16 and SCBR (baud rate) = 1.

### Problem Fix/Workaround

None.

## 42.1.10.6 SPI: Software Reset

If the Software reset command is performed at the same clock cycle as an event for TXRDY occurs, there is no reset.

### **Problem Fix/Workaround**

Perform another software reset.

### 42.1.10.7 SPI: Software Reset Must be Written Twice

If a software reset (SWRST in the SPI Control Register) is performed, the SPI may not work properly (the clock is enabled before the chip select).

#### Problem Fix/Workaround

The field SPI\_CR.SWRST needs to be written twice to be correctly set.

#### 42.1.10.8 SPI: Bad Serial Clock Generation on 2nd Chip Select

Bad Serial clock generation on the 2nd chip select when SSPI\_CSRx.SCBR = 1, SPI\_CSRx.CPOL = 1 and SPI\_CSRx.NCPHA = 0.

This occurs using SPI with the following conditions:

- Master Mode

- CPOL = 1 and NCPHA = 0

- Multiple chip selects are used with one transfer with SCBR (baud rate) = 1 (i.e., when serial clock frequency equals the system clock frequency) and the other transfers set with SCBR are not equal to 1.

- Transmitting with the slowest chip select and then with the fastest one, then an additional pulse is generated on output SPCK during the second transfer.

#### **Problem Fix/Workaround**

Do not use a multiple Chip Select configuration where at least one SPI\_CSRx is configured with SCBR = 1 and the others differ from 1 if NCPHA = 0 and CPOL = 1.

If all chip selects are configured with SCBR (baud rate) = 1, the issue does not appear.