# E·XFL

## NXP USA Inc. - MPC8315CVRAFDA Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                 |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 333MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (2)                                                         |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 620-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 620-HBGA (29x29)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8315cvrafda |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

# 1 Overview

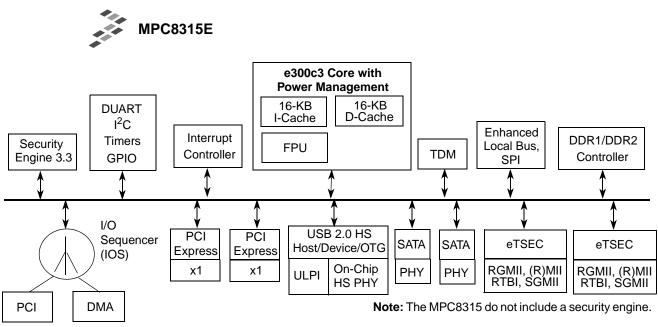

The MPC8315E incorporates the e300c3 (MPC603e-based) core, which includes 16 Kbytes of L1 instruction and data caches, on-chip memory management units (MMUs), and floating-point support. In addition to the e300 core, the SoC platform includes features such as dual enhanced three-speed 10, 100, 1000 Mbps Ethernet controllers (eTSECs) with SGMII support, a 32- or 16-bit DDR1/DDR2 SDRAM memory controller, dual SATA 3 Gbps controllers (MPC8315E-specific), a security engine to accelerate control and data plane security protocols, and a high degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration. The MPC8315E also offers peripheral interfaces such as a 32-bit PCI interface with up to 66 MHz operation, 16-bit enhanced local bus interface with up to 66 MHz operation, TDM interface, and USB 2.0 with an on-chip USB 2.0 PHY.

The MPC8315E offers additional high-speed interconnect support with dual integrated SATA 3 Gbps interfaces and dual single-lane PCI Express interfaces. When not used for PCI Express, the SerDes interface may be configured to support SGMII. The MPC8315E security engine (SEC 3.3) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. This figure shows a block diagram of the MPC8315E.

Figure 1. MPC8315E Block Diagram

# 2 MPC8315E Features

The following features are supported in the MPC8315E.

# 2.1 e300 Core

The e300 core has the following features:

• Operates at up to 400 MHz

- 16-Kbyte instruction cache, 16-Kbyte data cache

- One floating point unit and two integer units

- Software-compatible with the Freescale processor families implementing the PowerPC Architecture

- Performance monitor

## 2.2 Serial Interfaces

The following interfaces are supported in the MPC8315E.

- Two enhanced TSECs (eTSECs)

- Two Ethernet interfaces using one RGMII/MII/RMII/RTBI or SGMII (no GMII)

- Dual UART, one I<sup>2</sup>C, and one SPI interface

## 2.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, 802.11i, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are:

- Public key execution unit (PKEU)

- RSA and Diffie-Hellman (to 4096 bits)

- Programmable field size up to 2048 bits

- Elliptic curve cryptography (1023 bits)

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB, CBC, CFB-64 and OFB-64 modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rinjdael symmetric key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, CTR, GCM, CMAC, OFB, CFB, XCBC-MAC and LRW modes

- XOR acceleration

- Message digest execution unit (MDEU)

- SHA with 160-bit, 256-bit, 384-bit and 512-bit message digest

- SHA-384/512

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

|                 | Characteristic                                                                                        | Symbol           | Max Value            | Unit             | Note |

|-----------------|-------------------------------------------------------------------------------------------------------|------------------|----------------------|------------------|------|

| Input voltage   | DDR DRAM signals                                                                                      | MV <sub>IN</sub> | -0.3 to (GVDD + 0.3) | V<br>V<br>V<br>V | 2, 4 |

|                 | DDR DRAM reference                                                                                    | MVREF            | -0.3 to (GVDD + 0.3) | V                | 2, 4 |

|                 | eTSEC signals                                                                                         | LV <sub>IN</sub> | -0.3 to (LVDD + 0.3) | V                | 3, 4 |

|                 | Local bus, DUART, SYS_CLK_IN, system control and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub> | -0.3 to (NVDD + 0.3) | V                | 3, 4 |

|                 | PCI                                                                                                   | NV <sub>IN</sub> | -0.3 to (NVDD + 0.3) | V                | 5    |

|                 | SATA_CLKIN                                                                                            | NV <sub>IN</sub> | -0.3 to (NVDD + 0.3) | V                | 3, 4 |

| Storage tempera | ature range                                                                                           | T <sub>STG</sub> | -55 to150            | °C               | _    |

Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

Note:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution: MV<sub>IN</sub> must not exceed GVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** (N,L)V<sub>IN</sub> must not exceed (N,L)VDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. (M,N,L)V<sub>IN</sub> and MVREF may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

- 5. NV<sub>IN</sub> on the PCI interface may overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 2.

- 6. The max value of supply voltage should be selected based on the RGMII mode.

- 7. NVDD means NVDD1\_OFF, NVDD1\_ON, NVDD2\_OFF, NVDD2\_ON, NVDD3\_OFF, NVDD4\_OFF

- 8. LVDD means LVDD1\_OFF and LVDD2\_ON

## 3.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for theMPC8315E. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                           | Symbol        | Recommended<br>Value <sup>1</sup> | Unit | Status in D3<br>Warm mode | Note |

|------------------------------------------|---------------|-----------------------------------|------|---------------------------|------|

| SerDes internal digital power            | XCOREVDD      | 1.0 ± 50 mv                       | V    | Switched Off              |      |

| SerDes internal digital power            | XCOREVSS      | 0.0                               | V    | _                         | —    |

| SerDes I/O digital power                 | XPADVDD       | 1.0 ± 50 mv                       | V    | Switched Off              |      |

| SerDes I/O digital power                 | XPADVSS       | 0.0                               | V    | _                         | —    |

| SerDes analog power for PLL              | SDAVDD        | 1.0 ± 50 mv                       | V    | Switched Off              |      |

| SerDes analog power for PLL              | SDAVSS        | 0.0                               | V    | _                         |      |

| Dedicated 3.3 V analog power for USB PLL | USB_PLL_PWR3  | 3.3 ± 165mv                       | V    | Switched Off              |      |

| Dedicated 1.0 Vanalog power for USB PLL  | USB_PLL_PWR1  | 1.0 ± 50 mv                       | V    | Switched Off              |      |

| Dedicated analog ground for USB PLL      | USB_PLL_GND   | 0.0                               | V    | _                         |      |

| Dedicated USB power for USB bias circuit | USB_VDDA_BIAS | 3.3 ± 300 mv                      | V    | Switched Off              |      |

**Table 2. Recommended Operating Conditions**

| Driver Type                                       | Output<br>Impedance (Ω) | Supply<br>Voltage    |

|---------------------------------------------------|-------------------------|----------------------|

| DUART, system control, I <sup>2</sup> C, JTAG,SPI | 42                      | NVDD = 3.3 V         |

| GPIO signals                                      | 42                      | NVDD = 3.3 V         |

| eTSEC                                             | 42                      | LVDD = 3.3 V / 2.5 V |

<sup>1</sup> Output Impedance can also be adjusted through configurable options in DDR Control Driver Register (DDRCDR). See the MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

## 3.2 Power Sequencing

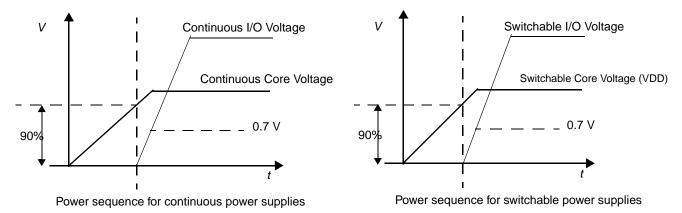

The MPC8315E does not require the core supply voltage (VDD and VDDC) and I/O supply voltages (GVDD, LVDDx\_ON, LVDDx\_OFF, NVDDx\_ON and NVDDx\_OFF) to be applied in any particular order. During the power ramp up, before the power supplies are stable, if the I/O voltages are supplied before the core voltage, there may be a period of time when all input and output pins be actively driven and cause contention and/or excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the continuous core voltage (VDDC) before the continuous I/O voltages (LVDDx\_ON and NVDDx\_ON) and switchable core voltage (VDD) before the switchable I/O voltages (GVDD, LVDDx\_OFF, and NVDDx\_OFF). PORESET should be asserted before the continuous power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V, see Figure 3. Once all the power supplies are stable, wait for a minimum of 32 clock cycles before negating PORESET.

The I/O power supply ramp-up slew rate should be slower than  $4V/100 \ \mu s$ , this requirement is for ESD circuit.

This figure shows the power-up sequencing for switchable and continuous supplies.

### Figure 3. Power-Up Sequencing

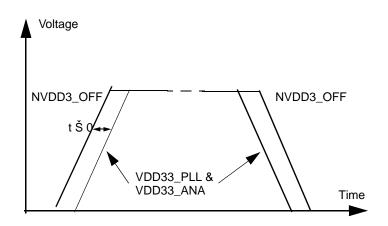

When switching from normal mode to D3 warm (standby) mode, first turn off the switchable I/O voltage supply and then turn off the switchable core voltage supply. Similarly, when switching from D3 warm (standby) mode to normal mode, first turn on the switchable core voltage supply and then turn on the switchable I/O voltage supply.

This figure shows the SATA power supplies.

**Figure 5. SATA Power Supplies**

# 4 **Power Characteristics**

This table shows the estimated typical power dissipation for this family of devices.

#### Table 4. MPC8315E Power Dissipation

(Does not include I/O power dissipation)

| Core Frequency (MHz) | CSB Frequency (MHz) | Typical <sup>1,3</sup> | Maximum <sup>1,2</sup> | Unit |

|----------------------|---------------------|------------------------|------------------------|------|

| 266                  | 133                 | 1.116                  | 1.646                  | W    |

| 333                  | 133                 | 1.142                  | 1.665                  | W    |

| 400                  | 133                 | 1.167                  | 1.690                  | W    |

Note:

1. The values do not include I/O supply power, but do include core, AVDD, USB PLL, digital SerDes power, and SATA PHY power.

- 2. Maximum power is based on a voltage of  $V_{dd}$  = 1.05V, a junction temperature of  $T_j$  = 105°C, and an artificial smoker test.

- 3. Typical power is based on a voltage of  $V_{dd}$  = 1.05V, and an artificial smoker test running at room temperature.

This table shows the estimated typical I/O power dissipation for this family of devices.

Table 5. MPC8315E Power Dissipation

| Interface         | Frequency          | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LVDD1_OFF/<br>LVDD2_ON<br>(3.3V) | LVDD2<br>_ON<br>(3.3V) | VDD33PLL,<br>VDD33ANA<br>(3.3V) | SATA_VDD,<br>VDD1IO,<br>VDD1ANA<br>(1.0V) | XCOREVDD,<br>XPADVDD,<br>SDAVDD<br>(1.0V) | Unit |

|-------------------|--------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------------|------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|------|

| DDR 1<br>Rs = 22Ω | 266MHz,<br>32 bits | —                           | 0.323                       | —                           | —                                | _                      | —                               | _                                         | -                                         | W    |

| Rt = 50Ω          | 200MHz,<br>32 bits | —                           | 0.291                       | —                           | —                                | _                      | —                               | _                                         | -                                         | W    |

NP

DDR and DDR2 SDRAM

### Table 9. RESET Initialization Timing Specifications (continued)

#### Note:

- 1. t<sub>PCL\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the SYS\_CLK\_IN input, and PCI\_SYNC\_IN period depends on the value of CFG\_SYS\_CLKIN\_DIV.

- 2. t<sub>SYS\_CLK\_IN</sub> is the clock period of the input clock applied to SYS\_CLK\_IN. It is only valid when the device is in PCI host mode.

- 3. POR configuration signals consists of CFG\_RESET\_SOURCE[0:3] and CFG\_SYS\_CLKIN\_DIV.

- 4. The parameter names CFG\_SYS\_CLKIN\_DIV and CFG\_CLKIN\_DIV are used interchangeably in this document.

This table provides the PLL lock times.

Table 10. PLL Lock Times

| Parameter/Condition                       | Min | Max | Unit | Note |

|-------------------------------------------|-----|-----|------|------|

| System PLL lock times                     | —   | 100 | μS   | —    |

| e300 core PLL lock times                  | —   | 100 | μS   | —    |

| SerDes (SGMII/PCI Exp Phy) PLL lock times | —   | 100 | μs   | —    |

| USB phy PLL lock times                    | —   | 100 | μS   | —    |

| SATA phy PLL lock times                   | —   | 100 | μs   | —    |

# 7 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the MPC8315E. Note that DDR SDRAM is GVDD(typ) = 2.5 V and DDR2 SDRAM is GVDD(typ) = 1.8 V.

# 7.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8315E when GVDD(typ) = 1.8 V.

| Parameter/Condition                                             | Symbol          | Min                       | Мах                | Unit | Note |

|-----------------------------------------------------------------|-----------------|---------------------------|--------------------|------|------|

| I/O supply voltage                                              | GVDD            | 1.7                       | 1.9                | V    | 1    |

| I/O reference voltage                                           | MVREF           | $0.49 \times \text{GVDD}$ | $0.51 \times GVDD$ | V    | 2    |

| I/O termination voltage                                         | V <sub>TT</sub> | MVREF – 0.04              | MVREF + 0.04       | V    | 3    |

| Input high voltage                                              | V <sub>IH</sub> | MVREF+ 0.125              | GVDD + 0.3         | V    | —    |

| Input low voltage                                               | V <sub>IL</sub> | -0.3                      | MVREF - 0.125      | V    | —    |

| Output leakage current                                          | I <sub>OZ</sub> | -9.9                      | 9.9                | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V,<br>GVDD= 1.7V) | I <sub>OH</sub> | -13.4                     | —                  | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)                 | I <sub>OL</sub> | 13.4                      | —                  | mA   |      |

Table 11. DDR2 SDRAM DC Electrical Characteristics for GVDD(typ) = 1.8 V

Ethernet: Three-Speed Ethernet, MII Management

## 9.2.2 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 9.2.2.1 RMII Transmit AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications. This table provides the RMII transmit AC timing specifications.

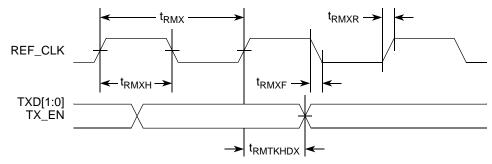

### Table 27. RMII Transmit AC Timing Specifications

At recommended operating conditions with LVDD of 3.3 V  $\pm$  300 mv

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock                                          | t <sub>RMX</sub>                    | _   | 20  | —   | ns   |

| REF_CLK duty cycle                                     | t <sub>RMXH/</sub> t <sub>RMX</sub> | 35  | _   | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay             | t <sub>RMTKHDX</sub>                | 2   | _   | 10  | ns   |

| REF_CLK data clock rise VIL(min) to VIH(max)           | t <sub>RMXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>RMXF</sub>                   | 1.0 |     | 4.0 | ns   |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state) (reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

This figure shows the RMII transmit AC timing diagram.

Figure 13. RMII Transmit AC Timing Diagram

## 9.2.2.2 RMII Receive AC Timing Specifications

This table provides the RMII receive AC timing specifications.

### Table 28. RMII Receive AC Timing Specifications

At recommended operating conditions with LVDD of 3.3 V  $\pm$  300 mv

| Parameter/Condition  | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|----------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock period | t <sub>RMX</sub>                    | _   | 20  | _   | ns   |

| REF_CLK duty cycle   | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _   | 65  | %    |

#### Ethernet: Three-Speed Ethernet, MII Management

#### Table 30. MII Management DC Electrical Characteristics Powered at 3.3 V (continued)

| Parameter         | Symbol          | Conditions |                  | Min  | Max | Unit |

|-------------------|-----------------|------------|------------------|------|-----|------|

| Input low current | ۱ <sub>IL</sub> | NVDD = Max | $V_{IN} = 0.5 V$ | -600 | _   | μA   |

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $NV_{IN}$  symbol referenced in Table 1 and Table 2.

## 9.3.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

#### Table 31. MII Management AC Timing Specifications

At recommended operating conditions with NVDD is 3.3 V ± 300 mv

| Parameter/Condition        | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Note |

|----------------------------|---------------------|-----|-----|-----|------|------|

| MDC frequency              | f <sub>MDC</sub>    | —   | 2.5 | —   | MHz  | 2    |

| MDC period                 | t <sub>MDC</sub>    | —   | 400 | —   | ns   | —    |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32  | —   | —   | ns   | —    |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10  | —   | 170 | ns   | 3    |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5   | —   | —   | ns   | —    |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0   | —   | —   | ns   | —    |

| MDC rise time              | t <sub>MDCR</sub>   | —   | —   | 10  | ns   | —    |

| MDC fall time              | t <sub>MDHF</sub>   | —   |     | 10  | ns   | —    |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. This parameter is dependent on the csb\_clk speed (that is, for a csb\_clk of 133 MHz, the maximum frequency is 4.16 MHz and the minimum frequency is 0.593 MHz).

3. This parameter is dependent on the csb\_clk speed (that is, for a csb\_clk of 133 MHz, the delay is 60 ns).

## 12.2 JTAG AC Timing Specifications

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface. This table provides the JTAG AC timing specifications as defined in Figure 29 through Figure 32.

## Table 46. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN)<sup>1</sup>

At recommended operating conditions (see Table 2)

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Note |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —    |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       | —        | ns   | —    |

| JTAG external clock pulse width measured at 1.4 V                          | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —    |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | —    |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       | —        | ns   | 3    |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>tJTIVKH             | 4<br>4   |          | ns   | 4    |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 | _        | ns   | 4    |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 2<br>2   | 11<br>11 | ns   | 5    |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 2<br>2   |          | ns   | 5    |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 2<br>2   | 19<br>9  | ns   | 5, 6 |

Note:

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Table 28). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design and characterization.

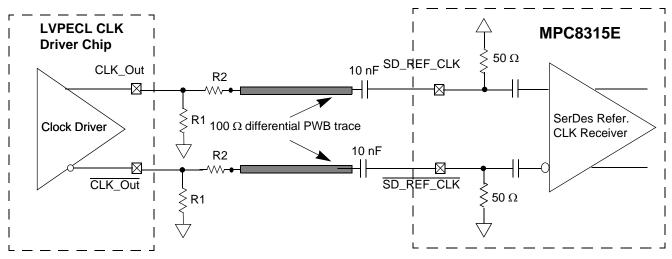

#### High-Speed Serial Interfaces (HSSI)

assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8315E SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 =  $25\Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

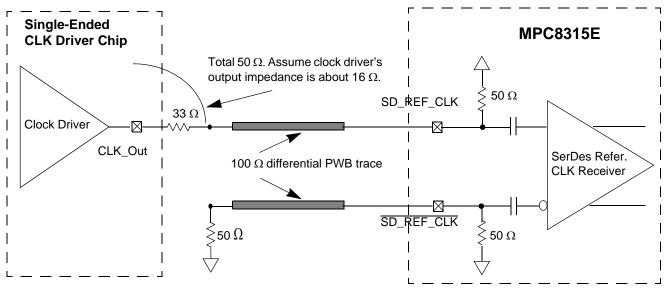

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8315E SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

Timers

# 17.3 Out-of-Band (OOB) Electrical Characteristics

This table provides the out-of-band (OOB) electrical characteristics for the SATA interface of the MPC8315.

| Parameter                                              | Symbol                               | Min      | Typical    | Max        | Units | Note |

|--------------------------------------------------------|--------------------------------------|----------|------------|------------|-------|------|

| OOB Signal Detection Threshold<br>1.5G                 |                                      |          |            |            |       |      |

| 3.0G                                                   | V <sub>SATA_OOBDETE</sub>            | 50<br>75 | 100<br>125 | 200<br>200 | mVp-p |      |

| UI During OOB Signaling                                | T <sub>SATA_UIOOB</sub>              | _        | 666.67     | —          | ps    |      |

| COMINIT/ COMRESET and<br>COMWAKE Transmit Burst Length | T <sub>SATA_UIOOBTXB</sub>           |          | 160        | _          | UI    |      |

| COMINIT/COMRESET Transmit Gap<br>Length                | T <sub>SATA_UIOOBTXGap</sub>         |          | 480        | _          | UI    | _    |

| COMWAKE Transmit Gap Length                            | T <sub>SATA_UIOOBTX</sub><br>WakeGap |          | 160        | _          | UI    | _    |

## Table 59. Out-of-Band (OOB) Electrical Characteristics

# 18 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8315E.

# **18.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the timers pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Table 60. Timers DC Electrical Characte | eristics |

|-----------------------------------------|----------|

|-----------------------------------------|----------|

| Characteristic      | Symbol          | Condition                                   | Min  | Max        | Unit |

|---------------------|-----------------|---------------------------------------------|------|------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA                   | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                    | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                    | _    | 0.4        | V    |

| Input high voltage  | V <sub>IH</sub> | —                                           | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                           | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq V_{IN} \leq N \text{VDD}$ | _    | ± 5        | μA   |

# **18.2 Timers AC Timing Specifications**

This table provides the timers input and output AC timing specifications.

Table 61. Timers Input AC Timing Specifications

| Characteristic                    | Symbol <sup>1</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

IPIC

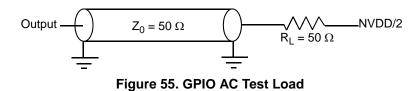

This figure provides the AC test load for the GPIO.

# 20 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins of the MPC8315E.

# 20.1 IPIC DC Electrical Characteristics

This table provides the DC electrical characteristics for the external interrupt pins.

| Characteristic      | Symbol          | Condition                 | Min  | Max        | Unit |

|---------------------|-----------------|---------------------------|------|------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | —                         | _    | ±5         | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4        | V    |

## Table 64. IPIC DC Electrical Characteristics

# 20.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

## Table 65. IPIC Input AC Timing Specifications

| Characteristic                  | Symbol <sup>1</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

# 21 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8315E.

| Signal       | Package Pin Number | Pin Type | Power<br>Supply | Note |

|--------------|--------------------|----------|-----------------|------|

| MEMC_MDM3    | AF6                | 0        | GVDD            | -    |

| MEMC_MDQS[0] | AF17               | I/O      | GVDD            | —    |

| MEMC_MDQS[1] | AG21               | I/O      | GVDD            | —    |

| MEMC_MDQS[2] | AG9                | I/O      | GVDD            | _    |

| MEMC_MDQS[3] | AF7                | I/O      | GVDD            | _    |

| MEMC_MBA[0]  | AH16               | 0        | GVDD            | —    |

| MEMC_MBA[1]  | AH15               | 0        | GVDD            | —    |

| MEMC_MBA[2]  | AG15               | 0        | GVDD            | —    |

| MEMC_MA0     | AD15               | 0        | GVDD            | —    |

| MEMC_MA1     | AE15               | 0        | GVDD            | —    |

| MEMC_MA2     | AH14               | 0        | GVDD            | —    |

| MEMC_MA3     | AG14               | 0        | GVDD            | —    |

| MEMC_MA4     | AF14               | 0        | GVDD            | —    |

| MEMC_MA5     | AE14               | 0        | GVDD            | —    |

| MEMC_MA6     | AH13               | 0        | GVDD            | —    |

| MEMC_MA7     | AH12               | 0        | GVDD            | —    |

| MEMC_MA8     | AF13               | 0        | GVDD            | —    |

| MEMC_MA9     | AD13               | 0        | GVDD            | —    |

| MEMC_MA10    | AG12               | 0        | GVDD            | —    |

| MEMC_MA11    | AH11               | 0        | GVDD            | —    |

| MEMC_MA12    | AH10               | 0        | GVDD            | —    |

| MEMC_MA13    | AE12               | 0        | GVDD            | —    |

| MEMC_MA14    | AF11               | 0        | GVDD            | —    |

| MEMC_MWE     | AE5                | 0        | GVDD            | —    |

| MEMC_MRAS    | AD7                | 0        | GVDD            | —    |

| MEMC_MCAS    | AG4                | 0        | GVDD            | —    |

| MEMC_MCS[0]  | AH3                | 0        | GVDD            | —    |

| MEMC_MCS[1]  | AD5                | 0        | GVDD            | —    |

| MEMC_MCKE    | AE4                | 0        | GVDD            | 3    |

| MEMC_MCK[0]  | AF4                | 0        | GVDD            | —    |

| MEMC_MCK[0]  | AF3                | 0        | GVDD            | —    |

| MEMC_MCK[1]  | AF1                | 0        | GVDD            | —    |

| MEMC_MCK[1]  | AE1                | 0        | GVDD            | —    |

| MEMC_MODT[0] | AE3                | 0        | GVDD            | —    |

| MEMC_MODT[1] | AD4                | 0        | GVDD            | —    |

| MEMC_MVREF   | AD12               | I        | GVDD            | —    |

## Table 70. MPC8315E TEPBGA II Pinout Listing (continued)

| Signal                                      | Package Pin Number | Pin Type | Power<br>Supply | Note |

|---------------------------------------------|--------------------|----------|-----------------|------|

| PCI_REQ0                                    | E18                | I/O      | NVDD2_OFF       | _    |

| PCI_REQ1/CPCI_HS_ES                         | C18                | I        | NVDD2_OFF       | —    |

| PCI_REQ2                                    | E17                | I        | NVDD2_OFF       | —    |

| PCI_GNT0                                    | B20                | I/O      | NVDD2_OFF       | _    |

| PCI_GNT1/CPCI_HS_LED                        | D17                | 0        | NVDD2_OFF       | —    |

| PCI_GNT2/CPCI_HS_ENUM                       | E15                | 0        | NVDD2_OFF       | _    |

| M66EN                                       | L24                | I        | NVDD2_OFF       | —    |

| PCI_CLK0                                    | E23                | 0        | NVDD2_OFF       | —    |

| PCI_CLK1                                    | F24                | 0        | NVDD2_OFF       | _    |

| PCI_CLK2                                    | E25                | 0        | NVDD2_OFF       | —    |

| PCI_PME                                     | B23                | I/O      | NVDD2_OFF       | 2    |

|                                             | ETSEC1/_USBULPI    |          |                 |      |

| GPIO_24/TSEC1_COL/USBDR_TXDRXD0             | J1                 | I/O      | LVDD1_OFF       | _    |

| GPIO_25/TSEC1_CRS/USBDR_TXDRXD1             | H1                 | I/O      | LVDD1_OFF       | _    |

| TSEC1_GTX_CLK/USBDR_TXDRXD2                 | K5                 | I/O      | LVDD1_OFF       | 3    |

| TSEC1_RX_CLK/USBDR_TXDRXD3                  | J4                 | I/O      | LVDD1_OFF       | _    |

| TSCE1_RX_DV/USBDR_TXDRXD4                   | J2                 | I/O      | LVDD1_OFF       | _    |

| TSEC1_RXD[3]/USBDR_TXDRXD5                  | G1                 | I/O      | LVDD1_OFF       | _    |

| TSEC1_RXD[2]/USBDR_TXDRXD6                  | H3                 | I/O      | LVDD1_OFF       | —    |

| TSEC1_RXD[1]/USBDR_TXDRXD7/TSEC<br>_TMR_CLK | J5                 | I/O      | LVDD1_OFF       | -    |

| TSEC1_RXD[0]/USBDR_NXT/TSEC_TMR<br>_TRIG1   | H2                 | I        | LVDD1_OFF       | —    |

| TSEC1_RX_ER/USBDR_DIR/TSEC_TMR_<br>TRIG2    | H5                 | I        | LVDD1_OFF       | -    |

| TSEC1_TX_CLK/USBDR_CLK                      | G2                 | I        | LVDD1_OFF       | _    |

| GPIO_28/TSEC1_TXD[3]/TSEC_TMR_GC<br>LK      | F3                 | I/O      | LVDD1_OFF       | _    |

| GPIO_29/TSEC1_TXD[2]/TSEC_TMR_PP1           | F2                 | I/O      | LVDD1_OFF       | _    |

| GPIO_30/TSEC1_TXD[1]/TSEC_TMR_PP2           | F1                 | I/O      | LVDD1_OFF       |      |

| TSEC1_TXD[0]/USBDR_STP/<br>TSEC_TMR_PP3     | G4                 | 0        | LVDD1_OFF       | 12   |

| GPIO_31/TSEC1_TX_EN/TSEC_TMR_AL<br>ARM1     | F4                 | I/O      | LVDD1_OFF       | -    |

| TSEC1_TX_ER/TSEC_TMR_ALARM2                 | G5                 | 0        | LVDD1_OFF       | _    |

| TSEC_GTX_CLK125                             | D1                 | 1        | NVDD1_ON        | —    |

| TSEC_MDC/LB_POR_CFG_BOOT_ECC                | E3                 | I/O      | NVDD1_ON        | 9    |

| TSEC_MDIO                                   | E2                 | I/O      | NVDD1_ON        |      |

The primary clock source can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the device is configured as a PCI host device, SYS\_CLK\_IN is its primary input clock. SYS\_CLK\_IN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_SYS\_CLKIN\_DIV configuration input selects whether SYS\_CLK\_IN or SYS\_CLK\_IN/2 is driven out on the PCI\_SYNC\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the device to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock. When the device is configured as a PCI agent device the SYS\_CLK\_IN signal should be tied to GND.

As shown in Figure 62, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create the coherent system bus clock ( $csb\_clk$ ), the internal clock for the DDR controller ( $ddr\_clk$ ), and the internal clock for the local bus interface unit ( $lbiu\_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$csb_clk = \{PCI_SYNC_IN \times (1 + \sim \overline{CFG_SYS_CLKIN_DIV})\} \times SPMF$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 + ~  $\overline{CFG_SYS_CLKIN_DIV}$ ) is the SYS\_CLK\_IN frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies up the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See Chapter 4, "Reset, Clocking, and Initialization," in the *MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual* for more information on the clock subsystem.

The internal *ddr\_clk* frequency is determined by the following equation:

$ddr_clk = csb_clk \times (1 + RCWL[DDRCM])$

Note that  $ddr_clk$  is not the external memory bus frequency;  $ddr_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the same frequency as  $ddr_clk$ .

The internal *lbiu\_clk* frequency is determined by the following equation:

$lbiu_clk = csb_clk \times (1 + RCWL[LBCM])$

Note that *lbiu\_clk* is not the external local bus frequency; *lbiu\_clk* passes through the LBIU clock divider to create the external local bus clock outputs (LCLK[0:1]). The LBIU clock divider ratio is controlled by LCRR[CLKDIV].

In addition, some of the internal units may be required to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. Table 71 specifies which units have a configurable clock frequency.

| Unit                         | Default Frequency | Options                            |

|------------------------------|-------------------|------------------------------------|

| eTSEC1                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| eTSEC2                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| Security Core, I2C, SAP, TPR | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| USB DR                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| PCI and DMA complex          | csb_clk           | Off, csb_clk                       |

| PCI Express                  | csb_clk           | Off, csb_clk                       |

| Serial ATA                   | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

This table provides the operating frequencies for the TEPBGA II under recommended operating conditions (see Table 2).

Table 72. Operating Frequencies for TEPBGA II

| Characteristic <sup>1</sup>                    | Max Operating Frequency | Unit |

|------------------------------------------------|-------------------------|------|

| e300 core frequency (core_clk)                 | 400                     | MHz  |

| Coherent system bus frequency (csb_clk)        | 133                     | MHz  |

| DDR1/2 memory bus frequency (MCK) <sup>2</sup> | 133                     | MHz  |

| Local bus frequency (LCLKn) <sup>3</sup>       | 66                      | MHz  |

| PCI input frequency (SYS_CLK_IN or PCI_CLK)    | 24-66                   | MHz  |

Note:

1. The SYS\_CLK\_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK[0:1], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies.

2. The DDR data rate is 2x the DDR memory bus frequency.

3. The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCRR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

## 24.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. Table 73 shows the multiplication factor encodings for the system PLL.

## NOTE

If RCWL[DDRCM] and RCWL[LBCM] are both cleared, the system PLL VCO frequency = (CSB frequency) × (System PLL VCO Divider).

If either RCWL[DDRCM] or RCWL[LBCM] are set, the system PLL VCO frequency =  $2 \times (CSB \text{ frequency}) \times (System PLL VCO Divider).$

The VCO divider needs to be set properly so that the System PLL VCO frequency is in the range of 450–750 MHz.

Thermal

## 25.2 Thermal Management Information

For the following sections,  $P_D = (VDD \times I_{DD}) + P_{I/O}$  where  $P_{I/O}$  is the power dissipation of the I/O drivers.

# 25.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$T_{J} = T_{A} + (R_{\theta JA} \times P_{D})$ where:  $T_{J} = \text{junction temperature (°C)}$  $T_{A} = \text{ambient temperature for the package (°C)}$  $R_{\theta JA} = \text{junction to ambient thermal resistance (°C/W)}$  $P_{D} = \text{power dissipation in the package (W)}$

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. As a general statement, the value obtained on a single layer board is appropriate for a tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated. Test cases have demonstrated that errors of a factor of two (in the quantity  $T_J - T_A$ ) are possible.

## 25.2.2 Estimation of Junction Temperature with Junction-to-Board Thermal Resistance

The thermal performance of a device cannot be adequately predicted from the junction to ambient thermal resistance. The thermal performance of any component is strongly dependent on the power dissipation of surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

$T_J = T_B + (R_{\theta JB} \times P_D)$ where:  $T_J = \text{junction temperature (°C)}$  $T_B = \text{board temperature at the package perimeter (°C)}$

$R_{\theta IB}$  = junction to board thermal resistance (°C/W) per JESD51-8

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. The application board should be similar to the thermal test condition: the component is soldered to a board with internal planes.

## 25.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$T_J = T_T + (\Psi_{JT} \times P_D)$ where:  $T_J = \text{junction temperature (°C)}$  $T_T = \text{thermocouple temperature on top of package (°C)}$  $\Psi_{JT} = \text{junction to ambient thermal resistance (°C/W)}$  $P_D = \text{power dissipation in the package (W)}$

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 25.2.4 Heat Sinks and Junction-to-Case Thermal Resistance

In some application environments, a heat sink is required to provide the necessary thermal management of the device. When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$ where:  $R_{\theta JA} = \text{junction to ambient thermal resistance (°C/W)}$  $R_{\theta JC} = \text{junction to case thermal resistance (°C/W)}$  $R_{\theta CA} = \text{case to ambient thermal resistance (°C/W)}$

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, air flow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

System Design Information

Power and ground connections must be made to all external VDD, GVDD, LVDD, NVDD, and GND pins of the device.

## 26.5 Output Buffer DC Impedance

The MPC8315E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

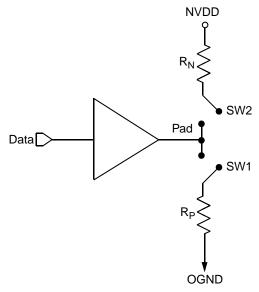

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to NVDD or GND. Then, the value of each resistor is varied until the pad voltage is NVDD/2 (see Figure 64). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals NVDD/2.  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 64. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. QorlQ is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2011 Freescale Semiconductor, Inc.

Document Number: MPC8315EEC Rev. 2 11/2011