# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Active                                                                 |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 400MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR, DDR2                                                              |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (2)                                                         |

| USB                             | USB 2.0 + PHY (1)                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 620-BBGA Exposed Pad                                                   |

| Supplier Device Package         | 620-HBGA (29x29)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8315cvragda |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# NP\_

MPC8315E Features

- Combines a True Random Number Generator (TRNG) and a NIST-approved Pseudo-Random Number Generator (PRNG) (as described in Annex C of FIPS140-2 and ANSI X9.62).

- Cyclical Redundancy Check Hardware Accelerator (CRCA)

- Implements CRC32C as required for iSCSI header and payload checksums, CRC32 as required for IEEE 802 packets, as well as for programmable 32 bit CRC polynomials

## 2.4 DDR Memory Controller

The DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 266 MHz data rate

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

## 2.5 PCI Controller

The PCI controller includes the following features:

- Designed to comply with PCI Local Bus Specification Revision 2.3

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

## 2.6 TDM Interface

The TDM interface includes the following features:

- Independent receive and transmit with dedicated data, clock and frame sync line

- Separate or shared RCK and TCK whose source can be either internal or external

- Glueless interface to E1/T1 frames and MVIP, SCAS, and H.110 buses

- Up to 128 time slots, where each slot can be programmed to be active or inactive

- 8- or 16-bit word widths

- The TDM Transmitter Sync Signal (TFS), Transmitter Clock Signal (TCK) and Receiver Clock

MPC8315E Features

## 2.9 Dual Serial ATA (SATA) Controllers

The SATA controllers have the following features:

- Designed to comply with Serial ATA Rev 2.5 Specification

- ATAPI 6+

- Spread spectrum clocking on receive

- Asynchronous notification

- Hot plug including asynchronous signal recovery

- Link power management

- Native command queuing

- Staggered spin-up and port multiplier support

- SATA 1.5 and 3.0 Gbps operation

- Interrupt driven

- Power management support

- Error handling and diagnostic features

- Far end/near end loopback

- Failed CRC error reporting

- Increased ALIGN insertion rates

- Scrambling and CONT override

### 2.10 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The eTSECs include the following features:

- Two SGMII/RGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3<sup>TM</sup>, IEEE 802.3u<sup>TM</sup>, IEEE 802.3x<sup>TM</sup>, IEEE 802.3z<sup>TM</sup>, IEEE 802.3au<sup>TM</sup>, IEEE 802.3ab<sup>TM</sup>, and IEEE Std 1588<sup>TM</sup>

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status.

## 2.11 Integrated Programmable Interrupt Controller (IPIC)

The integrated programmable interrupt controller (IPIC) provides a flexible solution for general-purpose interrupt control. The IPIC programming model is compatible with the MPC8260 interrupt controller and supports external and internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

**Electrical Characteristics**

| Characteristic                                             | Symbol        | Recommended<br>Value <sup>1</sup> | Unit | Status in D3<br>Warm mode | Note |

|------------------------------------------------------------|---------------|-----------------------------------|------|---------------------------|------|

| Dedicated USB ground for USB bias circuit                  | USB_VSSA_BIAS | 0.0                               | V    | _                         |      |

| Dedicated power for USB transceiver                        | USB_VDDA      | 3.3 ± 300 mv                      | V    | Switched Off              | —    |

| Dedicated ground for USB transceiver                       | USB_VSSA      | 0.0                               | V    | _                         | —    |

| SATA digital power                                         | SATA_VDD      | 1.0 ± 50 mv                       | V    | Switched Off              | —    |

| SATA digital ground                                        | SATA_VSS      | 0.0                               | V    | —                         | —    |

| SATA analog I/O power                                      | VDD1IO        | 1.0 ± 50 mv                       | V    | Switched Off              | —    |

| SATA analog I/O ground                                     | VSS1IO        | 0.0                               | V    | _                         | _    |

| SATA core analog power                                     | VDD1ANA       | 1.0 ± 50 mv                       | V    | Switched Off              | —    |

| SATA analog ground                                         | VSS1ANA       | 0.0                               | V    | _                         | _    |

| SATA analog power PLL                                      | VDD33PLL      | 3.3 ± 165 mv                      | V    | Switched Off              | —    |

| SATA 3.3 analog power                                      | VDD33ANA      | 3.3 ± 165 mv                      | V    | Switched Off              | —    |

| SATA reference analog ground                               | VSSRESREF     | 0.0                               | V    | _                         | —    |

| Core supply voltage                                        | VDD           | 1.0 ± 50 mv                       | V    | Switched Off              | _    |

| Core supply voltage                                        | VDDC          | 1.0 ± 50 mv                       | V    | Switched On               | —    |

| Analog power for e300 core APLL                            | AVDD1         | 1.0 ± 50 mv                       | V    | Switched Off              | 6    |

| Analog power for system APLL                               | AVDD2         | 1.0 ± 50 mv                       | V    | Switched On               | 6    |

| DDR and DDR2 DRAM I/O voltage                              | GVDD          | 2.5 ± 200 mv<br>1.8 ± 100 mv      | V    | Switched Off              | —    |

| Differential reference voltage for DDR and DDR2 controller | MVREF         | GVDD /2                           | V    | Switched Off              | —    |

| Standard I/O voltage                                       | NVDD1_ON      | 3.3 ± 300 mv                      | V    | Switched On               | 1    |

| Standard I/O voltage                                       | NVDD2_ON      | 3.3 ± 300 mv                      | V    | Switched On               | 1    |

| Standard I/O voltage                                       | NVDD1_OFF     | 3.3 ± 300 mv                      | V    | Switched Off              | 2    |

| Standard I/O voltage                                       | NVDD2_OFF     | 3.3 ± 300 mv                      | V    | Switched Off              | 2    |

| Standard I/O voltage                                       | NVDD3_OFF     | 3.3 ± 300 mv                      | V    | Switched Off              | 2    |

| Standard I/O voltage                                       | NVDD4_OFF     | 3.3 ± 300 mv                      | V    | Switched Off              | 2    |

| eTSEC/USBdr I/O supply                                     | LVDD1_OFF     | 2.5 ± 125 mv<br>3.3 ± 300 mv      | V    | Switched Off              | —    |

| eTSEC I/O supply                                           | LVDD2_ON      | 2.5 ± 125 mv<br>3.3 ± 300 mv      | V    | Switched On               | -    |

| Analog and digital ground                                  | VSS           | 0.0                               | V    | _                         |      |

| Junction temperature range                                 | $T_A/T_J$     | 0 to105                           | °C   | _                         | 3    |

### Table 2. Recommended Operating Conditions (continued)

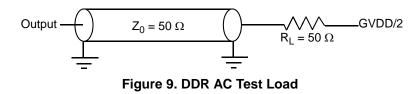

DDR and DDR2 SDRAM

### 7.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

### Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications

At recommended operating conditions

| Parameter                                                        | Symbol <sup>1</sup> | Min                      | Мах                        | Unit | Note |

|------------------------------------------------------------------|---------------------|--------------------------|----------------------------|------|------|

| MCK[n] cycle time at MCK[n]/MCK[n] crossing                      | t <sub>MCK</sub>    | 7.5                      | 10                         | ns   | 2    |

| ADDR/CMD output setup with respect to MCK<br>266 MHz<br>200 MHz  |                     | 2.9<br>3.5               | _                          | ns   | 3    |

| ADDR/CMD output hold with respect to MCK<br>266 MHz<br>200 MHz   |                     | 3.15<br>4.20             | _                          | ns   | 3    |

| MCS[n] output setup with respect to MCK<br>266 MHz<br>200 MHz    |                     | 3.15<br>4.20             | _                          | ns   | 3    |

| MCS[n] output hold with respect to MCK<br>266 MHz<br>200 MHz     |                     | 3.15<br>4.20             | _                          | ns   | 3    |

| MCK to MDQS Skew                                                 | t <sub>DDKHMH</sub> | -0.6                     | 0.6                        | ns   | 4    |

| MDQ//MDM output setup with respect to MDQS<br>266 MHz<br>200 MHz | DDRLDS              | 900<br>1000              | _                          | ps   | 5    |

| MDQ//MDM output hold with respect to MDQS<br>266 MHz<br>200 MHz  | DDRLDA              | 1100<br>1200             |                            | ps   | 5    |

| MDQS preamble start                                              | t <sub>DDKHMP</sub> | $-0.5\times t_{MCK}-0.6$ | $-0.5\times t_{MCK} + 0.6$ | ns   | 6    |

| MDQS epilogue end                                                | t <sub>DDKHME</sub> | -0.6                     | 0.6                        | ns   | 6    |

Note:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ//MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

DUART

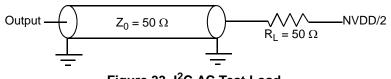

This figure provides the AC test load for the DDR bus.

## 8 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

### 8.1 DUART DC Electrical Characteristics

This table lists the DC electrical characteristics for the DUART interface.

### Table 21. DUART DC Electrical Characteristics

| Parameter                                              | Symbol          | Min        | Max        | Unit |

|--------------------------------------------------------|-----------------|------------|------------|------|

| High-level input voltage                               | V <sub>IH</sub> | 2.1        | NVDD + 0.3 | V    |

| Low-level input voltage NVDD                           | V <sub>IL</sub> | -0.3       | 0.8        | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$     | V <sub>OH</sub> | NVDD - 0.2 | _          | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$       | V <sub>OL</sub> | —          | 0.2        | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NVDD) | I <sub>IN</sub> | —          | ± 5        | μA   |

## 8.2 DUART AC Electrical Specifications

This table lists the AC timing parameters for the DUART interface.

Table 22. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | _    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          |      | 2    |

Note:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the eighth sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each sixteenth sample.

## 9 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

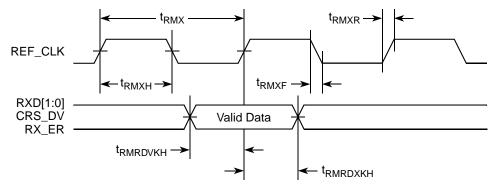

### Table 28. RMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LVDD of 3.3 V  $\pm$  300 mv

| Parameter/Condition                                               | Symbol <sup>1</sup>  | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                     | t <sub>RMRDVKH</sub> | 4.0 | _   | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                      | t <sub>RMRDXKH</sub> | 2.0 | _   | _   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>    | 1.0 | _   | 4.0 | ns   |

| REF_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>RMXF</sub>    | 1.0 | —   | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

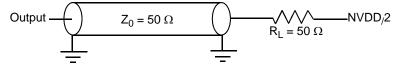

This figure provides the AC test load.

Figure 14. AC Test Load

This figure shows the RMII receive AC timing diagram.

Figure 15. RMII Receive AC Timing Diagram

### 9.2.3 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

### Table 29. RGMII and RTBI AC Timing Specifications

At recommended operating conditions (see Table 2)

| Parameter/Condition                                 | Symbol <sup>1</sup> | Min  | Тур | Max | Unit |

|-----------------------------------------------------|---------------------|------|-----|-----|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub>  | -0.6 | _   | 0.6 | ns   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>  | 1.0  |     | 2.6 | ns   |

#### Ethernet: Three-Speed Ethernet, MII Management

### Table 29. RGMII and RTBI AC Timing Specifications (continued)

At recommended operating conditions (see Table 2)

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min | Тур | Max  | Unit |

|--------------------------------------------------------|---------------------------------------|-----|-----|------|------|

| Clock cycle duration <sup>3</sup>                      | t <sub>RGT</sub>                      | 7.2 | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4, 5</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 45  | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 5</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub>   | 40  | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                     |     | —   | 0.75 | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub>                     | —   | —   | 0.75 | ns   |

| GTX_CLK125 reference clock period                      | t <sub>G12</sub> <sup>6</sup>         |     | 8.0 | —    | ns   |

| GTX_CLK125 reference clock duty cycle                  | t <sub>G125H</sub> /t <sub>G125</sub> | 47  | —   | 53   | %    |

Note:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the RTBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed so that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps, t<sub>RGT</sub> scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is LVDD/2.

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention. GTX\_CLK supply voltage is fixed at 3.3V inside the chip. If PHY supplies a 2.5 V Clock signal on this input, set TSCOMOBI bit of System I/O configuration register (SICRH) as 1. See the MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

- 7. The frequency of RX\_CLK should not exceed the TX\_CLK by more than 300 ppm

### Ethernet: Three-Speed Ethernet, MII Management

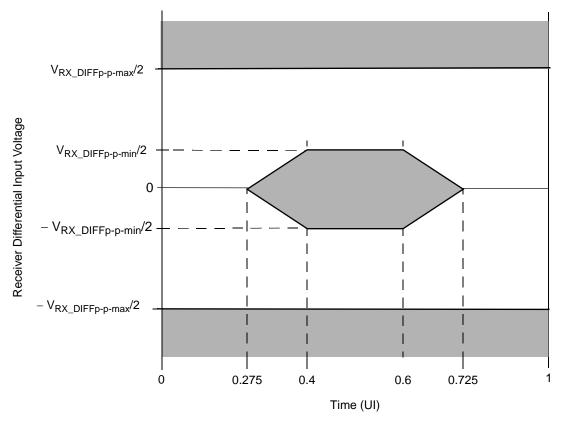

### **Table 38. SGMII Receive AC Timing Specifications**

At recommended operating conditions with XCOREVDD =  $1.0V \pm 5\%$ .

| Parameter                                          | Symbol          | Min    | Тур | Max               | Unit   | Note |

|----------------------------------------------------|-----------------|--------|-----|-------------------|--------|------|

| Deterministic Jitter Tolerance                     | JD              | 0.37   | —   | —                 | UI p-p | 1    |

| Combined Deterministic and Random Jitter Tolerance | JDR             | 0.55   | —   | —                 | UI p-p | 1    |

| Sinusoidal Jitter Tolerance                        | JSIN            | 0.1    | —   | —                 | UI p-p | 1    |

| Total Jitter Tolerance                             | JT              | 0.65   | —   | —                 | UI p-p | 1    |

| Bit Error Ratio                                    | BER             | —      | —   | 10 <sup>-12</sup> |        |      |

| Unit Interval                                      | UI              | 799.92 | 800 | 800.08            | ps     | 2    |

| AC Coupling Capacitor                              | C <sub>TX</sub> | 5      |     | 200               | nF     | 3    |

Note:

1. Measured at receiver.

2. Each UI is 800 ps ± 100 ppm.

The external AC coupling capacitor is required. It's recommended to be placed near the device transmitter outputs.

Refer to RapidIO<sup>TM</sup> 1x/4x LP Serial Physical Layer Specification for interpretation of jitter specifications.

Figure 20. SGMII Receiver Input Compliance Mask

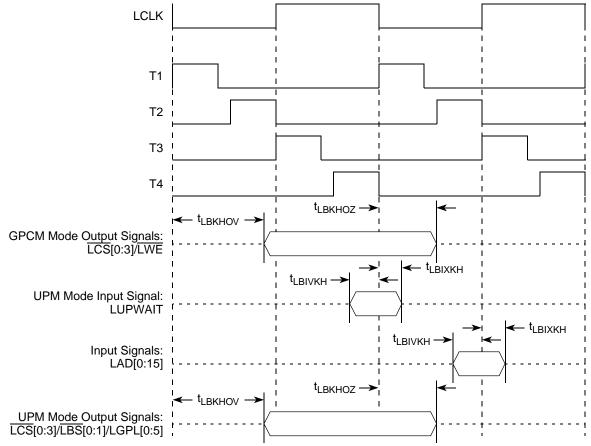

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4

## 12 JTAG

This section describes the DC and AC electrical specifications for the IEEE Std 1149.1<sup>TM</sup> (JTAG) interface.

## 12.1 JTAG DC Electrical Characteristics

This table provides the DC electrical characteristics for the IEEE 1149.1 (JTAG) interface.

Table 45. JTAG Interface DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                 | Min  | Max        | Unit |

|---------------------|-----------------|---------------------------|------|------------|------|

| Input high voltage  | V <sub>IH</sub> | _                         | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | VIL             | —                         | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | _                         | _    | ±5         | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4        | V    |

I<sup>2</sup>C

## 13.2 I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interface.

Table 48. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 47)

| Parameter                                                                                    | Symbol <sup>1</sup>            | Min                      | Max                  | Unit |

|----------------------------------------------------------------------------------------------|--------------------------------|--------------------------|----------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>               | 0                        | 400                  | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>              | 1.3                      |                      | μS   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>              | 0.6                      | _                    | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub>            | 0.6                      | _                    | μS   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub>            | 0.6                      | _                    | μs   |

| Data setup time                                                                              | t <sub>I2DVKH</sub>            | 100                      |                      | ns   |

| Data hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices                   | t <sub>i2DXKL</sub>            | 0 <sup>_2</sup>          | <br>0.9 <sup>3</sup> | μs   |

| Fall time of both SDA and SCL signals                                                        | t <sub>I2CF</sub> <sup>4</sup> | —                        | 300                  | ns   |

| Setup time for STOP condition                                                                | t <sub>I2PVKH</sub>            | 0.6                      | _                    | μS   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>            | 1.3                      | _                    | μS   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>                | $0.1 \times NVDD$        | _                    | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis)              | V <sub>NH</sub>                | $0.2 \times \text{NVDD}$ |                      | V    |

Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>12PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- MPC8315E provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum t<sub>I2DVKH</sub> has to be met only if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. MPC8315E does not follow the I2C-BUS Specifications version 2.1 regarding the tI2CF AC parameter.

This figure provides the AC test load for the  $I^2C$ .

Figure 33. I<sup>2</sup>C AC Test Load

Timers

## 17.3 Out-of-Band (OOB) Electrical Characteristics

This table provides the out-of-band (OOB) electrical characteristics for the SATA interface of the MPC8315.

| Parameter                                              | Symbol                               | Min      | Typical    | Max        | Units | Note |

|--------------------------------------------------------|--------------------------------------|----------|------------|------------|-------|------|

| OOB Signal Detection Threshold<br>1.5G                 |                                      |          |            |            |       |      |

| 3.0G                                                   | V <sub>SATA_OOBDETE</sub>            | 50<br>75 | 100<br>125 | 200<br>200 | mVp-p |      |

| UI During OOB Signaling                                | T <sub>SATA_UIOOB</sub>              | _        | 666.67     | —          | ps    |      |

| COMINIT/ COMRESET and<br>COMWAKE Transmit Burst Length | T <sub>SATA_UIOOBTXB</sub>           |          | 160        | _          | UI    |      |

| COMINIT/COMRESET Transmit Gap<br>Length                | T <sub>SATA_UIOOBTXGap</sub>         |          | 480        | _          | UI    | _    |

| COMWAKE Transmit Gap Length                            | T <sub>SATA_UIOOBTX</sub><br>WakeGap |          | 160        | _          | UI    | _    |

### Table 59. Out-of-Band (OOB) Electrical Characteristics

## 18 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8315E.

## **18.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the timers pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Table 60. Timers DC Electrical Characte | eristics |

|-----------------------------------------|----------|

|-----------------------------------------|----------|

| Characteristic      | Symbol          | Condition                                   | Min  | Max        | Unit |

|---------------------|-----------------|---------------------------------------------|------|------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA                   | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                    | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                    | _    | 0.4        | V    |

| Input high voltage  | V <sub>IH</sub> | —                                           | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                           | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq V_{IN} \leq N \text{VDD}$ | _    | ± 5        | μA   |

## 18.2 Timers AC Timing Specifications

This table provides the timers input and output AC timing specifications.

Table 61. Timers Input AC Timing Specifications

| Characteristic                    | Symbol <sup>1</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

IPIC

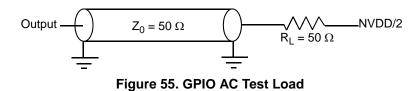

This figure provides the AC test load for the GPIO.

## 20 IPIC

This section describes the DC and AC electrical specifications for the external interrupt pins of the MPC8315E.

## 20.1 IPIC DC Electrical Characteristics

This table provides the DC electrical characteristics for the external interrupt pins.

| Characteristic      | Symbol          | Condition                 | Min  | Max        | Unit |

|---------------------|-----------------|---------------------------|------|------------|------|

| Input high voltage  | V <sub>IH</sub> | —                         | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                         | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | —                         | _    | ±5         | μΑ   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _    | 0.4        | V    |

### Table 64. IPIC DC Electrical Characteristics

## 20.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

### Table 65. IPIC Input AC Timing Specifications

| Characteristic                  | Symbol <sup>1</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

## 21 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8315E.

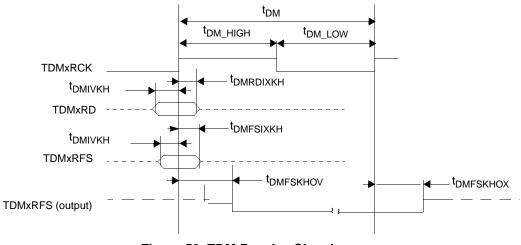

This table provides the TDM AC timing specifications.

Table 69. TDM AC Timing specifications

| Parameter/Condition                          | Symbol                | Min  | Мах  | Unit |

|----------------------------------------------|-----------------------|------|------|------|

| TDMxRCK/TDMxTCK                              | t <sub>DM</sub>       | 20.0 | —    | ns   |

| TDMxRCK/TDMxTCK high pulse width             | t <sub>DM_HIGH</sub>  | 8.0  | —    | ns   |

| TDMxRCK/TDMxTCK low pulse width              | t <sub>DM_LOW</sub>   | 8.0  | —    | ns   |

| TDMxRCK/TDMxTCK rise time (20% to 80%)       | t <sub>DMKH</sub>     | 1.0  | 4.0  | ns   |

| TDMxRCK/TDMxTCK fall time (80% to 20%)       | t <sub>DMKL</sub>     | 1.0  | 4.0  | ns   |

| TDM all input setup time                     | t <sub>DMIVKH</sub>   | 3.0  | —    | ns   |

| TDMxRD hold time                             | t <sub>DMRDIXKH</sub> | 3.5  | —    | ns   |

| TDMxTFS/TDMxRFS input hold time              | t <sub>DMFSIXKH</sub> | 2.0  | —    | ns   |

| TDMxTCK High to TDMxTD output active         | t <sub>DM_OUTAC</sub> | 4.0  | —    | ns   |

| TDMxTCK High to TDMxTD output valid          | t <sub>DMTKHOV</sub>  | _    | 14.0 | ns   |

| TDMxTD hold time                             | t <sub>DMTKHOX</sub>  | 2.0  | —    | ns   |

| TDMxTCK High to TDMxTD output high impedance | t <sub>DM_OUTHI</sub> | _    | 10.0 | ns   |

| TDMxTFS/TDMxRFS output valid                 | t <sub>DMFSKHOV</sub> | _    | 13.5 | ns   |

| TDMxTFS/TDMxRFS output hold time             | t <sub>DMFSKHOX</sub> | 2.5  | —    | ns   |

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TDMIVKH</sub> symbolizes TDM timing (DM) with respect to the time the input signals (I) reach the valid state (V) relative to the TDM Clock, t<sub>TC</sub>, reference (K) going to the high (H) state or setup time. Also, output signals (O), hold (X).

</sub>

2. Output values are based on 30 pF capacitive load.

Inputs are referenced to the sampling that the TDM is programmed to use. Outputs are referenced to the programming edge they are programmed to use. Use of the rising edge or falling edge as a reference is programmable. TDMxTCK and TDMxRCK are shown using the rising edge.

This figure shows the TDM receive signal timing.

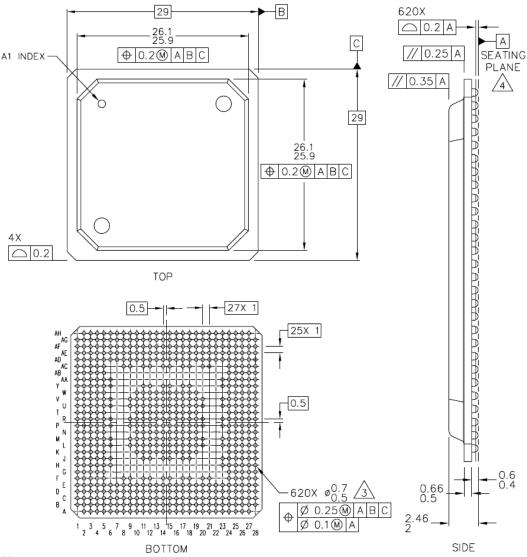

### 23.2 Mechanical Dimensions of the TEPBGA II

This figure shows the mechanical dimensions and bottom surface nomenclature of the 620-pin TEPBGA II package.

### Notes:

1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

Figure 61. Mechanical Dimensions and Bottom Surface Nomenclature of the TEPBGA II

### 23.3 Pinout Listings

This table provides the pin-out listing for the TEPBGA II package.

Package and Pin Listings

### Table 70. MPC8315E TEPBGA II Pinout Listing (continued)

| Signal                           | Package Pin Number      | Pin Type | Power<br>Supply | Note     |

|----------------------------------|-------------------------|----------|-----------------|----------|

|                                  | ETSEC2                  |          |                 | _        |

| GPIO_26/TSEC2_COL                | A8                      | I/O      | LVDD2_ON        | —        |

| GPIO_27/TSEC2_CRS                | E9                      | I/O      | LVDD2_ON        |          |

| TSEC2_GTX_CLK                    | B10                     | 0        | LVDD2_ON        | —        |

| TSEC2_RX_CLK                     | B8                      | I        | LVDD2_ON        | <u> </u> |

| TSCE2_RX_DV                      | C9                      | I        | LVDD2_ON        |          |

| TSEC2_RXD[3]                     | C10                     | I        | LVDD2_ON        |          |

| TSEC2_RXD[2]                     | D10                     | I        | LVDD2_ON        | —        |

| TSEC2_RXD[1]                     | A9                      | I        | LVDD2_ON        | —        |

| TSEC2_RXD[0]                     | B9                      | I        | LVDD2_ON        |          |

| TSEC2_RX_ER                      | A10                     | I        | LVDD2_ON        | <u> </u> |

| TSEC2_TX_CLK                     | D8                      | I        | LVDD2_ON        | —        |

| TSEC2_TXD[3]/CFG_RESET_SOURCE[0] | D11                     | I/O      | LVDD2_ON        | —        |

| TSEC2_TXD[2]/CFG_RESET_SOURCE[1] | C7                      | I/O      | LVDD2_ON        | <u> </u> |

| TSEC2_TXD[1]/CFG_RESET_SOURCE[2] | E8                      | I/O      | LVDD2_ON        | <u> </u> |

| TSEC2_TXD[0]/CFG_RESET_SOURCE[3] | B7                      | I/O      | LVDD2_ON        | <u> </u> |

| TSEC2_TX_EN                      | D12                     | 0        | LVDD2_ON        | <u> </u> |

| TSEC2_TX_ER                      | B11                     | 0        | LVDD2_ON        | <u> </u> |

|                                  | SGMII / PCI Express PHY |          |                 | -        |

| ТХА                              | P4                      | 0        | XPADVDD         | —        |

| TXA                              | N4                      | 0        | XPADVDD         | —        |

| RXA                              | R1                      | I        | XCOREVDD        |          |

| RXA                              | P1                      | I        | XCOREVDD        | —        |

| ТХВ                              | U4                      | 0        | XPADVDD         |          |

| TXB                              | V4                      | 0        | XPADVDD         | —        |

| RXB                              | U1                      | I        | XCOREVDD        | —        |

| RXB                              | V1                      | I        | XCOREVDD        |          |

| SD_IMP_CAL_RX                    | N3                      | I        | XCOREVDD        | —        |

| SD_REF_CLK                       | R4                      | I        | XCOREVDD        |          |

| SD_REF_CLK                       | R5                      | I        | XCOREVDD        | —        |

| SD_PLL_TPD                       | T2                      | 0        | _               | <u> </u> |

| SD_IMP_CAL_TX                    | V5                      | I        | XPADVDD         | -        |

| SDAVDD                           | Т3                      | I        | _               | <u> </u> |

| SD_PLL_TPA_ANA                   | T4                      | 0        | _               | <u> </u> |

| SDAVSS                           | T5                      | I        | _               | <u> </u> |

|                                  | USB Phy                 | · ·      |                 | <u>.</u> |

#### Package and Pin Listings

### Table 70. MPC8315E TEPBGA II Pinout Listing (continued)

| Signal   | Package Pin Number                             | Pin Type | Power<br>Supply | Note |

|----------|------------------------------------------------|----------|-----------------|------|

| VSS1IO   | M24, N24, P19, P20, P25, P27, R25, R27,<br>T24 | I        | _               | Ι    |

| XCOREVDD | P2, P10, R2, T1                                | I        | —               | _    |

| XCOREVSS | R3, R10, U2, V2                                | I        | —               | _    |

| XPADVDD  | P3, R9, U3                                     | I        | —               | _    |

| XPADVSS  | P5, P9, V3                                     | I        | _               | _    |

#### Note:

1. This pin is an open drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to NVDD.

2. This pin is an open drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to NVDD.

3. This output is actively driven during reset rather than being three-stated during reset.

4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

5. This pin should have a weak pull up if the chip is in PCI host mode. Follow PCI specifications recommendation.

6. This pin must always be tied to VSS.

7. Thermal sensitive resistor.

8. This pin should be connected to USB\_VSSA\_BIAS through 10K precision resistor.

The LB\_POR\_CFG\_BOOT\_ECC functionality for this pin is only available in MPC8315E revision 1.1 and later. The LB\_POR\_CFG\_BOOT\_ECC is sampled only during the PORESET negation. This pin with an internal pull down resistor enables the ECC by default. To disable the ECC an external strong pull up resistor or a tristate buffer is needed.

10. This pin should be connected to an external 2.7 K ±1% resistor connected to VSS. The resistor should be placed as close as possible to the input.

11. This pin has a weak internal pull-down.

12. This pin has a weak internal pull-up.

| Unit                         | Default Frequency | Options                            |

|------------------------------|-------------------|------------------------------------|

| eTSEC1                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| eTSEC2                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| Security Core, I2C, SAP, TPR | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| USB DR                       | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

| PCI and DMA complex          | csb_clk           | Off, csb_clk                       |

| PCI Express                  | csb_clk           | Off, csb_clk                       |

| Serial ATA                   | csb_clk           | Off, csb_clk, csb_clk/2, csb_clk/3 |

This table provides the operating frequencies for the TEPBGA II under recommended operating conditions (see Table 2).

Table 72. Operating Frequencies for TEPBGA II

| Characteristic <sup>1</sup>                    | Max Operating Frequency | Unit |

|------------------------------------------------|-------------------------|------|

| e300 core frequency (core_clk)                 | 400                     | MHz  |

| Coherent system bus frequency (csb_clk)        | 133                     | MHz  |

| DDR1/2 memory bus frequency (MCK) <sup>2</sup> | 133                     | MHz  |

| Local bus frequency (LCLKn) <sup>3</sup>       | 66                      | MHz  |

| PCI input frequency (SYS_CLK_IN or PCI_CLK)    | 24-66                   | MHz  |

Note:

1. The SYS\_CLK\_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK[0:1], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies.

2. The DDR data rate is 2x the DDR memory bus frequency.

3. The local bus frequency is 1/2, 1/4, or 1/8 of the *lbiu\_clk* frequency (depending on LCRR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

### 24.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. Table 73 shows the multiplication factor encodings for the system PLL.

### NOTE

If RCWL[DDRCM] and RCWL[LBCM] are both cleared, the system PLL VCO frequency = (CSB frequency) × (System PLL VCO Divider).

If either RCWL[DDRCM] or RCWL[LBCM] are set, the system PLL VCO frequency =  $2 \times (CSB \text{ frequency}) \times (System PLL VCO Divider).$

The VCO divider needs to be set properly so that the System PLL VCO frequency is in the range of 450–750 MHz.

Clocking

## 24.2 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). Table 76 shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in Table 76 should be considered as reserved.

### NOTE

Core VCO frequency = core frequency  $\times$  VCO divider VCO divider has to be set properly so that the core VCO frequency is in the range of 400–800 MHz.

| RC  | RCWL[COREPLL] |   | core alky ach alk Patia                                        | VCO Divider <sup>1</sup>                                       |

|-----|---------------|---|----------------------------------------------------------------|----------------------------------------------------------------|

| 0–1 | 2–5           | 6 | core_clk : csb_clk Ratio                                       |                                                                |

| nn  | 0000          | 0 | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) |

| 11  | nnnn          | n | N/A                                                            | N/A                                                            |

| 00  | 0001          | 0 | 1:1                                                            | 2                                                              |

| 01  | 0001          | 0 | 1:1                                                            | 4                                                              |

| 00  | 0001          | 1 | 1.5:1                                                          | 2                                                              |

| 01  | 0001          | 1 | 1.5:1                                                          | 4                                                              |

| 00  | 0010          | 0 | 2:1                                                            | 2                                                              |

| 01  | 0010          | 0 | 2:1                                                            | 4                                                              |

| 00  | 0010          | 1 | 2.5:1                                                          | 2                                                              |

| 01  | 0010          | 1 | 2.5:1                                                          | 4                                                              |

| 00  | 0011          | 0 | 3:1                                                            | 2                                                              |

| 01  | 0011          | 0 | 3:1                                                            | 4                                                              |

### Table 76. e300 Core PLL Configuration

<sup>1</sup> Core VCO frequency = core frequency  $\times$  VCO divider.

## 24.3 Suggested PLL Configurations

To simplify the PLL configurations, the MPC8315E might be separated into two clock domains. The first domain contain the CSB PLL and the core PLL. The core PLL is connected serially to the CSB PLL, and has the csb\_clk as its input clock. The clock domains are independent, and each of their PLLs are configured separately. Both of the domains has one common input clock. Table 77 shows suggested PLL configurations for 33, 25, and 66 MHz input clocks.

| Conf. No. | SPMF | Core\PLL | Input Clock Frequency (MHz) | CSB Frequency (MHz) | Core Frequency (MHz) |

|-----------|------|----------|-----------------------------|---------------------|----------------------|

| 1         | 0100 | 0000100  | 33.33                       | 133.33              | 266.66               |

| 3         | 0010 | 0000100  | 66.67                       | 133.33              | 266.66               |

| 4         | 0100 | 0000101  | 33.33                       | 133.33              | 333.33               |

| 5         | 0101 | 0000101  | 25                          | 125                 | 312.5                |

Table 77. Suggested PLL Configurations

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum VDD, nominal NVDD, 105°C.

| Impedance      | Local Bus, Ethernet,<br>DUART, Control,<br>Configuration, Power<br>Management | PCI Signals<br>(not including PCI<br>Output Clocks) | PCI Output Clocks<br>(including<br>PCI_SYNC_OUT) | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 42 Target                                                                     | 25 Target                                           | 42 Target                                        | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                            | NA                                                  | NA                                               | NA        | Z <sub>DIFF</sub> | Ω    |

**Table 80. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

### 26.6 Configuration Pin Multiplexing

The MPC8315E provides the user with power-on configuration options that can be set through the use of external pull-up or pull-down resistors of  $4.7 \text{ k}\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when PORESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

## 26.7 Pull-Up Resistor Requirements

The MPC8315E requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and EPIC interrupt pins.

For more information on required pull up resistors and the connections required for JTAG interface, see AN3438, MPC8315 Design Checklist

## 27 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 27.1, "Part Numbers Fully Addressed by this Document."

## 27.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the MPC8315E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. QorlQ is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2011 Freescale Semiconductor, Inc.

Document Number: MPC8315EEC Rev. 2 11/2011