Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                         |

|---------------------------------|-------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                |

| Core Processor                  | PowerPC e300c3                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 266MHz                                                                  |

| Co-Processors/DSP               | Security; SEC 3.3                                                       |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | SATA 3Gbps (2)                                                          |

| USB                             | USB 2.0 + PHY (1)                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 620-BBGA Exposed Pad                                                    |

| Supplier Device Package         | 620-HBGA (29x29)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8315ecvradda |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

### 1 Overview

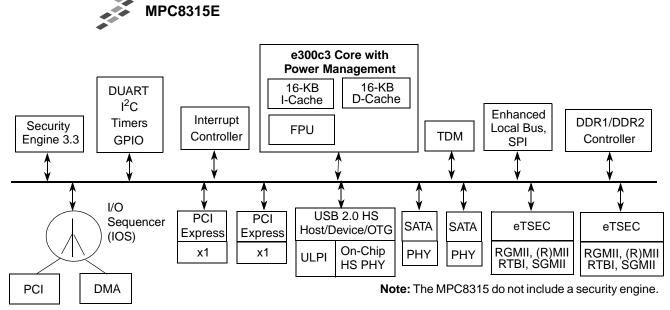

The MPC8315E incorporates the e300c3 (MPC603e-based) core, which includes 16 Kbytes of L1 instruction and data caches, on-chip memory management units (MMUs), and floating-point support. In addition to the e300 core, the SoC platform includes features such as dual enhanced three-speed 10, 100, 1000 Mbps Ethernet controllers (eTSECs) with SGMII support, a 32- or 16-bit DDR1/DDR2 SDRAM memory controller, dual SATA 3 Gbps controllers (MPC8315E-specific), a security engine to accelerate control and data plane security protocols, and a high degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration. The MPC8315E also offers peripheral interfaces such as a 32-bit PCI interface with up to 66 MHz operation, 16-bit enhanced local bus interface with up to 66 MHz operation, TDM interface, and USB 2.0 with an on-chip USB 2.0 PHY.

The MPC8315E offers additional high-speed interconnect support with dual integrated SATA 3 Gbps interfaces and dual single-lane PCI Express interfaces. When not used for PCI Express, the SerDes interface may be configured to support SGMII. The MPC8315E security engine (SEC 3.3) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. This figure shows a block diagram of the MPC8315E.

Figure 1. MPC8315E Block Diagram

## 2 MPC8315E Features

The following features are supported in the MPC8315E.

### 2.1 e300 Core

The e300 core has the following features:

• Operates at up to 400 MHz

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

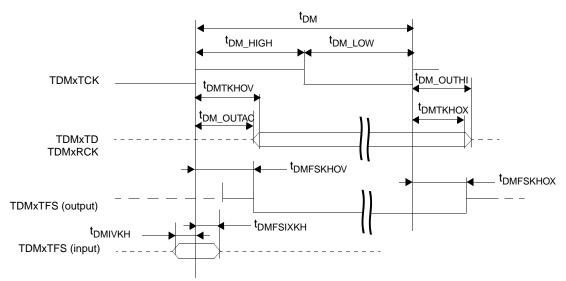

- Signal (RCK) can be configured as either input or output

- Frame sync and data signals can be programmed to be sampled either on the rising edge or on the falling edge of the clock

- Frame sync can be programmed as active low or active high

- Selectable delay (0–3 bits) between the Frame Sync signal and the beginning of the frame

- MSB or LSB first support

#### 2.7 USB Dual-Role Controller

The USB controller includes the following features:

- Designed to comply with USB Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI+ low pin interface (ULPI) or on-chip USB-2.0 full-speed/high-speed PHY

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI PHY

## 2.8 Dual PCI Express Interfaces

The PCI Express interfaces have the following features:

- PCI Express 1.0a compatible

- x1 link width

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 128-byte maximum payload size

- Support for MSI and INTx interrupt messages

- Virtual channel 0 only

- Selectable Traffic Class

- Full 64-bit decode with 32-bit wide windows

- Dedicated descriptor based DMA engine per interface with separate read and write channels

| Table 2  | Output | Drivo | Canability | (continued) |

|----------|--------|-------|------------|-------------|

| Table 3. | Outbut | Drive | Capability | (continuea) |

| Driver Type                                       | Output<br>Impedance (Ω) | Supply<br>Voltage    |

|---------------------------------------------------|-------------------------|----------------------|

| DUART, system control, I <sup>2</sup> C, JTAG,SPI | 42                      | NVDD = 3.3 V         |

| GPIO signals                                      | 42                      | NVDD = 3.3 V         |

| eTSEC                                             | 42                      | LVDD = 3.3 V / 2.5 V |

Output Impedance can also be adjusted through configurable options in DDR Control Driver Register (DDRCDR). See the MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual.

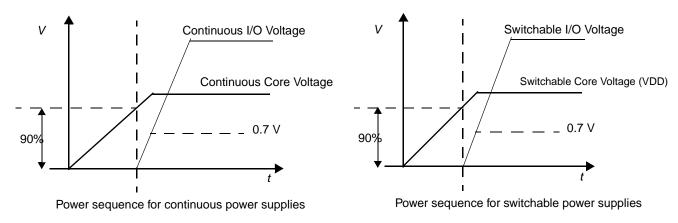

## 3.2 Power Sequencing

The MPC8315E does not require the core supply voltage (VDD and VDDC) and I/O supply voltages (GVDD, LVDDx\_ON, LVDDx\_OFF, NVDDx\_ON and NVDDx\_OFF) to be applied in any particular order. During the power ramp up, before the power supplies are stable, if the I/O voltages are supplied before the core voltage, there may be a period of time when all input and output pins be actively driven and cause contention and/or excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the continuous core voltage (VDDC) before the continuous I/O voltages (LVDDx\_ON and NVDDx\_ON) and switchable core voltage (VDD) before the switchable I/O voltages (GVDD, LVDDx\_OFF, and NVDDx\_OFF). PORESET should be asserted before the continuous power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V, see Figure 3. Once all the power supplies are stable, wait for a minimum of 32 clock cycles before negating PORESET.

The I/O power supply ramp-up slew rate should be slower than  $4V/100~\mu s$ , this requirement is for ESD circuit.

This figure shows the power-up sequencing for switchable and continuous supplies.

Figure 3. Power-Up Sequencing

When switching from normal mode to D3 warm (standby) mode, first turn off the switchable I/O voltage supply and then turn off the switchable core voltage supply. Similarly, when switching from D3 warm (standby) mode to normal mode, first turn on the switchable core voltage supply and then turn on the switchable I/O voltage supply.

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

**Clock Input Timing**

### 5.1 DC Electrical Characteristics

This table provides the clock input (SYS\_CLK\_IN/PCI\_SYNC\_IN) DC timing specifications for the MPC8315E.

**Parameter** Condition **Symbol** Min Max Unit Input high voltage  $V_{IH}$ 2.4 NVDD + 0.3V V Input low voltage -0.3  $V_{II}$ 0.4 SYS\_CLK\_IN input current  $0 \text{ V} \leq V_{IN} \leq NVDD$ ±10 μΑ  $I_{IN}$ SYS\_XTAL\_IN input current  $0 \text{ V} \leq V_{IN} \leq NVDD$ ±40 μΑ  $I_{IN}$ PCI\_SYNC\_IN input current  $0~V \leq V_{IN} \leq NVDD$ ±10 μΑ  $I_{IN}$ RTC\_CLK input current  $0 \text{ V} \leq V_{IN} \leq NVDD$  $I_{IN}$ ±10 μΑ USB\_CLK\_IN input current  $0 \text{ V} \leq V_{IN} \leq NVDD$ ±10  $I_{IN}$ μΑ  $0 \text{ V} \leq V_{IN} \leq NVDD$ USB\_XTAL\_IN input current ±40 μΑ  $I_{IN}$

$I_{IN}$

±10

μΑ

Table 6. SYS CLK IN DC Electrical Characteristics

### 5.2 AC Electrical Characteristics

SATA\_CLK\_IN input current

The primary clock source for the MPC8315E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the clock input (SYS\_CLK\_IN/PCI\_CLK) AC timing specifications for the MPC8315E.

$0 \text{ V} \leq V_{IN} \leq NVDD$

| Parameter/Condition           | Symbol                                    | Min | Typical | Max   | Unit | Note    |

|-------------------------------|-------------------------------------------|-----|---------|-------|------|---------|

| SYS_CLK_IN/PCI_CLK frequency  | f <sub>SYS_CLK_IN</sub>                   | 24  | _       | 66.67 | MHz  | 1, 6, 7 |

| SYS_CLK_IN/PCI_CLK cycle time | tsys_clk_in                               | 15  | _       | 41.6  | ns   | 6       |

| SYS_CLK_IN rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>         | 0.6 | _       | 4     | ns   | 2, 6    |

| PCI_CLK rise and fall time    | t <sub>PCH</sub> , t <sub>PCL</sub>       | 0.6 | 0.8     | 1.2   | ns   | 2       |

| SYS_CLK_IN/PCI_CLK duty cycle | t <sub>KHK</sub> /t <sub>SYS_CLK_IN</sub> | 40  | _       | 60    | %    | 3, 6    |

| SYS_CLK_IN/PCI_CLK jitter     | _                                         | _   | _       | ±150  | ps   | 4, 5, 6 |

Table 7. SYS CLK IN AC Timing Specifications

#### Note:

- 1. **Caution:** The system, core, and security block must not exceed their respective maximum or minimum operating frequencies.

- 2. Rise and fall times for SYS\_CLK\_IN/PCI\_CLK are specified at 20% to 80% of signal swing.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYS\_CLK\_IN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYS\_CLK\_IN drivers with the specified jitter.

- 6. The parameter names PCI\_CLK and PCI\_SYNC\_IN are used interchangeably in this document.

- 7. Spread spectrum is allowed up to 1% down-spread at 33kHz.(max. rate).

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

## 6 RESET Initialization

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8315E.

### 6.1 RESET DC Electrical Characteristics

This table provides the DC electrical characteristics for the RESET pins of the MPC8315E.

**Table 8. RESET Pins DC Electrical Characteristics**

| Characteristic      | Symbol          | Condition Min                                       |      | Max        | Unit |

|---------------------|-----------------|-----------------------------------------------------|------|------------|------|

| Input high voltage  | V <sub>IH</sub> | _                                                   | 2.0  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                                   | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{ V}_{IN} \leq \text{ NVDD}$ | _    | ±5         | μΑ   |

| Output high voltage | V <sub>OH</sub> | $I_{OH} = -8.0 \text{ mA}$                          | 2.4  | _          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                            | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                            | _    | 0.4        | V    |

### 6.2 RESET AC Electrical Characteristics

This table provides the reset initialization AC timing specifications of the MPC8315E.

**Table 9. RESET Initialization Timing Specifications**

| Parameter/Condition                                                                                                                                                   | Min | Max | Unit                     | Note |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|

| Required assertion time of HRESET to activate reset flow                                                                                                              | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Required assertion time of PORESET with stable clock applied to SYS_CLK_IN when the device is in PCI host mode                                                        | 32  | _   | tsys_clk_in              | 2    |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the device is in PCI agent mode                                                      | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| HRESET assertion (output)                                                                                                                                             | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3] and CFG_SYS_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI host mode  | 4   | _   | tsys_clk_in              | 2, 4 |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3] and CFG_SYS_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | _   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Input hold time for POR configuration signals with respect to negation of HRESET                                                                                      | 0   | _   | ns                       | _    |

| Time for the device to turn off POR configuration signals with respect to the assertion of HRESET                                                                     | _   | 4   | ns                       | 3    |

| Time for the device to turn on POR config signals with respect to the negation of HRESET                                                                              | 1   | _   | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

#### **DUART**

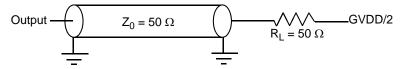

This figure provides the AC test load for the DDR bus.

Figure 9. DDR AC Test Load

### 8 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

### 8.1 DUART DC Electrical Characteristics

This table lists the DC electrical characteristics for the DUART interface.

**Table 21. DUART DC Electrical Characteristics**

| Parameter                                        | Symbol          | Min        | Max        | Unit |

|--------------------------------------------------|-----------------|------------|------------|------|

| High-level input voltage                         | V <sub>IH</sub> | 2.1        | NVDD + 0.3 | V    |

| Low-level input voltage NVDD                     | V <sub>IL</sub> | -0.3       | 0.8        | V    |

| High-level output voltage, $I_{OH} = -100 \mu A$ | V <sub>OH</sub> | NVDD - 0.2 | _          | V    |

| Low-level output voltage, $I_{OL} = 100 \mu A$   | V <sub>OL</sub> | _          | 0.2        | V    |

| Input current (0 V ≤V <sub>IN</sub> ≤ NVDD)      | I <sub>IN</sub> | _          | ± 5        | μΑ   |

## 8.2 DUART AC Electrical Specifications

This table lists the AC timing parameters for the DUART interface.

**Table 22. DUART AC Timing Specifications**

| Parameter         | Value       | Value Unit 256 baud |   |

|-------------------|-------------|---------------------|---|

| Minimum baud rate | 256         | baud                | _ |

| Maximum baud rate | > 1,000,000 | baud                | 1 |

| Oversample rate   | 16          | _                   | 2 |

#### Note:

- 1. Actual attainable baud rate is limited by the latency of interrupt processing.

- 2. The middle of a start bit is detected as the eighth sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each sixteenth sample.

## 9 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

**Ethernet: Three-Speed Ethernet, MII Management**

Table 24. RGMII/RTBI (When Operating at 2.5 V) DC Electrical Characteristics (continued)

|--|

#### Note:

1. The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

### 9.2 MII, RMII, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for MII, RMII, RGMII, and RTBI are presented in this section.

### 9.2.1 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

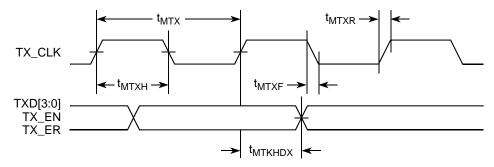

### 9.2.1.1 MII Transmit AC Timing Specifications

This table provides the MII transmit AC timing specifications.

#### Table 25. MII Transmit AC Timing Specifications

At recommended operating conditions with LVDD of 3.3 V  $\pm$  300 mv.

| Parameter/Condition                                                   | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                                           | t <sub>MTX</sub>                    | _   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                                          | t <sub>MTX</sub>                    | _   | 40  | _   | ns   |

| TX_CLK duty cycle                                                     | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay                       | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MTXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>MTXF</sub>                   | 1.0 | _   | 4.0 | ns   |

#### Note:

This figure shows the MII transmit AC timing diagram.

Figure 10. MII Transmit AC Timing Diagram

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

<sup>1.</sup> The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

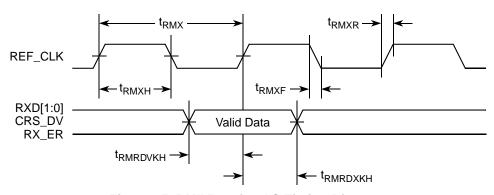

#### Table 28. RMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LVDD of 3.3 V ± 300 mv

| Parameter/Condition                                                    | Symbol <sup>1</sup>  | Min | Тур | Max | Unit |

|------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                          | t <sub>RMRDVKH</sub> | 4.0 | _   | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                           | t <sub>RMRDXKH</sub> | 2.0 | _   | _   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>RMXR</sub>    | 1.0 | _   | 4.0 | ns   |

| REF_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>    | 1.0 | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

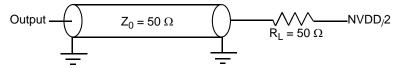

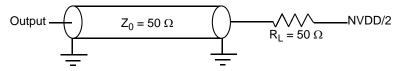

This figure provides the AC test load.

Figure 14. AC Test Load

This figure shows the RMII receive AC timing diagram.

Figure 15. RMII Receive AC Timing Diagram

### 9.2.3 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

Table 29. RGMII and RTBI AC Timing Specifications

At recommended operating conditions (see Table 2)

| Parameter/Condition                                 | Symbol <sup>1</sup> | Min  | Тур | Max | Unit |

|-----------------------------------------------------|---------------------|------|-----|-----|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub>  | -0.6 | _   | 0.6 | ns   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>  | 1.0  | _   | 2.6 | ns   |

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

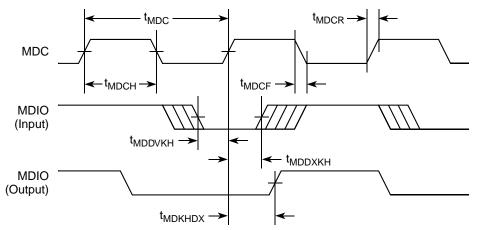

This figure shows the MII management AC timing diagram.

Figure 17. MII Management Interface Timing Diagram

## 9.4 1588 Timer Specifications

This section describes the DC and AC electrical specifications for the 1588 timer.

## 9.4.1 1588 Timer DC Specifications

This table provides the 1588 timer DC specifications.

Characteristic **Symbol** Condition Min Max Unit Output high voltage  $I_{OH} = -8.0 \text{ mA}$  $V_{OH}$ 2.4 ٧ Output low voltage  $I_{OL} = 8.0 \text{ mA}$ V  $V_{OL}$ 0.5 Output low voltage  $V_{OL}$  $I_{OI} = 3.2 \text{ mA}$ 0.4 ٧ Input high voltage  $V_{\mathsf{IH}}$ 2.0 NVDD + 0.3V Input low voltage ٧  $V_{IL}$ -0.38.0 Input current  $0~V \leq V_{IN} \leq NVDD$ ± 5 μΑ  $I_{IN}$

**Table 32. GPIO DC Electrical Characteristics**

## 9.4.2 1588 Timer AC Specifications

This table provides the 1588 timer AC specifications.

Table 33. 1588 Timer AC Specifications

| Parameter                    | Symbol              | Min | Max | Unit | Note |

|------------------------------|---------------------|-----|-----|------|------|

| Timer clock cycle time       | t <sub>TMRCK</sub>  | 0   | 70  | MHz  | 1    |

| Input setup to timer clock   | t <sub>TMRCKS</sub> | _   | _   | _    | 2, 3 |

| Input hold from timer clock  | t <sub>TMRCKH</sub> | _   | _   | _    | 2, 3 |

| Output clock to output valid | t <sub>GCLKNV</sub> | 0   | 6   | ns   |      |

| Timer alarm to output valid  | t <sub>TMRAL</sub>  | _   | _   | _    | 2    |

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

**Ethernet: Three-Speed Ethernet, MII Management**

Table 33. 1588 Timer AC Specifications (continued)

| Parameter | Symbol | Min | Max | Unit | Note |

|-----------|--------|-----|-----|------|------|

|-----------|--------|-----|-----|------|------|

#### Note:

- 1. The timer can operate on rtc\_clock or tmr\_clock. These clocks get muxed and any one of them can be selected.

- 2. Asynchronous signals.

- 3. Inputs need to be stable at least one TMR clock.

#### 9.5 SGMII Interface Electrical Characteristics

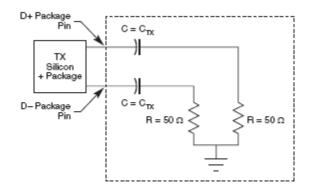

Each SGMII port features a 4-wire AC-Coupled serial link from the dedicated SerDes interface of MPC8315E as shown in Figure 18, where  $C_{TX}$  is the external (on board) AC-Coupled capacitor. Each output pin of the SerDes transmitter differential pair features 50- $\Omega$  output impedance. Each input of the SerDes receiver differential pair features 50- $\Omega$  on-die termination to XCOREVSS. The reference circuit of the SerDes transmitter and receiver is shown in Figure 49.

When an eTSEC port is configured to operate in SGMII mode, the parallel interface's output signals of this eTSEC port can be left floating. The input signals should be terminated based on the guidelines described in Section 26.4, "Connection Recommendations," as long as such termination does not violate the desired POR configuration requirement on these pins, if applicable.

When operating in SGMII mode, the TSEC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD\_REF\_CLK and SD\_REF\_CLK pins.

## 9.5.1 DC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 15, "High-Speed Serial Interfaces (HSSI)."

## 9.5.2 AC Requirements for SGMII SD\_REF\_CLK and SD\_REF\_CLK

This table lists the SGMII SerDes reference clock AC requirements. Please note that SD\_REF\_CLK and SD\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

Table 34. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

| Symbol             | Parameter Description                                                                    | Min             | Typical | Max | Unit | Note |

|--------------------|------------------------------------------------------------------------------------------|-----------------|---------|-----|------|------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | _               | 8       | _   | ns   | _    |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |                 | 1       | 100 | ps   | _    |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | <del>-</del> 50 |         | 50  | ps   | _    |

#### 9.5.3 SGMII Transmitter and Receiver DC Electrical Characteristics

Table 35 and Table 36 describe the SGMII SerDes transmitter and receiver AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs (SD\_TX[n]) and SD\_TX[n]) as depicted in Figure 17.

| Parameter                             | Symbol                | Min | Тур                   | Max | Unit | Note |

|---------------------------------------|-----------------------|-----|-----------------------|-----|------|------|

| Input AC common mode voltage          | V <sub>CM_ACp-p</sub> | _   | _                     | 100 | mV   | 5    |

| Receiver differential input impedance | Z <sub>RX_DIFF</sub>  | 80  | 100                   | 120 | Ω    | _    |

| Receiver common mode input impedance  | Z <sub>RX_CM</sub>    | 20  | _                     | 35  | Ω    | _    |

| Common mode input voltage             | V <sub>CM</sub>       | _   | V <sub>xcorevss</sub> | _   | V    | 6    |

#### Note:

- 1. Input must be externally AC-coupled.

- 2. V<sub>RX DIFFp-p</sub> is also referred to as peak to peak input differential voltage

- 3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in PCI Express. Refer to PCI Express Differential Receiver (RX) Input Specifications section for further explanation.

- 4. The EQ shown in the table refers to the RXEQA or RXEQE bit field of MPC8315E's SerDes Control Register 0.

- 5.  $V_{CM\ ACp-p}$  is also referred to as peak to peak AC common mode voltage.

- 6. On-chip termination to XCOREVSS.

### 9.5.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs  $(TX[n] \text{ and } \overline{TX}[n])$  or at the receiver inputs  $(RX[n] \text{ and } \overline{RX}[n])$  as depicted in Figure 21 respectively.

### 9.5.4.1 SGMII Transmit AC Timing Specifications

This table provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

#### **Table 37. SGMII Transmit AC Timing Specifications**

At recommended operating conditions with XCOREVDD =  $1.0V \pm 5\%$ .

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Note |

|-------------------------------------|-------------------|--------|-----|--------|--------|------|

| Deterministic Jitter                | JD                | _      | _   | 0.17   | UI p-p | _    |

| Total Jitter                        | JT                | _      | _   | 0.35   | UI p-p | _    |

| Unit Interval                       | UI                | 799.92 | 800 | 800.08 | ps     | _    |

| V <sub>OD</sub> fall time (80%-20%) | tfall             | 50     | _   | 120    | ps     | _    |

| V <sub>OD</sub> rise time (20%-80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _    |

#### Note:

1. Each UI is 800 ps ± 100 ppm.

## 9.5.4.2 SGMII Receive AC Timing Specifications

This table provides the SGMII receive AC timing specifications. Source synchronous clocking is not supported. Clock is recovered from the data. Figure 20 shows the SGMII Receiver Input Compliance Mask eye diagram.

Figure 21. SGMII AC Test/Measurement Load

### **10 USB**

### 10.1 USB Dual-Role Controllers

This section provides the AC and DC electrical specifications for the USB-ULPI interface.

#### 10.1.1 USB DC Electrical Characteristics

This table lists the DC electrical characteristics for the USB interface.

Table 39, USB DC Electrical Characteristics

| Parameter                                        | Symbol          | Min        | Max        | Unit |

|--------------------------------------------------|-----------------|------------|------------|------|

| High-level input voltage                         | V <sub>IH</sub> | 2          | LVDD + 0.3 | V    |

| Low-level input voltage                          | V <sub>IL</sub> | -0.3       | 0.8        | V    |

| Input current                                    | I <sub>IN</sub> | _          | ±5         | μΑ   |

| High-level output voltage, $I_{OH} = -100 \mu A$ | V <sub>OH</sub> | LVDD - 0.2 | _          | V    |

| Low-level output voltage, $I_{OL} = 100 \mu A$   | V <sub>OL</sub> | _          | 0.2        | V    |

#### Note:

## 10.1.2 USB AC Electrical Specifications

This table lists the general timing parameters of the USB-ULPI interface.

**Table 40. USB General Timing Parameters**

| Parameter                           | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|-------------------------------------|---------------------|-----|-----|------|------|

| USB clock cycle time                | t <sub>USCK</sub>   | 15  | _   | ns   | 1, 2 |

| Input setup to USB clock—all inputs | t <sub>USIVKH</sub> | 4   | _   | ns   | 1, 4 |

| Input hold to USB clock—all inputs  | t <sub>USIXKH</sub> | 1   | _   | ns   | 1, 4 |

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

<sup>1.</sup> The symbol  $V_{IN}$ , in this case, represents the  $NV_{IN}$  symbol referenced in Table 1 and Table 2.

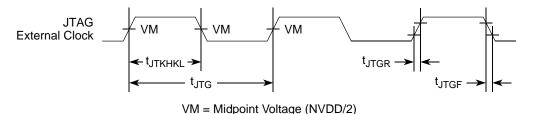

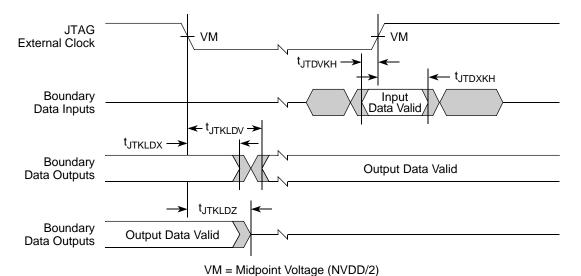

## 12.2 JTAG AC Timing Specifications

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface. This table provides the JTAG AC timing specifications as defined in Figure 29 through Figure 32.

Table 46. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN) 1

At recommended operating conditions (see Table 2)

| Parameter                                                             | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Note |

|-----------------------------------------------------------------------|--------------------------------------------|----------|----------|------|------|

| JTAG external clock frequency of operation                            | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | _    |

| JTAG external clock cycle time                                        | t <sub>JTG</sub>                           | 30       | _        | ns   | _    |

| JTAG external clock pulse width measured at 1.4 V                     | t <sub>JTKHKL</sub>                        | 15       | _        | ns   | _    |

| JTAG external clock rise and fall times                               | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | _    |

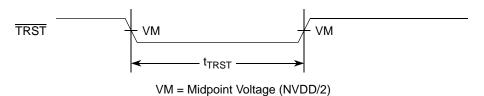

| TRST assert time                                                      | t <sub>TRST</sub>                          | 25       | _        | ns   | 3    |

| Input setup times:  Boundary-scan data TMS, TDI                       |                                            | 4<br>4   | _        | ns   | 4    |

| Input hold times:  Boundary-scan data TMS, TDI                        |                                            | 10<br>10 | _        | ns   | 4    |

| Valid times:  Boundary-scan data TDO                                  | t <sub>JTKLDV</sub>                        | 2<br>2   | 11<br>11 | ns   | 5    |

| Output hold times:  Boundary-scan data TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 2<br>2   | _        | ns   | 5    |

| JTAG external clock to output high impedance:  Boundary-scan data TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 2<br>2   | 19<br>9  | ns   | 5, 6 |

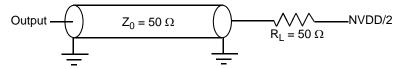

#### Note:

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question.

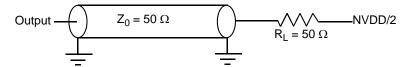

The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Table 28).

Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design and characterization.

**JTAG**

This figure provides the AC test load for TDO and the boundary-scan outputs of the MPC8315E.

Figure 28. AC Test Load for the JTAG Interface

This figure provides the JTAG clock input timing diagram.

Figure 29. JTAG Clock Input Timing Diagram

This figure provides the  $\overline{TRST}$  timing diagram.

Figure 30. TRST Timing Diagram

This figure provides the boundary-scan timing diagram.

Figure 31. Boundary-Scan Timing Diagram

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

PCI

Table 50. PCI AC Timing Specifications at 66 MHz (continued)

| Parameter             | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|-----------------------|---------------------|-----|-----|------|------|

| Input hold from clock | t <sub>PCIXKH</sub> | 0   | _   | ns   | 2, 4 |

#### Note:

- 1. Note that the symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

This table shows the PCI AC Timing Specifications at 33 MHz.

Table 51. PCI AC Timing Specifications at 33 MHz

| Parameter                      | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|--------------------------------|---------------------|-----|-----|------|------|

| Clock to output valid          | t <sub>PCKHOV</sub> | _   | 11  | ns   | 2    |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | _   | ns   | 2    |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | _   | 14  | ns   | 2, 3 |

| Input setup to clock           | t <sub>PCIVKH</sub> | 4.0 | _   | ns   | 2, 4 |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | _   | ns   | 2, 4 |

#### Note:

- 1. Note that the symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

- 2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

This figure provides the AC test load for PCI.

Figure 35. PCI AC Test Load

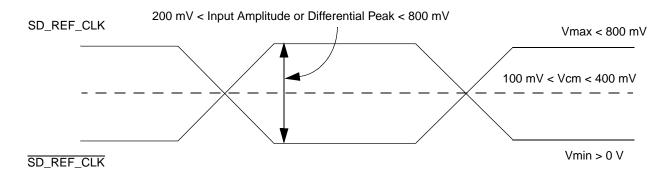

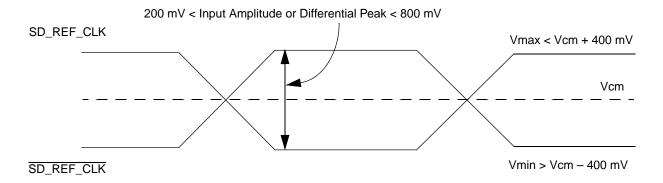

- between 100 mV and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to XCOREVSS. Each signal wire of the differential inputs is allowed to swing below and above the common mode voltage (XCOREVSS). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

#### Single-ended Mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400mV and 800mV peak-peak (from Vmin to Vmax) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

Figure 41. Differential Reference Clock Input DC Requirements (External AC-Coupled)

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

### 15.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15MHz is filtered by the PLL. The most problematic phase noise occurs in the 1-15MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters common to SGMII and PCI Express protocols.

Table 52. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with XCOREVDD=  $1.0V \pm 5\%$

| Parameter                                                                  | Symbol                | Min  | Max  | Unit | Note |

|----------------------------------------------------------------------------|-----------------------|------|------|------|------|

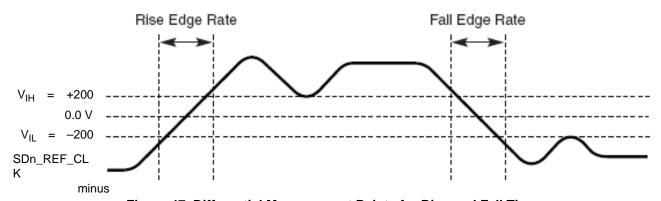

| Rising Edge Rate                                                           | Rise Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3 |

| Falling Edge Rate                                                          | Fall Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3 |

| Differential Input High Voltage                                            | V <sub>IH</sub>       | +200 | _    | mV   | 2    |

| Differential Input Low Voltage                                             | V <sub>IL</sub>       | _    | -200 | mV   | 2    |

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-Fall<br>Matching | _    | 20   | %    | 1, 4 |

#### Note:

- 1. Measurement taken from single ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from -200 mV to +200 mV on the differential waveform (derived from SDn\_REF\_CLK minus SDn\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 47.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of SDn\_REF\_CLK should be compared to the Fall Edge Rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 48.

Figure 47. Differential Measurement Points for Rise and Fall Time

**IPIC**

This figure provides the AC test load for the GPIO.

Figure 55. GPIO AC Test Load

### **20 IPIC**

This section describes the DC and AC electrical specifications for the external interrupt pins of the MPC8315E.

### 20.1 IPIC DC Electrical Characteristics

This table provides the DC electrical characteristics for the external interrupt pins.

Characteristic **Symbol** Condition Min Max Unit ٧ Input high voltage  $V_{IH}$ 2.1 NVDD + 0.3Input low voltage  $V_{\mathsf{IL}}$ -0.38.0 ٧ Input current ±5 μΑ  $I_{IN}$ Output high voltage  $V_{OH}$  $I_{OH} = -8.0 \text{ mA}$ 2.4 V Output low voltage  $I_{OL} = 8.0 \text{ mA}$ V  $V_{OL}$ 0.5 Output low voltage  $I_{OL} = 3.2 \text{ mA}$ 0.4 V  $V_{OL}$

**Table 64. IPIC DC Electrical Characteristics**

## 20.2 IPIC AC Timing Specifications

This table provides the IPIC input and output AC timing specifications.

**Table 65. IPIC Input AC Timing Specifications**

| Characteristic                  | Symbol <sup>1</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| IPIC inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

#### Note:

IPIC inputs and outputs are asynchronous to any visible clock. IPIC outputs should be synchronized before use by any

external synchronous logic. IPIC inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation when

working in edge triggered mode.

## 21 SPI

This section describes the DC and AC electrical specifications for the SPI of the MPC8315E.

#### Package and Pin Listings

This figure shows the TDM transmit signal timing.

Figure 60. TDM Transmit Signals

# 23 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8315E is available in a thermally enhanced plastic ball grid array (TEPBGA II), see Section 23.1, "Package Parameters for the MPC8315E TEPBGA II," and Section 23.2, "Mechanical Dimensions of the TEPBGA II," for information on the TEPBGA II.

## 23.1 Package Parameters for the MPC8315E TEPBGA II

The package parameters are as provided in the following list. The package type is  $29 \text{ mm} \times 29 \text{ mm}$ , TEPBGA II.

Package outline  $29 \text{ mm} \times 29 \text{ mm}$

Interconnects 620

Pitch 1 mm

Module height (typical) 2.23 mm

Solder balls 96.5 Sn/3.5 Ag (VR package)

Ball diameter (typical) 0.6 mm

#### Package and Pin Listings

### Table 70. MPC8315E TEPBGA II Pinout Listing (continued)

| Signal                           | Package Pin Number      | Pin Type | Power<br>Supply | Note |

|----------------------------------|-------------------------|----------|-----------------|------|

| ·                                | ETSEC2                  |          |                 |      |

| GPIO_26/TSEC2_COL                | A8                      | I/O      | LVDD2_ON        | _    |

| GPIO_27/TSEC2_CRS                | E9                      | I/O      | LVDD2_ON        | _    |

| TSEC2_GTX_CLK                    | B10                     | 0        | LVDD2_ON        | _    |

| TSEC2_RX_CLK                     | B8                      | I        | LVDD2_ON        | _    |

| TSCE2_RX_DV                      | C9                      | 1        | LVDD2_ON        | _    |

| TSEC2_RXD[3]                     | C10                     | I        | LVDD2_ON        | _    |

| TSEC2_RXD[2]                     | D10                     | 1        | LVDD2_ON        | _    |

| TSEC2_RXD[1]                     | A9                      | I        | LVDD2_ON        | _    |

| TSEC2_RXD[0]                     | B9                      | I        | LVDD2_ON        | _    |

| TSEC2_RX_ER                      | A10                     | I        | LVDD2_ON        | _    |

| TSEC2_TX_CLK                     | D8                      | I        | LVDD2_ON        | _    |

| TSEC2_TXD[3]/CFG_RESET_SOURCE[0] | D11                     | I/O      | LVDD2_ON        | _    |

| TSEC2_TXD[2]/CFG_RESET_SOURCE[1] | C7                      | I/O      | LVDD2_ON        | _    |

| TSEC2_TXD[1]/CFG_RESET_SOURCE[2] | E8                      | I/O      | LVDD2_ON        | _    |

| TSEC2_TXD[0]/CFG_RESET_SOURCE[3] | B7                      | I/O      | LVDD2_ON        | _    |

| TSEC2_TX_EN                      | D12                     | 0        | LVDD2_ON        | _    |

| TSEC2_TX_ER                      | B11                     | 0        | LVDD2_ON        | _    |

|                                  | SGMII / PCI Express PHY |          |                 |      |

| TXA                              | P4                      | 0        | XPADVDD         | _    |

| TXA                              | N4                      | 0        | XPADVDD         | _    |

| RXA                              | R1                      | I        | XCOREVDD        | _    |

| RXA                              | P1                      | I        | XCOREVDD        | _    |

| TXB                              | U4                      | 0        | XPADVDD         | _    |

| TXB                              | V4                      | 0        | XPADVDD         | _    |

| RXB                              | U1                      | 1        | XCOREVDD        | _    |

| RXB                              | V1                      | I        | XCOREVDD        | _    |

| SD_IMP_CAL_RX                    | N3                      | I        | XCOREVDD        | _    |

| SD_REF_CLK                       | R4                      | I        | XCOREVDD        | _    |

| SD_REF_CLK                       | R5                      | 1        | XCOREVDD        | _    |

| SD_PLL_TPD                       | T2                      | 0        | _               | _    |

| SD_IMP_CAL_TX                    | V5                      | 1        | XPADVDD         | _    |

| SDAVDD                           | T3                      | 1        | _               | _    |

| SD_PLL_TPA_ANA                   | T4                      | 0        | _               | _    |

| SDAVSS                           | T5                      | 1        | _               | _    |

|                                  | USB Phy                 |          |                 |      |

MPC8315E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2