Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

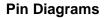

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga406-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.1.4 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ256GA412/GB412 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) nominal 8 MHz output with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

#### 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, while still selecting a Microchip device.

### 1.2 Cryptographic Engine

The Cryptographic Engine provides a new set of data security options. Using its own free-standing math engine, the module can independently perform NIST standard encryption and decryption of data, independently of the CPU. The Cryptographic Engine supports AES and DES/3DES encryption ciphers in up to 5 modes, and supports key lengths from 128 to 256 bits. Additional features include True Random Number Generation (TRNG) within the engine, multiple encryption/decryption key storage options and secure data handling that prevents data in the engine from being compromised by external reads.

### 1.3 USB On-The-Go (OTG)

USB On-The-Go provides on-chip functionality as a target device compatible with the USB 2.0 standard, as well as limited stand-alone functionality as a USB embedded host. By implementing USB Host Negotiation Protocol (HNP), the module can also dynamically switch between device and host operation, allowing for a much wider range of versatile USB-enabled applications on a microcontroller platform.

PIC24FJ256GA412/GB412 family devices also incorporate an integrated USB transceiver and precision oscillator, minimizing the required complexity of implementing a complete USB device, embedded host, dual role or On-The-Go application.

### 1.4 DMA Controller

PIC24FJ256GA412/GB412 family devices also add a Direct Memory Access (DMA) Controller to the existing PIC24F architecture. The DMA acts in concert with the CPU, allowing data to move between data memory and peripherals without the intervention of the CPU, increasing data throughput and decreasing execution time overhead. Six independently programmable channels make it possible to service multiple peripherals at virtually the same time, with each channel peripheral performing a different operation. Many types of data transfer operations are supported.

#### 1.5 LCD Controller

The versatile on-chip LCD Controller includes many features that make the integration of displays in low-power applications easier. These include an integrated voltage regulator with charge pump and an integrated internal resistor ladder that allows contrast control in software, and display operation above device VDD.

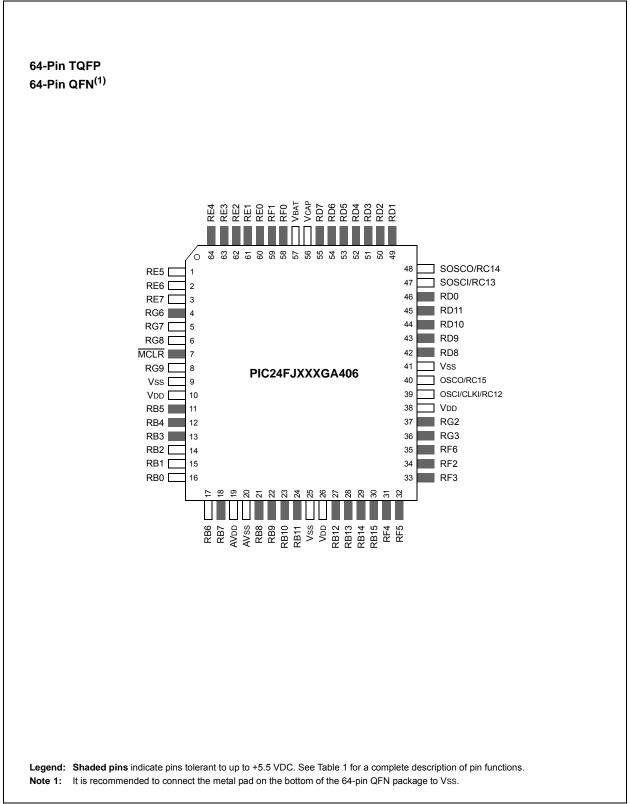

| TABLE 4-1: | PROGRAM MEMORY SIZES AND BOUNDARIES |

|------------|-------------------------------------|

|------------|-------------------------------------|

|                 | Program Memory   | / Upper Boundary (I       |                    |                                |                                |

|-----------------|------------------|---------------------------|--------------------|--------------------------------|--------------------------------|

| Device          | Single Partition | Dual Partition Flash Mode |                    | Write<br>Blocks <sup>(1)</sup> | Erase<br>Blocks <sup>(1)</sup> |

|                 | Flash Mode       | Active Partition          | Inactive Partition |                                |                                |

| PIC24FJ256GX4XX | 02AFFEh (88K)    | 0157FEh(44K)              | 0157FEh(44K)       | 1376                           | 172                            |

| PIC24FJ128GX4XX | 0157FEh(44K)     | 00ABFEh (22K)             | 00ABFEh (22K)      | 688                            | 86                             |

| PIC24FJ64GX4XX  | 00AFFEh (22K)    | 0057FEh (11K)             | 0057FEh (11K)      | 352                            | 44                             |

Note 1: One Write Block = 64 Instruction Words; One Erase Block = 512 Instruction Words.

The Boot Sequence Configuration Words (FBTSEQ) determine whether Partition 1 or Partition 2 will be active after Reset. If the part is operating in Dual Partition mode, the partition with the lower boot sequence number will operate as the Active Panel (FBTSEQ is unused in Single Partition mode). The partitions can be switched between Active and Inactive by reprogramming their boot sequence numbers, but the Active Partition will not change until a device Reset is performed. If both boot sequence numbers are the same, or if both are corrupted, the part will use Partition 1 as the Active Partition. If only one boot sequence number is corrupted, the device will use the partition without a corrupted boot sequence number as the Active Partition.

The user can also change which partition is active at run time using the BOOTSWP instruction. Issuing a BOOTSWP instruction does not affect which partition will be the Active Partition after a Reset. Figure 4-4 demonstrates how the relationship between Partitions 1 and 2, shown in red and blue, respectively, and the Active and Inactive Partitions are affected by reprogramming the boot sequence number or issuing a BOOTSWP instruction.

The P2ACTIV bit (NVMCON<10>) can be used to determine which physical partition is the Active Partition. If P2ACTIV = 1, Partition 2 is active; if P2ACTIV = 0, Partition 1 is active.

## 4.4.3 READING DATA FROM PROGRAM MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> decides which word should be addressed; when the bit is '0', the lower word and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported. Table 4-16 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV, and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| DSRPAGSource Address While(Data Space Read Register)Indirect Addressing |                | 23-Bit EA Pointing<br>to EDS | Comment                           |  |

|-------------------------------------------------------------------------|----------------|------------------------------|-----------------------------------|--|

| 200h                                                                    |                | 000000h to 007FFEh           | Lower words of 4M program         |  |

| •                                                                       |                | •                            | instructions; (8 Mbytes) for      |  |

| •                                                                       |                | •                            | read operations only              |  |

| •                                                                       |                | •                            |                                   |  |

| 2FFh                                                                    |                | 7F8000h to 7FFFFEh           |                                   |  |

| 300h                                                                    | 8000h to FFFFh | 000001h to 007FFFh           | Upper words of 4M program         |  |

| •                                                                       |                | •                            | instructions (4 Mbytes remaining, |  |

| •                                                                       |                | •                            | 4 Mbytes are phantom bytes); for  |  |

| •                                                                       |                | •                            | read operations only              |  |

| 3FFh                                                                    |                | 7F8001h to 7FFFFFh           |                                   |  |

| 000h                                                                    |                | Invalid Address              | Address error trap <sup>(1)</sup> |  |

TABLE 4-16: EDS PROGRAM ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

**Note 1:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

| ; Set the  | EDS page from where the dat | a to be read                                              |

|------------|-----------------------------|-----------------------------------------------------------|

|            | #0x0202, w0                 |                                                           |

| mov        | w0, DSRPAG                  | ;page 0x202, consisting lower words, is selected for read |

| mov        | #0x000A, w1                 | ;select the location (0x0A) to be read                    |

| bset       | w1, #15                     | ;set the MSB of the base address, enable EDS mode         |

| ;Read a by | te from the selected locati | on                                                        |

| mov.b      | [w1++], w2                  | ;read Low byte                                            |

| mov.b      | [w1++], w3                  | ;read High byte                                           |

| ;Read a wo | rd from the selected locati | on                                                        |

| mov        | [w1], w2                    | ;                                                         |

| ;Read Doub | le - word from the selected | location                                                  |

| mov.d      | [w1], w2                    | ;two word read, stored in w2 and w3                       |

|            |                             |                                                           |

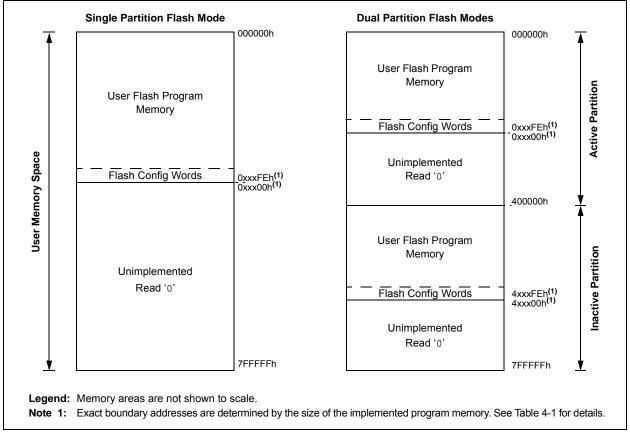

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLES

#### TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source            |

|---------------|-------------|--------------|------------------------|

| 0             | 000004h     | BOA+04h      | Oscillator Failure     |

| 1             | 000006h     | BOA+06h      | Address Error          |

| 2             | 000008h     | BOA+08h      | General Hardware Error |

| 3             | 00000Ah     | BOA+0Ah      | Stack Error            |

| 4             | 00000Ch     | BOA+0Ch      | Math Error             |

| 5             | 00000Eh     | BOA+0Eh      | Reserved               |

| 6             | 000010h     | BOA+10h      | General Software Error |

| 7             | 000012h     | BOA+12h      | Reserved               |

**Legend:** BOA = Base Offset Address for AIVT segment, which is the starting address of the last page of the Boot Segment.

#### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(1)</sup> | —   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit     |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-2 for bit description.

| R/W-0         | R/W-0                                 | R/W-0                                               | R/W-0                      | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

|---------------|---------------------------------------|-----------------------------------------------------|----------------------------|-------------------|------------------|-----------------|----------|

| CCP1IF        | RTCIF                                 | DMA5IF                                              | SPI3RXIF                   | SPI2RXIF          | SPI1RXIF         | SPI4RXIF        | KEYSTRIF |

| bit 15        | ·                                     |                                                     | -                          |                   | ÷                |                 | bit 8    |

| R/W-0         | R/W-0                                 | R/W-0                                               | U-0                        | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

| CRYDNIF       | INT4IF                                | INT3IF                                              | _                          | CCT7IF            | MI2C2IF          | SI2C2IF         | CCT6IF   |

| bit 7         |                                       |                                                     |                            |                   |                  |                 | bit C    |

| Legend:       |                                       |                                                     |                            |                   |                  |                 |          |

| R = Readable  | e bit                                 | W = Writable                                        | bit                        | U = Unimplem      | nented bit, read | as '0'          |          |

| -n = Value at | POR                                   | '1' = Bit is set                                    |                            | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |

| bit 15        | 1 = Interrupt r                       | CP1 Capture/C<br>request has occ<br>request has not |                            | ot Flag Status b  | it               |                 |          |

| bit 14        | 1 = Interrupt r                       | Time Clock and<br>equest has occ<br>equest has not  |                            | rupt Flag Statu   | s bit            |                 |          |

| bit 13        | 1 = Interrupt r                       | A Channel 5 In<br>equest has occ<br>equest has not  |                            | tus bit           |                  |                 |          |

| bit 12        | SPI3RXIF: SF<br>1 = Interrupt r       | •                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 11        | SPI2RXIF: SF<br>1 = Interrupt r       | •                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 10        | SPI1RXIF: SF<br>1 = Interrupt r       | -                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 9         | SPI4RXIF: SF<br>1 = Interrupt r       | -                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 8         | <b>KEYSTRIF:</b> C<br>1 = Interrupt r | -                                                   | ey Store Progra            | am Done Interru   | upt Flag Status  | bit             |          |

| bit 7         | CRYDNIF: Cr<br>1 = Interrupt r        |                                                     | peration Done Ir           | nterrupt Flag St  | atus bit         |                 |          |

| bit 6         | INT4IF: Exter<br>1 = Interrupt r      | •                                                   | Flag Status bit<br>curred  |                   |                  |                 |          |

| bit 5         | INT3IF: Exter                         | •                                                   | Flag Status bit<br>curred  |                   |                  |                 |          |

| bit 4         | Unimplemen                            | ted: Read as '                                      | 0'                         |                   |                  |                 |          |

| bit 3         |                                       | P7 Timer Inter                                      | rupt Flag Status<br>curred | s bit             |                  |                 |          |

|               |                                       | request has not                                     |                            |                   |                  |                 |          |

|               |                                       |                                                     |                            |                   |                  |                 |          |

#### REGISTER 8-9: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| R/W-0           | R/W-0                                                                                              | R/W-0                               | R/W-0           | R/W-0             | R/W-0          | R/W-0           | R/W-0  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-------------------|----------------|-----------------|--------|--|--|--|

| CCP4IE          | CCP3IE                                                                                             | SPI4TXIE                            | SPI4IE          | SPI3TXIE          | SPI3IE         | U4TXIE          | U4RXIE |  |  |  |

| bit 15          | •                                                                                                  | •                                   |                 |                   |                |                 | bit 8  |  |  |  |

| <b>D</b> 444.0  | DAALO                                                                                              | DAALO                               | DAALO           | DAVA              | <b>D</b> 444.0 | DAMA            |        |  |  |  |

| R/W-0           | R/W-0                                                                                              | R/W-0                               | R/W-0           | R/W-0             | R/W-0          | R/W-0           | U-0    |  |  |  |

| U4ERIE          | USB1IE                                                                                             | I2C2BCIE                            | I2C1BCIFE       | U3TXIE            | U3RXIE         | U3ERIE          | —      |  |  |  |

| bit 7           |                                                                                                    |                                     |                 |                   |                |                 | bit (  |  |  |  |

| Legend:         |                                                                                                    |                                     |                 |                   |                |                 |        |  |  |  |

| R = Readable    | bit                                                                                                | W = Writable                        | bit             | U = Unimplem      | ented bit, rea | d as '0'        |        |  |  |  |

| -n = Value at I | POR                                                                                                | '1' = Bit is set                    |                 | '0' = Bit is clea | red            | x = Bit is unkr | nown   |  |  |  |

|                 |                                                                                                    |                                     |                 |                   |                |                 |        |  |  |  |

| bit 15          |                                                                                                    | P4 Capture/Co                       |                 | t Enable bit      |                |                 |        |  |  |  |

|                 |                                                                                                    | request is enat<br>request is not e |                 |                   |                |                 |        |  |  |  |

| bit 14          | •                                                                                                  | P3 Capture/Co                       |                 | t Enable bit      |                |                 |        |  |  |  |

|                 |                                                                                                    | request is enat                     |                 |                   |                |                 |        |  |  |  |

|                 |                                                                                                    | request is not e                    |                 |                   |                |                 |        |  |  |  |

| bit 13          | SPI4TXIE: SPI4 Transmit Interrupt Enable bit                                                       |                                     |                 |                   |                |                 |        |  |  |  |

|                 | 1 = Interrupt request is enabled                                                                   |                                     |                 |                   |                |                 |        |  |  |  |

|                 | 0 = Interrupt request is not enabled                                                               |                                     |                 |                   |                |                 |        |  |  |  |

| bit 12          | SPI4IE: SPI4 General Interrupt Enable bit                                                          |                                     |                 |                   |                |                 |        |  |  |  |

|                 | <ol> <li>Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>     |                                     |                 |                   |                |                 |        |  |  |  |

| bit 11          | SPI3TXIE: SPI3 Transmit Interrupt Enable bit                                                       |                                     |                 |                   |                |                 |        |  |  |  |

|                 | 1 = Interrupt request is enabled                                                                   |                                     |                 |                   |                |                 |        |  |  |  |

|                 | 0 = Interrupt request is not enabled                                                               |                                     |                 |                   |                |                 |        |  |  |  |

| bit 10          | SPI3IE: SPI3                                                                                       | General Interru                     | upt Enable bit  |                   |                |                 |        |  |  |  |

|                 | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                     |                 |                   |                |                 |        |  |  |  |

| bit 9           | •                                                                                                  | T4 Transmitter                      |                 | le hit            |                |                 |        |  |  |  |

| DIL 9           |                                                                                                    | request is enat                     |                 |                   |                |                 |        |  |  |  |

|                 |                                                                                                    | request is not e                    |                 |                   |                |                 |        |  |  |  |

| bit 8           | U4RXIE: UAF                                                                                        | RT4 Receiver Ir                     | nterrupt Enable | bit               |                |                 |        |  |  |  |

|                 |                                                                                                    | request is enat                     |                 |                   |                |                 |        |  |  |  |

|                 | -                                                                                                  | request is not e                    |                 |                   |                |                 |        |  |  |  |

| bit 7           |                                                                                                    | RT4 Error Interr                    | -               |                   |                |                 |        |  |  |  |

|                 |                                                                                                    | request is enab                     |                 |                   |                |                 |        |  |  |  |

| bit 6           | 0 = Interrupt request is not enabled                                                               |                                     |                 |                   |                |                 |        |  |  |  |

|                 | USB1IE: USB1 (USB OTG) Interrupt Enable bit<br>1 = Interrupt request is enabled                    |                                     |                 |                   |                |                 |        |  |  |  |

|                 | •                                                                                                  | request is not e                    |                 |                   |                |                 |        |  |  |  |

| bit 5           | 12C2BCIE: 12                                                                                       | C2 Bus Collisio                     | n Interrupt Ena | able bit          |                |                 |        |  |  |  |

|                 | -                                                                                                  | request is enat                     |                 |                   |                |                 |        |  |  |  |

|                 | •                                                                                                  | request is not e                    |                 |                   |                |                 |        |  |  |  |

|                 |                                                                                                    |                                     |                 |                   |                |                 |        |  |  |  |

| bit 4           |                                                                                                    | C1 Bus Collisic<br>request is enat  | -               | able bit          |                |                 |        |  |  |  |

#### REGISTER 8-19: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| R/W-0        | U-0                                                                                                                                                                                                | U-0              | R/W-0            | R/W-0                                 | U-0             | U-0                  | U-0       |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|---------------------------------------|-----------------|----------------------|-----------|--|--|--|

| DSEN         | —                                                                                                                                                                                                  | —                | RTCCMD           | KEYRAMEN                              | —               | _                    | _         |  |  |  |

| bit 15       |                                                                                                                                                                                                    |                  |                  |                                       |                 |                      | bit 8     |  |  |  |

|              |                                                                                                                                                                                                    |                  |                  |                                       | <b>D</b> # 44 0 |                      |           |  |  |  |

| U-0          | U-0                                                                                                                                                                                                | U-0              | U-0              | U-0                                   | R/W-0           | R/W-0                | R/C-0, HS |  |  |  |

|              | —                                                                                                                                                                                                  | —                |                  | —                                     | WAKEDIS         | DSBOR <sup>(2)</sup> | RELEASE   |  |  |  |

| bit 7        |                                                                                                                                                                                                    |                  |                  |                                       |                 |                      | bit (     |  |  |  |

| Legend:      |                                                                                                                                                                                                    | C = Clearable    | bit              | HS = Hardwar                          | e Settable bit  |                      |           |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                             | W = Writable     | bit              | U = Unimplem                          | ented bit, read | as '0'               |           |  |  |  |

| -n = Value a | t POR                                                                                                                                                                                              | '1' = Bit is set |                  | '0' = Bit is clea                     | red             | x = Bit is unkr      | nown      |  |  |  |

| bit 14-13    | 0 = Enters no                                                                                                                                                                                      | rmal Sleep on    | execution of PI  |                                       |                 |                      |           |  |  |  |

|              |                                                                                                                                                                                                    |                  |                  |                                       |                 |                      |           |  |  |  |

| bit 14-13    | -                                                                                                                                                                                                  | ted: Read as '   |                  |                                       |                 |                      |           |  |  |  |

| bit 12       |                                                                                                                                                                                                    | CC Module Di     | sable bit        |                                       |                 |                      |           |  |  |  |

|              | <ol> <li>Module is disabled</li> <li>Module power and clock sources are enabled</li> </ol>                                                                                                         |                  |                  |                                       |                 |                      |           |  |  |  |

| bit 11       | •                                                                                                                                                                                                  |                  |                  | AM Deep Sleep                         | Enable bit      |                      |           |  |  |  |

|              | 1 = Power is r                                                                                                                                                                                     | maintained to k  | Key RAM during   | g Deep Sleep al<br>Ind VBAT modes     | nd VBAT modes   | i                    |           |  |  |  |

| bit 10-3     |                                                                                                                                                                                                    | ted: Read as '   |                  |                                       |                 |                      |           |  |  |  |

| bit 2        | WAKEDIS: EX                                                                                                                                                                                        | kternal Wake-u   | ip Source Disa   | ble bit                               |                 |                      |           |  |  |  |

|              |                                                                                                                                                                                                    |                  |                  | nd ignored durin<br>Id can be used t  | <b>v</b> , ,    |                      | an        |  |  |  |

| bit 1        |                                                                                                                                                                                                    | p Sleep BOR E    |                  |                                       |                 |                      | γ         |  |  |  |

|              |                                                                                                                                                                                                    |                  |                  | ent was detecte                       | d during Deep S | Sleep                |           |  |  |  |

|              | <ul> <li>1 = The DSBOR was active and a BOR event was detected during Deep Sleep</li> <li>0 = The DSBOR was not active, or was active, but did not detect a BOR event during Deep Sleep</li> </ul> |                  |                  |                                       |                 |                      |           |  |  |  |

| bit 0        | RELEASE: 1/0                                                                                                                                                                                       | O Pin State Re   | lease bit        |                                       |                 |                      |           |  |  |  |

|              | 0 = Releases                                                                                                                                                                                       |                  | their state prev | is maintain their<br>ious to Deep Sle |                 |                      |           |  |  |  |

|              | Il register bits ar                                                                                                                                                                                |                  |                  | POR event outsig                      | •               | •                    |           |  |  |  |

### REGISTER 10-1: DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

2: Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms the POR.

| REGISTER      | 14-6: CCPx                                                                                                                                                                                | CON3H: CC                            | Px CONTRO                         | L 3 HIGH RE      | GISTERS              |                        |                        |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|------------------|----------------------|------------------------|------------------------|--|--|--|

| R/W-0         | R/W-0                                                                                                                                                                                     | R/W-0                                | R/W-0                             | U-0              | R/W-0                | R/W-0                  | R/W-0                  |  |  |  |

| OETRIG        | OSCNT2                                                                                                                                                                                    | OSCNT1                               | OSCNT0                            | —                | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>   |  |  |  |

| bit 15        |                                                                                                                                                                                           |                                      |                                   |                  |                      |                        | bit 8                  |  |  |  |

| U-0           | U-0                                                                                                                                                                                       | R/W-0                                | R/W-0                             | R/W-0            | R/W-0                | R/W-0                  | R/W-0                  |  |  |  |

|               | _                                                                                                                                                                                         | POLACE                               | POLBDF <sup>(1)</sup>             | PSSACE1          | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                           |                                      |                                   |                  |                      |                        | bit (                  |  |  |  |

| Legend:       |                                                                                                                                                                                           |                                      |                                   |                  |                      |                        |                        |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                                     | W = Writable                         | bit                               | U = Unimplen     | nented bit, rea      | d as '0'               |                        |  |  |  |

| -n = Value at | POR                                                                                                                                                                                       | '1' = Bit is set                     |                                   | '0' = Bit is cle |                      | x = Bit is unkr        | nown                   |  |  |  |

|               | -                                                                                                                                                                                         |                                      |                                   |                  |                      |                        |                        |  |  |  |

| bit 15        | OETRIG: CC                                                                                                                                                                                | Px Dead-Time                         | Select bit                        |                  |                      |                        |                        |  |  |  |

|               | <ul> <li>1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered</li> <li>0 = Normal output pin operation</li> </ul>                               |                                      |                                   |                  |                      |                        |                        |  |  |  |

| bit 14-12     |                                                                                                                                                                                           | : One-Shot Ev                        |                                   |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      |                                   | ase periods (8 t | ime base perio       | ods total)             |                        |  |  |  |

|               | <ul><li>111 = Extends one-shot event by 7 time base periods (8 time base periods total)</li><li>110 = Extends one-shot event by 6 time base periods (7 time base periods total)</li></ul> |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 101 = Extends one-shot event by 5 time base periods (6 time base periods total)                                                                                                           |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 100 = Extends one-shot event by 4 time base periods (5 time base periods total)<br>011 = Extends one-shot event by 3 time base periods (4 time base periods total)                        |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 010 = Extends one-shot event by 3 time base periods (4 time base periods total)<br>010 = Extends one-shot event by 2 time base periods (3 time base periods total)                        |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      | ent by 1 time ba                  |                  | me base period       | ds total)              |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      | shot trigger eve                  | ent              |                      |                        |                        |  |  |  |

| bit 11        | -                                                                                                                                                                                         | ted: Read as '                       |                                   | (1)              |                      |                        |                        |  |  |  |

| bit 10-8      | OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup>                                                                                                                                   |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 111 = Reserv<br>110 = Output                                                                                                                                                              |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           | DC Output mo                         | de. forward                       |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           | DC Output mo                         |                                   |                  |                      |                        |                        |  |  |  |

|               | 011 = Reserved                                                                                                                                                                            |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 010 = Half-Bridge Output mode<br>001 = Push-Pull Output mode                                                                                                                              |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 001 = Push-Puil Output mode<br>000 = Steerable Single Output mode                                                                                                                         |                                      |                                   |                  |                      |                        |                        |  |  |  |

| bit 7-6       |                                                                                                                                                                                           | ted: Read as '                       |                                   |                  |                      |                        |                        |  |  |  |

| bit 5         | POLACE: CC                                                                                                                                                                                | Px Output Pin                        | s, OCMx, OCM                      | lxA, OCMxC a     | nd OCMxE, Po         | larity Control b       | it                     |  |  |  |

|               | <b>POLACE:</b> CCPx Output Pins, OCMx, OCMxA, OCMxC and OCMxE, Polarity Control bit<br>1 = Output pin polarity is active-low                                                              |                                      |                                   |                  |                      |                        |                        |  |  |  |

|               | 0 = Output pi                                                                                                                                                                             | n polarity is ac                     | tive-high                         |                  |                      |                        |                        |  |  |  |

| bit 4         | POLBDF: CC                                                                                                                                                                                | Px Output Pin                        | s, OCxB, OCxE                     | D and OCxF, Po   | olarity Control      | bit <sup>(1)</sup>     |                        |  |  |  |

|               |                                                                                                                                                                                           | n polarity is ac<br>n polarity is ac |                                   |                  |                      |                        |                        |  |  |  |

| bit 3-2       | PSSACE<1:0                                                                                                                                                                                | >: PWMx Outp                         | ut Pins, OCMx,                    | OCMxA, OCM       | xC and OCMxE         | E, Shutdown Sta        | ate Control bits       |  |  |  |

|               | 11 = Pins are                                                                                                                                                                             | driven active                        | when a shutdow                    | vn event occur   | s                    |                        |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      | e when a shutd                    |                  | urs                  |                        |                        |  |  |  |

| 1.1.4.0       |                                                                                                                                                                                           |                                      | n a shutdown e                    |                  |                      |                        |                        |  |  |  |

| bit 1-0       |                                                                                                                                                                                           | -                                    |                                   |                  |                      | n State Control        | bits                   |  |  |  |

|               |                                                                                                                                                                                           |                                      | when a shutdow<br>e when a shutdo |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      | edance state wh                   |                  |                      |                        |                        |  |  |  |

|               |                                                                                                                                                                                           |                                      |                                   |                  |                      |                        |                        |  |  |  |

### REGISTER 14-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

Note 1: These bits are implemented in MCCPx modules only.

#### REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 9         | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <u>Master Mode:</u><br>1 = Input data is sampled at the end of data output time                                                                                                                                                     |

|               | 0 = Input data is sampled at the middle of data output time                                                                                                                                                                         |

|               | Slave Mode:                                                                                                                                                                                                                         |

|               | Input data is always sampled at the middle of data output time, regardless of the SMP setting.                                                                                                                                      |

| bit 8         | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                                      |

|               | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                          |

| bit 7         | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                           |

|               | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select input<br>0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

| bit 6         | CKP: Clock Polarity Select bit                                                                                                                                                                                                      |

|               | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                            |

| bit 5         | MSTEN: Master Mode Enable bit                                                                                                                                                                                                       |

|               | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                   |

| bit 4         | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                                 |

|               | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                    |

| bit 3         | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                                |

|               | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                    |

| bit 2         | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                      |

|               | 1 = REFO is used by the BRG<br>0 = Fosc/2 is used by the BRG                                                                                                                                                                        |

| bit 1         | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                             |

|               | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                                  |

| bit 0         | ENHBUF: Enhanced Buffer Enable bit                                                                                                                                                                                                  |

|               | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                               |

| Note 1:<br>2: | When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.<br>When $FRMEN = 1$ SSEN is not used                                                                                           |

- EN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

#### REGISTER 17-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0          | U-0                                          | U-0              | U-0             | U-0               | U-0              | U-0             | U-0     |

|--------------|----------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|---------|

|              | —                                            | _                |                 | _                 | _                | _               | _       |

| bit 15       |                                              |                  |                 |                   |                  |                 | bit 8   |

|              |                                              |                  |                 |                   |                  |                 |         |

| U-0          | U-0                                          | U-0              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

| 0-0          | 0-0                                          | 0-0              | N/W-0           |                   | LENGTH<4:0>      |                 | FV/VV-0 |

|              | _                                            | _                |                 | VVI               | LENGTH<4:0>      | (-, <b>-</b> ,  |         |

| bit 7        |                                              |                  |                 |                   |                  |                 | bit 0   |

|              |                                              |                  |                 |                   |                  |                 |         |

| Legend:      |                                              |                  |                 |                   |                  |                 |         |

| R = Readal   | ole bit                                      | W = Writable     | bit             | U = Unimplen      | nented bit, read | l as '0'        |         |

| -n = Value a | at POR                                       | '1' = Bit is set | t               | '0' = Bit is clea | ared             | x = Bit is unkn | own     |

|              |                                              |                  |                 |                   |                  |                 |         |

| bit 15-5     | Unimplemen                                   | nted: Read as '  | 0'              |                   |                  |                 |         |

| bit 4-0      | =                                            | 4:0>: Variable   |                 | ito(1,2)          |                  |                 |         |

| DIL 4-0      |                                              |                  | word Length b   | 115 7             |                  |                 |         |

|              | 11111 = 32-<br>11110 = 31-                   |                  |                 |                   |                  |                 |         |

|              | 11101 <b>= 30</b> -                          |                  |                 |                   |                  |                 |         |

|              | 11100 <b>= 29</b> -                          |                  |                 |                   |                  |                 |         |

|              | 1100 = 29-bit data                           |                  |                 |                   |                  |                 |         |

|              | 11010 = 27-                                  |                  |                 |                   |                  |                 |         |

|              | 11001 <b>= 26</b> -                          |                  |                 |                   |                  |                 |         |

|              | 11000 <b>= 25-bit data</b>                   |                  |                 |                   |                  |                 |         |

|              | 10111 <b>= 24</b> -                          | bit data         |                 |                   |                  |                 |         |

|              | 10110 <b>= 23</b> -                          |                  |                 |                   |                  |                 |         |

|              | 10101 = 22-                                  |                  |                 |                   |                  |                 |         |

|              | 10100 <b>= 21</b> -                          |                  |                 |                   |                  |                 |         |

|              | 10011 = 20-                                  |                  |                 |                   |                  |                 |         |

|              | 10010 = 19-                                  |                  |                 |                   |                  |                 |         |

|              | 10001 = <b>18</b> -<br>10000 = <b>17</b> -   |                  |                 |                   |                  |                 |         |

|              | 01111 <b>= 16</b> -                          |                  |                 |                   |                  |                 |         |

|              | 01110 = 15-                                  |                  |                 |                   |                  |                 |         |

|              | 01101 <b>= 14</b> -                          |                  |                 |                   |                  |                 |         |

|              | 01100 <b>= 13</b> -                          | bit data         |                 |                   |                  |                 |         |

|              | 01011 <b>= 12</b> -                          | bit data         |                 |                   |                  |                 |         |

|              | 01010 = <b>11-</b>                           | bit data         |                 |                   |                  |                 |         |

|              | 01001 = 10-                                  | bit data         |                 |                   |                  |                 |         |

|              | 01000 <b>= 9-b</b>                           |                  |                 |                   |                  |                 |         |

|              | 00111 = 8-bit data                           |                  |                 |                   |                  |                 |         |

|              | 00110 = <b>7</b> -bi                         |                  |                 |                   |                  |                 |         |

|              | 00101 = 6-bi                                 |                  |                 |                   |                  |                 |         |

|              | 00100 <b>= 5-b</b> i<br>00011 <b>= 4-b</b> i |                  |                 |                   |                  |                 |         |

|              | 00011 = 4-bi<br>00010 = 3-bi                 |                  |                 |                   |                  |                 |         |

|              | 00010 = 3-bi                                 |                  |                 |                   |                  |                 |         |

|              |                                              | e MODE<32,16     | > bits in SPIxC | ON1L<11:10>       |                  |                 |         |

|              |                                              |                  |                 |                   |                  |                 |         |

- **Note 1:** These bits are effective when AUDEN = 0 only.

- 2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

| R/W-0        | U-0                                                                                                                                                                   | R/W-0                                                                                                                                                                                    | R/W-0                           | R/W-0             | U-0               | R/W-0             | R/W-0        |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|-------------------|-------------------|--------------|--|--|--|--|

| PMEN         |                                                                                                                                                                       | PSIDL                                                                                                                                                                                    | ADRMUX1                         | ADRMUX0           |                   | MODE1             | MODE0        |  |  |  |  |

| bit 15       |                                                                                                                                                                       |                                                                                                                                                                                          |                                 |                   |                   |                   | bit 8        |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                 | R/W-0                                                                                                                                                                                    | R/W-0                           | U-0               | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| CSF1         | CSF0                                                                                                                                                                  | ALP                                                                                                                                                                                      | ALMODE                          | 0-0               | BUSKEEP           | IRQM1             | IRQM0        |  |  |  |  |