Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb406t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | Mem                | nory            | iory |                    | log P      | eriphe      | erals |           |                  | Digita    | al Per           | ipher | als |           |     |         |               | els)                    | L<br>L            |

|-----------------|--------------------|-----------------|------|--------------------|------------|-------------|-------|-----------|------------------|-----------|------------------|-------|-----|-----------|-----|---------|---------------|-------------------------|-------------------|

| Device          | Program<br>(bytes) | Data<br>(bytes) | Pins | 10/12-Bit A/D (ch) | 10-Bit DAC | Comparators | CTMU  | MCCP/SCCP | 16/32-Bit Timers | NWM-DO/DI | I <sup>2</sup> C | IdS   |     | dSdJ/dWd3 | CLC | DIO ASU | Crypto Engine | LCD Controller (pixels) | Deep Sleep + VBAT |

| PIC24FJ256GA412 | 256K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Y                 |

| PIC24FJ256GA410 | 256K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Υ                 |

| PIC24FJ256GA406 | 256K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Υ             | 248                     | Y                 |

| PIC24FJ128GA412 | 128K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Y                 |

| PIC24FJ128GA410 | 128K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Υ                 |

| PIC24FJ128GA406 | 128K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 248                     | Y                 |

| PIC24FJ64GA412  | 64K                | 8K              | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Υ                 |

| PIC24FJ64GA410  | 64K                | 8K              | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Y                 |

| PIC24FJ64GA406  | 64K                | 8K              | 64   | 16                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Ν       | Υ             | 248                     | Υ                 |

| PIC24FJ256GB412 | 256K               | 16K             | 121  | 24                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Υ       | Υ             | 512                     | Υ                 |

| PIC24FJ256GB410 | 256K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 480                     | Y                 |

| PIC24FJ256GB406 | 256K               | 16K             | 64   | 16                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Υ       | Υ             | 240                     | Υ                 |

| PIC24FJ128GB412 | 128K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 512                     | Υ                 |

| PIC24FJ128GB410 | 128K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Υ       | Υ             | 480                     | Y                 |

| PIC24FJ128GB406 | 128K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Υ       | Υ             | 240                     | Y                 |

| PIC24FJ64GB412  | 64K                | 8K              | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Υ       | Υ             | 512                     | Y                 |

| PIC24FJ64GB410  | 64K                | 8K              | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Y       | Y             | 480                     | Y                 |

| PIC24FJ64GB406  | 64K                | 8K              | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 240                     | Y                 |

## **Peripheral Features**

- LCD Display Controller:

- Up to 64 Segments by 8 Commons

- Internal charge pump and low-power, internal resistor biasing

Operation in Sleep mode

- Up to Five External Interrupt Sources

- Peripheral Pin Select (PPS); allows Independent I/O Mapping of Many Peripherals

- Six-Channel DMA Supports All Peripheral modules:

Minimizes CPU overhead and increases data throughput

- Five 16-Bit Timers/Counters with Prescalers:

- Can be paired as 32-bit timers/counters

- Using a combination of Timer, CCP, IC and OC Timers, the Device can be Configured to use up to 31 16-Bit Timers, and up to 15 32-Bit Timers

- Six Input Capture modules, each with a Dedicated

16-Bit Timer

- Six Output Compare/PWM modules, each with a Dedicated 16-Bit Timer

- Six Single Output CCPs (SCCP) and One Multiple Output CCP (MCCP) modules:

- Independent 16/32-bit time base for each module

- Internal time base and Period registers

- Legacy PIC24F Capture and Compare modes (16 and 32-bit)

- Special variable frequency pulse and Brushless DC Motor (BDCM) Output modes

- Enhanced Parallel Master/Slave Port (EPMP/EPSP)

- Hardware Real-Time Clock/Calendar (RTCC) with Timestamping:

- Tamper detection with timestamping feature and tamper pin

- Runs in Deep Sleep and VBAT modes

- Four 3-Wire/4-Wire SPI modules (support 4 Frame modes) with 8-Level FIFO Buffer

- Three I<sup>2</sup>C modules support Multi-Master/Slave mode and 7-Bit/10-Bit Addressing

- Six UART modules:

- Support RS-485, RS-232 and LIN/J2602

- On-chip hardware encoder/decoder for IrDA<sup>®</sup>

- Auto-wake-up on Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Programmable 32-Bit Cyclic Redundancy Check (CRC) Generator

- Four Configurable Logic Cells (CLCs):

- Two inputs and one output, all mappable to peripherals or I/O pins

- AND/OR/XOR logic and D/JK flip-flop functions

- High-Current Sink/Source (18 mA/18 mA) on All I/O Pins

- Configurable Open-Drain Outputs on Digital I/O Pins

- 5.5V Tolerant Inputs on Multiple I/O Pins

|               | Pir            | n/Pad Numl      | ber              |     |                |                            |

|---------------|----------------|-----------------|------------------|-----|----------------|----------------------------|

| Pin Function  | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer   | Description                |

| INT0          | 46             | 72              | D9               | I   | ST/STMV        | External Interrupt Input 0 |

| IOCA0         | —              | 17              | G3               | 1   | ST             | PORTA Interrupt-on-Change  |

| IOCA1         | _              | 38              | J6               | I   | ST             | 1                          |

| IOCA2         | _              | 58              | H11              | I   | ST             |                            |

| IOCA3         | —              | 59              | G10              | 1   | ST             |                            |

| IOCA4         | _              | 60              | G11              | I   | ST             |                            |

| IOCA5         | _              | 61              | G9               | I   | ST             |                            |

| IOCA6         | _              | 91              | E10              | I   | ST             |                            |

| IOCA7         | _              | 92              | E11              | I   | ST             | 1                          |

| IOCA9         | -              | 28              | L2               | I   | ST             | 1                          |

| IOCA10        | -              | 29              | K3               | I   | ST             | 1                          |

| IOCA14        | —              | 66              | E11              | I   | ST             | 1                          |

| IOCA15        | _              | 67              | E8               | I   | ST             | 1                          |

| IOCB0         | 16             | 25              | K2               | 1   | ST             | PORTB Interrupt-on-Change  |

| IOCB1         | 15             | 24              | K1               | I   | ST             | 1                          |

| IOCB2         | 14             | 23              | J2               | I   | ST             | 1                          |

| IOCB3         | 13             | 22              | J1               | I   | ST             | 1                          |

| IOCB4         | 12             | 21              | H2               | I   | ST             | ]                          |

| IOCB5         | 11             | 20              | H1               | I   | ST             | ]                          |

| IOCB6         | 17             | 26              | L1               | I   | ST             |                            |

| IOCB7         | 18             | 27              | J3               | I   | ST             |                            |

| IOCB8         | 21             | 32              | K4               | I   | ST             | ]                          |

| IOCB9         | 22             | 33              | L4               | I   | ST             | ]                          |

| IOCB10        | 23             | 34              | H5               | I   | ST             |                            |

| IOCB11        | 24             | 35              | K5               | I   | ST             |                            |

| IOCB12        | 27             | 41              | J7               | I   | ST             |                            |

| IOCB13        | 28             | 42              | L7               | I   | ST             | ]                          |

| IOCB14        | 29             | 43              | K7               | I   | ST             | ]                          |

| IOCB15        | 30             | 44              | L8               | I   | ST             | ]                          |

| IOCC1         | _              | 6               | D1               | I   | ST             | PORTC Interrupt-on-Change  |

| IOCC2         | _              | 7               | E4               | I   | ST             | ]                          |

| IOCC3         | —              | 8               | E2               | I   | ST             | ]                          |

| IOCC4         | _              | 9               | E1               | I   | ST             | ]                          |

| IOCC12        | 39             | 63              | F9               | I   | ST             | ]                          |

| IOCC13        | 47             | 73              | C10              | I   | ST             | ]                          |

| IOCC14        | 48             | 74              | B11              | I   | ST             | ]                          |

| IOCC15        | 40             | 64              | F11              | I   | ST             | ]                          |

| Legend: TTL = | TTL input buf  | fer             |                  |     | ST = Schmitt T | rigger input buffer        |

#### **TABLE 1-4:** PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

TTL = TTL input buffer Legend: ANA = Analog-level input/output DIG = Digital input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

SMB = SMBus

XCVR = Dedicated transceiver

|              | Pin/Pad Number |                 |                  |     |              |                                                                               |  |  |

|--------------|----------------|-----------------|------------------|-----|--------------|-------------------------------------------------------------------------------|--|--|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                                                                   |  |  |

| IOCG0        | _              | 90              | A5               | 1   | ST           | PORTG Interrupt-on-Change                                                     |  |  |

| IOCG1        | _              | 89              | E6               | I   | ST           |                                                                               |  |  |

| IOCG2        | 37             | 57              | H10              | I   | ST           | 1                                                                             |  |  |

| IOCG3        | 36             | 56              | J11              | I   | ST           | 1                                                                             |  |  |

| IOCG6        | 4              | 10              | E3               | I   | ST           | 1                                                                             |  |  |

| IOCG7        | 5              | 11              | F4               | I   | ST           | ]                                                                             |  |  |

| IOCG8        | 6              | 12              | F2               | I   | ST           | ]                                                                             |  |  |

| IOCG9        | 8              | 14              | F3               | I   | ST           | ]                                                                             |  |  |

| IOCG12       | —              | 96              | E17              | I   | ST           |                                                                               |  |  |

| IOCG13       | —              | 97              | E18              | I   | ST           |                                                                               |  |  |

| IOCG14       | —              | 95              | E16              | I   | ST           |                                                                               |  |  |

| IOCG15       | _              | 1               | B2               | I   | ST           |                                                                               |  |  |

| IOCH1        | —              | _               | B1               | I   | ST           | PORTH Interrupt-on-Change                                                     |  |  |

| IOCH2        | _              | _               | D4               | I   | ST           | ]                                                                             |  |  |

| IOCH3        | _              |                 | G4               | I   | ST           | ]                                                                             |  |  |

| IOCH4        | _              |                 | H3               | I   | ST           | ]                                                                             |  |  |

| IOCH5        | —              | —               | H4               | I   | ST           |                                                                               |  |  |

| IOCH6        | _              | _               | L5               | I   | ST           |                                                                               |  |  |

| IOCH7        | _              | _               | J5               | I   | ST           |                                                                               |  |  |

| IOCH8        | —              | _               | H7               | Ι   | ST           |                                                                               |  |  |

| IOCH9        | _              | —               | J8               | Ι   | ST           |                                                                               |  |  |

| IOCH10       | _              | —               | J9               | Ι   | ST           |                                                                               |  |  |

| IOCH11       | —              | _               | G8               | I   | ST           |                                                                               |  |  |

| IOCH12       | —              | —               | F7               | I   | ST           |                                                                               |  |  |

| IOCH13       | —              | —               | C9               | I   | ST           |                                                                               |  |  |

| IOCH14       |                | —               | A8               | I   | ST           |                                                                               |  |  |

| IOCH15       |                | —               | F6               | I   | ST           |                                                                               |  |  |

| IOCJ0        | —              | —               | E13              | I   | ST           | PORTJ Interrupt-on-Change                                                     |  |  |

| IOCJ1        |                | —               | E14              | I   | ST           |                                                                               |  |  |

| LCDBIAS0     | 3              | 5               | D2               | 0   | ANA          | Bias Inputs for LCD Driver Charge Pump                                        |  |  |

| LCDBIAS1     | 2              | 4               | C1               | 0   | ANA          |                                                                               |  |  |

| LCDBIAS2     | 1              | 3               | D3               | 0   | ANA          |                                                                               |  |  |

| LCDBIAS3     | 17             | 26              | L1               | 0   | ANA          |                                                                               |  |  |

| LVDIN        | 64             | 100             | E31              | I   | ANA          | Low-Voltage Detect Input                                                      |  |  |

| MCLR         | 7              | 13              | F1               | I   | ST/STMV      | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |  |  |

| OC4          | 54             | 83              | D7               | 0   | DIG          | Output Compare 4 Output                                                       |  |  |

| OC5          | 55             | 84              | C7               | 0   | DIG          | Output Compare 5 Output                                                       |  |  |

| OC6          | 58             | 87              | B6               | 0   | DIG          | Output Compare 6 Output                                                       |  |  |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

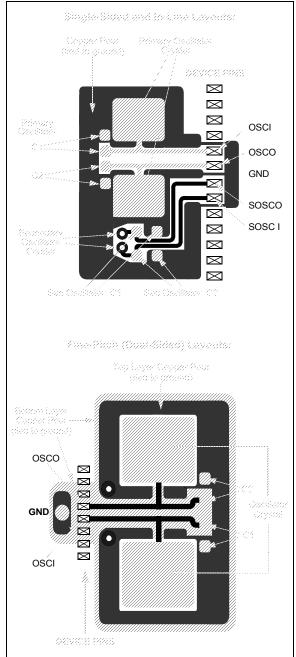

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

- AN1798, "Crystal Selection for Low-Power Secondary Oscillator"

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

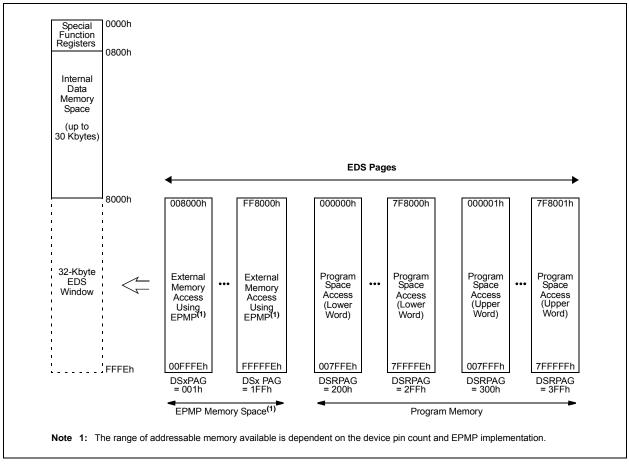

### 4.3.5 EXTENDED DATA SPACE (EDS)

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space and any external memory through the Enhanced Parallel Master Port (EPMP).

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.4.3 "Reading Data from Program Memory Using EDS".

Figure 4-6 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to the size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read Page register (DSRPAG) or Data Space Write Page register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). The data addressing range of PIC24FJ256GA412/ GB412 family devices depends on the version of the Enhanced Parallel Master Port (EPMP) implemented on a particular device; this is, in turn, a function of the device pin count. Table 4-13 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Enhanced Parallel Master Port (EPMP)"** (DS39730).

| TABLE 4-13: | TOTAL ACCESSIBLE DATA |

|-------------|-----------------------|

|             | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGX406 | 8 Kbytes        | Up to 64 Kbytes                      |

| PIC24FJXXXGX410 | 16 Kbytes       | Up to 16 Mbytes                      |

| PIC24FJXXXGX412 | 16 Kbytes       | Up to 16 Mbytes                      |

Note: Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

#### FIGURE 4-6: EXTENDED DATA SPACE

| R/W-0                                                                                                                                         | U-0                                                                | U-0                                                       | U-0                  | U-0               | U-0    | U-0              | U-0   |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|----------------------|-------------------|--------|------------------|-------|

| NSTDIS                                                                                                                                        | —                                                                  |                                                           | —                    | —                 | —      | —                | —     |

| bit 15                                                                                                                                        |                                                                    |                                                           |                      |                   |        |                  | bit 8 |

|                                                                                                                                               |                                                                    |                                                           |                      |                   |        |                  |       |

| U-0                                                                                                                                           | U-0                                                                | U-0                                                       | R/W-0                | R/W-0             | R/W-0  | R/W-0            | U-0   |

|                                                                                                                                               |                                                                    |                                                           | MATHERR              | ADDRERR           | STKERR | OSCFAIL          |       |

| bit 7                                                                                                                                         |                                                                    |                                                           |                      |                   |        |                  | bit C |

|                                                                                                                                               |                                                                    |                                                           |                      |                   |        |                  |       |

| Legend:                                                                                                                                       |                                                                    |                                                           |                      |                   |        |                  |       |

| R = Readab                                                                                                                                    |                                                                    | W = Writable                                              |                      | U = Unimplem      |        |                  |       |

| -n = Value a                                                                                                                                  | at POR                                                             | '1' = Bit is se                                           | t                    | '0' = Bit is clea | ared   | x = Bit is unkno | own   |

| bit 15<br>bit 14-5                                                                                                                            | NSTDIS: Inter<br>1 = Interrupt n<br>0 = Interrupt n<br>Unimplement | nesting is disa<br>nesting is ena<br>t <b>ed:</b> Read as | abled<br>bled<br>'0' |                   |        |                  |       |

| bit 4                                                                                                                                         | MATHERR: A<br>1 = Overflow<br>0 = Overflow                         | trap has occu                                             |                      | t                 |        |                  |       |

| bit 3                                                                                                                                         | ADDRERR: A<br>1 = Address e<br>0 = Address e                       | error trap has                                            |                      |                   |        |                  |       |

| bit 2                                                                                                                                         | · ·                                                                |                                                           |                      |                   |        |                  |       |

| bit 1 OSCFAIL: Oscillator Failure Trap Status bit<br>1 = Oscillator failure trap has occurred<br>0 = Oscillator failure trap has not occurred |                                                                    |                                                           |                      |                   |        |                  |       |

| bit 0                                                                                                                                         | Unimplement                                                        | ted: Read as                                              | ʻ0'                  |                   |        |                  |       |

|                                                                                                                                               |                                                                    |                                                           |                      |                   |        |                  |       |

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0         | R/W-0         | R/W-0                               | U-0         | U-0               | R/W-0            | U-0             | U-0    |

|---------------|---------------|-------------------------------------|-------------|-------------------|------------------|-----------------|--------|

| U5RXIE        | RTCTSIE       | I2C3BCIE                            | —           | _                 | FSTIE            |                 | _      |

| bit 15        |               |                                     |             |                   |                  |                 | bit 8  |

|               |               |                                     |             |                   |                  |                 |        |

| U-0           | R/W-0         | R/W-0                               | R/W-0       | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —             | CCT2IE        | CCT1IE                              | LCDIE       | CLC4IE            | CLC3IE           | CLC2IE          | CLC1IE |

| bit 7         |               |                                     |             |                   |                  |                 | bit (  |

|               |               |                                     |             |                   |                  |                 |        |

| Legend:       |               |                                     |             |                   |                  |                 |        |

| R = Readable  |               | W = Writable I                      | oit         | •                 | nented bit, read |                 |        |

| -n = Value at | POR           | '1' = Bit is set                    |             | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| L:4 / F       |               |                                     | 4 4 <b></b> | - 1-:4            |                  |                 |        |

| bit 15        |               | RT5 Receiver In<br>request is enab  | •           | e bit             |                  |                 |        |

|               |               | request is enact                    |             |                   |                  |                 |        |

| bit 14        | •             | CC Timestamp                        |             | able bit          |                  |                 |        |

|               | 1 = Interrupt | request is enab                     | led         |                   |                  |                 |        |

|               | •             | request is not e                    |             |                   |                  |                 |        |

| bit 13        |               | C3 Bus Collisio                     |             | able bit          |                  |                 |        |

|               |               | request is enab<br>request is not e |             |                   |                  |                 |        |

| bit 12-11     | •             | ted: Read as '0                     |             |                   |                  |                 |        |

| bit 10        | -             | Self-Tune Interr                    |             | t                 |                  |                 |        |

|               |               | request is enab                     | •           | •                 |                  |                 |        |

|               | 0 = Interrupt | request is not e                    | nabled      |                   |                  |                 |        |

| bit 9-7       | Unimplemen    | ted: Read as 'o                     | )'          |                   |                  |                 |        |

| bit 6         |               | P2 Timer Interr                     | •           | t                 |                  |                 |        |

|               |               | request is enab                     |             |                   |                  |                 |        |

| L:4 F         | -             | request is not e                    |             | 1                 |                  |                 |        |

| bit 5         |               | CP1 Timer Interr<br>request is enab |             | t                 |                  |                 |        |

|               |               | request is enact                    |             |                   |                  |                 |        |

| bit 4         | •             | Controller Interi                   |             | t                 |                  |                 |        |

|               |               | request is enab                     |             |                   |                  |                 |        |

|               | 0 = Interrupt | request is not e                    | nabled      |                   |                  |                 |        |

| bit 3         |               | 4 Interrupt Ena                     |             |                   |                  |                 |        |

|               |               | request is enab<br>request is not e |             |                   |                  |                 |        |

| bit 2         |               | 3 Interrupt Ena                     |             |                   |                  |                 |        |

|               |               | request is enab                     |             |                   |                  |                 |        |

|               |               | request is not e                    |             |                   |                  |                 |        |

| bit 1         | CLC2IE: CLC   | 2 Interrupt Ena                     | ble bit     |                   |                  |                 |        |

|               | •             | request is enab                     |             |                   |                  |                 |        |

|               | 0 = Interrupt | request is not a                    | nahled      |                   |                  |                 |        |

|               | -             | -                                   |             |                   |                  |                 |        |

| bit 0         | CLC1IE: CLC   | 1 Interrupt Ena<br>request is enab  | ble bit     |                   |                  |                 |        |

## REGISTER 8-20: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

#### REGISTER 8-21: IEC7: INTERRUPT ENABLE CONTROL REGISTER 7

| U-0                               | U-0           | U-0                                | U-0            | U-0               | U-0              | U-0                | U-0    |  |

|-----------------------------------|---------------|------------------------------------|----------------|-------------------|------------------|--------------------|--------|--|

| —                                 | —             | —                                  | —              | _                 |                  | —                  | —      |  |

| bit 15                            |               |                                    |                |                   |                  |                    | bit 8  |  |

|                                   |               |                                    |                |                   |                  |                    |        |  |

| U-0                               | U-0           | R/W-0                              | R/W-0          | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |

|                                   |               | JTAGIE                             | U6ERIE         | U6TXIE            | U6RXIE           | U5ERIE             | U5TXIE |  |

| bit 7                             |               |                                    |                |                   |                  |                    | bit 0  |  |

|                                   |               |                                    |                |                   |                  |                    |        |  |

| Legend:                           |               |                                    |                |                   |                  |                    |        |  |

| R = Readable bit W = Writable bit |               |                                    | bit            | U = Unimplem      | nented bit, read | l as '0'           |        |  |

| -n = Value a                      | at POR        | '1' = Bit is set                   |                | '0' = Bit is clea | ared             | x = Bit is unknown |        |  |

|                                   |               |                                    |                |                   |                  |                    |        |  |

| bit 15-6                          | Unimplemen    | ted: Read as '                     | כי             |                   |                  |                    |        |  |

| bit 5                             | JTAGIE: JAT   | G Interrupt Ena                    | ble bit        |                   |                  |                    |        |  |

|                                   |               | request is enat                    |                |                   |                  |                    |        |  |

|                                   | 0 = Interrupt | request is not e                   | enabled        |                   |                  |                    |        |  |

| bit 4                             | U6ERIE: UAF   | RT6 Error Interr                   | upt Enable bit |                   |                  |                    |        |  |

|                                   |               | 1 = Interrupt request has occurred |                |                   |                  |                    |        |  |

|                                   | 0 = Interrupt | request has no                     | t occurred     |                   |                  |                    |        |  |

| bit 3                             |               | T6 Transmitter                     | •              | ole bit           |                  |                    |        |  |

|                                   |               | request has oc                     |                |                   |                  |                    |        |  |

|                                   |               | request has no                     |                |                   |                  |                    |        |  |

| bit 2                             |               | RT6 Receiver Ir                    | •              | bit               |                  |                    |        |  |

|                                   | 1 = Interrupt | request has oc                     | curred         |                   |                  |                    |        |  |

- 0 = Interrupt request has not occurred

- bit 1 U5ERIE: UART5 Error Interrupt Enable bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 U5TXIE: UART5 Transmitter Interrupt Enable bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

|                  | R/W-1                                       | R/W-0                                                                                                   | R/W-0                        | U-0             | R/W-1             | R/W-0           | R/W-0     |

|------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|-----------------|-------------------|-----------------|-----------|

|                  | U1RXIP2                                     | U1RXIP1                                                                                                 | U1RXIP0                      | _               | SPI1TXIP2         | SPI1TXIP1       | SPI1TXIP0 |

| bit 15           |                                             |                                                                                                         |                              |                 |                   |                 | bit       |

| U-0              | R/W-1                                       | R/W-0                                                                                                   | R/W-0                        | U-0             | R/W-1             | R/W-0           | R/W-0     |

| 0-0              | SPI1IP2                                     | SPI1IP1                                                                                                 | SPI1IP0                      | 0-0             | T3IP2             | T3IP1           | T3IP0     |

| bit 7            | 011112                                      | OF THE T                                                                                                | OF THE U                     |                 | 1011 2            | 10111           | bit       |

|                  |                                             |                                                                                                         |                              |                 |                   |                 |           |

| Legend:          |                                             |                                                                                                         |                              |                 |                   |                 |           |

| R = Readab       | ole bit                                     | W = Writable                                                                                            | bit                          | U = Unimple     | emented bit, read | d as '0'        |           |

| -n = Value a     | at POR                                      | '1' = Bit is set                                                                                        |                              | '0' = Bit is cl | eared             | x = Bit is unkr | nown      |

| bit 15           | Unimplomon                                  | ted: Read as '                                                                                          | ۰ <b>،</b>                   |                 |                   |                 |           |

| bit 14-12        | -                                           | : UART1 Rece                                                                                            |                              | Priority hits   |                   |                 |           |

| 51(1412          |                                             | pt is Priority 7 (                                                                                      |                              |                 |                   |                 |           |

|                  | •                                           | . , ,                                                                                                   |                              | , ,             |                   |                 |           |

|                  | •                                           |                                                                                                         |                              |                 |                   |                 |           |

|                  | 001 = Interru                               | pt is Priority 1                                                                                        |                              |                 |                   |                 |           |

|                  |                                             | pt source is dis                                                                                        | abled                        |                 |                   |                 |           |

| bit 11           | Unimplemen                                  | ted: Read as '                                                                                          | )'                           |                 |                   |                 |           |

| bit 10-8         | SPI1TXIP<2:                                 | 0>: SPI1 Trans                                                                                          | mit Interrupt P              | riority bits    |                   |                 |           |

|                  | 111 = Interru                               | pt is Priority 7 (                                                                                      | highest priority             | y interrupt)    |                   |                 |           |

|                  | •                                           |                                                                                                         |                              |                 |                   |                 |           |

|                  | •                                           |                                                                                                         |                              |                 |                   |                 |           |

|                  | 001 = Interru                               | pt is Priority 1                                                                                        |                              |                 |                   |                 |           |

|                  |                                             | pt source is dis                                                                                        | abled                        |                 |                   |                 |           |

| bit 7            | Unimplemen                                  | ted: Read as '                                                                                          | )'                           |                 |                   |                 |           |

| bit 6-4          | SPI1IP<2:0>:                                | SPI1 General                                                                                            | Interrupt Prior              | ity bits        |                   |                 |           |

|                  | 111 = Interru                               | ot is Priority 7 (                                                                                      | highoot priority             | •               |                   |                 |           |

|                  |                                             |                                                                                                         | nignest priority             | y interrupt)    |                   |                 |           |

|                  | •                                           |                                                                                                         | nighest phone                | y interrupt)    |                   |                 |           |

|                  | •                                           | p: .e :e                                                                                                | nignest priority             | y interrupt)    |                   |                 |           |

|                  | •<br>•<br>•<br>001 = Interru                |                                                                                                         | nignest priority             | y interrupt)    |                   |                 |           |

|                  | •<br>•<br>001 = Interru<br>000 = Interru    |                                                                                                         |                              | y interrupt)    |                   |                 |           |

| bit 3            | 000 = Interru                               | pt is Priority 1                                                                                        | abled                        | y interrupt)    |                   |                 |           |

|                  | 000 = Interru<br>Unimplemen                 | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                          | abled                        | y interrupt)    |                   |                 |           |

|                  | 000 = Interru<br>Unimplemen<br>T3IP<2:0>: T | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as 'd<br>imer3 Interrupt                       | abled<br>)'<br>Priority bits |                 |                   |                 |           |

|                  | 000 = Interru<br>Unimplemen<br>T3IP<2:0>: T | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                          | abled<br>)'<br>Priority bits |                 |                   |                 |           |

| bit 3<br>bit 2-0 | 000 = Interru<br>Unimplemen<br>T3IP<2:0>: T | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as 'd<br>imer3 Interrupt                       | abled<br>)'<br>Priority bits |                 |                   |                 |           |

|                  | 000 = Interru<br>Unimplemen<br>T3IP<2:0>: T | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>imer3 Interrupt<br>pt is Priority 7 ( | abled<br>)'<br>Priority bits |                 |                   |                 |           |

### REGISTER 8-24: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

## **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Power-Saving Features with Deep Sleep" (DS39727). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ256GA412/GB412 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked reduces consumed power.

PIC24FJ256GA412/GB412 family devices manage power consumption with five strategies:

- Instruction-Based Power Reduction Modes

- Hardware-Based Power Reduction Features

- Clock Frequency Control

- Software Controlled Doze Mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Overview of Power-Saving Modes

In addition to full-power operation, otherwise known as Run mode, the PIC24FJ256GA412/GB412 family of devices offers three Instruction-Based Power-Saving modes and one Hardware-Based mode:

- Idle

- Sleep (Sleep and Low-Voltage Sleep)

- Deep Sleep (without retention)

- VBAT (with and without RTCC)

All four modes can be activated by powering down different functional areas of the microcontroller, allowing progressive reductions of operating and Idle power consumption. In addition, three of the modes can be tailored for more power reduction at a trade-off of some operating features. Table 10-1 lists all of the operating modes in order of increasing power savings. Table 10-2 summarizes how the microcontroller exits the different modes. Specific information is provided in the following sections.

|                   |                            | Active Systems |                  |                       |                     |                                |  |  |  |  |

|-------------------|----------------------------|----------------|------------------|-----------------------|---------------------|--------------------------------|--|--|--|--|

| Mode              | Entry                      | Core           | Peripherals      | Data RAM<br>Retention | RTCC <sup>(1)</sup> | DSGPR0/<br>DSGPR1<br>Retention |  |  |  |  |

| Run (default)     | N/A                        | Y              | Y                | Y                     | Y                   | Y                              |  |  |  |  |

| Idle              | Instruction                | Ν              | Y                | Y                     | Y                   | Y                              |  |  |  |  |

| Sleep:            |                            |                |                  |                       |                     |                                |  |  |  |  |

| Sleep             | Instruction                | Ν              | S <sup>(2)</sup> | Y                     | Y                   | Y                              |  |  |  |  |

| Low-Voltage Sleep | Instruction +<br>RETEN bit | Ν              | S <sup>(2)</sup> | Y                     | Y                   | Y                              |  |  |  |  |

| Deep Sleep:       |                            |                |                  |                       |                     |                                |  |  |  |  |

| Deep Sleep        | Instruction +<br>DSEN bit  | Ν              | Ν                | Ν                     | Y                   | Y                              |  |  |  |  |

| VBAT:             |                            |                |                  |                       |                     |                                |  |  |  |  |

| with RTCC         | Hardware                   | Ν              | Ν                | Ν                     | Y                   | Y                              |  |  |  |  |

#### TABLE 10-1: OPERATING MODES FOR PIC24FJ256GA412/GB412 FAMILY DEVICES

Note 1: If RTCC is otherwise enabled in firmware.

2: A select peripheral can operate during this mode from LPRC or some external clock.

### 11.4 Interrupt-on-Change (IOC)

The interrupt-on-change function of the I/O ports allows the PIC24FJ256GA412/GB412 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on any of the input port pins. This feature is capable of detecting input Change-of-States, even in Sleep mode when the clocks are disabled.

Interrupt-on-change functionality is globally enabled by setting the IOCON bit in the PADCON register (Register 11-1). Functionality is then enabled for a particular pin by setting the IOCPx and/or IOCNx register bit for that pin. Setting a value of '1' in the IOCPx register enables interrupts for low-to-high transitions, while setting a value of '1' in the IOCNx register enables interrupts for high-to-low transitions. Setting a value of '1' in both register bits will enable interrupts for either case (e.g., a pulse on the pin will generate two interrupts).

When an interrupt request is generated for a pin, the corresponding status flag bit in the IOCFx register will be set, indicating that a Change-of-State occurred on that pin. The IOCFx register bit will remain set until cleared by writing a zero to it. When any IOCFx flag bit in a given port is set, the corresponding IOCPxF bit in the IOCSTAT register (Register 11-2) will also be set. This flag indicates that a change was detected on one of the bits on the given port. The IOCPxF flag will be cleared when all IOCFx

Multiple individual status flags can be cleared by writing a zero to one or more bits using a Read-Modify-Write operation. If another edge is detected on a pin whose status bit is being cleared during the Read-Modify-Write sequence, the associated change flag will still be set at the end of the Read-Modify-Write sequence. The user should use the instruction sequence (or equivalent) shown in Example 11-1 to clear the Interrupt-on-Change Status registers.

At the end of this sequence, the W0 register will contain a zero for each bit for which the port pin had a change detected. In this way, any indication of a pin changing will not be lost.

Due to the asynchronous and real-time nature of the interrupt-on-change, the value read on the port pins may not indicate the state of the port when the change was detected, as a second change can occur during the interval between clearing the flag and reading the port. It is up to the user code to handle this case if it is a possibility in their application. To keep this interval to a minimum, it is recommended that any code modifying the IOCFx registers be run either in the interrupt handler or with interrupts disabled.

#### 11.4.1 PULL-UPS AND PULL-DOWNS

Each IOC pin has both a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source connected to the pin, while the pull-downs act as a current sink connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected.

The pull-ups and pull-downs are separately enabled using the IOCPUx registers (for pull-ups) and the IOCPDx registers (for pull-downs). Each IOC pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

Note: Pull-ups and pull-downs on pins should always be disabled whenever the pin is configured as a digital output.

#### EXAMPLE 11-1: IOC STATUS READ/CLEAR IN ASSEMBLY

| MOV 0xFFFF,  | ; Initial mask value 0xFFFF -> W0      |

|--------------|----------------------------------------|

| XOR IOCFx, W | ; WO has '1' for each bit set in IOCFx |

| AND IOCFx    | ; IOCFx & WO ->IOCFx                   |

#### EXAMPLE 11-2: PORT READ/WRITE IN ASSEMBLY

| ĺ | MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|---|------|------------|-----------------------------------|

|   | MOV  | W0, TRISB  | ; and PORTB<7:0> as outputs       |

|   | NOP  |            | ; Delay 1 cycle                   |

|   | BTSS | PORTB, #13 | ; Next Instruction                |

#### EXAMPLE 11-3: PORT READ/WRITE IN 'C'

| TRISB = 0xFF00;                    | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------------------------------------|--------------------------------------------------------------|

| Nop();                             | // Delay 1 cycle                                             |

| <pre>If (PORTBbits.RB13){ };</pre> | // Next Instruction                                          |

| REGISTE    | R 13-1: TxCC                                                                                                                                            | ON: TIMER2 A                                                                                      | ND TIMER4                                                      | CONTROL R                                  | EGISTER <sup>(1)</sup> | )                    |                      |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------|----------------------|----------------------|--|--|--|

| R/W-0      | U-0                                                                                                                                                     | R/W-0                                                                                             | U-0                                                            | U-0                                        | U-0                    | R/W-0                | R/W-0                |  |  |  |

| TON        | —                                                                                                                                                       | TSIDL                                                                                             | _                                                              |                                            | —                      | TECS1 <sup>(2)</sup> | TECS0 <sup>(2)</sup> |  |  |  |

| bit 15     |                                                                                                                                                         |                                                                                                   |                                                                |                                            |                        |                      | bit 8                |  |  |  |

| U-0        | R/W-0                                                                                                                                                   | R/W-0                                                                                             | R/W-0                                                          | R/W-0                                      | U-0                    | R/W-0                | U-0                  |  |  |  |

| _          | TGATE                                                                                                                                                   | TCKPS1                                                                                            | TCKPS0                                                         | T32 <b>(3)</b>                             | —                      | TCS <sup>(2)</sup>   | —                    |  |  |  |

| bit 7      |                                                                                                                                                         |                                                                                                   |                                                                |                                            |                        |                      | bit C                |  |  |  |

| Legend:    |                                                                                                                                                         |                                                                                                   |                                                                |                                            |                        |                      |                      |  |  |  |

| R = Reada  | able bit                                                                                                                                                | W = Writable                                                                                      | bit                                                            | U = Unimplem                               | nented bit, rea        | ad as '0'            |                      |  |  |  |

| -n = Value | e at POR                                                                                                                                                | '1' = Bit is set                                                                                  |                                                                | '0' = Bit is clea                          | ared                   | x = Bit is unkr      | nown                 |  |  |  |

| bit 15     | TON: Timerx           When TxCOI           1 = Starts 32:           0 = Stops 32:           When TxCOI           1 = Starts 16:           0 = Stops 16: | <u>N&lt;3&gt; = 1:</u><br>-bit Timerx/y<br>-bit Timerx/y<br><u>N&lt;3&gt; = 0:</u><br>-bit Timerx |                                                                |                                            |                        |                      |                      |  |  |  |

| bit 14     | -                                                                                                                                                       | ted: Read as '                                                                                    | 0'                                                             |                                            |                        |                      |                      |  |  |  |

| bit 13     | TSIDL: Timerx Stop in Idle Mode bit                                                                                                                     |                                                                                                   |                                                                |                                            |                        |                      |                      |  |  |  |

|            | 1 = Discontin                                                                                                                                           | iues module op                                                                                    | eration when de                                                |                                            | e mode                 |                      |                      |  |  |  |

| bit 12-10  |                                                                                                                                                         | nted: Read as '                                                                                   |                                                                |                                            |                        |                      |                      |  |  |  |

| bit 9-8    | When TCS =           11 = Generic           10 = LPRC C           01 = TxCK e           00 = SOSC           When TCS =                                  | 1:<br>Timer (TMRCP<br>Dscillator<br>xternal clock inp<br>0:                                       | ed Clock Source<br><) external inpu<br>put<br>Fimer is clocked | t                                          |                        |                      |                      |  |  |  |

| bit 7      |                                                                                                                                                         | nted: Read as '                                                                                   |                                                                |                                            | ,                      | ( , ,                |                      |  |  |  |

| bit 6      | When TCS =<br>This bit is ign<br>When TCS =<br>1 = Gated tin                                                                                            | <u>1:</u><br>ored.                                                                                |                                                                | Enable bit                                 |                        |                      |                      |  |  |  |

| bit 5-4    |                                                                                                                                                         |                                                                                                   | Clock Prescale                                                 | Select bits                                |                        |                      |                      |  |  |  |

| Note 1:    | Changing the val<br>reset and is not r                                                                                                                  |                                                                                                   | hile the timer is                                              | running (TON                               | = 1) causes            | the timer presca     | le counter to        |  |  |  |

| 2:<br>3:   | If TCS = 1 and T<br>to an available R<br>In T4CON, the T4<br>T5CON control b                                                                            | Pn/RPIn pin. Fo<br>45 bit is implem                                                               | or more informa<br>ented instead o                             | tion, see <b>Sect</b> i<br>f T32 to select | ion 11.5 "Per          | ipheral Pin Sel      | ect (PPS)".          |  |  |  |