Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb410t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA406

- 06 PIC24FJ64GB406

- PIC24FJ128GA406

PIC24FJ256GA406

- PIC24FJ128GB406

PIC24FJ256GB406

- PIC24FJ64GA410

PIC24FJ64GB410

- PIC24FJ128GA410

PIC24FJ128GB410

- PIC24FJ256GA410

- PIC24FJ256GB410

- PIC24FJ64GA412

- PIC24FJ64GB412

- PIC24FJ128GA412PIC24FJ256GA412

- PIC24FJ128GB412

PIC24FJ256GB412

- The PIC24FJ256GA412/GB412 family expands the capabilities of the PIC24F family by adding a complete selection of advanced analog peripherals to its existing digital features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals, USB On-The-Go (OTG) and a built-in LCD Controller and driver, makes this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

## 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ256GA412/GB412 family of devices incorporates a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep, with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC, for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC), to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, the PIC24FJ256GA412/ GB412 devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

#### 1.1.3 DUAL PARTITION FLASH PROGRAM MEMORY

A brand new feature to the PIC24F family is the use of Dual Partition Flash program memory technology. This allows PIC24FJ256GA412/GB412 family devices a range of new operating options not available before:

- Dual Partition Operation, which can store two different applications in their own code partition, and allows for the support of robust bootloader applications and enhanced security

- Live Update Operation, which allows the main application to continue operation while the second Flash partition is being reprogrammed – all without adding Wait states to code execution

- Direct Run-Time Programming from Data RAM, with the option of data compression in the RAM image

PIC24FJ256GA412/GB412 family devices can also operate with their two Flash partitions as one large program memory, providing space for large and complex applications.

|              | Pin/Pad Number |                 |                  |     |              |                                     |

|--------------|----------------|-----------------|------------------|-----|--------------|-------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                         |

| AN0          | 16             | 25              | K2               | I   | ANA          | A/D Analog Inputs                   |

| AN1          | 15             | 24              | K1               | I   | ANA          |                                     |

| AN1-         | 15             | 24              | K1               | I   | ANA          |                                     |

| AN2          | 14             | 23              | J2               | I   | ANA          |                                     |

| AN3          | 13             | 22              | J1               | I   | ANA          |                                     |

| AN4          | 12             | 21              | H2               | I   | ANA          |                                     |

| AN5          | 11             | 20              | H1               | I   | ANA          |                                     |

| AN6          | 17             | 26              | L1               | I   | ANA          |                                     |

| AN7          | 18             | 27              | J3               | I   | ANA          |                                     |

| AN8          | 21             | 32              | K4               | I   | ANA          |                                     |

| AN9          | 22             | 33              | L4               | I   | ANA          |                                     |

| AN10         | 23             | 34              | H5               | I   | ANA          |                                     |

| AN11         | 24             | 35              | K5               | I   | ANA          |                                     |

| AN12         | 27             | 41              | J7               | I   | ANA          |                                     |

| AN13         | 28             | 42              | L7               | I   | ANA          |                                     |

| AN14         | 29             | 43              | K7               | I   | ANA          |                                     |

| AN15         | 30             | 44              | L8               | I   | ANA          |                                     |

| AN16         | _              | 9               | E1               | I   | ANA          |                                     |

| AN17         | _              | 10              | E3               | I   | ANA          |                                     |

| AN18         | _              | 11              | F4               | I   | ANA          |                                     |

| AN19         | _              | 12              | F2               | I   | ANA          |                                     |

| AN20         | _              | 14              | F3               | I   | ANA          |                                     |

| AN21         | _              | 19              | G2               | I   | ANA          |                                     |

| AN22         | _              | 92              | E11              | I   | ANA          |                                     |

| AN23         | —              | 91              | E10              | I   | ANA          |                                     |

| AVDD         | 19             | 30              | J4               | Р   | —            | Positive Supply for Analog modules  |

| AVss         | 20             | 31              | L3               | Р   | —            | Ground Reference for Analog modules |

| C1INA        | 11             | 20              | H1               | I   | ANA          | Comparator 1 Input A                |

| C1INB        | 12             | 21              | H2               | Ι   | ANA          | Comparator 1 Input B                |

| C1INC        | 5,8            | 11,14           | F4,F3            | Ι   | ANA          | Comparator 1 Input C                |

| C1IND        | 4              | 10              | E3               | I   | ANA          | Comparator 1 Input D                |

| C2INA        | 13             | 22              | J1               | Ι   | ANA          | Comparator 2 Input A                |

| C2INB        | 14             | 23              | J2               | I   | ANA          | Comparator 2 Input B                |

| C2INC        | 8              | 14              | F3               | I   | ANA          | Comparator 2 Input C                |

| C2IND        | 6              | 12              | F2               | I   | ANA          | Comparator 2 Input D                |

| C3INA        | 55             | 84              | C7               | I   | ANA          | Comparator 3 Input A                |

| C3INB        | 54             | 83              | D7               | I   | ANA          | Comparator 3 Input B                |

| C3INC        | 8,45           | 14,71           | F3,C11           | I   | ANA          | Comparator 3 Input C                |

| C3IND        | 44             | 70              | D11              | I   | ANA          | Comparator 3 Input D                |

| CLC3OUT      | 46             | 72              | D9               | 0   | DIG          | CLC3 Output                         |

| CLC4OUT      | 42             | 68              | E9               | 0   | DIG          | CLC4 Output                         |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION

**Legend:** TTL = TTL input buffer

ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

| TADLE 1-4.   | 1              |                 |                  |     |                |                    |

|--------------|----------------|-----------------|------------------|-----|----------------|--------------------|

|              |                | n/Pad Numl      |                  |     | In most Dest() | Departmetter       |

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer   | Description        |

| RB0          | 16             | 25              | K2               | I/O | DIG/ST         | PORTB Digital I/Os |

| RB1          | 15             | 24              | K1               | I/O | DIG/ST         |                    |

| RB2          | 14             | 23              | J2               | I/O | DIG/ST/TTL     |                    |

| RB3          | 13             | 22              | J1               | I/O | DIG/ST/TTL     |                    |

| RB4          | 12             | 21              | H2               | I/O | DIG/ST/TTL     |                    |

| RB5          | 11             | 20              | H1               | I/O | DIG/ST/TTL     |                    |

| RB6          | 17             | 26              | L1               | I/O | DIG/ST         |                    |

| RB7          | 18             | 27              | J3               | I/O | DIG/ST/TTL     |                    |

| RB8          | 21             | 32              | K4               | I/O | DIG/ST         |                    |

| RB9          | 22             | 33              | L4               | I/O | DIG/ST         |                    |

| RB10         | 23             | 34              | H5               | I/O | DIG/ST         | 1                  |

| RB11         | 24             | 35              | K5               | I/O | DIG/ST         | ]                  |

| RB12         | 27             | 41              | J7               | I/O | DIG/ST         | 1                  |

| RB13         | 28             | 42              | L7               | I/O | DIG/ST         |                    |

| RB14         | 29             | 43              | K7               | I/O | DIG/ST         |                    |

| RB15         | 30             | 44              | L8               | I/O | DIG/ST         |                    |

| RC1          |                | 6               | D1               | I/O | DIG/ST         | PORTC Digital I/Os |

| RC2          | _              | 7               | E4               | I/O | DIG/ST         |                    |

| RC3          | _              | 8               | E2               | I/O | DIG/ST         |                    |

| RC4          |                | 9               | E1               | I/O | DIG/ST         |                    |

| RC12         | 39             | 63              | F9               | I/O | DIG/ST         |                    |

| RC13         | 47             | 73              | C10              | I   | ST             |                    |

| RC14         | 48             | 74              | B11              | I   | ST             |                    |

| RC15         | 40             | 64              | F11              | I/O | DIG/ST         |                    |

| RD0          | 46             | 72              | D9               | I/O | DIG/ST         | PORTD Digital I/Os |

| RD1          | 49             | 76              | A11              | I/O | DIG/ST         |                    |

| RD2          | 50             | 77              | A10              | I/O | DIG/ST         |                    |

| RD3          | 51             | 78              | B9               | I/O | DIG/ST         |                    |

| RD4          | 52             | 81              | C8               | I/O | DIG/ST         |                    |

| RD5          | 53             | 82              | B8               | I/O | DIG/ST         |                    |

| RD6          | 54             | 83              | D7               | I/O | DIG/ST         | 1                  |

| RD7          | 55             | 84              | C7               | I/O | DIG/ST         | 1                  |

| RD8          | 42             | 68              | E9               | I/O | DIG/ST         | 1                  |

| RD9          | 43             | 69              | E10              | I/O | DIG/ST         | 1                  |

| RD10         | 44             | 70              | D11              | I/O | DIG/ST         | 1                  |

| RD11         | 45             | 71              | C11              | I/O | DIG/ST         | 1                  |

| RD12         | —              | 79              | A9               | I/O | DIG/ST         | 1                  |

| RD13         | _              | 80              | D8               | I/O | DIG/ST         | 1                  |

| RD14         | —              | 47              | L9               | I/O | DIG/ST         | 1                  |

| RD15         | —              | 48              | K9               | I/O | DIG/ST         | 1                  |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24FJ256GA412/GB412 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All analog power pins (AVDD and AVSS), regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- The USB transceiver supply, VUSB3V3, regardless of whether or not the USB module is used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- Any voltage reference pins used when external voltage reference for analog modules is implemented (AVREF+/AVREF-, CVREF+/CVREFand DVREF+)

- **Note:** All analog power supply and return pins must always be connected, regardless of whether any of the analog modules are being used.

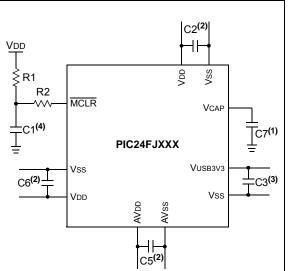

The minimum mandatory connections are shown in Figure 2-1.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},\,6.3\text{V}$  or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100 $\Omega$  to 470 $\Omega$

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for details on selecting the proper capacitor for VCAP.

- 2: The example shown is for a PIC24F device with five power and ground pairs (including analog and USB). Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

- Implemented on PIC24FJXXXGB4XX devices only. See Section 20.1 "Hardware Configuration" for details on connecting the pins for USB operation.

- 4: C1 is optional, see Section 2.3 "Master Clear (MCLR) Pin" and Section 2.5 "ICSP Pins" for more information.

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are described in **Section 6.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address (TBLPAG) register. TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only Table Read operations will execute in the configuration memory space where Device IDs are located. Table Write operations are not allowed.

|       | 99303                     | gram Space                                                               |                                     |                                             |                     |

|-------|---------------------------|--------------------------------------------------------------------------|-------------------------------------|---------------------------------------------|---------------------|

|       |                           |                                                                          |                                     |                                             |                     |

| 23 25 | 9<br>0200005<br>0200005 _ |                                                                          | 23                                  |                                             | 8 0                 |

|       | 200000k                   | versen<br>versen<br>versen<br>versen<br>vine address ha<br>wine the care | defined by 1995<br>alions are chows | )<br>)<br>flori is distanti<br>REUPAO conje | ined by the data EA |

### FIGURE 4-11: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

|  | REGISTER 8-43: | <b>IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21</b> |

|--|----------------|------------------------------------------------------|

|--|----------------|------------------------------------------------------|

| U-0     | R/W-1     | R/W-0     | R/W-0     | U-0 | R/W-1     | R/W-0     | R/W-0     |

|---------|-----------|-----------|-----------|-----|-----------|-----------|-----------|

| _       | U4ERIP2   | U4ERIP1   | U4ERIP0   | _   | USB1IP2   | USB1IP1   | USB1IP0   |

| bit 15  |           |           | •         |     | -         |           | bit 8     |

|         |           |           |           |     |           |           |           |

| U-0     | R/W-1     | R/W-0     | R/W-0     | U-0 | R/W-1     | R/W-0     | R/W-0     |

| _       | I2C2BCIP2 | I2C2BCIP1 | I2C2BCIP0 | _   | I2C1BCIP2 | I2C1BCIP1 | I2C1BCIP0 |

| bit 7   |           |           |           |     |           | •         | bit 0     |

|         |           |           |           |     |           |           |           |

| Legend: |           |           |           |     |           |           |           |

| Legena:      |                 |                                  |                       |                    |

|--------------|-----------------|----------------------------------|-----------------------|--------------------|

| R = Readab   | ole bit         | W = Writable bit                 | U = Unimplemented bit | , read as '0'      |

| -n = Value a | at POR          | '1' = Bit is set                 | '0' = Bit is cleared  | x = Bit is unknown |

|              |                 |                                  |                       |                    |

| bit 15       | Unimple         | mented: Read as '0'              |                       |                    |

| bit 14-12    | U4ERIP•         | <2:0>: UART4 Error Interrupt     | Priority bits         |                    |

|              | 111 <b>= In</b> | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              | 000 <b>= In</b> | terrupt source is disabled       |                       |                    |

| bit 11       | Unimple         | mented: Read as '0'              |                       |                    |

| bit 10-8     |                 | <2:0>: USB1 (USB OTG) Inte       |                       |                    |

|              | 111 <b>= In</b> | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              |                 | terrupt source is disabled       |                       |                    |

| bit 7        | -               | mented: Read as '0'              |                       |                    |

| bit 6-4      |                 | P<2:0>: I2C2 Bus Collision Ir    |                       |                    |

|              | 111 = In        | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

| 1.1.0        |                 | terrupt source is disabled       |                       |                    |

| bit 3        | -               | mented: Read as '0'              |                       |                    |

| bit 2-0      |                 | P<2:0>: I2C1 Bus Collision In    |                       |                    |

|              | •               | terrupt is Priority 7 (highest p | nonty interrupt)      |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              | $000 = \ln 3$   | terrupt source is disabled       |                       |                    |

|              |                 |                                  |                       |                    |

|              |                 |                                  |                       |                    |

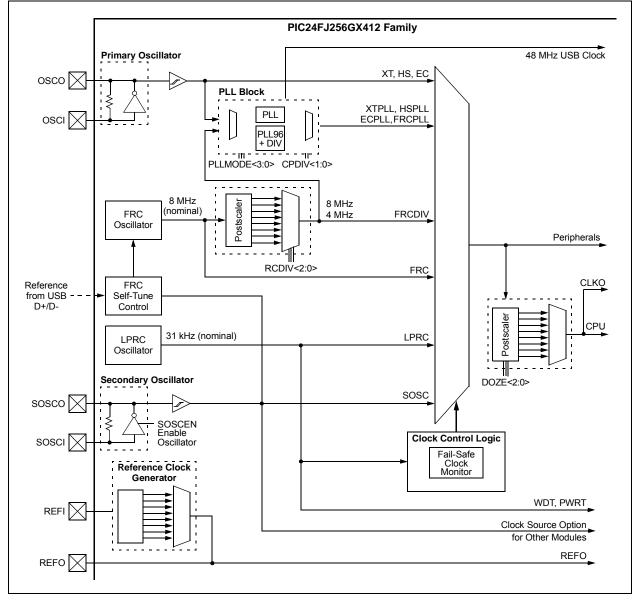

## 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Oscillator" (DS39700). The information in this data sheet supersedes the information in the FRM.

The oscillator system for PIC24FJ256GA412/GB412 family devices has the following features:

A Total of Four External and Internal Oscillator Options as Clock Sources, providing 11 Different Clock Modes

- An On-Chip PLL Block to provide a Wide Range of Precise Frequency Options for the System Clock, plus a Stable 48 MHz Clock for USB Devices

- Software-Controllable Switching between Various Clock Sources

- Software-Controllable Postscaler for Selective Clocking of CPU for System Power Savings

- A Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- A Separate and Independently Configurable Reference Clock for Synchronizing External Hardware

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24FJ256GA412/GB412 FAMILY GENERAL CLOCK DIAGRAM

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | T5CKR5 | T5CKR4 | T5CKR3 | T5CKR2 | T5CKR1 | T5CKR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | T4CKR5 | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | T5CKR<5:0>: Assign Timer5 Clock Input (T5CK) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | T4CKR<5:0>: Assign Timer4 Clock Input (T4CK) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 11-8: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | IC2R5 | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC1R5 | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC2R<5:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC1R<5:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits

| U-0           | U-0         | R/W-0            | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|---------------|-------------|------------------|---------------|-------------------|------------------|-----------------|--------|

|               | _           | RP17R5           | RP17R4        | RP17R3            | RP17R2           | RP17R1          | RP17R0 |

| bit 15        |             |                  |               |                   |                  |                 | bit 8  |

|               |             |                  |               |                   |                  |                 |        |

| U-0           | U-0         | R/W-0            | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —             | —           | RP16R5           | RP16R4        | RP16R3            | RP16R2           | RP16R1          | RP16R0 |

| bit 7         |             |                  |               |                   |                  |                 | bit 0  |

|               |             |                  |               |                   |                  |                 |        |

| Legend:       |             |                  |               |                   |                  |                 |        |

| R = Readable  | e bit       | W = Writable I   | oit           | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|               |             |                  |               |                   |                  |                 |        |

| bit 15-14     | Unimplement | ted: Read as 'd  | )'            |                   |                  |                 |        |

| bit 13-8      | RP17R<5:0>: | RP17 Output I    | ⊃in Mapping b | its               |                  |                 |        |

#### REGISTER 11-31: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| bit 7-6 | Unimplemented: Read as '0'                                                                             |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 5-0 | RP16R<5:0>: RP16 Output Pin Mapping bits                                                               |

|         | Peripheral Output Number n is assigned to pin, RP16 (see Table 11-12 for peripheral function numbers). |

Peripheral Output Number n is assigned to pin, RP17 (see Table 11-12 for peripheral function numbers).

### REGISTER 11-32: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0                                                                  | U-0                               | R/W-0  | R/W-0           | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

|----------------------------------------------------------------------|-----------------------------------|--------|-----------------|--------------|------------------|----------|--------|

|                                                                      | —                                 | RP19R5 | RP19R4          | RP19R3       | RP19R2           | RP19R1   | RP19R0 |

| bit 15                                                               |                                   |        |                 |              |                  |          | bit 8  |

|                                                                      |                                   |        |                 |              |                  |          |        |

| U-0                                                                  | U-0                               | R/W-0  | R/W-0           | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

| —                                                                    | —                                 | RP18R5 | RP18R4          | RP18R3       | RP18R2           | RP18R1   | RP18R0 |

| bit 7                                                                |                                   |        |                 |              |                  |          | bit 0  |

|                                                                      |                                   |        |                 |              |                  |          |        |

| Legend:                                                              |                                   |        |                 |              |                  |          |        |

| R = Readable                                                         | R = Readable bit W = Writable bit |        |                 | U = Unimplem | nented bit, read | l as '0' |        |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |                                   |        | x = Bit is unkr | nown         |                  |          |        |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP19R<5:0>:** RP19 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP19 (see Table 11-12 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP18R<5:0>:** RP18 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP18 (see Table 11-12 for peripheral function numbers).

NOTES:

### 13.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704). The information in this data sheet supersedes the information in the FRM.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two Independent 16-Bit Timers with all 16-Bit Operating Modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep Modes

- Interrupt on a 32-Bit Period Register Match

- A/D Event Trigger (only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D Event Trigger. This trigger is implemented only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1; T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer5 are the most significant word of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 or Timer5 interrupt flags. To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 or T45 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word (msw) of the value, while PR2 (or PR4) contains the least significant word (lsw).

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2> (or TMR<5:4>). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 11.5 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON (TxCON<15> = 1) bit.

| R/W-0              | U-0                                  | R/W-0                                         | U-0                   | U-0              | U-0             | R/W-0                       | R/W-0                  |

|--------------------|--------------------------------------|-----------------------------------------------|-----------------------|------------------|-----------------|-----------------------------|------------------------|

| TON <sup>(2)</sup> | —                                    | TSIDL <sup>(2)</sup>                          | —                     | _                | _               | TECS1 <sup>(2,3)</sup>      | TECS0 <sup>(2,3)</sup> |

| bit 15             |                                      |                                               |                       |                  |                 |                             | bit                    |

|                    |                                      |                                               |                       |                  |                 |                             |                        |

| U-0                | R/W-0                                | R/W-0                                         | R/W-0                 | U-0              | U-0             | R/W-0                       | U-0                    |

|                    | TGATE <sup>(2)</sup>                 | TCKPS1 <sup>(2)</sup>                         | TCKPS0 <sup>(2)</sup> | _                | _               | TCS <sup>(2,3)</sup>        | _                      |

| bit 7              |                                      |                                               |                       |                  |                 |                             | bit                    |

| Legend:            |                                      |                                               |                       |                  |                 |                             |                        |

| R = Reada          | ble bit                              | W = Writable                                  | bit                   | U = Unimplen     | nented bit, rea | ad as '0'                   |                        |

| -n = Value         | at POR                               | '1' = Bit is set                              |                       | '0' = Bit is cle | ared            | x = Bit is unkn             | iown                   |

|                    |                                      |                                               |                       |                  |                 |                             |                        |

| bit 15             | TON: Timery                          | On bit <sup>(2)</sup>                         |                       |                  |                 |                             |                        |

|                    | 1 = Starts 16-                       |                                               |                       |                  |                 |                             |                        |

|                    | 0 = Stops 16-                        |                                               |                       |                  |                 |                             |                        |

| bit 14             | •                                    | ted: Read as '                                |                       |                  |                 |                             |                        |

| bit 13             |                                      | y Stop in Idle N                              |                       |                  |                 |                             |                        |

|                    |                                      | ues module opera module opera                 |                       |                  | le mode         |                             |                        |

| bit 12-10          |                                      | ted: Read as '                                |                       |                  |                 |                             |                        |

| bit 9-8            | TECS<1:0>:                           | Timery Extende                                | ed Clock Sourc        | e Select bits (s | elected when    | 1 TCS = 1) <sup>(2,3)</sup> |                        |

|                    |                                      | Timer (TMRCk                                  |                       |                  |                 | ,                           |                        |

|                    | 10 = LPRC O                          |                                               |                       |                  |                 |                             |                        |

|                    | 01 = TxCK ex<br>00 = SOSC            | ternal clock inp                              | but                   |                  |                 |                             |                        |

| bit 7              |                                      | ted: Read as '                                | ı'                    |                  |                 |                             |                        |

| bit 6              | -                                    | ery Gated Time                                |                       | Enable hit(2)    |                 |                             |                        |

|                    | When TCS =                           | •                                             |                       |                  |                 |                             |                        |

|                    | This bit is ign                      | ored.                                         |                       |                  |                 |                             |                        |

|                    | When TCS =                           |                                               |                       |                  |                 |                             |                        |

|                    |                                      | ne accumulatio                                |                       |                  |                 |                             |                        |

| bit 5-4            |                                      | ne accumulatio<br>: Timery Input (            |                       | Soloot hito(2)   |                 |                             |                        |

| DIL 3-4            | 11 = 1:256                           | . Timery input                                |                       | Select bits ?    |                 |                             |                        |

|                    | 10 = 1:64                            |                                               |                       |                  |                 |                             |                        |

|                    | 01 <b>= 1:8</b>                      |                                               |                       |                  |                 |                             |                        |

|                    | 00 = 1:1                             |                                               |                       |                  |                 |                             |                        |

| bit 3-2            |                                      | ted: Read as 'o                               |                       |                  |                 |                             |                        |

| bit 1              | •                                    | Clock Source S                                |                       |                  |                 |                             |                        |

|                    | 1 = External o<br>0 = Internal c     | clock from pin, <sup>-</sup><br>lock (Fosc/2) | TyCK (on the ri       | sing edge)       |                 |                             |                        |

| bit 0              |                                      | ted: Read as '                                | )'                    |                  |                 |                             |                        |

|                    | Changing the valu                    | -                                             | nile the timer is     | running (TON :   | = 1) causes th  | e timer prescale            | counter to             |

|                    | When 32-bit oper operation; all time |                                               |                       |                  |                 | ts have no effect           | on Timery              |

| 3:                 | If TCS = 1 and Th                    | ECS<1:0> = x1                                 | -                     | external timer i | nput (TyCK) r   |                             |                        |

### REGISTER 13-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER<sup>(1)</sup>

#### REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| —      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R-0, HSC | R-0, HSC | R/W-0               | R/W-0               | R/W-0               |

|-------|-------|-------|----------|----------|---------------------|---------------------|---------------------|

| —     | ICI1  | ICI0  | ICOV     | ICBNE    | ICM2 <sup>(1)</sup> | ICM1 <sup>(1)</sup> | ICM0 <sup>(1)</sup> |

| bit 7 |       |       |          |          |                     |                     | bit 0               |

| Legend:           | HSC = Hardware Settable/C | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

|-------------------|---------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'    |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

| bit 15-14     | Unimplemented: Read as '0'                                                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13        | ICSIDL: Input Capture x Module Stop in Idle Control bit                                                                                                   |

|               | 1 = Input capture module halts in CPU Idle mode                                                                                                           |

|               | 0 = Input capture module continues to operate in CPU Idle mode                                                                                            |

| bit 12-10     | ICTSEL<2:0>: Input Capture x Timer Select bits                                                                                                            |

|               | 111 = System clock (Fosc/2)                                                                                                                               |

|               | 110 = Reserved<br>101 = Reserved                                                                                                                          |

|               | 100 = Timer1                                                                                                                                              |

|               | 011 = Timer5                                                                                                                                              |

|               | 010 = Timer4                                                                                                                                              |

|               | 001 = Timer2<br>000 = Timer3                                                                                                                              |

| bit 9-7       | Unimplemented: Read as '0'                                                                                                                                |

| bit 6-5       | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                    |

|               | 11 = Interrupt on every fourth capture event                                                                                                              |

|               | 10 = Interrupt on every third capture event                                                                                                               |

|               | 01 = Interrupt on every second capture event                                                                                                              |

|               | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4         | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                                                                |

|               | 1 = Input capture overflow has occurred                                                                                                                   |

| <b>h</b> :+ 0 | 0 = No input capture overflow has occurred                                                                                                                |

| bit 3         | ICBNE: Input Capture x Buffer Empty Status bit (read-only)                                                                                                |

|               | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

| bit 2-0       | ICM<2:0>: Input Capture x Mode Select bits <sup>(1)</sup>                                                                                                 |

|               | 111 = Interrupt mode: Input capture functions as an interrupt pin only when the device is in Sleep or                                                     |

|               | Idle mode (rising edge detect only, all other control bits are not applicable)                                                                            |

|               | 110 = Unused (module is disabled)                                                                                                                         |

|               | 101 = Prescaler Capture mode: Capture on every 16 <sup>th</sup> rising edge<br>100 = Prescaler Capture mode: Capture on every 4 <sup>th</sup> rising edge |

|               | 011 = Simple Capture mode: Capture on every rising edge                                                                                                   |

|               | 010 = Simple Capture mode: Capture on every falling edge                                                                                                  |

|               | 001 = Edge Detect Capture mode: Capture on every edge (rising and falling); ICI<1:0> bits do not                                                          |

|               | control interrupt generation for this mode                                                                                                                |

|               | 000 = Input capture module is turned off                                                                                                                  |

Note 1: The ICx input must also be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

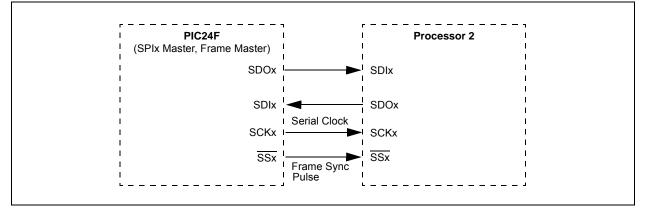

#### FIGURE 17-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

#### REGISTER 19-2: UxSTAL: UARTx STATUS LOW AND CONTROL REGISTER

| R/W-0           | R/W-0                 | R/W-0                    | R/W-0           | R/W-0, HC                             | R/W-0                | R-0, HSC        | R-1, HSC |  |

|-----------------|-----------------------|--------------------------|-----------------|---------------------------------------|----------------------|-----------------|----------|--|

| UTXISEL1        | UTXINV <sup>(1)</sup> | UTXISEL0                 | URXEN           | UTXBRK                                | UTXEN <sup>(2)</sup> | UTXBF           | TRMT     |  |

| bit 15          |                       | •                        |                 |                                       |                      |                 | bit 8    |  |

|                 |                       |                          |                 |                                       |                      |                 |          |  |

| R/W-0           | R/W-0                 | R/W-0                    | R-1, HSC        | R-0, HSC                              | R-0, HSC             | R/C-0, HS       | R-0, HSC |  |

| URXISEL1        | URXISEL0              | ADDEN                    | RIDLE           | PERR                                  | FERR                 | OERR            | URXDA    |  |

| bit 7           |                       |                          |                 |                                       |                      |                 | bit      |  |

|                 |                       |                          |                 |                                       |                      |                 |          |  |

| Legend:         |                       | C = Clearable            | bit             | HSC = Hardware Settable/Clearable bit |                      |                 |          |  |

| R = Readable    | bit                   | W = Writable b           | pit             | U = Unimplemented bit, read as '0'    |                      |                 |          |  |

| -n = Value at I | POR                   | '1' = Bit is set         |                 | '0' = Bit is clea                     | ared                 | x = Bit is unkr | nown     |  |

| HS = Hardwar    | e Settable bit        | HC = Hardware            | e Clearable bit |                                       |                      |                 |          |  |

|                 |                       |                          |                 |                                       |                      |                 |          |  |

| bit 15,13       | UTXISEL<1:0           | <b>)&gt;:</b> UARTx Trar | smission Interi | rupt Mode Seleo                       | ction bits           |                 |          |  |

|                 |                       | ed; do not use           |                 |                                       |                      |                 |          |  |

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

| bit 14 | <b>UTXINV:</b> UARTx IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit <sup>(1)</sup> |

|--------|-----------------------------------------------------------------------------------------------|

|--------|-----------------------------------------------------------------------------------------------|

|         | For IREN = 0:<br>1 = UxTX Idle state is '0'<br>0 = UxTX Idle state is '1'<br>For IREN = 1:<br>1 = UxTX Idle state is '1'<br>0 = UxTX Idle state is '0'                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12  | URXEN: UARTx Receive Enable bit                                                                                                                                                                                                     |

|         | <ul> <li>1 = Receive is enabled, UxRX pin is controlled by UARTx</li> <li>0 = Receive is disabled, UxRX pin is controlled by the port</li> </ul>                                                                                    |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                                    |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> <li>0 = Sync Break transmission is disabled or completed</li> </ul> |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(2)</sup>                                                                                                                                                                                     |

|         | <ul> <li>1 = Transmit is enabled, UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by the port</li> </ul>                     |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                            |

|         | <ul> <li>1 = Transmit buffer is full</li> <li>0 = Transmit buffer is not full, at least one more character can be written</li> </ul>                                                                                                |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                 |

|         | <ul> <li>1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit Shift Register is not empty, a transmission is in progress or queued</li> </ul>              |

| Note 1: | The value of this bit only affects the transmit properties of the module when the IrDA encoder is enabled (IREN = 1).                                                                                                               |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

#### REGISTER 20-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| STALLIF   | —   | RESUMEIF  | IDLEIF    | TRNIF     | SOFIF     | UERRIF    | URSTIF    |

| bit 7     |     |           |           |           |           |           | bit 0     |

| Legend:          | HS = Hardware Settable b   | HS = Hardware Settable bit |                    |  |  |

|------------------|----------------------------|----------------------------|--------------------|--|--|

| R = Readable bit | K = Write '1' to Clear bit | U = Unimplemented bit,     | read as '0'        |  |  |

| -n = Value at PO | R '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                                                                                                                                          |

|          | <ul> <li>1 = A STALL handshake was sent by the peripheral during the handshake phase of the transaction in<br/>Device mode</li> <li>0 = A STALL handshake has not been sent</li> </ul>                                                                                                                                                          |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 5    | RESUMEIF: Resume Interrupt bit                                                                                                                                                                                                                                                                                                                  |

| bito     | <ul> <li>1 = A K-state is observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed)</li> <li>0 = No K-state is observed</li> </ul>                                                                                                                                                              |

| bit 4    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Idle condition is detected (constant Idle state of 3 ms or more)</li> <li>0 = No Idle condition is detected</li> </ul>                                                                                                                                                                                                             |

| bit 3    | TRNIF: Token Processing Complete Interrupt bit                                                                                                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Processing of the current token is complete; read the U1STAT register for endpoint information</li> <li>0 = Processing of the current token is not complete; clear the U1STAT register or load the next token from STAT (clearing this bit causes the STAT FIFO to advance)</li> </ul>                                             |

| bit 2    | SOFIF: Start-of-Frame Token Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | 1 = A Start-of-Frame token is received by the peripheral or the Start-of-Frame threshold is reached by<br>the host                                                                                                                                                                                                                              |

|          | 0 = No Start-of-Frame token is received or threshold reached                                                                                                                                                                                                                                                                                    |

| bit 1    | UERRIF: USB Error Condition Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | 1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set this bit                                                                                                                                                                                                                                  |

|          | 0 = No unmasked error condition has occurred                                                                                                                                                                                                                                                                                                    |

| bit 0    | URSTIF: USB Reset Interrupt bit                                                                                                                                                                                                                                                                                                                 |

|          | 1 = Valid USB Reset has occurred for at least 2.5 μs; Reset state must be cleared before this bit can be reasserted                                                                                                                                                                                                                             |

|          | <ul> <li>0 = No USB Reset has occurred; individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared</li> </ul> |

|          | Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause                                                                                                                |

all set bits, at the moment of the write, to become cleared.

| R/W-0                                                                                                               | R/W-0                                                                                                                                                                            | R/W-0                                                   | R/W-0                                     | U-0                  | R/W-0            | R/W-0           | R/W-0   |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|----------------------|------------------|-----------------|---------|

| CSDIS                                                                                                               | CSP                                                                                                                                                                              | CSPTEN                                                  | BEP                                       | —                    | WRSP             | RDSP            | SM      |

| bit 15                                                                                                              |                                                                                                                                                                                  |                                                         |                                           |                      |                  |                 | bit 8   |

| R/W-0                                                                                                               | R/W-0                                                                                                                                                                            | R/W-0                                                   | U-0                                       | U-0                  | U-0              | U-0             | U-0     |