Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 101                                                                            |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

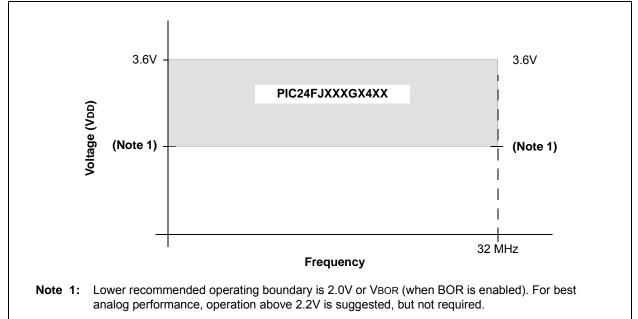

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

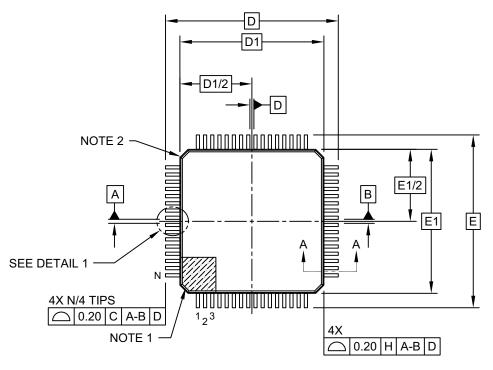

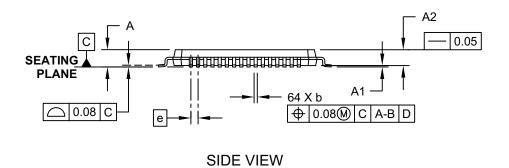

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb412-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

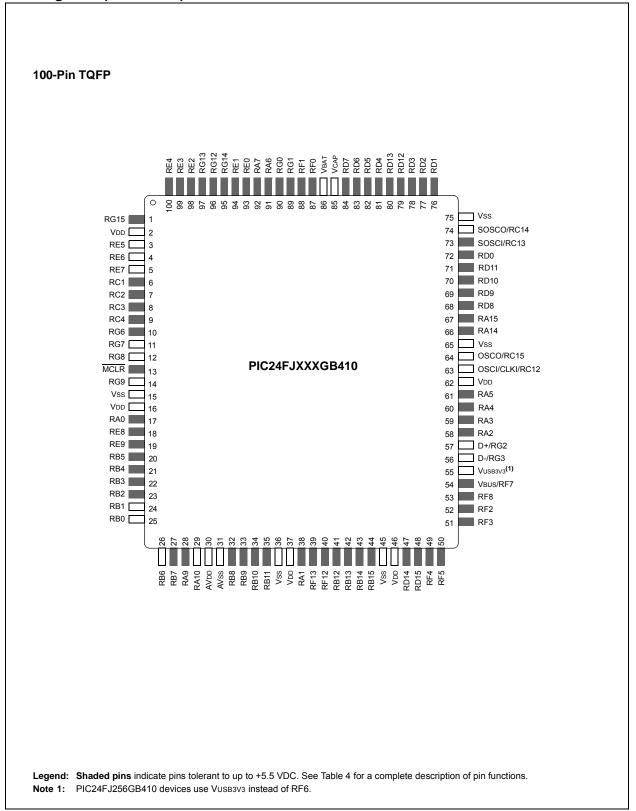

#### Pin Diagrams (Continued)

#### **Pin/Pad Number Pin Function** I/O Input Buffer Description 64-Pin 100-Pin 121-Pin TQFP TQFP TFBGA SEG0 4 10 E3 0 ANA LCD Driver Segment Outputs SEG1 ANA 8 14 F3 0 SEG2 11 20 H1 0 ANA 0 SEG3 12 21 H2 ANA SEG4 13 22 J1 0 ANA 0 SEG5 14 23 J2 ANA SEG6 15 24 K1 0 ANA SEG7 16 25 K2 0 ANA SEG8 29 43 K7 ANA 0 SEG9 30 44 L8 0 ANA SEG10 31 49 L10 ANA 0 SEG11 32 50 L11 0 ANA SEG12 33 51 K10 0 ANA SEG13 42 68 E9 0 ANA SEG14 E10 43 69 0 ANA SEG15 44 70 D11 0 ANA 71 C11 0 SEG16 45 ANA SEG17 46 72 D9 0 ANA SEG18 27 41 J7 0 ANA L7 SEG19 28 42 0 ANA SEG20 49 76 A11 0 ANA SEG21 50 77 A10 0 ANA SEG22 51 78 B9 0 ANA SEG23 52 81 C8 0 ANA SEG24 53 82 B8 0 ANA SEG25 54 83 D7 0 ANA SEG26 55 84 C7 0 ANA SEG27 B6 0 58 87 ANA SEG28 \_\_\_\_ 61 G9 0 ANA 23 SEG29 H5 0 ANA 34 SEG30 22 33 L4 0 ANA 0 SEG31 21 32 K4 ANA SEG32 D1 0 ANA \_\_\_\_ 6 SEG33 8 E2 0 ANA \_\_\_\_ SEG34 18 G1 0 ANA \_\_\_\_ SEG35 19 G2 0 ANA SEG36 28 L2 0 ANA SEG37 29 K3 0 ANA \_\_\_\_ SEG38 47 L9 0 ANA SEG39 \_\_\_\_ 48 K9 0 ANA SEG40 52 K11 0 ANA

#### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

|              | Pir | /Pad Numl | ber              |     |              |                                          |

|--------------|-----|-----------|------------------|-----|--------------|------------------------------------------|

| Pin Function |     |           | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                              |

| SEG41        | —   | 53        | J10              | 0   | ANA          | LCD Driver Segment Outputs               |

| SEG42        | —   | 66        | E11              | 0   | ANA          |                                          |

| SEG43        | _   | 67        | E8               | 0   | ANA          |                                          |

| SEG44        | _   | 79        | A9               | 0   | ANA          |                                          |

| SEG45        | —   | 80        | D8               | 0   | ANA          |                                          |

| SEG46        | —   | 89        | E6               | 0   | ANA          |                                          |

| SEG47        | 59  | 88        | A6               | 0   | ANA          |                                          |

| SEG48        | —   | 17        | G3               | 0   | ANA          |                                          |

| SEG49        | —   | 90        | A5               | 0   | ANA          |                                          |

| SEG50        | —   | 1         | B2               | 0   | ANA          |                                          |

| SEG51        | —   | 7         | E4               | 0   | ANA          |                                          |

| SEG52        | —   | 9         | E1               | 0   | ANA          |                                          |

| SEG53        | —   | 39        | L6               | 0   | ANA          |                                          |

| SEG54        | —   | 40        | K6               | 0   | ANA          |                                          |

| SEG55        | —   | 58        | H11              | 0   | ANA          |                                          |

| SEG56        | —   | 59        | G10              | 0   | ANA          |                                          |

| SEG57        | —   | 91        | C5               | 0   | ANA          |                                          |

| SEG58        | —   | 92        | B5               | 0   | ANA          |                                          |

| SEG59        | —   | 95        | C4               | 0   | ANA          |                                          |

| SEG60        | —   | 96        | C3               | 0   | ANA          |                                          |

| SEG61        | —   | 97        | A3               | 0   | ANA          |                                          |

| SEG62        | 64  | 100       | A1               | 0   | ANA          |                                          |

| SEG63        | 18  | 27        | J3               | 0   | ANA          |                                          |

| SOSCI        | 47  | 73        | C10              |     | —            | Secondary Oscillator/Timer1 Clock Input  |

| SOSCO        | 48  | 74        | B11              | —   | _            | Secondary Oscillator/Timer1 Clock Output |

| SS4/FSYNC4   | 24  | 35        | K5               | I/O | DIG/ST       | SPI4 Slave Select/Frame Sync             |

| T1CK         | 22  | 33        | L4               | I   | ST           | Timer1 Clock                             |

| ТСК          | 27  | 38        | J6               | I   | ST           | JTAG Test Clock/Programming Clock Input  |

| TDI          | 28  | 60        | G11              | I   | ST           | JTAG Test Data/Programming Data Input    |

| TDO          | 24  | 61        | G9               | 0   | DIG          | JTAG Test Data Output                    |

| TMPR         | 22  | 33        | L4               |     | _            | Tamper Detect Input                      |

| TMS          | 23  | 17        | G3               | I   | ST           | JTAG Test Mode Select Input              |

| U5CTS        | 58  | 87        | B6               | I   | ST           | UART5 Clear-to-Send Output               |

| U5RTS/U5BCLK | 55  | 84        | C7               | 0   | DIG          | UART5 Request-to-Send Input              |

| U5RX         | 54  | 83        | D7               | I   | ST           | UART5 Receive Input                      |

| U5TX         | 49  | 76        | A11              | 0   | DIG          | UART5 Transmit Output                    |

| U6CTS        | 46  | 72        | D9               | I   | ST           | UART6 Clear-to-Send Output               |

| U6RTS/U6BCLK | 42  | 68        | E9               | 0   | DIG          | UART6 Request-to-Send Input              |

| U6RX         | 27  | 41        | J7               | 1   | ST           | UART6 Receive Input                      |

| U6TX         | 18  | 27        | J3               | 0   | DIG          | UART6 Transmit Output                    |

#### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer

ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

#### 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. This is done by clearing all bits in the ANSx registers. Refer to **Section 11.2 "Configuring Analog Port Pins (ANSx)**" for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, it must set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time. When a Microchip debugger/emulator is used as a programmer, the user application must correctly configure the ANSx registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### 8.3 Interrupt Control and Status Registers

The PIC24FJ256GA412/GB412 family of devices implements a total of 50 registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON4

- IFS0 through IFS7

- IEC0 through IEC7

- IPC0 through ICP29

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls global interrupt generation, the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT). INTCON2 and INTCON4 also contain status flags for various hardware trap events.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Priority Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 8-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test register, INTTREG, which displays the status of the interrupt controller. When an interrupt request occurs, its associated vector number and the new Interrupt Priority Level are latched into INTTREG. This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors (such as when ISR remapping is used in bootloader applications) or to check if another interrupt is pending while in an ISR.

All Interrupt registers are described in Register 8-3 through Register 8-52 in the succeeding pages.

| Dit 14       I         Dit 13       I         Dit 12       I         Dit 12       I         Dit 11       I         Dit 10       I         Dit 10       I         Dit 9       I         Dit 8       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                       | PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ompare Interrup<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>errupt Enable b<br>oled<br>enabled                                     | '0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit                           |                  | R/W-0<br>SI2C2IE | KEYSTRIE<br>bit 8<br>R/W-0<br>CCT6IE<br>bit 0 |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------|------------------|-----------------------------------------------|--|--|--|--|--|--|

| R/W-0         CRYDNIE         Dit 7         Legend:         R = Readable b         m = Value at PC         Dit 15       C         Dit 14       F         Dit 13       C         Dit 12       C         Dit 12       C         Dit 11       C         Dit 12       C         Dit 13       C         Dit 14       F         Dit 13       C         Dit 14       F         Dit 13       C         Dit 14       F         Dit 15       C         Dit 16       C         Dit 17       C         Dit 10       C         Dit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INT4IE <sup>(1)</sup><br>Dit<br>DR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt | INT3IE <sup>(1)</sup><br>W = Writable to<br>'1' = Bit is set<br>CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dit<br>Dit<br>Dit<br>Dit<br>Died<br>Calendar Interpled<br>d Calendar Interpled<br>enabled<br>terrupt Enable<br>enabled<br>errupt Enable b<br>Died<br>errupt Enable b<br>Died<br>errupt Enable b | CCT7IE<br>U = Unimpler<br>'0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit | MI2C2IE          | SI2C2IE          | R/W-0<br>CCT6IE<br>bit 0                      |  |  |  |  |  |  |

| CRYDNIE           bit 7           Legend:           R = Readable b           n = Value at PC           bit 15           bit 15           bit 13           bit 12           bit 11           bit 12           bit 11           bit 12           bit 12           bit 13           bit 14           bit 12           bit 12           bit 10           bit 10           bit 9           cit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INT4IE <sup>(1)</sup><br>Dit<br>DR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt | INT3IE <sup>(1)</sup><br>W = Writable to<br>'1' = Bit is set<br>CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dit<br>Dit<br>Dit<br>Dit<br>Died<br>Calendar Interpled<br>d Calendar Interpled<br>enabled<br>terrupt Enable<br>enabled<br>errupt Enable b<br>Died<br>errupt Enable b<br>Died<br>errupt Enable b | CCT7IE<br>U = Unimpler<br>'0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit | MI2C2IE          | SI2C2IE          | CCT6IE<br>bit C                               |  |  |  |  |  |  |

| Dit 7         Legend:         R = Readable b         n = Value at PC         Dit 15         Dit 15         Dit 14         Dit 13         Dit 12         Dit 11         Dit 12         Dit 11         Dit 12         Dit 11         Dit 12         Dit 13         Dit 14         Dit 12         Dit 12         Dit 13         Dit 14         Dit 12         Dit 13         Dit 14         Dit 12         Dit 13         Dit 14         Dit 15         Dit 10         Dit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit<br>DR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                | W = Writable to<br>'1' = Bit is set<br>CP1 Capture/Co<br>request is enable<br>request is not e<br>Time Clock and<br>request is enable<br>request is not e<br>A Channel 5 Int<br>request is enable<br>request is not e<br>PI3 Receive Inter<br>request is enable<br>request is enable<br>request is enable<br>request is not e<br>PI2 Receive Inter<br>PI2 Recei | ompare Interrup<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>errupt Enable b<br>oled<br>enabled                                     | CCT7IE<br>U = Unimpler<br>'0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit | mented bit, read | 1 as '0'         | bit (                                         |  |  |  |  |  |  |

| Legend:         R = Readable b         in = Value at PC         bit 15         bit 15         bit 14         bit 13         bit 12         bit 11         bit 12         bit 11         bit 12         bit 12         bit 13         bit 14         bit 12         bit 12         bit 11         bit 12         bit 10         bit 10 <t< td=""><td>OR<br/>CCP1IE: MCC<br/>1 = Interrupt<br/>0 = Interrupt<br/>RTCIE: Real-<br/>1 = Interrupt<br/>0 = Interrupt<br/>DMA5IE: DM.<br/>1 = Interrupt<br/>0 = Interrupt<br/>SPI3RXIE: SF<br/>1 = Interrupt<br/>SPI2RXIE: SF<br/>1 = Interrupt<br/>1 = Interrupt</td><td>'1' = Bit is set<br/>CP1 Capture/Co<br/>request is enab<br/>request is not e<br/>Time Clock and<br/>request is enab<br/>request is not e<br/>A Channel 5 In<br/>request is enab<br/>request is not e<br/>Pl3 Receive Inte<br/>request is not e<br/>Pl2 Receive Inte</td><td>ompare Interrup<br/>enabled<br/>d Calendar Inte<br/>oled<br/>enabled<br/>terrupt Enable<br/>oled<br/>errupt Enable b<br/>oled<br/>errupt Enable b<br/>oled<br/>enabled</td><td>'0' = Bit is cle<br/>ot Enable bit<br/>errupt Enable t<br/>bit</td><td>eared</td><td></td><td></td></t<> | OR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                       | '1' = Bit is set<br>CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>Pl3 Receive Inte<br>request is not e<br>Pl2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ompare Interrup<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>errupt Enable b<br>oled<br>enabled                                     | '0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit                           | eared            |                  |                                               |  |  |  |  |  |  |

| R = Readable b         n = Value at PC         pit 15         pit 15         pit 14         pit 13         pit 12         pit 11         pit 12         pit 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                       | '1' = Bit is set<br>CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>Pl3 Receive Inte<br>request is not e<br>Pl2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ompare Interrup<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>errupt Enable b<br>oled<br>enabled                                     | '0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit                           | eared            |                  | IOWN                                          |  |  |  |  |  |  |

| R = Readable b         n = Value at PC         pit 15         pit 15         pit 14         pit 13         pit 12         pit 11         pit 12         pit 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OR<br>CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                       | '1' = Bit is set<br>CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>Pl3 Receive Inte<br>request is not e<br>Pl2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ompare Interrup<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>errupt Enable b<br>oled<br>enabled                                     | '0' = Bit is cle<br>ot Enable bit<br>errupt Enable t<br>bit                           | eared            |                  | iown                                          |  |  |  |  |  |  |

| Dit 15       0         Dit 14       0         Dit 13       0         Dit 12       0         Dit 11       0         Dit 10       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CCP1IE: MCC<br>1 = Interrupt<br>0 = Interrupt<br>RTCIE: Real-<br>1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>0 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt                                                         | CP1 Capture/Co<br>request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 Im<br>request is enab<br>request is enab<br>request is enab<br>request is enab<br>request is enab<br>request is enab<br>request is enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | oled<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>enabled                                                                           | ot Enable bit<br>errupt Enable t<br>bit                                               |                  | x = Bit is unkn  | iown                                          |  |  |  |  |  |  |

| Dit 14       I         Dit 13       I         Dit 12       I         Dit 12       I         Dit 11       I         Dit 10       I         Dit 10       I         Dit 9       I         Dit 8       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 = Interrupt<br>0 = Interrupt<br><b>RTCIE</b> : Real-<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IE</b> : DM.<br>1 = Interrupt<br>0 = Interrupt<br><b>SPI3RXIE</b> : SF<br>1 = Interrupt<br><b>SPI2RXIE</b> : SF<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt                                                                           | request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>PI3 Receive Inte<br>request is not e<br>PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oled<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>enabled                                                                           | errupt Enable t<br>bit                                                                | bit              |                  |                                               |  |  |  |  |  |  |

| Dit 14       I         Dit 13       I         Dit 12       I         Dit 12       I         Dit 11       I         Dit 10       I         Dit 10       I         Dit 9       I         Dit 8       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 = Interrupt<br>0 = Interrupt<br><b>RTCIE</b> : Real-<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IE</b> : DM.<br>1 = Interrupt<br>0 = Interrupt<br><b>SPI3RXIE</b> : SF<br>1 = Interrupt<br><b>SPI2RXIE</b> : SF<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt                                                                           | request is enab<br>request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>PI3 Receive Inte<br>request is not e<br>PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oled<br>enabled<br>d Calendar Inte<br>oled<br>enabled<br>terrupt Enable<br>oled<br>errupt Enable b<br>oled<br>enabled                                                                           | errupt Enable t<br>bit                                                                | pit              |                  |                                               |  |  |  |  |  |  |

| bit 14       I         bit 13       I         bit 12       I         bit 12       I         bit 11       I         bit 10       I         bit 10       I         bit 9       I         bit 8       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 = Interrupt<br><b>RTCIE:</b> Real-<br>1 = Interrupt<br>0 = Interrupt<br><b>DMA5IE:</b> DM.<br>1 = Interrupt<br><b>SPI3RXIE:</b> SF<br>1 = Interrupt<br>0 = Interrupt<br><b>SPI2RXIE:</b> SF<br>1 = Interrupt<br>1 = Interrupt<br>1 = Interrupt                                                                                                | request is not e<br>Time Clock and<br>request is enab<br>request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>PI3 Receive Inte<br>request is enab<br>request is not e<br>PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | enabled<br>d Calendar Inte<br>bled<br>enabled<br>terrupt Enable<br>bled<br>errupt Enable b<br>bled<br>errupt Enable b<br>bled<br>enabled                                                        | bit                                                                                   | bit              |                  |                                               |  |  |  |  |  |  |

| Dit 13       1         Dit 12       2         Dit 12       2         Dit 11       2         Dit 10       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 = Interrupt<br>0 = Interrupt<br>DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>0 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt<br>1 = Interrupt                                                                                                                                                             | request is enab<br>request is not e<br>A Channel 5 Ini<br>request is enab<br>request is not e<br>PI3 Receive Inte<br>request is enab<br>request is not e<br>PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oled<br>enabled<br>terrupt Enable<br>oled<br>enabled<br>errupt Enable b<br>oled<br>enabled                                                                                                      | bit                                                                                   | bit              |                  |                                               |  |  |  |  |  |  |

| bit 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 = Interrupt<br><b>DMA5IE:</b> DM.<br>1 = Interrupt<br>0 = Interrupt<br><b>SPI3RXIE:</b> SF<br>1 = Interrupt<br>0 = Interrupt<br><b>SPI2RXIE:</b> SF<br>1 = Interrupt                                                                                                                                                                          | request is not e<br>A Channel 5 In<br>request is enab<br>request is not e<br>Pl3 Receive Inte<br>request is enab<br>request is not e<br>Pl2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | enabled<br>terrupt Enable<br>bled<br>enabled<br>errupt Enable b<br>bled<br>enabled                                                                                                              |                                                                                       |                  |                  |                                               |  |  |  |  |  |  |

| Dit 13       1         Dit 12       2         Dit 12       2         Dit 11       2         Dit 11       2         Dit 10       2         Dit 10       2         Dit 9       2         Dit 8       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DMA5IE: DM.<br>1 = Interrupt<br>0 = Interrupt<br>SPI3RXIE: SF<br>1 = Interrupt<br>0 = Interrupt<br>SPI2RXIE: SF<br>1 = Interrupt                                                                                                                                                                                                                | A Channel 5 In<br>request is enab<br>request is not e<br>PI3 Receive Inte<br>request is enab<br>request is not e<br>PI2 Receive Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | terrupt Enable<br>bled<br>enabled<br>errupt Enable b<br>bled<br>enabled                                                                                                                         |                                                                                       |                  |                  |                                               |  |  |  |  |  |  |