Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Decans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 101                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb412t-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

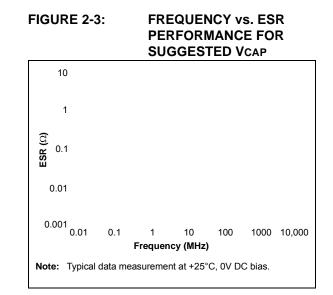

# 2.4 Voltage Regulator Pin (VCAP)

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the output voltage of the on-chip voltage regulator. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 36.0** "**Electrical Characteristics**" for additional information.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

Refer to **Section 33.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

# TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

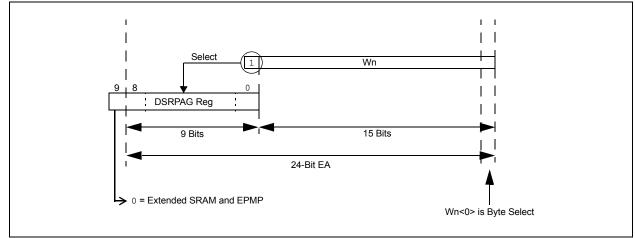

# 4.3.5.1 Data Read from EDS

In order to read the data from the EDS space, first, an Address Pointer is set up by loading the required EDS page number into the DSRPAG register and assigning the offset address to one of the W registers. Once the above assignment is done, the EDS window is enabled by setting bit 15 of the Working register assigned with the offset address; then, the contents of the pointed EDS location can be read.

Figure 4-7 illustrates how the EDS space address is generated for read operations.

When the Most Significant bit (MSb) of EA is '1' and DSRPAG<9> = 0, the lower 9 bits of DSRPAG are concatenated to the lower 15 bits of the EA to form a 24-bit EDS space address for read operations. Example 4-1 shows how to read a byte, word and double-word from EDS.

Note: All read operations from EDS space have an overhead of one instruction cycle. Therefore, a minimum of two instruction cycles is required to complete an EDS read. EDS reads under the REPEAT instruction; the first two accesses take three cycles and the subsequent accesses take one cycle.

# FIGURE 4-7: EDS ADDRESS GENERATION FOR READ OPERATIONS

## EXAMPLE 4-1: EDS READ CODE IN ASSEMBLY

```

; Set the EDS page from where the data to be read

#0x0002, w0

mov

w0, DSRPAG

;page 2 is selected for read

mov

mov

#0x0800, w1 ;select the location (0x800) to be read

bset

w1, #15

;set the MSB of the base address, enable EDS mode

;Read a byte from the selected location

mov.b

[w1++], w2 ;read Low byte

mov.b

[w1++], w3

;read High byte

;Read a word from the selected location

[w1], w2

;

mov

;Read Double - word from the selected location

mov.d

[w1], w2

;two word read, stored in w2 and w3

```

## REGISTER 6-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/S-0, HC <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R-0, HSC <sup>(1)</sup>                   | R/W-0              | R/C-0, HSC <sup>(2)</sup>    | R-0                   | U-0                   | U-0                   |

|--------------------------|----------------------|-------------------------------------------|--------------------|------------------------------|-----------------------|-----------------------|-----------------------|

| WR                       | WREN                 | WRERR                                     | NVMPIDL            | SFTSWP                       | P2ACTIV               | —                     | —                     |

| bit 15                   |                      | •                                         |                    |                              |                       |                       | bit 8                 |

|                          |                      |                                           |                    |                              |                       | R/W-0 <sup>(1)</sup>  |                       |

| U-0                      | U-0                  | U-0                                       |                    |                              |                       |                       | R/W-0 <sup>(1)</sup>  |

|                          |                      |                                           |                    | NVMOP3 <sup>(3)</sup>        | NVMOP2 <sup>(3)</sup> | NVMOP1 <sup>(3)</sup> | NVMOP0 <sup>(3)</sup> |

| bit 7                    |                      |                                           |                    |                              |                       |                       | bit (                 |

|                          |                      |                                           |                    |                              |                       |                       |                       |

| Legend:                  |                      | S = Settable bit                          |                    | U = Unimpleme                |                       |                       |                       |

| R = Readab               |                      | W = Writable b                            | t                  | HSC = Hardwar                |                       | arable bit            |                       |

| -n = Value at            |                      | '1' = Bit is set                          |                    | '0' = Bit is clear           | red                   | x = Bit is unkn       | own                   |

| C = Clearab              | le bit               | HC = Hardware                             | Clearable bit      |                              |                       |                       |                       |

|                          |                      | - · · · · · · · (1)                       |                    |                              |                       |                       |                       |

| bit 15                   | WR: Write (          |                                           |                    |                              | n the energy          |                       | and the hit i         |

|                          |                      | s a Flash memo<br>I by hardware on        |                    |                              | n; the operation      | on is sell-timed      | and the bit i         |

|                          |                      | m or erase opera                          |                    |                              |                       |                       |                       |

| oit 14                   | WREN: Wri            | te Enable bit <sup>(1)</sup>              |                    |                              |                       |                       |                       |

|                          |                      | s Flash program/                          |                    |                              |                       |                       |                       |

|                          |                      | Flash program/e                           | •                  | าร                           |                       |                       |                       |

| bit 13                   |                      | /rite Sequence E                          |                    |                              |                       |                       |                       |

|                          |                      | proper program                            |                    |                              | , or terminati        | on has occurr         | ed (bit is se         |

|                          |                      | atically on any se<br>ogram or erase o    |                    |                              |                       |                       |                       |

| bit 12                   | -                    | NVM Power-Dov                             |                    | -                            |                       |                       |                       |

|                          |                      | es power from p                           |                    |                              | enters Idle mod       | е                     |                       |

|                          |                      | program memory                            |                    |                              |                       |                       |                       |

| bit 11                   | SFTSWP: S            | Soft Swap Status                          | bit <sup>(2)</sup> |                              |                       |                       |                       |

|                          |                      | tition Flash Mode                         |                    |                              |                       |                       |                       |

|                          |                      | ns have been su<br>g successful par       |                    |                              |                       | uction                |                       |

|                          |                      | artition Flash Mod                        | -                  | -                            | Instruction           |                       |                       |

|                          |                      | nted, read as '0'.                        |                    | <u>.07 – 11).</u>            |                       |                       |                       |

| bit 10                   | •                    | Dual Active Partit                        | on Status bit      |                              |                       |                       |                       |

|                          |                      | tition Flash Mode                         |                    | :0> = 10 or 0x):             |                       |                       |                       |

|                          |                      | n 2 Flash is the A                        |                    |                              |                       |                       |                       |

|                          |                      | n 1 Flash is the A                        |                    |                              |                       |                       |                       |

|                          |                      | artition Flash Moon<br>nted, read as '0'. | ie (BIMOD<1        | : <b>U&gt; =</b> <u>11):</u> |                       |                       |                       |

| bit 9-4                  | •                    | ented: Read as '                          | ז'                 |                              |                       |                       |                       |

|                          | -                    |                                           |                    | _                            |                       |                       |                       |

|                          |                      | only be reset or                          |                    |                              |                       |                       |                       |

|                          |                      | oftware, as well a                        |                    |                              |                       |                       |                       |

| <b>3</b> : A             | II other comb        | inations of NVM                           | JP<3:0> are ι      | inimplemented in             | n this device fa      | mily.                 |                       |

4: Available only in Dual Partition modes (BTMOD<1:0> = 10 or 0x).

# REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(1)</sup> | —   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit     |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-2 for bit description.

### REGISTER 8-6: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

- bit 3 **T1IF:** Timer1 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 2 OC1IF: Output Compare Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| U-0         | U-0                                                                                                                                                | U-0                                  | U-0              | U-0               | U-0              | U-0             | U-0    |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|

| _           |                                                                                                                                                    |                                      | —                | —                 | _                | —               | —      |  |  |

| it 15       |                                                                                                                                                    |                                      |                  |                   |                  |                 | bit 8  |  |  |

|             |                                                                                                                                                    |                                      |                  |                   |                  |                 | R/W-0  |  |  |

| U-0         | U-0         R/W-0         R/W-0         R/W-0         R/W-0           —         JTAGIF         U6ERIF         U6TXIF         U6RXIF         U5ERIF |                                      |                  |                   |                  |                 |        |  |  |

| —           | —                                                                                                                                                  | JTAGIF                               | U6ERIF           | U6TXIF            | U6RXIF           | U5ERIF          | U5TXIF |  |  |

| oit 7       |                                                                                                                                                    |                                      |                  |                   |                  |                 | bit (  |  |  |

| <u> </u>    |                                                                                                                                                    |                                      |                  |                   |                  |                 |        |  |  |

| Legend:     | -1                                                                                                                                                 |                                      | 1. 14            |                   |                  |                 |        |  |  |

| R = Readat  |                                                                                                                                                    | W = Writable                         |                  | •                 | nented bit, read |                 |        |  |  |

| n = Value a | at POR                                                                                                                                             | '1' = Bit is set                     |                  | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |

| bit 15-6    | Unimpleme                                                                                                                                          | nted: Read as '                      | ٥'               |                   |                  |                 |        |  |  |

| it 5        | •                                                                                                                                                  | AG Controller In                     |                  | atus hit          |                  |                 |        |  |  |

| 511 5       |                                                                                                                                                    | t request has or                     |                  |                   |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has no                     |                  |                   |                  |                 |        |  |  |

| oit 4       | U6ERIF: UA                                                                                                                                         | RT6 Error Inter                      | rupt Flag Status | s bit             |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has o                      |                  |                   |                  |                 |        |  |  |

|             | •                                                                                                                                                  | t request has no                     |                  |                   |                  |                 |        |  |  |

| oit 3       |                                                                                                                                                    | RT6 Transmitte                       |                  | Status bit        |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has or<br>t request has no |                  |                   |                  |                 |        |  |  |

| oit 2       | •                                                                                                                                                  | RT6 Receiver li                      |                  | tatus bit         |                  |                 |        |  |  |

| 511 2       |                                                                                                                                                    | t request has or                     |                  |                   |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has no                     |                  |                   |                  |                 |        |  |  |

| oit 1       | U5ERIF: UA                                                                                                                                         | RT5 Error Inter                      | rupt Flag Status | s bit             |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has o                      |                  |                   |                  |                 |        |  |  |

|             | 0 = Interrup                                                                                                                                       | t request has no                     | ot occurred      |                   |                  |                 |        |  |  |

| oit O       | U5TXIF: UA                                                                                                                                         | RT5 Transmitte                       | r Interrupt Flag | Status bit        |                  |                 |        |  |  |

|             |                                                                                                                                                    | t request has o                      |                  |                   |                  |                 |        |  |  |

|             | 0 = Interrup                                                                                                                                       | t request has no                     | ot occurred      |                   |                  |                 |        |  |  |

## REGISTER 8-13: IFS7: INTERRUPT FLAG STATUS REGISTER 7

## REGISTER 8-15: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <ul> <li>CNIE: Input Change Notification Interrupt Enable bit</li> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                                                                                            |

|       | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>                                                                  |

| bit 1 | MI2C1IE: Master I2C1 Event Interrupt Enable bit                                                                                                                  |

|       | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>                                                                  |

| bit 0 | SI2C1IE: Slave I2C1 Event Interrupt Enable bit                                                                                                                   |

|       | <ol> <li>Interrupt request is enabled</li> </ol>                                                                                                                 |

|       | 0 = Interrupt request is not enabled                                                                                                                             |

Note 1: If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. See Section 11.5 "Peripheral Pin Select (PPS)" for more information.

# 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. OSCCON is protected by a write lock to prevent inadvertent clock switches. See **Section 9.4** "**Clock Switching Operation**" for more information.

The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 1.5\%$ . It also controls the FRC self-tuning features, described in **Section 9.5** "**FRC Active Clock Tuning**".

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| —      | COSC2 | COSC1 | COSC0 | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | —   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | end: CO = Clearable Only bit SO = Settable Only bit |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 15 Unimplemented: Read as '0'

- bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)<sup>(4)</sup>

- 000 = Fast RC Oscillator (FRC)

#### bit 11 Unimplemented: Read as '0'

### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Reserved

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)<sup>(4)</sup>

- 000 = Fast RC Oscillator (FRC)

- Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- 4: The default divisor of the postscaler is 2, which will generate a 4 MHz clock to the PLL module.

# 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMODx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

# 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSMx Configuration bits in the FOSC Configuration Word must be programmed. (Refer to **Section 33.1** "**Configuration Bits**" for further details.) If the bits are unmodified, the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC<2:0> bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or SOSC (if SOSCEN remains set).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

#### TABLE 10-2: EXITING POWER-SAVING MODES

|                   |                   | Code |     |     |      |       |      |                        |                  |

|-------------------|-------------------|------|-----|-----|------|-------|------|------------------------|------------------|

| Mode              | Interrupts Resets |      |     |     |      | RTCC  | WDT  | VDD                    | Execution        |

|                   | All               | INT0 | All | POR | MCLR | Alarm | WDI  | Restore <sup>(2)</sup> | Resumes          |

| Idle              | Y                 | Y    | Y   | Y   | Y    | Y     | Y    | N/A                    | Next instruction |

| Sleep (all modes) | Y                 | Y    | Y   | Y   | Y    | Y     | Y    | N/A                    |                  |

| Deep Sleep        | Ν                 | Y    | Ν   | Y   | Y    | Y     | Y(1) | N/A                    | Reset vector     |

| VBAT              | Ν                 | Ν    | Ν   | Ν   | Ν    | Ν     | Ν    | Y                      | Reset vector     |

Note 1: Deep Sleep WDT.

2: A POR or POR-like Reset results whenever VDD is removed and restored in any mode.

#### 10.1.1 INSTRUCTION-BASED POWER-SAVING MODES

Three of the power-saving modes are entered through the execution of the PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals, except RTCC and DSWDT. It also freezes I/O states and removes power to Flash memory, and may remove power to SRAM.

The assembly syntax of the PWRSAV instruction is shown in Example 10-1. Sleep and Idle modes are entered directly with a single assembler command. Deep Sleep requires an additional sequence to unlock and enable the entry into Deep Sleep, which is described in **Section 10.4.1 "Entering Deep Sleep Mode**".

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

The features enabled with the low-voltage/retention regulator result in some changes to the way that Sleep and Deep Sleep modes behave. See **Section 10.3 "Sleep Mode"** and **Section 10.4 "Deep Sleep Mode"** for additional information.

# 10.1.1.1 Interrupts Coincident with Power Save Instructions

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

For Deep Sleep mode, interrupts that coincide with the execution of the PWRSAV instruction may be lost. The microcontroller resets on leaving Deep Sleep and the interrupt will be lost.

Interrupts that occur during the Deep Sleep unlock sequence will interrupt the mandatory five-instruction cycle sequence timing and cause a failure to enter Deep Sleep. For this reason, it is recommended to disable all interrupts during the Deep Sleep unlock sequence.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

```

// Syntax to enter Sleep mode:

#SLEEP_MODE

PWRSAV

; Put the device into SLEEP mode

11

//Synatx to enter Idle mode:

PWRSAV

#IDLE MODE

; Put the device into IDLE mode

11

// Syntax to enter Deep Sleep mode:

// First use the unlock sequence to set the DSEN bit (see Example 10-2)

BSET DSCON, #DSEN ; Enable Deep Sleep

DSCON, #DSEN

BSET

; Enable Deep Sleep(repeat the command)

PWRSAV

#SLEEP_MODE

; Put the device into Deep SLEEP mode

```

NOTES:

## 16.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS and OCxR registers. The OCxRS and OCxR registers can be written to at any time, but the duty cycle value is not latched until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation.

Some important boundary parameters of the PWM duty cycle include:

- If OCxR, OCxRS and PRy are all loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than PRy, the pin will remain high (100% duty cycle).

See Example 16-1 for PWM mode timing details. Table 16-1 and Table 16-2 show example PWM frequencies and resolutions for a device operating at 4 MIPS and 10 MIPS, respectively.

# EQUATION 16-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

$$Maximum PWM Resolution (bits) = \frac{\left(\frac{FCY}{FPWM \bullet (Timer Prescale Value)}\right)}{\log_{10}^{(2)}} bits$$

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# EXAMPLE 16-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

TCY = 2 \* TOSC = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz = 19.2 ms

PWM Period =  $(PR2 + 1) \bullet TCY \bullet (Timer2 Prescale Value)$

$19.2 \ \mu s = (PR2 + 1) \cdot 62.5 \ ns \cdot 1$

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution =  $log_{10}(FCY/FPWM)/log_{10}2)$  bits

$= (\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2) \text{ bits}$

= 8.3 bits

**Note 1:** Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |  |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|--|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |  |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |  |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |  |

## TABLE 16-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

## TABLE 16-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

# REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>S: I2Cx Start bit</li> <li>Updated when Start, Reset or Stop is detected; cleared when the I<sup>2</sup>C module is disabled, I2CEN = 0.</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                           |

|       | <ul> <li>1 = Read: Indicates the data transfer is output from the slave</li> <li>0 = Write: Indicates the data transfer is input to the slave</li> </ul>                                                                                                                                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                          |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> </ul>                                                                                                                                                                          |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                         |

|       | <ul> <li>1 = Transmit is in progress, I2CxTRN is full (8-bits of data)</li> <li>0 = Transmit is complete, I2CxTRN is empty</li> </ul>                                                                                                                                                        |

# REGISTER 18-4: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| _      | —   | —   | —   | —   | —   | MSK   | <9:8> |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | MSK   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 15-10 Unimplemented: Read as '0'

bit 9-0

MSK<9:0>: I2Cx Mask for Address Bit x Select bits

1 = Enables masking for bit x of the incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

| U-0          | U-0                 | U-0                                  | U-0                   | U-0                         | U-0                        | U-0             | U-0   |  |  |  |

|--------------|---------------------|--------------------------------------|-----------------------|-----------------------------|----------------------------|-----------------|-------|--|--|--|

| _            | —                   | _                                    | _                     |                             |                            |                 |       |  |  |  |

| bit 15       |                     |                                      |                       |                             |                            |                 | bit 8 |  |  |  |

|              |                     |                                      |                       |                             |                            |                 |       |  |  |  |

| U-0          | U-0                 | R/W-0                                | R/W-0                 | R/W-0                       | R/W-0                      | R/W-0           | R/W-0 |  |  |  |

| —            | —                   | TXRPT1 <sup>(2)</sup>                | TXRPT0 <sup>(2)</sup> | CONV                        | T0PD <sup>(2)</sup>        | PTRCL           | SCEN  |  |  |  |

| bit 7        |                     |                                      |                       |                             |                            |                 | bit 0 |  |  |  |

|              |                     |                                      |                       |                             |                            |                 |       |  |  |  |

| Legend:      | -1- h:t             |                                      | L :4                  |                             | a suct as the state of the |                 |       |  |  |  |

| R = Readat   |                     | W = Writable                         |                       | -                           | nented bit, read           |                 |       |  |  |  |

| -n = Value a | at POR              | '1' = Bit is set                     |                       | '0' = Bit is clea           | ared                       | x = Bit is unkn | own   |  |  |  |

| bit 15-6     | Unimplomen          | ted. Dood oo '                       | ,                     |                             |                            |                 |       |  |  |  |

|              | -                   | ted: Read as '                       |                       | ·+- (2)                     |                            |                 |       |  |  |  |

| oit 5-4      |                     | : Transmit Rep                       |                       | its(=)                      |                            |                 |       |  |  |  |

|              |                     | mits the error b                     |                       |                             |                            |                 |       |  |  |  |

|              |                     | mits the error b                     |                       |                             |                            |                 |       |  |  |  |

|              |                     | mits the error b<br>mits the error b |                       |                             |                            |                 |       |  |  |  |

| oit 3        |                     | Convention Se                        | •                     |                             |                            |                 |       |  |  |  |

|              | -                   | gic convention                       |                       |                             |                            |                 |       |  |  |  |

|              | 0 = Direct log      | •                                    |                       |                             |                            |                 |       |  |  |  |

| bit 2        | TOPD: Pull-D        | own Duration fo                      | or T = 0 Error H      | landling bit <sup>(2)</sup> |                            |                 |       |  |  |  |

|              | 1 = 2 ETUs          |                                      |                       | -                           |                            |                 |       |  |  |  |

|              | 0 = 1 ETU           |                                      |                       |                             |                            |                 |       |  |  |  |

| bit 1        | PTRCL: Sma          | rt Card Protoco                      | I Selection bit       |                             |                            |                 |       |  |  |  |

|              | 1 = T = 1 prof      |                                      |                       |                             |                            |                 |       |  |  |  |

|              | 0 = T = 0 protocol  |                                      |                       |                             |                            |                 |       |  |  |  |

| oit 0        |                     | Card Mode Er                         |                       |                             |                            |                 |       |  |  |  |

|              |                     | rd mode is ena                       |                       | N (UxMODE<1                 | 5>) = 1                    |                 |       |  |  |  |

|              | 0 = Smart Ca        | rd mode is disa                      | bled                  |                             |                            |                 |       |  |  |  |

| Note 1: 7    | This register is or | nly available for                    | UART1 and U           | ART2.                       |                            |                 |       |  |  |  |

| 2: 1         | These bits are ap   | plicable to T =                      | 0 only, see the       | PTRCL bit (U)               | (SCCON<1>).                |                 |       |  |  |  |

|              |                     |                                      |                       |                             |                            |                 |       |  |  |  |

# REGISTER 19-5: UxSCCON: UARTx SMART CARD CONTROL REGISTER<sup>(1)</sup>

### REGISTER 22-2: LCDREG: LCD CHARGE PUMP CONTROL REGISTER

| RW-0          | U-0   | U-0              | U-0 | U-0                                     | U-0 | U-0    | U-0    |  |

|---------------|-------|------------------|-----|-----------------------------------------|-----|--------|--------|--|

| CPEN          | —     | —                | —   | —                                       | —   | —      | —      |  |

| bit 15        |       | •                |     |                                         |     |        | bit 8  |  |

|               |       |                  |     |                                         |     |        |        |  |

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0 | RW-0   | RW-0   |  |

| —             | _     | —                | _   | —                                       | —   | CKSEL1 | CKSEL0 |  |

| bit 7         |       | •                |     |                                         |     |        | bit 0  |  |

|               |       |                  |     |                                         |     |        |        |  |

| Legend:       |       |                  |     |                                         |     |        |        |  |

| R = Readable  | e bit | W = Writable I   | oit | t U = Unimplemented bit, read as '0'    |     |        |        |  |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |        |        |  |

bit 15 **CPEN:** 3.6V Charge Pump Enable bit

1 = The regulator generates the highest (3.6V) voltage

0 = Highest voltage in the system is supplied externally (AVDD)

#### bit 14-2 Unimplemented: Read as '0'

### bit 1-0 CLKSEL<1:0>: Regulator Clock Select Control bits

11 **= SOSC**

10 = 8 MHz FRC

01 = 31 kHz LPRC

00 = Disables regulator and floats regulator voltage output

| R/W-0         | R/W-0                                                                                              | R/W-0                                 | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0              |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------|---------------------------------------|--------|------------------------------------|--------|--------|--------------------|--|--|--|

| CH0NB2        | CH0NB1                                                                                             | CH0NB0                                | CH0SB4 | CH0SB3 CH0SB2                      |        | CH0SB1 | CH0SB0             |  |  |  |

| bit 15        | bit 15                                                                                             |                                       |        |                                    |        | ·      | bit 8              |  |  |  |

|               |                                                                                                    |                                       |        |                                    |        |        |                    |  |  |  |

| R/W-0         | R/W-0                                                                                              | R/W-0                                 | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0              |  |  |  |

| CH0NA2        | CH0NA1                                                                                             | CH0NA0                                | CH0SA4 | CH0SA3                             | CH0SA2 | CH0SA1 | CH0SA0             |  |  |  |

| bit 7         |                                                                                                    |                                       |        |                                    |        |        | bit 0              |  |  |  |

|               |                                                                                                    |                                       |        |                                    |        |        |                    |  |  |  |

| Legend:       |                                                                                                    |                                       |        |                                    |        |        |                    |  |  |  |

| R = Readable  | e bit                                                                                              | W = Writable                          | bit    | U = Unimplemented bit, read as '0' |        |        |                    |  |  |  |

| -n = Value at | POR                                                                                                | '1' = Bit is set                      |        | '0' = Bit is cleared               |        |        | x = Bit is unknown |  |  |  |

| bit 15-13     | 1xx = Unimpl<br>011 = Unimpl<br>010 = AN1<br>001 = Unimpl<br>000 = VREF-//                         | emented<br>emented<br>emented<br>AVss | -      | ive Input Select                   |        |        |                    |  |  |  |

| bit 12-8      | CH0SB<4:0>: Sample B Channel 0 Positive Input Select bits<br>See Table 27-2 for available options. |                                       |        |                                    |        |        |                    |  |  |  |

| bit 7-5       |                                                                                                    | : Sample A Ch<br>ons as for CHC       | •      | ive Input Select                   | bits   |        |                    |  |  |  |

| bit 4-0       | CH0SA<4:0>: Sample A Channel 0 Positive Input Select bits                                          |                                       |        |                                    |        |        |                    |  |  |  |

|               |                                                                                                    |                                       |        |                                    |        |        |                    |  |  |  |

### REGISTER 27-6: AD1CHS: A/D SAMPLE SELECT REGISTER

Same definitions as for CHOSB<4:0>.

| TABI F 27-2. | POSITIVE CHANNEL SELECT OPTIONS (CHOSA<4:0> OR CHOSB<4:0>) |

|--------------|------------------------------------------------------------|

|              |                                                            |

| CH0SA<4:0> or<br>CH0SB<4:0> | Analog Channel                         | CH0SA<4:0> or<br>CH0SB<4:0> | Analog Channel |  |

|-----------------------------|----------------------------------------|-----------------------------|----------------|--|

| 11111                       | VBAT/2 <sup>(1)</sup>                  | 01111                       | AN15           |  |

| 11110                       | AVDD <sup>(1)</sup>                    | 01110                       | AN14           |  |

| 11101                       | AVss <sup>(1)</sup>                    | 01101                       | AN13           |  |

| 11100                       | VBG <sup>(1)</sup>                     | 01100                       | AN12           |  |

| 11011                       | Reserved                               | 01011                       | AN11           |  |

| 11010                       | Reserved                               | 01010                       | AN10           |  |

| 11001                       | CTMU                                   | 01001                       | AN9            |  |

| 11000                       | CTMU Temperature Sensor <sup>(2)</sup> | 01000                       | AN8            |  |

| 10111                       | AN23 <sup>(3)</sup>                    | 00111                       | AN7            |  |

| 10110                       | AN22 <sup>(3)</sup>                    | 00110                       | AN6            |  |

| 10101                       | AN21 <sup>(3)</sup>                    | 00101                       | AN5            |  |

| 10100                       | AN20 <sup>(3)</sup>                    | 00100                       | AN4            |  |

| 10011                       | AN19 <sup>(3)</sup>                    | 00011                       | AN3            |  |

| 10010                       | AN18 <sup>(3)</sup>                    | 00010                       | AN2            |  |

| 10001                       | AN17 <sup>(3)</sup>                    | 00001                       | AN1            |  |

| 10000                       | AN16 <sup>(3)</sup>                    | 00000                       | AN0            |  |

**Note 1:** These input channels do not have corresponding memory-mapped result buffers.

2: Temperature sensor does not require AD1CTMENL<13> to be set.

**3:** These channels are not implemented in 64-pin devices.

# 34.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 34.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

## TABLE 36-11: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |        |                                      |     |     |     |       |                                                                     |  |

|---------------------------------------------------------------------------|--------|--------------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------|--|

| Param<br>No.                                                              | Symbol | Characteristics                      | Min | Тур | Max | Units | Comments                                                            |  |

| DVR10                                                                     | Vbg    | Internal Band Gap Reference          | _   | 1.2 | —   | V     |                                                                     |  |

| DVR11                                                                     | Tbg    | Band Gap Reference Start-up<br>Time  | _   | 1   | _   | ms    |                                                                     |  |

| DVR20                                                                     | Vrgout | Regulator Output Voltage             |     | 1.8 | —   | V     | VDD > 2.0V                                                          |  |

| DVR21                                                                     | CEFC   | External Filter Capacitor Value      | 4.7 | 10  | -   | μF    | Series Resistance < $3\Omega$<br>recommended; < $5\Omega$ required. |  |

| DVR                                                                       | TVREG  | Start-up Time                        | _   | 10  | —   | μS    | PMSLP = 1 with any POR or BOR                                       |  |

| DVR30                                                                     | Vlvr   | Low-Voltage Regulator Output Voltage | —   | 1.2 | _   | V     | RETEN = 1, LPCFG = 0                                                |  |

# TABLE 36-12: VBAT OPERATING VOLTAGE SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic                                              | Min     | Тур | Max | Units | Comments                                                            |

|--------------|--------|-------------------------------------------------------------|---------|-----|-----|-------|---------------------------------------------------------------------|

| DVB01        | Vbt    | Operating Voltage                                           | 1.6     | _   | 3.6 | V     | Battery connected to the VBAT pin, VBTBOR = 0                       |

| DVB02        |        |                                                             | VBATBOR | _   | 3.6 | V     | Battery connected to the VBAT pin, VBTBOR = 1                       |

| DVB10        | VBTADC | VBAT A/D Monitoring Voltage<br>Specification <sup>(1)</sup> | 1.6     | _   | 3.6 | V     | A/D is monitoring the VBAT<br>pin using the internal A/D<br>channel |

**Note 1:** Measuring the A/D value using the A/D is represented by the equation: Measured Voltage = ((VBAT/2)/VDD) \* 4096) for 12-bit A/D.

## TABLE 36-13: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |       |                                                           | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |                                    |                     |  |  |

|--------------------|-------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------------------------------|---------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                                            | Min                                                                                                                                             | Typ <sup>(1)</sup> | Max | Units | Comments                           | Conditions          |  |  |

| DCT10              | IOUT1 | CTMU Current<br>Source, Base Range                        | —                                                                                                                                               | 550                |     | nA    | CTMUCON1L<1:0> = 00                |                     |  |  |

| DCT11              | IOUT2 | CTMU Current<br>Source, 10x Range                         | —                                                                                                                                               | 5.5                | —   | μA    | CTMUCON1L<1:0> = 01                | 2.5V < VDD < VDDMAX |  |  |

| DCT12              | IOUT3 | CTMU Current<br>Source, 100x Range                        | —                                                                                                                                               | 55                 | —   | μA    | CTMUCON1L<1:0> = 10                | 2.5V < VDD < VDDMAX |  |  |

| DCT13              | Iout4 | CTMU Current<br>Source, 1000x Range                       | —                                                                                                                                               | 550                | —   | μA    | CTMUCON1L<1:0> = 11 <sup>(2)</sup> |                     |  |  |

| DCT21              | VΔ    | Temperature Diode<br>Voltage Change per<br>Degree Celsius |                                                                                                                                                 | -3                 | _   | mV/°C |                                    |                     |  |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON1L<7:2> = 000000).

**2:** Do not use this current range with temperature sensing diode.

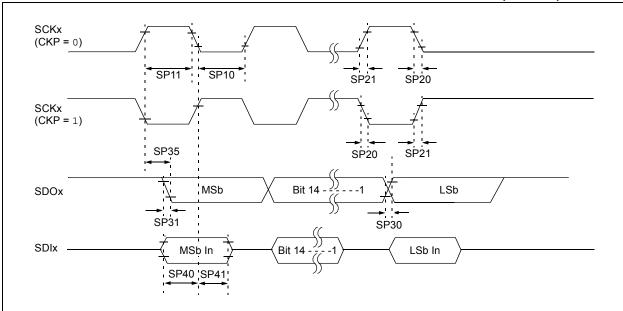

#### FIGURE 36-13: SPIX MODULE MASTER MODE TIMING CHARACTERISTICS (CKE = 0)

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \end{array}$ |                    |     |       |            |  |  |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|--|

| Param<br>No.       | Symbol                | Characteristic                               | Min                                                                                                                                                                                                                 | Typ <sup>(1)</sup> | Max | Units | Conditions |  |  |

| SP10               | TscL                  | SCKx Output Low Time <sup>(2)</sup>          | Tcy/2                                                                                                                                                                                                               | —                  | _   | ns    |            |  |  |

| SP11               | TscH                  | SCKx Output High Time <sup>(2)</sup>         | Tcy/2                                                                                                                                                                                                               | —                  | _   | ns    |            |  |  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(3)</sup>         | _                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |  |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(3)</sup>         | _                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>    | _                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>    | _                                                                                                                                                                                                                   | 10                 | 25  | ns    |            |  |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After<br>SCKx Edge    | —                                                                                                                                                                                                                   | —                  | 30  | ns    |            |  |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 20                                                                                                                                                                                                                  | —                  | _   | ns    |            |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge | 20                                                                                                                                                                                                                  | —                  |     | ns    |            |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** The minimum clock period for SCKx is 100 ns; therefore, the clock generated in Master mode must not violate this specification.

3: Assumes 50 pF load on all SPIx pins.

NOTES: