Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga406-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 Voltage Regulator Pin (VCAP)

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the output voltage of the on-chip voltage regulator. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specification can be used.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 36.0** "**Electrical Characteristics**" for additional information.

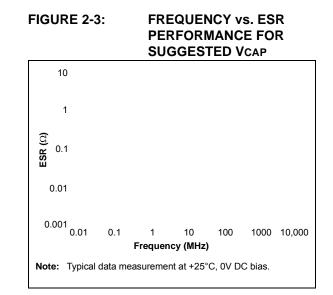

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

Refer to **Section 33.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

## TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

## 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (i.e.,  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

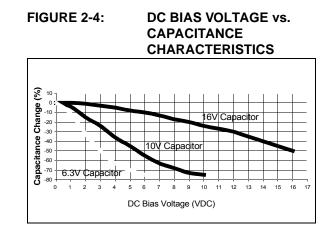

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V or 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

The  $\overline{\text{MCLR}}$  connection from the ICSP header should connect directly to the  $\overline{\text{MCLR}}$  pin on the device. A capacitor to ground (C1 in Figure 2-2) is optional, but if used, may interfere with ICSP operation if the value exceeds 0.01  $\mu$ F. In most cases, this capacitor is not required.

For more information on available Microchip development tools connection requirements, refer to **Section 34.0 "Development Support"**.

| Register     | Address | All Resets                              | Register         | Address | All Resets                              | Register | Address | All Resets         |

|--------------|---------|-----------------------------------------|------------------|---------|-----------------------------------------|----------|---------|--------------------|

| I/O (Continu | ed)     |                                         | AD1CON1          | 746     | 000000000000000000000000000000000000000 | RPINR13  | 7AA     | 0011111100111111   |

| PORTJ        | 700     | 000000000000000000000000000000000000000 | AD1CON2          | 748     | 000000000000000000000000000000000000000 | RPINR14  | 7AC     | 0011111100111111   |

| LATJ         | 702     | 000000000000000000000000000000000000000 | AD1CON3          | 74A     | 000000000000000000000000000000000000000 | RPINR15  | 7AE     | 0011111100111111   |

| ODCJ         | 704     | 000000000000000000000000000000000000000 | AD1CHS           | 74C     | 000000000000000000000000000000000000000 | RPINR16  | 7B0     | 0011111100111111   |

| IOCPJ        | 708     | 000000000000000000000000000000000000000 | AD1CSSL          | 74E     | 000000000000000000000000000000000000000 | RPINR17  | 7B2     | 0011111100111111   |

| IOCNJ        | 70A     | 000000000000000000000000000000000000000 | AD1CSSH          | 750     | 000000000000000000000000000000000000000 | RPINR18  | 7B4     | 0011111100111111   |

| IOCFJ        | 70C     | 000000000000000000000000000000000000000 | AD1CON4          | 752     | 000000000000000000000000000000000000000 | RPINR19  | 7B6     | 0011111100111111   |

| IOCPUJ       | 70E     | 000000000000000000000000000000000000000 | AD1CON5          | 754     | 000000000000000000000000000000000000000 | RPINR20  | 7B8     | 0011111100111111   |

| IOCPDJ       | 710     | 000000000000000000000000000000000000000 | AD1CHITL         | 756     | 000000000000000000000000000000000000000 | RPINR21  | 7BA     | 0011111100111111   |

| A/D          |         |                                         | AD1CHITH         | 758     | 000000000000000000000000000000000000000 | RPINR22  | 7BC     | 0011111100111111   |

| AD1BUF0      | 712     | *****                                   | ADC1CTMENL       | 75A     | 000000000000000000000000000000000000000 | RPINR23  | 7BE     | 0011111100111111   |

| AD1BUF1      | 714     | *****                                   | ADC1CTMENH       | 75C     | 000000000000000000000000000000000000000 | RPINR24  | 7C0     | 0011111100111111   |

| AD1BUF2      | 716     | *****                                   | ADC1RESDMA       | 75E     | 000000000000000000000000000000000000000 | RPINR25  | 7C2     | 0011111100111111   |

| AD1BUF3      | 718     | *****                                   | NVM Controller   | •       |                                         | RPINR26  | 7C4     | 0011111100111111   |

| AD1BUF4      | 71A     | *****                                   | NVMCON           | 760     | 00000000000000000000( <b>1)</b>         | RPINR27  | 7C6     | 0011111100111111   |

| AD1BUF5      | 71C     | *****                                   | NVMADRL          | 762     | 000000000000000000000000000000000000000 | RPINR28  | 7C8     | 0011111100111111   |

| AD1BUF6      | 71E     | *****                                   | NVMADRH          | 764     | 000000000000000000000000000000000000000 | RPINR29  | 7CA     | 0011111100111111   |

| AD1BUF7      | 720     | *****                                   | NVMKEY           | 766     | 000000000000000000000000000000000000000 | RPINR30  | 7CC     | 0011111100111111   |

| AD1BUF8      | 722     | *****                                   | NVMSRCADRL       | 768     | 000000000000000000000000000000000000000 | RPINR31  | 7CE     | 0011111100111111   |

| AD1BUF9      | 724     | *****                                   | NVMSRCADRH       | 76A     | 000000000000000000000000000000000000000 | RPOR0    | 7D4     | 000000000000000000 |

| AD1BUF10     | 726     | *****                                   | JDATAL           | 77C     | *****                                   | RPOR1    | 7D6     | 000000000000000000 |

| AD1BUF11     | 728     | *****                                   | JDATAH           | 77E     | *****                                   | RPOR2    | 7D8     | 000000000000000000 |

| AD1BUF12     | 72A     | *****                                   | Peripheral Pin S | elect   |                                         | RPOR3    | 7DA     | 000000000000000000 |

| AD1BUF13     | 72C     | *****                                   | RPINR0           | 790     | 0011111100111111                        | RPOR4    | 7DC     | 000000000000000000 |

| AD1BUF14     | 72E     | *****                                   | RPINR1           | 792     | 0011111100111111                        | RPOR5    | 7DE     | 000000000000000000 |

| AD1BUF15     | 730     | *****                                   | RPINR2           | 794     | 0011111100111111                        | RPOR6    | 7E0     | 000000000000000000 |

| AD1BUF16     | 732     | *****                                   | RPINR3           | 796     | 0011111100111111                        | RPOR7    | 7E2     | 000000000000000000 |

| AD1BUF17     | 734     | *****                                   | RPINR4           | 798     | 0011111100111111                        | RPOR8    | 7E4     | 000000000000000000 |

| AD1BUF18     | 736     | *****                                   | RPINR5           | 79A     | 0011111100111111                        | RPOR9    | 7E6     | 000000000000000000 |

| AD1BUF19     | 738     | *****                                   | RPINR6           | 79C     | 0011111100111111                        | RPOR10   | 7E8     | 000000000000000000 |

| AD1BUF20     | 73A     | *****                                   | RPINR7           | 7A2     | 0011111100111111                        | RPOR11   | 7EA     | 000000000000000000 |

| AD1BUF21     | 73C     | *****                                   | RPINR8           | 7A0     | 0011111100111111                        | RPOR12   | 7EC     | 000000000000000000 |

| AD1BUF22     | 73E     | *****                                   | RPINR9           | 7A2     | 0011111100111111                        | RPOR13   | 7EE     | 000000000000000000 |

| AD1BUF23     | 740     | *****                                   | RPINR10          | 7A4     | 0011111100111111                        | RPOR14   | 7F0     | 000000000000000000 |

| AD1BUF24     | 742     | *****                                   | RPINR11          | 7A6     | 0011111100111111                        | RPOR15   | 7F2     | 000000000000000000 |

| AD1BUF25     | 744     | *****                                   | RPINR12          | 7A8     | 0011111100111111                        |          |         |                    |

#### TABLE 4-12: SFR BLOCK 700h

Legend: x = unknown or indeterminate value. Reset and address values are in hexadecimal.

Note 1: The Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write/erase operations or partition swap at the time of Reset.

| R/W-0         | R/W-0                                 | R/W-0                                               | R/W-0                      | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

|---------------|---------------------------------------|-----------------------------------------------------|----------------------------|-------------------|------------------|-----------------|----------|

| CCP1IF        | RTCIF                                 | DMA5IF                                              | SPI3RXIF                   | SPI2RXIF          | SPI1RXIF         | SPI4RXIF        | KEYSTRIF |

| bit 15        | ·                                     |                                                     |                            |                   | ÷                |                 | bit 8    |

| R/W-0         | R/W-0                                 | R/W-0                                               | U-0                        | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

| CRYDNIF       | INT4IF                                | INT3IF                                              | _                          | CCT7IF            | MI2C2IF          | SI2C2IF         | CCT6IF   |

| bit 7         |                                       |                                                     |                            |                   |                  |                 | bit C    |

| Legend:       |                                       |                                                     |                            |                   |                  |                 |          |

| R = Readable  | e bit                                 | W = Writable                                        | bit                        | U = Unimplem      | nented bit, read | as '0'          |          |

| -n = Value at | POR                                   | '1' = Bit is set                                    |                            | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |

| bit 15        | 1 = Interrupt r                       | CP1 Capture/C<br>request has occ<br>request has not |                            | ot Flag Status b  | it               |                 |          |

| bit 14        | 1 = Interrupt r                       | Time Clock and<br>equest has occ<br>equest has not  |                            | rupt Flag Statu   | s bit            |                 |          |

| bit 13        | 1 = Interrupt r                       | A Channel 5 In<br>equest has occ<br>equest has not  |                            | tus bit           |                  |                 |          |

| bit 12        | SPI3RXIF: SF<br>1 = Interrupt r       | •                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 11        | SPI2RXIF: SF<br>1 = Interrupt r       | •                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 10        | SPI1RXIF: SF<br>1 = Interrupt r       | -                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 9         | SPI4RXIF: SF<br>1 = Interrupt r       | -                                                   | errupt Flag Stat<br>curred | us bit            |                  |                 |          |

| bit 8         | <b>KEYSTRIF:</b> C<br>1 = Interrupt r | -                                                   | ey Store Progra            | am Done Interru   | upt Flag Status  | bit             |          |

| bit 7         | CRYDNIF: Cr<br>1 = Interrupt r        |                                                     | peration Done Ir           | nterrupt Flag St  | atus bit         |                 |          |

| bit 6         | INT4IF: Exter<br>1 = Interrupt r      | •                                                   | Flag Status bit<br>curred  |                   |                  |                 |          |

| bit 5         | INT3IF: Exter                         | •                                                   | Flag Status bit<br>curred  |                   |                  |                 |          |

| bit 4         | Unimplemen                            | ted: Read as '                                      | 0'                         |                   |                  |                 |          |

| bit 3         |                                       | P7 Timer Inter                                      | rupt Flag Status<br>curred | s bit             |                  |                 |          |

|               |                                       | request has not                                     |                            |                   |                  |                 |          |

|               |                                       |                                                     |                            |                   |                  |                 |          |

#### REGISTER 8-9: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| REGISTER         | 8-26: IPC4:                                 |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|------------------|-----------------|----------|--|--|--|--|--|

| U-0              | R/W-1                                       | R/W-0                                                                                                   | R/W-0                         | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |

| _                | CNIP2                                       | CNIP1                                                                                                   | CNIP0                         | —                 | CMIP2            | CMIP1           | CMIP0    |  |  |  |  |  |

| bit 15           |                                             |                                                                                                         |                               |                   |                  |                 | bit      |  |  |  |  |  |

| U-0              | R/W-1                                       | R/W-0                                                                                                   | R/W-0                         | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |

| 0-0              | MI2C1IP2                                    | MI2C1IP1                                                                                                | MI2C1IP0                      | 0-0               | SI2C1IP2         | SI2C1IP1        | SI2C1IP0 |  |  |  |  |  |

|                  | IVII2CTIP2                                  | WIZCTFT                                                                                                 | IVIIZG HFU                    |                   | 3120 TIF2        | SIZCTIFT        | 1        |  |  |  |  |  |

| bit 7            |                                             |                                                                                                         |                               |                   |                  |                 | bit      |  |  |  |  |  |

| Legend:          |                                             |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

| R = Readab       | le bit                                      | W = Writable I                                                                                          | oit                           | U = Unimpler      | mented bit, read | d as '0'        |          |  |  |  |  |  |

| -n = Value a     | t POR                                       | '1' = Bit is set                                                                                        |                               | '0' = Bit is cle  | ared             | x = Bit is unkn | iown     |  |  |  |  |  |

|                  |                                             |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

| bit 15           | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |  |  |

| bit 14-12        | CNIP<2:0>:                                  | nput Change N                                                                                           | otification Inte              | rrupt Priority bi | ts               |                 |          |  |  |  |  |  |

|                  | 111 = Interru                               | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|                  | 001 = Interru                               | pt is Priority 1                                                                                        |                               |                   |                  |                 |          |  |  |  |  |  |

|                  |                                             | pt source is dis                                                                                        | abled                         |                   |                  |                 |          |  |  |  |  |  |

| bit 11           | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |  |  |

| bit 10-8         | CMIP<2:0>: (                                | Comparator Inte                                                                                         | errupt Priority I             | oits              |                  |                 |          |  |  |  |  |  |

|                  | 111 = Interru                               | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|                  | 001 = Interrupt is Priority 1               |                                                                                                         |                               |                   |                  |                 |          |  |  |  |  |  |

|                  | 000 = Interru                               | pt source is dis                                                                                        | abled                         |                   |                  |                 |          |  |  |  |  |  |

| bit 7            | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |  |  |

| bit 6-4          | MI2C1IP<2:0                                 | >: Master I2C1                                                                                          | Event Interrup                | ot Priority bits  |                  |                 |          |  |  |  |  |  |

|                  | 111 = Interru                               | at in Dainait 7 (                                                                                       |                               |                   |                  |                 |          |  |  |  |  |  |

|                  |                                             | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | •                                           | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | •                                           | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | •<br>•<br>001 = Interru                     | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  |                                             |                                                                                                         |                               | / interrupt)      |                  |                 |          |  |  |  |  |  |

| bit 3            | 000 = Interru                               | pt is Priority 1                                                                                        | abled                         | / interrupt)      |                  |                 |          |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen                 | pt is Priority 1<br>pt source is dis                                                                    | abled                         |                   |                  |                 |          |  |  |  |  |  |

| bit 3<br>bit 2-0 | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0                                          | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br>t <b>ed:</b> Read as '0<br>>: Slave I2C1 E                      | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br>t <b>ed:</b> Read as '0<br>>: Slave I2C1 E                      | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0<br>>: Slave I2C1 E<br>pt is Priority 7 ( | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |  |  |

## REGISTER 8-26: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

A recommended code sequence for a clock switch includes the following:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0> in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of the failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON,#0                            |

|                                           |

## 9.5 FRC Active Clock Tuning

PIC24FJ256GA412/GB412 family devices include an automatic mechanism to calibrate the FRC during run time. This system uses active clock tuning from a source of known accuracy to maintain the FRC within a very narrow margin of its nominal 8 MHz frequency. This allows for a frequency accuracy that is well within the requirements of the *"USB 2.0 Specification"*, regarding full-speed USB devices.

| Note: | The self-tune feature maintains sufficient |  |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | accuracy for operation in USB Device       |  |  |  |  |  |  |  |  |  |  |

|       | mode. For applications that function as a  |  |  |  |  |  |  |  |  |  |  |

|       | USB host, a high-accuracy clock source     |  |  |  |  |  |  |  |  |  |  |

|       | (±0.05%) is still required.                |  |  |  |  |  |  |  |  |  |  |

The self-tune system is controlled by the bits in the upper half of the OSCTUN register. Setting the STEN bit (OSCTUN<15>) enables the self-tuning feature, allowing the hardware to calibrate to a source selected by the STSRC bit (OSCTUN<12>). When STSRC = 1, the system uses the Start-of-Frame (SOF) packets from an external USB host for its source. When STSRC = 0, the system uses the crystal-controlled SOSC for its calibration source. Regardless of the source, the system uses the TUN<5:0> bits (OSCTUN<5:0>) to change the FRC Oscillator's frequency. Frequency monitoring and adjustment is dynamic, occurring continuously during run time. While the system is active, the TUNx bits cannot be written to by software.

| Note: | To use the USB as a reference clock<br>tuning source (STSRC = 1), the micro-<br>controller must be configured for USB<br>device operation and connected to a<br>non-suspended USB host or hub port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If the SOSC is to be used as the reference clock tuning source (STSRC = 0), the SOSC must also be enabled for clock tuning to occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -     | the second s |

The self-tune system can generate a hardware interrupt, FSTIF. The interrupt can result from a drift of the FRC from the reference by greater than 0.2%, in either direction, or whenever the frequency deviation is beyond the ability of the TUNx bits to correct (i.e., greater than 1.5%). The STLOCK and STOR status bits (OSCTUN<11,9>) are used to indicate these conditions.

The STLPOL and STORPOL bits (OSCTUN<10,8>) configure the FSTIF interrupt to occur in the presence or the absence of the conditions. It is the user's responsibility to monitor both the STLOCK and STOR bits to determine the exact cause of the interrupt.

**Note:** The STLPOL and STORPOL bits should be ignored when the self-tune system is disabled (STEN = 0).

#### TABLE 10-2: EXITING POWER-SAVING MODES

|                   |       | Exit Conditions |     |        |      |       |      |                        |                   |  |  |  |

|-------------------|-------|-----------------|-----|--------|------|-------|------|------------------------|-------------------|--|--|--|

| Mode              | Inter | rupts           |     | Resets |      | RTCC  | WDT  | Vdd                    | Code<br>Execution |  |  |  |

|                   | All   | INT0            | All | POR    | MCLR | Alarm | WDI  | Restore <sup>(2)</sup> | Resumes           |  |  |  |

| Idle              | Y     | Y               | Y   | Y      | Y    | Y     | Y    | N/A                    | Next instruction  |  |  |  |

| Sleep (all modes) | Y     | Y               | Y   | Y      | Y    | Y     | Y    | N/A                    |                   |  |  |  |

| Deep Sleep        | Ν     | Y               | Ν   | Y      | Y    | Y     | Y(1) | N/A                    | Reset vector      |  |  |  |

| VBAT              | Ν     | Ν               | Ν   | Ν      | Ν    | Ν     | Ν    | Y                      | Reset vector      |  |  |  |

Note 1: Deep Sleep WDT.

2: A POR or POR-like Reset results whenever VDD is removed and restored in any mode.

#### 10.1.1 INSTRUCTION-BASED POWER-SAVING MODES

Three of the power-saving modes are entered through the execution of the PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. Deep Sleep mode stops clock operation, code execution and all peripherals, except RTCC and DSWDT. It also freezes I/O states and removes power to Flash memory, and may remove power to SRAM.

The assembly syntax of the PWRSAV instruction is shown in Example 10-1. Sleep and Idle modes are entered directly with a single assembler command. Deep Sleep requires an additional sequence to unlock and enable the entry into Deep Sleep, which is described in **Section 10.4.1 "Entering Deep Sleep Mode**".

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

The features enabled with the low-voltage/retention regulator result in some changes to the way that Sleep and Deep Sleep modes behave. See **Section 10.3 "Sleep Mode"** and **Section 10.4 "Deep Sleep Mode"** for additional information.

## 10.1.1.1 Interrupts Coincident with Power Save Instructions

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

For Deep Sleep mode, interrupts that coincide with the execution of the PWRSAV instruction may be lost. The microcontroller resets on leaving Deep Sleep and the interrupt will be lost.

Interrupts that occur during the Deep Sleep unlock sequence will interrupt the mandatory five-instruction cycle sequence timing and cause a failure to enter Deep Sleep. For this reason, it is recommended to disable all interrupts during the Deep Sleep unlock sequence.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

```

// Syntax to enter Sleep mode:

#SLEEP_MODE

PWRSAV

; Put the device into SLEEP mode

11

//Synatx to enter Idle mode:

PWRSAV

#IDLE MODE

; Put the device into IDLE mode

11

// Syntax to enter Deep Sleep mode:

// First use the unlock sequence to set the DSEN bit (see Example 10-2)

BSET DSCON, #DSEN ; Enable Deep Sleep

DSCON, #DSEN

BSET

; Enable Deep Sleep(repeat the command)

PWRSAV

#SLEEP_MODE

; Put the device into Deep SLEEP mode

```

## TABLE 11-4: PORTC REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | ange   |              |        |         |         |    |    |   |   | Bits |   |   |             |         |        |   |   |

|------------------|--------|--------------|--------|---------|---------|----|----|---|---|------|---|---|-------------|---------|--------|---|---|

| Register<br>Name | Bit Ra | 15           | 14     | 13      | 12      | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4           | 4 3 2 1 |        | 0 |   |

| ANSC             | 15:0   | —            |        | —       | —       | —  |    |   | — | _    |   | — | ANSC<4:1>   |         |        | — |   |

| TRISC            | 15:0   | TRISC15      |        | —       | TRISC12 | —  |    | - | — |      |   | — | TRISC<4:1>  |         |        | — |   |

| PORTC            | 15:0   |              | PORTC  | <15:12> |         | —  |    |   | — | _    |   | — | PORTC<4:1>  |         |        |   |   |

| LATC             | 15:0   | LATC15       |        |         | LATC12  | —  |    |   | — | _    |   | — | LATC<4:1>   |         |        |   |   |

| ODCC             | 15:0   | ODCC15       |        |         | ODCC12  | —  |    |   | — | _    |   | — |             | ODCC    | <4:1>  |   |   |

| IOCPC            | 15:0   |              | IOCPC< | <15:12> |         | —  |    |   | — | _    |   | — | IOCPC<4:1>  |         |        |   |   |

| IOCNC            | 15:0   |              | IOCNC< | <15:12> |         | —  |    |   | — | _    |   | — |             | IOCNC   | <4:1>  |   |   |

| IOCFC            | 15:0   | IOCFC<15:12> |        |         |         | —  |    |   | — | _    |   | — | IOCFC<4:1>  |         |        |   |   |

| IOCPUC           | 15:0   |              | IOCPUC | <15:12> |         | —  |    |   | — | _    |   | — | IOCPUC<4:1> |         |        |   | — |

| IOCPDC           | 15:0   |              | IOCPDC | <15:12> |         | _  |    |   | _ | _    |   | - |             | IOCPD   | C<4:1> |   | — |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

## TABLE 11-5: PORTD REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | ange      |    |             |    |    |    |    |   |     | Bits       |   |   |   |   |   |   |   |

|------------------|-----------|----|-------------|----|----|----|----|---|-----|------------|---|---|---|---|---|---|---|

| Register<br>Name | Bit Range | 15 | 14          | 13 | 12 | 11 | 10 | 9 | 8   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ANSD             | 15:0      |    | ANSD<15:0>  |    |    |    |    |   |     |            |   |   |   |   |   |   |   |

| TRISD            | 15:0      |    | TRISD<15:0> |    |    |    |    |   |     |            |   |   |   |   |   |   |   |

| PORTD            | 15:0      |    | PORTD<15:0> |    |    |    |    |   |     |            |   |   |   |   |   |   |   |

| LATD             | 15:0      |    | LATD<15:0>  |    |    |    |    |   |     |            |   |   |   |   |   |   |   |

| ODCD             | 15:0      |    |             |    |    |    |    |   | O   | DCD<15:0>  |   |   |   |   |   |   |   |

| IOCPD            | 15:0      |    |             |    |    |    |    |   | 10  | CPD<15:0>  |   |   |   |   |   |   |   |

| IOCND            | 15:0      |    |             |    |    |    |    |   | 10  | CND<15:0>  |   |   |   |   |   |   |   |

| IOCFD            | 15:0      |    | IOCFD<15:0> |    |    |    |    |   |     |            |   |   |   |   |   |   |   |

| IOCPUD           | 15:0      |    |             |    |    |    |    |   | 100 | CPUD<15:0> | > |   |   |   |   |   |   |

| IOCPDD           | 15:0      |    |             |    |    |    |    |   | 100 | CPDD<15:0> | > |   |   |   |   |   |   |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

| U-0           | U-0                                                                                                                                                          |                  |       |                   |       |                    |       |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|-------|--------------------|-------|--|--|--|--|--|

|               | 0-0                                                                                                                                                          | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0              | R/W-0 |  |  |  |  |  |

| —             | —                                                                                                                                                            | RP9R5            | RP9R4 | RP9R3             | RP9R2 | RP9R1              | RP9R0 |  |  |  |  |  |

| bit 15        |                                                                                                                                                              |                  |       |                   |       |                    | bit 8 |  |  |  |  |  |

|               |                                                                                                                                                              |                  |       |                   |       |                    |       |  |  |  |  |  |

| U-0           | U-0                                                                                                                                                          | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0              | R/W-0 |  |  |  |  |  |

| —             | —                                                                                                                                                            | RP8R5            | RP8R4 | RP8R3             | RP8R2 | RP8R1              | RP8R0 |  |  |  |  |  |

| bit 7         |                                                                                                                                                              |                  |       |                   |       |                    | bit 0 |  |  |  |  |  |

|               |                                                                                                                                                              |                  |       |                   |       |                    |       |  |  |  |  |  |

| Legend:       |                                                                                                                                                              |                  |       |                   |       |                    |       |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                        | W = Writable I   | oit   | U = Unimplem      |       |                    |       |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                          | '1' = Bit is set |       | '0' = Bit is clea | ared  | x = Bit is unknown |       |  |  |  |  |  |

|               |                                                                                                                                                              |                  |       |                   |       |                    |       |  |  |  |  |  |

| bit 15-14     | Unimplement                                                                                                                                                  | ted: Read as 'o  | )'    |                   |       |                    |       |  |  |  |  |  |

| bit 13-8      | <b>RP9R&lt;5:0&gt;:</b> RP9 Output Pin Mapping bits<br>Peripheral Output Number n is assigned to pin, RP9 (see Table 11-12 for peripheral function numbers). |                  |       |                   |       |                    |       |  |  |  |  |  |

#### REGISTER 11-27: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|         | •                                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------|

| bit 5-0 | RP8R<5:0>: RP8 Output Pin Mapping bits                                                                |

|         | Peripheral Output Number n is assigned to pin, RP8 (see Table 11-12 for peripheral function numbers). |

### REGISTER 11-28: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0                                | U-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----|--------------|-----------------------------------------|------------------------------------|--------|--------|--------|

| _                                  | —   | RP11R5       | RP11R4                                  | RP11R3                             | RP11R2 | RP11R1 | RP11R0 |

| bit 15                             |     |              |                                         |                                    |        |        | bit 8  |

|                                    |     |              |                                         |                                    |        |        |        |

| U-0                                | U-0 | R/W-0        | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |

| —                                  | —   | RP10R5       | RP10R4                                  | RP10R3                             | RP10R2 | RP10R1 | RP10R0 |

| bit 7                              |     |              |                                         |                                    |        |        | bit 0  |

|                                    |     |              |                                         |                                    |        |        |        |

| Legend:                            |     |              |                                         |                                    |        |        |        |

| R = Readable bit W = Writab        |     | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |        |        |        |

| -n = Value at POR '1' = Bit is set |     |              | '0' = Bit is cleared x = Bit is unknown |                                    |        | nown   |        |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits

**Unimplemented:** Read as '0'

Peripheral Output Number n is assigned to pin, RP11 (see Table 11-12 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP10R<5:0>:** RP10 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP10 (see Table 11-12 for peripheral function numbers).

bit 7-6

| R/W-0              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                         | U-0                        | U-0                        | U-0             | R/W-0                  | R/W-0                  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------|----------------------------|-----------------|------------------------|------------------------|

| TON <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TSIDL <sup>(2)</sup>                          |                            |                            | —               | TECS1 <sup>(2,3)</sup> | TECS0 <sup>(2,3)</sup> |

| bit 15             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |                            |                            |                 |                        | bit                    |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DAALO                                         | DAMO                       |                            |                 | DAVO                   |                        |

| U-0                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                         | R/W-0                      | U-0                        | U-0             | R/W-0                  | U-0                    |

|                    | TGATE <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TCKPS1 <sup>(2)</sup>                         | TCKPS0 <sup>(2)</sup>      |                            | —               | TCS <sup>(2,3)</sup>   | — hit.                 |

| bit 7              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |                            |                            |                 |                        | bit                    |

| Legend:            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |                            |                            |                 |                        |                        |