Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga406t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR PIC24FJXXXGB412 (CONTINUED)

| Pin | Function                                                  | Pin | Function                                          |

|-----|-----------------------------------------------------------|-----|---------------------------------------------------|

| J1  | SEG4/AN3/C2INA/IOCB3/RB3                                  | K7  | SEG8/AN14/RP14/CTED5/CTPLS/PMA1/PMALH/IOCB14/RB14 |

| J2  | SEG5/AN2/CTCMP/C2INB/RP13/CTED13/IOCB2/RB2                | K8  | Vdd                                               |

| J3  | PGED2/SEG63/AN7/RP7/U6TX/IOCB7/RB7                        | K9  | SEG39/ <b>RP5</b> /IOCD15/RD15                    |

| J4  | AVdd                                                      | K10 | SEG12/RP16/USBID/IOCF3/RF3                        |

| J5  | IOCH7/RH7                                                 | K11 | SEG40/ <b>RP30</b> /IOCF2/RF2                     |

| J6  | TCK/IOCA1/RA1                                             | L1  | PGEC2/LCDBIAS3/AN6/ <b>RP6</b> /IOCB6/RB6         |

| J7  | SEG18/AN12/U6RX/CTED2/PMA11/IOCB12/RB12                   | L2  | SEG36/VREF-/CVREF-/PMA7/IOCA9/RA9                 |

| J8  | IOCH9/RH9                                                 | L3  | AVss                                              |

| J9  | IOCH10/RH10                                               | L4  | SEG30/AN9/TMPR/RP9/T1CK/IOCB9/RB9                 |

| J10 | SEG41/ <b>RP15</b> /IOCF8/RF8                             | L5  | IOCH6/RH6                                         |

| J11 | D-/IOCG3/RG3                                              | L6  | SEG53/ <b>RP31</b> /IOCF13/RF13                   |

| K1  | PGEC1/SEG6/VREF-/CVREF-/AN1/AN1-/RP1/CTED12/IOCB1/<br>RB1 | L7  | SEG19/AN13/SDI4/CTED1/PMA10/IOCB13/RB13           |

| K2  | PGED1/SEG7/VREF+/CVREF+/DVREF+/AN0/ <b>RP0</b> /IOCB0/RB0 | L8  | SEG9/AN15/RP29/CTED6/PMA0/PMALL/IOCB15/RB15       |

| K3  | SEG37/VREF+/CVREF+/DVREF+/PMA6/IOCA10/RA10                | L9  | SEG38/ <b>RPI43</b> /IOCD14/RD14                  |

| K4  | SEG31/AN8/ <b>RP8</b> /PWRGT/IOCB8/RB8                    | L10 | SEG10/RP10/PMA9/IOCF4/RF4                         |

| K5  | AN11/REFI1/SS4/FSYNC4/PMA12/IOCB11/RB11                   | L11 | SEG11/RP17/PMA8/IOCF5/RF5                         |

| K6  | SEG54/RPI32/CTED7/PMA18/IOCF12/RF12                       |     |                                                   |

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select functions.

| TADLE 1-4:    | 1             | n/Pad Numl |         |     |                |                           |  |  |  |  |

|---------------|---------------|------------|---------|-----|----------------|---------------------------|--|--|--|--|

| Pin Function  | 64-Pin        | 100-Pin    | 121-Pin | I/O | Input Buffer   | Description               |  |  |  |  |

|               | TQFP          | TQFP       | TFBGA   |     | input Builer   |                           |  |  |  |  |

| IOCD0         | 46            | 72         | D9      | I   | ST             | PORTD Interrupt-on-Change |  |  |  |  |

| IOCD1         | 49            | 76         | A11     | I   | ST             |                           |  |  |  |  |

| IOCD2         | 50            | 77         | A10     | I   | ST             |                           |  |  |  |  |

| IOCD3         | 51            | 78         | B9      | I   | ST             |                           |  |  |  |  |

| IOCD4         | 52            | 81         | C8      | I   | ST             |                           |  |  |  |  |

| IOCD5         | 53            | 82         | B8      | I   | ST             |                           |  |  |  |  |

| IOCD6         | 54            | 83         | D7      | I   | ST             |                           |  |  |  |  |

| IOCD7         | 55            | 84         | C7      | I   | ST             |                           |  |  |  |  |

| IOCD8         | 42            | 68         | E9      | I   | ST             |                           |  |  |  |  |

| IOCD9         | 43            | 69         | E10     | I   | ST             |                           |  |  |  |  |

| IOCD10        | 44            | 70         | D11     | I   | ST             |                           |  |  |  |  |

| IOCD11        | 45            | 71         | C11     | I   | ST             |                           |  |  |  |  |

| IOCD12        | —             | 79         | A9      | I   | ST             |                           |  |  |  |  |

| IOCD13        | —             | 80         | D8      | I   | ST             |                           |  |  |  |  |

| IOCD14        | —             | 47         | L9      | I   | ST             |                           |  |  |  |  |

| IOCD15        | —             | 48         | K9      | I   | ST             |                           |  |  |  |  |

| IOCE0         | 60            | 93         | 1E3     | I   | ST             | PORTE Interrupt-on-Change |  |  |  |  |

| IOCE1         | 61            | 94         | E15     | I   | ST             |                           |  |  |  |  |

| IOCE2         | 62            | 98         | E19     | I   | ST             |                           |  |  |  |  |

| IOCE3         | 63            | 99         | E30     | I   | ST             |                           |  |  |  |  |

| IOCE4         | 64            | 100        | E31     | I   | ST             |                           |  |  |  |  |

| IOCE5         | 1             | 3          | D3      | I   | ST             |                           |  |  |  |  |

| IOCE6         | 2             | 4          | C1      | I   | ST             |                           |  |  |  |  |

| IOCE7         | 3             | 5          | D2      | I   | ST             |                           |  |  |  |  |

| IOCE8         | —             | 18         | G1      | I   | ST             |                           |  |  |  |  |

| IOCE9         | —             | 19         | G2      | I   | ST             |                           |  |  |  |  |

| IOCF0         | 58            | 87         | B6      | I   | ST             | PORTF Interrupt-on-Change |  |  |  |  |

| IOCF1         | 59            | 88         | A6      | I   | ST             |                           |  |  |  |  |

| IOCF2         | 34            | 52         | K11     | I   | ST             |                           |  |  |  |  |

| IOCF3         | 33            | 51         | K10     | I   | ST             |                           |  |  |  |  |

| IOCF4         | 31            | 49         | L10     | I   | ST             |                           |  |  |  |  |

| IOCF5         | 32            | 50         | L11     | I   | ST             |                           |  |  |  |  |

| IOCF6         | 35            | 55         | H9      | I   | ST             |                           |  |  |  |  |

| IOCF7         | _             | 54         | H8      | I   | ST             |                           |  |  |  |  |

| IOCF8         | —             | 53         | J10     | I   | ST             |                           |  |  |  |  |

| IOCF12        | —             | 40         | K6      | I   | ST             |                           |  |  |  |  |

| IOCF13        | _             | 39         | L6      | I   | ST             |                           |  |  |  |  |

| Legend: TTL = | TTL input buf | fer        |         |     | ST = Schmitt T | rigger input buffer       |  |  |  |  |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

|               | 1                                                               | n/Pad Numb      |                  |     |                          |                                            |  |  |  |  |  |

|---------------|-----------------------------------------------------------------|-----------------|------------------|-----|--------------------------|--------------------------------------------|--|--|--|--|--|

| Pin Function  | 64-Pin<br>TQFP                                                  | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer             | Description                                |  |  |  |  |  |

| RPI32         | _                                                               | 40              | K6               | I   | ST                       | Remappable Peripherals (Input only)        |  |  |  |  |  |

| RPI33         | —                                                               | 18              | G1               | I   | ST                       |                                            |  |  |  |  |  |

| RPI34         | —                                                               | 19              | G2               | I   | ST                       |                                            |  |  |  |  |  |

| RPI35         | _                                                               | 67              | E8               | I   | ST                       |                                            |  |  |  |  |  |

| RPI36         | —                                                               | 66              | E11              | I   | ST                       |                                            |  |  |  |  |  |

| RPI37         | 48                                                              | 74              | B11              | I   | ST                       |                                            |  |  |  |  |  |

| RPI38         | _                                                               | 6               | D1               | I   | ST                       |                                            |  |  |  |  |  |

| RPI39         | _                                                               | 7               | E4               | I   | ST                       |                                            |  |  |  |  |  |

| RPI40         | _                                                               | 8               | E2               | I   | ST                       |                                            |  |  |  |  |  |

| RPI41         | _                                                               | 9               | E1               | I   | ST                       |                                            |  |  |  |  |  |

| RPI42         | _                                                               | 79              | A9               | I   | ST                       |                                            |  |  |  |  |  |

| RPI43         | —                                                               | 47              | L9               | I   | ST                       |                                            |  |  |  |  |  |

| RTCC          | 42                                                              | 68              | E9               | 0   | DIGMV                    | Real-Time Clock Alarm/Seconds Pulse Output |  |  |  |  |  |

| SCK4          | 59                                                              | 88              | A6               | I/O | DIG/ST                   | SPI4 Clock                                 |  |  |  |  |  |

| SCL1          | 37                                                              | 57              | H10              | I/O | DIG/I <sup>2</sup> C/SMB | I2C1 Synchronous Serial Clock Input/Output |  |  |  |  |  |

| SCL2          | 32                                                              | 58              | H11              | I/O | DIG/I <sup>2</sup> C/SMB | I2C2 Synchronous Serial Clock Input/Output |  |  |  |  |  |

| SCL3          | 2                                                               | 4               | C1               | I/O | DIG/I <sup>2</sup> C/SMB | I2C3 Synchronous Serial Clock Input/Output |  |  |  |  |  |

| SDA1          | 36                                                              | 56              | J11              | I/O | DIG/I <sup>2</sup> C/SMB | I2C1 Data Input/Output                     |  |  |  |  |  |

| SDA2          | 31                                                              | 59              | G10              | I/O | DIG/I <sup>2</sup> C/SMB | I2C2 Data Input/Output                     |  |  |  |  |  |

| SDA3          | 3                                                               | 5               | D2               | I/O | DIG/I <sup>2</sup> C/SMB | I2C3 Data Input/Output                     |  |  |  |  |  |

| SDI4          | 28                                                              | 42              | L7               | I   | ST                       | SPI4 Data Input                            |  |  |  |  |  |

| SDO4          | 23                                                              | 34              | H5               | 0   | DIG                      | SPI4 Data Output                           |  |  |  |  |  |

| Legend: TTL = | egend: TTL = TTL input buffer ST = Schmitt Trigger input buffer |                 |                  |     |                          |                                            |  |  |  |  |  |

#### **TABLE 1-4:** PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

|              | Pir            | /Pad Numl       | per              |     |              |                                          |

|--------------|----------------|-----------------|------------------|-----|--------------|------------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                              |

| RP0          | 16             | 25              | K2               | I/O | DIG/ST       | Remappable Peripherals (Input or Output) |

| RP1          | 15             | 24              | K1               | I/O | DIG/ST       |                                          |

| RP2          | 42             | 68              | E9               | I/O | DIG/ST       |                                          |

| RP3          | 44             | 70              | D11              | I/O | DIG/ST       |                                          |

| RP4          | 43             | 69              | E10              | I/O | DIG/ST       |                                          |

| RP5          | _              | 48              | K9               | I/O | DIG/ST       |                                          |

| RP6          | 17             | 26              | L1               | I/O | DIG/ST       |                                          |

| RP7          | 18             | 27              | J3               | I/O | DIG/ST       |                                          |

| RP8          | 21             | 32              | K4               | I/O | DIG/ST       |                                          |

| RP9          | 22             | 33              | L4               | I/O | DIG/ST       |                                          |

| RP10         | 31             | 49              | L10              | I/O | DIG/ST       |                                          |

| RP11         | 46             | 72              | D9               | I/O | DIG/ST       |                                          |

| RP12         | 45             | 71              | C11              | I/O | DIG/ST       |                                          |

| RP13         | 14             | 23              | J2               | I/O | DIG/ST       |                                          |

| RP14         | 29             | 43              | K7               | I/O | DIG/ST       |                                          |

| RP15         | _              | 53              | J10              | I/O | DIG/ST       |                                          |

| RP16         | 33             | 51              | K10              | I/O | DIG/ST       |                                          |

| RP17         | 32             | 50              | L11              | I/O | DIG/ST       |                                          |

| RP18         | 11             | 20              | H1               | I/O | DIG/ST       |                                          |

| RP19         | 6              | 12              | F2               | I/O | DIG/ST       |                                          |

| RP20         | 53             | 82              | B8               | I/O | DIG/ST       |                                          |

| RP21         | 4              | 10              | E3               | I/O | DIG/ST       |                                          |

| RP22         | 51             | 78              | B9               | I/O | DIG/ST       |                                          |

| RP23         | 50             | 77              | A10              | I/O | DIG/ST       |                                          |

| RP24         | 49             | 76              | A11              | I/O | DIG/ST       |                                          |

| RP25         | 52             | 81              | C8               | I/O | DIG/ST       |                                          |

| RP26         | 5              | 11              | F4               | I/O | DIG/ST       |                                          |

| RP27         | 8              | 14              | F3               | I/O | DIG/ST       | 1                                        |

| RP28         | 12             | 21              | H2               | I/O | DIG/ST       | 1                                        |

| RP29         | 30             | 44              | L8               | I/O | DIG/ST       | 1                                        |

| RP30         | _              | 52              | K11              | I/O | DIG/ST       | 1                                        |

| RP31         | _              | 39              | L6               | I/O | DIG/ST       | 1                                        |

### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer I<sup>2</sup>C = I<sup>2</sup>C/SMBus input buffer XCVR = Dedicated transceiver

| TABLE 5 | 5-1: | DMA CHANNEL T          | RIGGER  | SOU  | RCES                   |         |      |                        |

|---------|------|------------------------|---------|------|------------------------|---------|------|------------------------|

| CHSEL<  | 6:0> | Trigger (Interrupt)    | CHSEL<  | 6:0> | Trigger (Interrupt)    | CHSEL<  | 6:0> | Trigger (Interrupt)    |

| 0000000 | 00h  | (Unimplemented)        | 0100110 | 26h  | SPI1 Receive Event     | 1001100 | 4Ch  | DMA Channel 4          |

| 0000001 | 01h  | SCCP7 IC/OC Event      | 0100111 | 27h  | SPI1 Transmit Event    | 1001101 | 4Dh  | DMA Channel 3          |

| 0000010 | 02h  | SCCP7 Timer            | 0101000 | 28h  | SPI1 General Event     | 1001110 | 4Eh  | DMA Channel 2          |

| 0000011 | 03h  | SCCP6 IC/OC Event      | 0101001 | 29h  | (Reserved, do not use) | 1001111 | 4Fh  | DMA Channel 1          |

| 0000100 | 04h  | SCCP6 Timer            | 0101010 | 2Ah  | (Reserved, do not use) | 1010000 | 50h  | DMA Channel 0          |

| 0000101 | 05h  | SCCP5 IC/OC Event      | 0101011 | 2Bh  | (Reserved, do not use) | 1010001 | 51h  | A/D Converter          |

| 0000110 | 06h  | SCCP5 Timer            | 0101100 | 2Ch  | I2C3 Slave Event       | 1010010 | 52h  | USB                    |

| 0000111 | 07h  | SCCP4 IC/OC Event      | 0101101 | 2Dh  | I2C3 Master Event      | 1010011 | 53h  | EPMP                   |

| 0001000 | 08h  | SCCP4 Timer            | 0101110 | 2Eh  | I2C3 Collision Event   | 1010100 | 54h  | HLVD                   |

| 0001001 | 09h  | (Reserved, do not use) | 0101111 | 2Fh  | I2C2 Slave Event       | 1010101 | 55h  | CRC Done               |

| 0001010 | 0Ah  | (Reserved, do not use) | 0110000 | 30h  | I2C2 Master Event      | 1010110 | 56h  | LCD                    |

| 0001011 | 0Bh  | SCCP3 IC/OC Event      | 0110001 | 31h  | I2C2 Collision Event   | 1010111 | 57h  | Crypto Done            |

| 0001100 | 0Ch  | SCCP3 Timer            | 0110010 | 32h  | I2C1 Slave Event       | 1011000 | 58h  | Crypto OTP Done        |

| 0001101 | 0Dh  | SCCP2 IC/OC Event      | 0110011 | 33h  | I2C1 Master Event      | 1011001 | 59h  | CLC4 Output            |

| 0001110 | 0Eh  | SCCP2 Timer            | 0110100 | 34h  | I2C1 Collision Event   | 1011010 | 5Ah  | CLC3 Output            |

| 0001111 | 0Fh  | MCCP1 IC/OC Event      | 0110101 | 35h  | UART6 Transmit         | 1011011 | 5Bh  | CLC2 Output            |

| 0010000 | 10h  | MCCP1 Timer            | 0110110 | 36h  | UART6 Receive          | 1011100 | 5Ch  | CLC1 Output            |

| 0010001 | 11h  | Output Compare 6       | 0110111 | 37h  | UART6 Error            | 1011101 | 5Dh  | (Reserved, do not use) |

| 0010010 | 12h  | Output Compare 5       | 0111000 | 38h  | UART5 Transmit         | 1011110 | 5Eh  | RTCC                   |

| 0010011 | 13h  | Output Compare 4       | 0111001 | 39h  | UART5 Receive          | 1011111 | 5Fh  | Timer5                 |

| 0010100 | 14h  | Output Compare 3       | 0111010 | 3Ah  | UART5 Error            | 1100000 | 60h  | Timer4                 |

| 0010101 | 15h  | Output Compare 2       | 0111011 | 3Bh  | UART4 Transmit         | 1100001 | 61h  | Timer3                 |

| 0010110 | 16h  | Output Compare 1       | 0111100 | 3Ch  | UART4 Receive          | 1100010 | 62h  | Timer2                 |

| 0010111 | 17h  | Input Capture 6        | 0111101 | 3Dh  | UART4 Error            | 1100011 | 63h  | Timer1                 |

| 0011000 | 18h  | Input Capture 5        | 0111110 | 3Eh  | UART3 Transmit         | 1100100 | 64h  | (Reserved, do not use) |

| 0011001 | 19h  | Input Capture 4        | 0111111 | 3Fh  | UART3 Receive          | 1100101 | 65h  | DAC                    |

| 0011010 | 1Ah  | Input Capture 3        | 1000000 | 40h  | UART3 Error            | 1100110 | 66h  | CTMU                   |

| 0011011 | 1Bh  | Input Capture 2        | 1000001 | 41h  | UART2 Transmit         | 1100111 | 67h  | Comparators Event      |

| 0011100 | 1Ch  | Input Capture 1        | 1000010 | 42h  | UART2 Receive          | 1101000 | 68h  | External Interrupt 4   |

| 0011101 | 1Dh  | SPI4 Receive Event     | 1000011 | 43h  | UART2 Error            | 1101001 | 69h  | External Interrupt 3   |

| 0011110 | 1Eh  | SPI4 Transmit Event    | 1000100 | 44h  | UART1 Transmit         | 1101010 | 6Ah  | External Interrupt 2   |

| 0011111 | 1Fh  | SPI4 General Event     | 1000101 | 45h  | UART1 Receive          | 1101011 | 6Bh  | External Interrupt 1   |

| 0100000 | 20h  | SPI3 Receive Event     | 1000110 | 46h  | UART1 Error            | 1101100 | 6Ch  | External Interrupt 0   |

| 0100001 | 21h  | SPI3 Transmit Event    | 1000111 | 47h  | (Reserved, do not use) | 1101101 | 6Dh  | Interrupt-on-Change    |

| 0100010 | 22h  | SPI3 General Event     | 1001000 | 48h  | (Reserved, do not use) | 1101110 | 6Eh  |                        |

| 0100011 | 23h  | SPI2 Receive Event     | 1001001 | 49h  | (Reserved, do not use) | •       | •    |                        |

| 0100100 | 24h  | SPI2 Transmit Event    | 1001010 | 4Ah  | (Reserved, do not use) | •       | •    | (Unimplemented)        |

| 0100101 | 25h  | SPI2 General Event     | 1001011 | 4Bh  | DMA Channel 5          | 1111111 | 7Fh  |                        |

# TABLE 5-1: DMA CHANNEL TRIGGER SOURCES

| REGISTER      |                                                                                                                             |                                                                                       |                | IUS REGISTE       |                  |                 |        |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| U-0           | R/W-0                                                                                                                       | R/W-0                                                                                 | U-0            | U-0               | U-0              | R/W-0           | R/W-0  |  |  |  |  |  |

| _             | DAC1IF                                                                                                                      | CTMUIF                                                                                |                |                   |                  | CCP7IF          | HLVDIF |  |  |  |  |  |

| bit 15        |                                                                                                                             |                                                                                       |                |                   |                  |                 | bit    |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                       | U-0                                                                                   | U-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| MI2C3IF       | SI2C3IF                                                                                                                     |                                                                                       | _              | CRCIF             | U2ERIF           | U1ERIF          | CCP2IF |  |  |  |  |  |

| bit 7         |                                                                                                                             |                                                                                       |                |                   |                  |                 | bit    |  |  |  |  |  |

| Legend:       |                                                                                                                             |                                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                       | W = Writable b                                                                        | oit            | U = Unimplerr     | nented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value at | POR                                                                                                                         | '1' = Bit is set                                                                      |                | '0' = Bit is clea |                  | x = Bit is unkr | iown   |  |  |  |  |  |

| bit 15        | Unimplemen                                                                                                                  | ted: Read as '0                                                                       | ,              |                   |                  |                 |        |  |  |  |  |  |

| bit 14        | -                                                                                                                           | C Converter Inte                                                                      |                | atus bit          |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has not                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 13        | CTMUIF: CTI                                                                                                                 | MU Interrupt Fla                                                                      | ig Status bit  |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 12-10     | •                                                                                                                           | request has not                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 9         | -                                                                                                                           | Unimplemented: Read as '0'<br>CCP7IF: SCCP7 Capture/Compare Interrupt Flag Status bit |                |                   |                  |                 |        |  |  |  |  |  |

| DIL 9         |                                                                                                                             | request has occ                                                                       |                | ipt Flag Status L | Л                |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has not                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 8         | HLVDIF: High                                                                                                                | n/Low-Voltage D                                                                       | etect Interrup | t Flag Status bit | t                |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

|               | -                                                                                                                           | request has not                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 7         |                                                                                                                             | ster I2C3 Event                                                                       |                | Status bit        |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ<br>request has not                                                    |                |                   |                  |                 |        |  |  |  |  |  |

| bit 6         | -                                                                                                                           | /e I2C3 Event Ir                                                                      |                | Status bit        |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

|               | 0 = Interrupt                                                                                                               | request has not                                                                       | occurred       |                   |                  |                 |        |  |  |  |  |  |

| bit 5-4       | Unimplemen                                                                                                                  | ted: Read as '0                                                                       | 3              |                   |                  |                 |        |  |  |  |  |  |

| bit 3         |                                                                                                                             | Generator Inter                                                                       |                | us bit            |                  |                 |        |  |  |  |  |  |

|               | •                                                                                                                           | request has occ                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 2         | •                                                                                                                           | request has not                                                                       |                | a hit             |                  |                 |        |  |  |  |  |  |

| DIL Z         |                                                                                                                             | RT2 Error Interru                                                                     |                | S DIL             |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has not                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

| bit 1         | U1ERIF: UAF                                                                                                                 | RT1 Error Interru                                                                     | upt Flag Statu | s bit             |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | request has occ<br>request has not                                                    |                |                   |                  |                 |        |  |  |  |  |  |

| bit 0         | <ul> <li>0 = Interrupt request has not occurred</li> <li>CCP2IF: SCCP2 Capture/Compare Interrupt Flag Status bit</li> </ul> |                                                                                       |                |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | equest has occu                                                                       | • •            |                   |                  |                 |        |  |  |  |  |  |

|               |                                                                                                                             | equest has not o                                                                      |                |                   |                  |                 |        |  |  |  |  |  |

### REGISTER 8-10: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0         | U-0          | U-0                                  | U-0              | U-0               | U-0              | U-0             | U-0    |  |  |  |  |  |

|-------------|--------------|--------------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| _           |              |                                      | —                | —                 | _                | —               | —      |  |  |  |  |  |

| it 15       |              |                                      |                  |                   |                  |                 | bit 8  |  |  |  |  |  |

|             |              |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| U-0         | U-0          | R/W-0                                | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| —           | —            | JTAGIF                               | U6ERIF           | U6TXIF            | U6RXIF           | U5ERIF          | U5TXIF |  |  |  |  |  |

| oit 7       |              |                                      |                  |                   |                  |                 | bit (  |  |  |  |  |  |

| <u> </u>    |              |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| Legend:     | -1           |                                      | 1. 14            |                   |                  |                 |        |  |  |  |  |  |

| R = Readat  |              | W = Writable                         |                  | •                 | nented bit, read |                 |        |  |  |  |  |  |

| n = Value a | at POR       | '1' = Bit is set                     |                  | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |  |  |  |  |  |

| bit 15-6    | Unimpleme    | nted: Read as '                      | ٥'               |                   |                  |                 |        |  |  |  |  |  |

| it 5        | •            | AG Controller In                     |                  | atus hit          |                  |                 |        |  |  |  |  |  |

| 511 5       |              | t request has or                     |                  |                   |                  |                 |        |  |  |  |  |  |

|             |              | t request has no                     |                  |                   |                  |                 |        |  |  |  |  |  |

| oit 4       | U6ERIF: UA   | RT6 Error Inter                      | rupt Flag Status | s bit             |                  |                 |        |  |  |  |  |  |

|             |              | t request has o                      |                  |                   |                  |                 |        |  |  |  |  |  |

|             | •            | t request has no                     |                  |                   |                  |                 |        |  |  |  |  |  |

| oit 3       |              | RT6 Transmitte                       |                  | Status bit        |                  |                 |        |  |  |  |  |  |

|             |              | t request has or<br>t request has no |                  |                   |                  |                 |        |  |  |  |  |  |

| oit 2       | •            | RT6 Receiver li                      |                  | tatus bit         |                  |                 |        |  |  |  |  |  |

| 511 2       |              | t request has or                     |                  |                   |                  |                 |        |  |  |  |  |  |

|             |              | t request has no                     |                  |                   |                  |                 |        |  |  |  |  |  |

| oit 1       | U5ERIF: UA   | RT5 Error Inter                      | rupt Flag Status | s bit             |                  |                 |        |  |  |  |  |  |

|             |              | t request has o                      |                  |                   |                  |                 |        |  |  |  |  |  |

|             | 0 = Interrup | t request has no                     | ot occurred      |                   |                  |                 |        |  |  |  |  |  |

| oit O       | U5TXIF: UA   | RT5 Transmitte                       | r Interrupt Flag | Status bit        |                  |                 |        |  |  |  |  |  |

|             |              | 1 = Interrupt request has occurred   |                  |                   |                  |                 |        |  |  |  |  |  |

|             | 0 = Interrup | t request has no                     | ot occurred      |                   |                  |                 |        |  |  |  |  |  |

#### REGISTER 8-13: IFS7: INTERRUPT FLAG STATUS REGISTER 7

#### REGISTER 10-3: RCON2: RESET AND SYSTEM CONTROL REGISTER 2

| U-0            | U-0                                                                   | U-0                                                                                                                                           | U-0                                                                             | U-0                                              | U-0                     | U-0                    | U-0                 |

|----------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|------------------------|---------------------|

| _              | _                                                                     | —                                                                                                                                             | _                                                                               | _                                                |                         | —                      | _                   |

| bit 15         |                                                                       | · ·                                                                                                                                           |                                                                                 |                                                  |                         |                        | bit 8               |

|                |                                                                       |                                                                                                                                               |                                                                                 |                                                  |                         |                        |                     |

| U-0            | U-0                                                                   | U-0                                                                                                                                           | r-0                                                                             | R/CO-1                                           | R/CO-1                  | R/CO-1                 | R/CO-0              |

| —              | _                                                                     | —                                                                                                                                             | —                                                                               | VDDBOR <sup>(1)</sup>                            | VDDPOR <sup>(1,2)</sup> | VBPOR <sup>(1,3)</sup> | VBAT <sup>(1)</sup> |

| bit 7          |                                                                       |                                                                                                                                               |                                                                                 |                                                  |                         |                        | bit C               |

|                |                                                                       |                                                                                                                                               |                                                                                 |                                                  |                         |                        |                     |

| Legend:        |                                                                       | r = Reserved b                                                                                                                                | pit                                                                             | CO = Clearab                                     | le Only bit             |                        |                     |

| R = Reada      | ble bit                                                               | W = Writable b                                                                                                                                | pit                                                                             | U = Unimplen                                     | nented bit, read        | as '0'                 |                     |

| -n = Value     | x = Bit is unkno                                                      | own                                                                                                                                           |                                                                                 |                                                  |                         |                        |                     |

| bit 3<br>bit 2 | 1 = A VDD E<br>0 = A VDD E<br>VDDPOR: V<br>1 = A VDD F                | /DD Brown-out Reset<br>Brown-out Reset<br>Brown-out Reset<br>/DD Power-on Re<br>Power-on Reset P<br>Power-on Reset P                          | has occurred<br>has not occur<br>set Flag bit <sup>(1,2</sup><br>has occurred ( | (set by hardwa<br>red<br>2)<br>set by hardwar    | ,                       |                        |                     |

| bit 1<br>bit 0 | 1 = A VBAT<br>Sleep s<br>0 = A VBAT<br><b>VBAT:</b> VBAT<br>1 = A POR | AT Power-on Res<br>POR has occurr<br>emaphore retenti<br>POR has not occ<br>Flag bit <sup>(1)</sup><br>exit has occurrec<br>exit from VBAT ha | ed (no battery<br>on level, set b<br>curred                                     | y connected to<br>by hardware)<br>was applied to |                         |                        | ·                   |

| 2:             |                                                                       | hardware only; it<br>VDD POR. Settin                                                                                                          | g the POR bit                                                                   | (RCON<0>) in                                     | dicates a VCOR          |                        |                     |

3: This bit is set when the device is originally powered up, even if power is present on VBAT.

## TABLE 11-8: PORTG REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | ange   |    |        |          |    | Bits |    |                |             |        |   |       |        |               |            |        |        |

|------------------|--------|----|--------|----------|----|------|----|----------------|-------------|--------|---|-------|--------|---------------|------------|--------|--------|

| Register<br>Name | Bit Ra | 15 | 14     | 13       | 12 | 11   | 10 | 9              | 8           | 7      | 6 | 5     | 4      | 3             | 2          | 1      | 0      |

| ANSG             | 15:0   |    | ANSG<  | <15:12>  |    | —    | —  |                | ANSG<9:6> — |        |   |       | _      | — — ANSG<1:0> |            |        | G<1:0> |

| TRISG            | 15:0   |    | TRISG  | <15:12>  |    | —    | —  |                | TRISG       | <9:6>  |   | _     | _      |               | TRISG      | i<3:0> |        |

| PORTG            | 15:0   |    | PORTG  | <15:12>  |    | _    | _  |                | PORTO       | 6<9:6> |   | _     | _      |               | PORTG<3:0> |        |        |

| LATG             | 15:0   |    | LATG<  | :15:12>  |    | _    | _  | LATG<9:6>      |             |        | _ | _     |        | LATG          | <3:0>      |        |        |

| ODCG             | 15:0   |    | ODCG<  | <15:12>  |    | —    | —  |                | ODCG<9:6>   |        |   | _     | _      |               | ODCG       | i<3:0> |        |

| IOCPG            | 15:0   |    | IOCPG- | <15:12>  |    | _    | _  |                | IOCPG       | <9:6>  |   | _     | _      |               | IOCPG<3:0> |        |        |

| IOCNG            | 15:0   |    | IOCNG- | <15:12>  |    | _    | _  |                | IOCNG       | <9:6>  |   | _     | _      | IOCNG<3:0>    |            |        |        |

| IOCFG            | 15:0   |    | IOCFG. | <15:12>  |    | _    | _  | IOCFG<9:6> — — |             |        |   | IOCFG | 6<3:0> |               |            |        |        |

| IOCPUG           | 15:0   |    | IOCPUG | 6<15:12> |    | _    | _  |                | IOCPU       | G<9:6> |   | _     | _      |               | IOCPU      | G<3:0> |        |

| IOCPDG           | 15:0   |    | IOCPDG | 6<15:12> |    | _    | _  |                | IOCPDO      | 3<9:6> |   | —     | _      |               | IOCPD      | G<3:0> |        |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

### TABLE 11-9: PORTH REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | Range  |    |                |    |    |    |    |   |         | Bits  |   |   |   |      |       |   |   |

|------------------|--------|----|----------------|----|----|----|----|---|---------|-------|---|---|---|------|-------|---|---|

| Register<br>Name | Bit Ra | 15 | 14             | 13 | 12 | 11 | 10 | 9 | 8       | 7     | 6 | 5 | 4 | 3    | 2     | 1 | 0 |

| ANSH             | 15:0   |    |                | _  |    |    | _  |   |         | —     |   |   |   | ANSH | <4:1> |   | _ |

| TRISH            | 15:0   |    |                |    |    |    |    |   | TRISH<1 | 5:1>  |   |   |   |      |       |   | _ |

| PORTH            | 15:0   |    |                |    |    |    |    |   | PORTH<  | 15:1> |   |   |   |      |       |   | _ |

| LATH             | 15:0   |    |                |    |    |    |    |   | LATH<1  | 5:1>  |   |   |   |      |       |   | _ |

| ODCH             | 15:0   |    |                |    |    |    |    |   | ODCH<1  | 5:1>  |   |   |   |      |       |   | _ |

| IOCPH            | 15:0   |    |                |    |    |    |    |   | IOCPH<1 | 5:1>  |   |   |   |      |       |   | _ |

| IOCNH            | 15:0   |    |                |    |    |    |    |   | IOCNH<1 | 5:1>  |   |   |   |      |       |   | _ |

| IOCFH            | 15:0   |    | IOCFH<15:1>    |    |    |    |    |   |         |       |   |   | _ |      |       |   |   |

| IOCPUH           | 15:0   |    | IOCPUH<15:1> — |    |    |    |    |   |         |       |   |   |   | _    |       |   |   |

| IOCPDH           | 15:0   |    |                |    |    |    |    |   | IOCPDH< | 15:1> |   |   |   |      |       |   | — |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

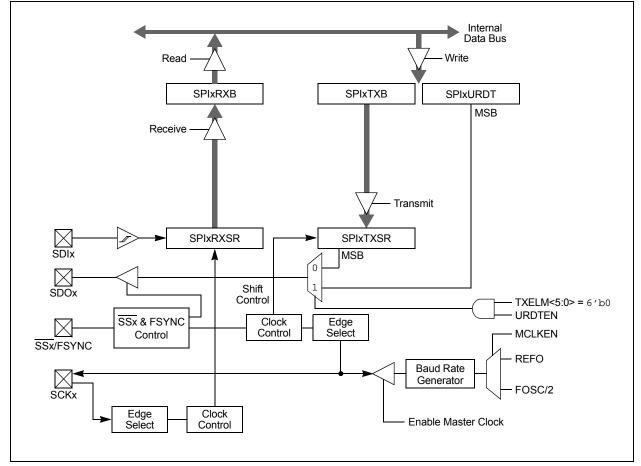

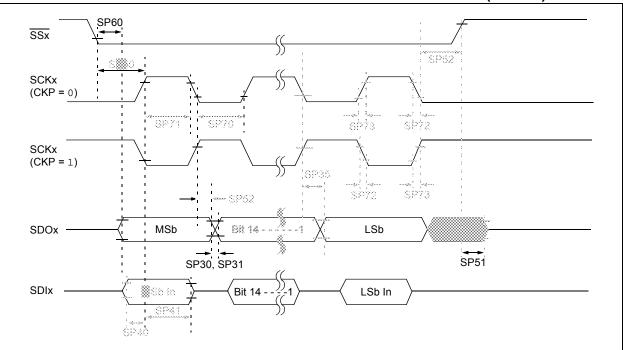

To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

### FIGURE 17-1: SPIx MODULE BLOCK DIAGRAM (STANDARD MODE)

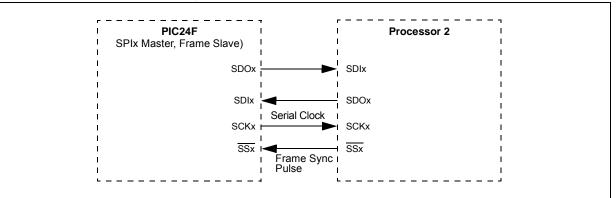

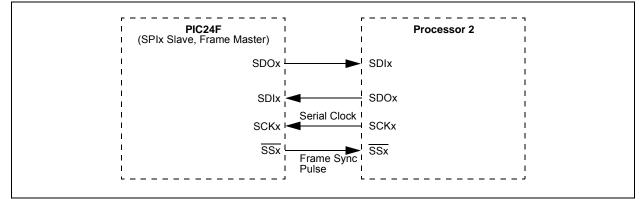

FIGURE 17-6: SPIX MASTER, FRAME SLAVE CONNECTION DIAGRAM

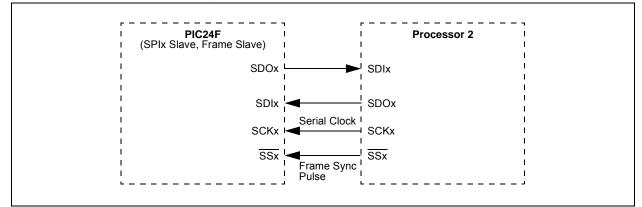

#### FIGURE 17-7: SPIx SLAVE, FRAME MASTER CONNECTION DIAGRAM

#### FIGURE 17-8: SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

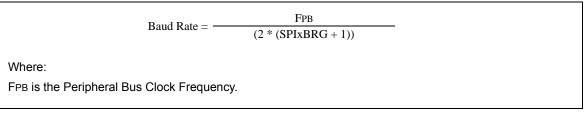

#### EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

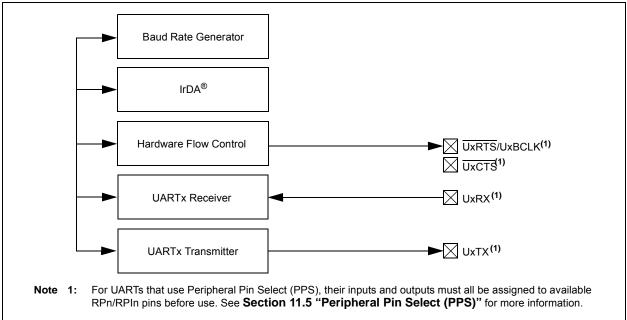

### 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ256GA412/GB412 family devices are equipped with six UART modules, referred to as UART1 through UART6.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from up to 2.5 Mbps and Down to 38 Hz at 40 MIPS in 16x Mode

- Baud Rates Range from up to 10 Mbps and Down to 152 Hz at 40 MIPS in 4x Mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Mode with Address Detect (9<sup>th</sup> bit = 1)

- Separate Transmit and Receive Interrupts

- Loopback Mode for Diagnostic Support

- · Polarity Control for Transmit and Receive Lines

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 19-1. The UARTx module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

Asynchronous Receiver

Note: Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTAL" might refer to the Status Low register for either UART1, UART2, UART3 or UART4.

#### REGISTER 21-9: PADCON: PAD CONFIGURATION CONTROL REGISTER

| R/W-0         | U-0   | U-0              | U-0 | U-0                                     | U-0              | U-0      | U-0   |  |  |

|---------------|-------|------------------|-----|-----------------------------------------|------------------|----------|-------|--|--|

| IOCON         |       | _                |     |                                         |                  | _        | —     |  |  |

| bit 15        |       |                  |     |                                         |                  | •        | bit 8 |  |  |

|               |       |                  |     |                                         |                  |          |       |  |  |

| U-0           | U-0   | U-0              | U-0 | U-0                                     | U-0              | U-0      | R/W-0 |  |  |

| _             | _     | —                | _   |                                         | _                | —        | PMTTL |  |  |

| bit 7         |       |                  |     |                                         | •                |          | bit 0 |  |  |

|               |       |                  |     |                                         |                  |          |       |  |  |

| Legend:       |       |                  |     |                                         |                  |          |       |  |  |

| R = Readable  | e bit | W = Writable t   | bit | U = Unimplem                            | nented bit, read | d as '0' |       |  |  |

| -n = Value at | POR   | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

bit 15 **IOCON:** Interrupt-on-Change Enable bit

Not used by the EPMP; see Register 11-1 for definition.

bit 14-1 Unimplemented: Read as '0'

bit 0 PMTTL: EPMP Module TTL Input Buffer Select bit

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

### 22.1 Registers

The LCD Controller has up to 40 registers:

- LCD Control Register (LCDCON)

- LCD Charge Pump Control Register (LCDREG)

- LCD Phase Register (LCDPS)

- LCD Voltage Ladder Control Register (LCDREF)

- Four LCD Segment Enable Registers (LCDSE3:LCDSE0)

- Up to 32 LCD Data Registers (LCDDATA31:LCDDATA0)

### REGISTER 22-1: LCDCON: LCD CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|-----|-----|-----|-----|-------|

| LCDEN  | —   | LCDSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |         |     |     |     |     | bit 8 |

|        |     |         |     |     |     |     |       |

| U-0   | R/W-0 | R/C-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | SLPEN | WERR  | CS1   | CS0   | LMUX2 | LMUX1 | LMUX0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           | C = Clearable bit                                   |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15   | LCDEN: LCD Driver Enable bit<br>1 = LCD driver module is enabled<br>0 = LCD driver module is disabled                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | Unimplemented: Read as '0'                                                                                                                       |

| bit 13   | LCDSIDL: Stop LCD Drive in CPU Idle Mode Control bit                                                                                             |

|          | <ul> <li>1 = LCD driver halts in CPU Idle mode</li> <li>0 = LCD driver continues to operate in CPU Idle mode</li> </ul>                          |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                       |

| bit 6    | SLPEN: LCD Driver Enable in Sleep Mode bit                                                                                                       |

|          | <ul> <li>1 = LCD driver module is disabled in Sleep mode</li> <li>0 = LCD driver module is enabled in Sleep mode</li> </ul>                      |

| bit 5    | WERR: LCD Write Failed Error bit                                                                                                                 |

|          | <ul> <li>1 = LCDDATAx register is written while WA (LCDPS&lt;4&gt;) = 0 (must be cleared in software)</li> <li>0 = No LCD write error</li> </ul> |

| bit 4-3  | CS<1:0>: Clock Source Select bits                                                                                                                |

|          | 1x = SOSC<br>01 = LPRC<br>00 = FRC                                                                                                               |

| hit 2-0  | I MIX < 2:0>. I CD Commons Select hits                                                                                                           |

#### bit 2-0 LMUX<2:0>: LCD Commons Select bits

| LMUX<2:0> | .MUX<2:0> Multiplex                  |            |

|-----------|--------------------------------------|------------|

| 111       | 11 1/8 MUX (COM<7:0>) <sup>(1)</sup> |            |

| 110       | 1/7 MUX (COM<6:0>) <sup>(1)</sup>    | 1/3        |

| 101       | 1/6 MUX (COM<5:0>) <sup>(1)</sup>    | 1/3        |

| 100       | 1/5 MUX (COM<4:0>) <sup>(1)</sup>    | 1/3        |

| 011       | 1/4 MUX (COM<3:0>)                   | 1/3        |

| 010       | 1/3 MUX (COM<2:0>)                   | 1/2 or 1/3 |

| 001       | 1/2 MUX (COM<1:0>)                   | 1/2 or 1/3 |

| 000       | Static (COM0)                        | Static     |

**Note 1:** On 64-pin and 100-pin devices, COM4 through COM7 also have Segment functionality. If the COM is enabled in multiplexing, the Segment will not be available on that pin.

#### 24.3 Power Control

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current lower power mode.

To use this feature:

- 1. Enable the RTCC (RTCEN = 1).

- 2. Set the PWCEN bit (RTCCON1L<10>).

- 3. Configure the RTCC pin to drive the PWC control signal (RTCOE = 1 and OUTSEL<2:0> = 011).

The polarity of the PWC control signal is selected by the PWCPOL bit (RTCCON1L<9>). An active-low or active-high signal may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin, in order to drive the ground pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

Once the RTCC and PWC are enabled and running, the PWC logic will generate a control output and a sample gate output. The control output is driven out on the RTCC pin (when RTCOE = 1 and OUTSEL<2:0> = 011) and is used to power-up or power-down the device, as described above.

Once the control output is asserted, the Stability Window begins, in which the external device is given enough time to power-up and provide a stable output.

Once the output is stable, the RTCC provides a sample gate during the Sample Window. The use of this sample gate depends on the external device being used, but typically, it is used to mask out one or more wake-up signals from the external device.

Finally, both the Stability and the Sample Windows close after the expiration of the Sample Window, and the external device is powered down.

#### 24.3.1 POWER CONTROL CLOCK SOURCE

The Stability and Sample Windows are controlled by the PWCSAMP<7:0> and PWCSTAB<7:0> bits field in the RTCCON3L register (RTCCON3L<15:8> and <7:0>, respectively). As both the Stability and Sample Windows are defined in terms of the RTCC clock, their absolute values vary by the value of the PWC clock base period. The 8-bit magnitude of PWCSTABx and PWCSAMPx allows for a window size of 0 to 255 clock periods.

The period of the PWC clock can also be adjusted with a 1:1, 1:16, 1:64 or 1:256 prescaler, determined by the PWCPS<1:0> bits (RTCCON2L<7:6>).

In addition, certain values for the PWCSTABx and PWCSAMPx fields have specific control meanings in determining power control operations. If either bit field is 00h, the corresponding window is inactive. In addition, if the PWCSTABx field is FFh, the Stability Window remains active continuously, even if power control is disabled.

### 24.4 Event Timestamping

The RTCC includes two sets of Timestamp registers that may be used for the capture of Time and Date register values when an external input signal is received. The RTCC triggers the timestamps for two events:

- For Timestamp A, a falling edge on the TMPR pin

- For Timestamp B, when the devices transition from VDD to VBAT power

A Timestamp A event can be triggered while running the device in VBAT mode if the TMPR pin is pulled up to VBAT.

#### 24.4.1 TIMESTAMP OPERATION

The event input is enabled for timestamping using the TSAEN bit (RTCCON1L<0>). When the timestamp event occurs, the present time and date values are stored in the TSATIMEL/H and TSADATEL/H registers, the TSAEVT status bit (RTCSTATL<3>) becomes set and an RTCC interrupt occurs. A new timestamp capture event cannot occur until the user clears the TSAEVT status bit.

#### 24.4.2 MANUAL TIMESTAMP

The current time and date may be captured in the TSATIMEL/H and TSADATEL/H registers by writing a '1' to the TSAEVT bit location while the timestamp functionality is enabled (TSAEN = 1). This write will not set the TSAEVT bit, but it will initiate a timestamp capture. The TSAEVT bit will be set when the capture operation is complete. The user must poll the TSAEVT bit to determine when the capture operation is complete.

After the Timestamp registers have been read, the TSAEVT bit should be cleared to allow further hardware or software timestamp capture events.

| REGISTER 2    | 24-2: RTCC                                                 | ON1H: RTCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CONTROL         | <b>REGISTER</b> 1 | I (HIGH)         |                 |                |  |  |  |

|---------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|----------------|--|--|--|