Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 102                                                                            |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

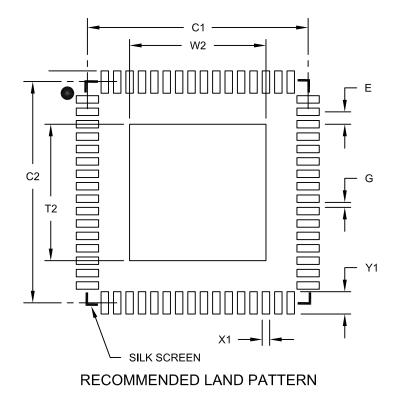

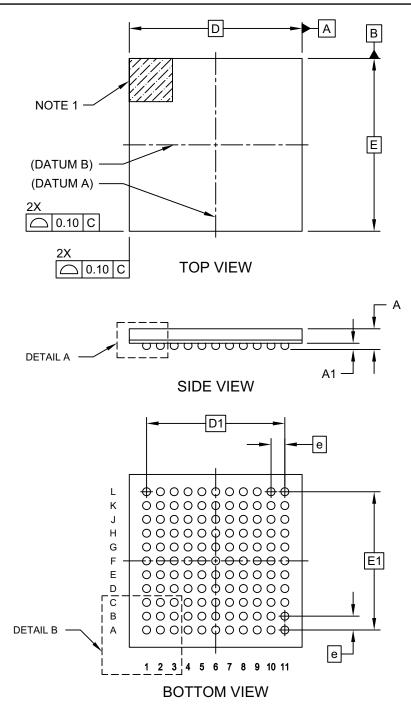

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga412-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ256GA412/GB412 FAMILY: 100-PIN

| Feetures                                                        | PIC24FJXXXGA/GB410 |               |                                                            |                |                |        |  |  |  |

|-----------------------------------------------------------------|--------------------|---------------|------------------------------------------------------------|----------------|----------------|--------|--|--|--|

| Features                                                        | 64GA               | 128GA         | 256GA                                                      | 64GB           | 128GB          | 256GB  |  |  |  |

| Operating Frequency                                             |                    |               | DC – 3                                                     | 32 MHz         |                |        |  |  |  |

| Program Memory (bytes)                                          | 64K                | 128K          | 256K                                                       | 64K            | 128K           | 256K   |  |  |  |

| Program Memory (instructions)                                   | 22,016             | 44,032        | 88,064                                                     | 22,016         | 44,032         | 88,064 |  |  |  |

| Data Memory (bytes)                                             | 8K                 | 8K 16K 8K 16  |                                                            |                |                |        |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                  |                    |               | 113 (1                                                     | 107/6)         |                |        |  |  |  |

| I/O Ports                                                       |                    |               | Ports A, B,                                                | C, D, E, F, G  |                |        |  |  |  |

| Total I/O Pins                                                  |                    | 85            |                                                            |                | 84             |        |  |  |  |

| Remappable Pins                                                 |                    |               | 44 (32 l/Os,                                               | 12 input only) |                |        |  |  |  |

| Timers:                                                         |                    |               |                                                            |                |                |        |  |  |  |

| Total Number (16-bit)                                           |                    |               | 19                                                         | (1,2)          |                |        |  |  |  |

| 32-Bit (from paired 16-bit timers)                              |                    |               |                                                            | 9              |                |        |  |  |  |

| Input Capture w/Timer Channels                                  |                    |               |                                                            | (2)            |                |        |  |  |  |

| Output Compare/PWM Channels                                     |                    |               | 6                                                          | (2)            |                |        |  |  |  |

| Capture/Compare/PWM/Timer:                                      |                    |               |                                                            |                |                |        |  |  |  |

| Single Output (SCCP)                                            |                    |               | 6                                                          | (2)            |                |        |  |  |  |

| Multiple Output (MCCP)                                          |                    |               | 1                                                          | (2)            |                |        |  |  |  |

| Serial Communications:                                          |                    |               |                                                            |                |                |        |  |  |  |

| UART                                                            |                    |               | 6                                                          | (2)            |                |        |  |  |  |

| SPI (3-wire/4-wire)                                             |                    |               | 4                                                          | (2)            |                |        |  |  |  |

| l <sup>2</sup> C                                                |                    |               | :                                                          | 3              |                |        |  |  |  |

| USB On-The-Go                                                   |                    | No            |                                                            |                | Yes            |        |  |  |  |

| Cryptographic Engine                                            |                    |               | Y                                                          | es             |                |        |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                           |                    |               | Y                                                          | es             |                |        |  |  |  |

| 10/12-Bit Analog-to-Digital<br>Converter (A/D) (input channels) |                    |               | 2                                                          | 4              |                |        |  |  |  |

| Digital-to-Analog Converter<br>(DAC)                            |                    |               |                                                            | 1              |                |        |  |  |  |

| Analog Comparators                                              |                    |               |                                                            | 3              |                |        |  |  |  |

| CTMU Interface                                                  |                    |               | Y                                                          | es             |                |        |  |  |  |

| LCD Controller (available pixels)                               |                    |               | 512 (64 SE                                                 | G x 8 COM)     |                |        |  |  |  |

| JTAG Boundary Scan                                              |                    |               | Y                                                          | es             |                |        |  |  |  |

| Resets (and delays)                                             | C                  | MCLR, WI      | POR, VBAT F<br>DT, Illegal Opc<br>Traps, Config<br>(OST, P | ode, REPEAT    | Instruction,   | n,     |  |  |  |

| Instruction Set                                                 | 7                  | 7 Base Instru | ctions, Multiple                                           | e Addressing N | Node Variation | าร     |  |  |  |

| Packages                                                        |                    |               | 100-Pii                                                    | n TQFP         |                |        |  |  |  |

**Note 1:** Includes the Timer modes of the SCCP and MCCP modules.

**2:** Some instantiations of these modules are only available through remappable pins.

## 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU with Extended Data Space (EDS)" (DS39732). The information in this data sheet supersedes the information in the FRM.

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16<sup>th</sup> Working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The lower 32 Kbytes of the Data Space (DS) can be accessed linearly. The upper 32 Kbytes of the Data Space are referred to as Extended Data Space to which the extended data RAM, EPMP memory space or program memory can be mapped.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs. The core supports Inherent (no operand), Relative, Literal and Memory Direct Addressing modes, along with three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit x 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit x 16-bit or 8-bit x 8-bit, integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

### 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions.

A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory-mapped.

| U-0              | R/W-1                                                             | R/W-0                                                                      | R/W-0                   | U-0            | R/W-1             | R/W-0           | R/W-0      |  |  |  |

|------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|----------------|-------------------|-----------------|------------|--|--|--|

| _                | CRYROLLIP2                                                        | CRYROLLIP1                                                                 | CRYROLLIP0              | _              | CRYFREEIP2        | CRYFREEIP1      | CRYFREEIPO |  |  |  |

| bit 15           |                                                                   |                                                                            |                         |                |                   |                 | bit 8      |  |  |  |

| U-0              | R/W-1                                                             | R/W-0                                                                      | R/W-0                   | U-0            | R/W-1             | R/W-0           | R/W-0      |  |  |  |

|                  | SPI2TXIP2                                                         | SPI2TXIP1                                                                  | SPI2TXIP0               | 0-0            | SPI2IP2           | SPI2IP1         | SPI2IP0    |  |  |  |

| bit 7            | 011217(112                                                        | 011217/111                                                                 |                         |                | 0112112           |                 | bit (      |  |  |  |

|                  |                                                                   |                                                                            |                         |                |                   |                 | bit t      |  |  |  |

| Legend:          |                                                                   |                                                                            |                         |                |                   |                 |            |  |  |  |

| R = Readab       | ole bit                                                           | W = Writable b                                                             | oit                     | U = Unimple    | emented bit, read | l as '0'        |            |  |  |  |

| -n = Value a     | it POR                                                            | '1' = Bit is set                                                           |                         | '0' = Bit is c | leared            | x = Bit is unkr | nown       |  |  |  |

|                  |                                                                   |                                                                            |                         |                |                   |                 |            |  |  |  |

| bit 15           | -                                                                 | ted: Read as '0                                                            |                         |                |                   |                 |            |  |  |  |

| bit 14-12        |                                                                   | <2:0>: Cryptogr                                                            | •                       | •              | ority bits        |                 |            |  |  |  |

|                  | 111 = Interru                                                     | pt is Priority 7 (                                                         | highest priority        | interrupt)     |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | 001 = Interru                                                     | pt is Priority 1                                                           |                         |                |                   |                 |            |  |  |  |

|                  | 000 = Interru                                                     | pt source is dis                                                           | abled                   |                |                   |                 |            |  |  |  |

| bit 11           | Unimplement                                                       | ted: Read as 'o                                                            | )'                      |                |                   |                 |            |  |  |  |

| bit 10-8         | CRYFREEIP<2:0>: Cryptographic Buffer Free Interrupt Priority bits |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | 111 = Interru                                                     | pt is Priority 7 (                                                         | highest priority        | interrupt)     |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | 001 = Interru                                                     | pt is Priority 1                                                           |                         |                |                   |                 |            |  |  |  |

|                  |                                                                   | pt source is dis                                                           | abled                   |                |                   |                 |            |  |  |  |

| bit 7            | Unimplement                                                       | ted: Read as '0                                                            | )'                      |                |                   |                 |            |  |  |  |

| bit 6-4          | SPI2TXIP<2:0                                                      | 0>: SPI2 Transi                                                            | mit Interrupt Pr        | iority bits    |                   |                 |            |  |  |  |

|                  | 111 = Interru                                                     | pt is Priority 7 (                                                         | highest priority        | interrupt)     |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | •                                                                 |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | •                                                                 | ntic Drievity (                                                            |                         |                |                   |                 |            |  |  |  |

|                  |                                                                   |                                                                            |                         |                |                   |                 |            |  |  |  |

|                  | 001 = Interru<br>000 = Interru                                    |                                                                            | abled                   |                |                   |                 |            |  |  |  |

| bit 3            | 000 = Interru                                                     | pt is Phonty 1<br>pt source is dis<br><b>ted:</b> Read as '0               |                         |                |                   |                 |            |  |  |  |

|                  | 000 = Interru                                                     | pt source is dis<br>ted: Read as '0                                        | )'                      | v bits         |                   |                 |            |  |  |  |

| bit 3<br>bit 2-0 | 000 = Interru<br>Unimplemen<br>SPI2IP<2:0>:                       | pt source is dis<br>ted: Read as '0<br>SPI2 General                        | )'<br>Interrupt Priorit | -              |                   |                 |            |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SPI2IP<2:0>:                       | pt source is dis<br>ted: Read as '0                                        | )'<br>Interrupt Priorit | -              |                   |                 |            |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SPI2IP<2:0>:                       | pt source is dis<br>ted: Read as '0<br>SPI2 General                        | )'<br>Interrupt Priorit | -              |                   |                 |            |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SPI2IP<2:0>:                       | pt source is dis<br>ted: Read as 'c<br>SPI2 General<br>ot is Priority 7 (f | )'<br>Interrupt Priorit | -              |                   |                 |            |  |  |  |

| U-0          | U-0                        | U-0                | U-0               | U-0                                | R/W-1  | R/W-0              | R/W-0  |  |  |

|--------------|----------------------------|--------------------|-------------------|------------------------------------|--------|--------------------|--------|--|--|

| _            | —                          | —                  |                   | —                                  | FSTIP2 | FSTIP1             | FSTIP0 |  |  |

| bit 15       | 15                         |                    |                   |                                    |        |                    | bit 8  |  |  |

|              |                            |                    |                   |                                    |        |                    |        |  |  |

| U-0          | U-0                        | U-0 U-0            |                   | U-0                                | U-0    | U-0                | U-0    |  |  |

| —            | —                          |                    |                   | —                                  | —      | —                  | —      |  |  |

| bit 7        |                            |                    |                   |                                    |        |                    | bit 0  |  |  |

|              |                            |                    |                   |                                    |        |                    |        |  |  |

| Legend:      |                            |                    |                   |                                    |        |                    |        |  |  |

| R = Readab   | le bit                     | W = Writable       | bit               | U = Unimplemented bit, read as '0' |        |                    |        |  |  |

| -n = Value a | It POR                     | '1' = Bit is set   |                   | '0' = Bit is clea                  | ared   | x = Bit is unknown |        |  |  |

|              |                            |                    |                   |                                    |        |                    |        |  |  |

| bit 15-11    | Unimplement                | ted: Read as '     | 0'                |                                    |        |                    |        |  |  |

| bit 10-8     | FSTIP<2:0>:                | FRC Self-Tune      | e Interrupt Prior | rity bits                          |        |                    |        |  |  |

|              | 111 = Interru              | pt is Priority 7 ( | highest priority  | / interrupt)                       |        |                    |        |  |  |

|              | •                          |                    |                   |                                    |        |                    |        |  |  |

|              | •                          |                    |                   |                                    |        |                    |        |  |  |

|              | •                          |                    |                   |                                    |        |                    |        |  |  |

|              | 001 = Interru              |                    | ablad             |                                    |        |                    |        |  |  |

|              |                            | pt source is dis   |                   |                                    |        |                    |        |  |  |

| bit 7-0      | Unimplemented: Read as '0' |                    |                   |                                    |        |                    |        |  |  |

|              | omplomon                   |                    | 0                 |                                    |        |                    |        |  |  |

#### REGISTER 8-48: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| U-0          | U-0                           | U-0                          | U-0             | U-0               | U-0             | U-0            | U-0   |

|--------------|-------------------------------|------------------------------|-----------------|-------------------|-----------------|----------------|-------|

| _            | _                             | —                            | —               | —                 | _               | _              |       |

| bit 15       | ·                             |                              |                 |                   |                 |                | bit 8 |

|              |                               |                              |                 |                   | <b>D</b> #44.0  |                |       |

| R/W-0        | R/W-0                         | R/W-0<br>CLC4MD              | R/W-0<br>CLC3MD | R/W-0<br>CLC2MD   | R/W-0<br>CLC1MD | U-0            | R/W-0 |

| U6MD         | U5MD                          | CRYMD                        |                 |                   |                 |                |       |

| bit 7        |                               |                              |                 |                   |                 |                | bit C |

| Legend:      |                               |                              |                 |                   |                 |                |       |

| R = Readat   | ole bit                       | W = Writable I               | oit             | U = Unimplem      | ented bit, read | d as '0'       |       |

| -n = Value a | at POR                        | '1' = Bit is set             |                 | '0' = Bit is clea | ared            | x = Bit is unk | nown  |

|              |                               |                              |                 |                   |                 |                |       |

| bit 15-8     | Unimplemen                    | ted: Read as 'o              | )'              |                   |                 |                |       |

| bit 7        | U6MD: UART                    | 6 Module Disal               | ole bit         |                   |                 |                |       |

|              | 1 = Module is                 |                              |                 |                   |                 |                |       |

|              |                               | ower and clock               |                 | enabled           |                 |                |       |

| bit 6        |                               | 5 Module Disal               | ole bit         |                   |                 |                |       |

|              | 1 = Module is<br>0 = Module p | s disabled<br>ower and clock | sources are e   | enabled           |                 |                |       |

| bit 5        |                               | C4 Module Dis                |                 |                   |                 |                |       |

|              | 1 = Module is                 |                              |                 |                   |                 |                |       |

|              | 0 = Module p                  | ower and clock               | sources are e   | enabled           |                 |                |       |

| bit 4        | CLC3MD: CL                    | C3 Module Dis                | able bit        |                   |                 |                |       |

|              | 1 = Module is                 |                              |                 |                   |                 |                |       |

|              | -                             | ower and clock               |                 | enabled           |                 |                |       |

| bit 3        |                               | C2 Module Dis                | able bit        |                   |                 |                |       |

|              | 1 = Module is                 |                              |                 | nablad            |                 |                |       |

| L:1 0        | -                             | ower and clock               |                 | enabled           |                 |                |       |

| bit 2        | 1 = Module is                 | C1 Module Dis                | able bit        |                   |                 |                |       |

|              |                               | ower and clock               | sources are e   | enabled           |                 |                |       |

| bit 1        |                               | ted: Read as '0              |                 |                   |                 |                |       |

| bit 0        | -                             | otographic Engi              |                 |                   |                 |                |       |

|              | 1 = Module is                 |                              |                 |                   |                 |                |       |

|              |                               |                              |                 |                   |                 |                |       |

#### REGISTER 10-11: PMD8: PERIPHERAL MODULE DISABLE REGISTER 8

| U-0             | U-0                                | R/W-1  | R/W-1  | R/W-1 R/W-1 R/W-1                       |                 | R/W-1    |        |

|-----------------|------------------------------------|--------|--------|-----------------------------------------|-----------------|----------|--------|

| —               | —                                  | SCK1R5 | SCK1R4 | SCK1R3 SCK1R2 SCK1R                     |                 | SCK1R1   | SCK1R0 |

| bit 15          |                                    |        |        |                                         |                 | bit 8    |        |

|                 |                                    |        |        |                                         |                 |          |        |

| U-0             | U-0                                | R/W-1  | R/W-1  | R/W-1                                   | R/W-1           | R/W-1    | R/W-1  |

| —               | —                                  | SDI1R5 | SDI1R4 | SDI1R3                                  | SDI1R2          | SDI1R1   | SDI1R0 |

| bit 7           |                                    |        |        |                                         |                 |          | bit 0  |

|                 |                                    |        |        |                                         |                 |          |        |

| Legend:         |                                    |        |        |                                         |                 |          |        |

| R = Readable    | R = Readable bit W = Writable bit  |        |        | U = Unimplem                            | ented bit, read | l as '0' |        |

| -n = Value at F | -n = Value at POR '1' = Bit is set |        |        | '0' = Bit is cleared x = Bit is unknown |                 |          |        |

| •               |                                    |        |        |                                         |                 |          |        |

#### REGISTER 11-15: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK1R<5:0>: Assign SPI1 Clock Input (SCK1IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI1R<5:0>: Assign SPI1 Data Input (SDI1) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 11-16: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U3CTSR5 | U3CTSR4 | U3CTSR3 | U3CTSR2 | U3CTSR1 | U3CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3CTSR<5:0>: Assign UART3 Clear-to-Send (U3CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS1R<5:0>: Assign SPI1 Slave Select Input (SS1IN) to Corresponding RPn or RPIn Pin bits

### 14.5 Auxiliary Output

The MCCPx and SCCPx modules have an auxiliary (secondary) output that provides other peripherals access to internal module signals. The auxiliary output is intended to connect to other MCCP or SCCP modules, or other digital peripherals, to provide these types of functions:

- Time Base Synchronization

- Peripheral Trigger and Clock Inputs

- Signal Gating

The type of output signal is selected using the AUXOUT<1:0> control bits (CCPxCON2H<4:3>). The type of output signal is also dependent on the module operating mode.

On the PIC24FJ256GA412/GB412 family of devices, only the CTMU discharge trigger has access to the auxiliary output signal.

| AUXOUT<1:0> | CCSEL | MOD<3:0> | Comments                  | Signal Description                  |

|-------------|-------|----------|---------------------------|-------------------------------------|

| 00          | х     | xxxx     | Auxiliary output disabled | No Output                           |

| 01          | 0     | 0000     | Time Base modes           | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Special Event Trigger Output        |

| 11          |       |          |                           | No Output                           |

| 01          | 0     | 0001     | Output Compare modes      | Time Base Period Reset or Rollover  |

| 10          |       | through  |                           | Output Compare Event Signal         |

| 11          |       | 1111     |                           | Output Compare Signal               |

| 01          | 1     | xxxx     | Input Capture modes       | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Reflects the Value of the ICDIS bit |

| 11          |       |          |                           | Input Capture Event Signal          |

### TABLE 14-4: AUXILIARY OUTPUT

### 16.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS and OCxR registers. The OCxRS and OCxR registers can be written to at any time, but the duty cycle value is not latched until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation.

Some important boundary parameters of the PWM duty cycle include:

- If OCxR, OCxRS and PRy are all loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than PRy, the pin will remain high (100% duty cycle).

See Example 16-1 for PWM mode timing details. Table 16-1 and Table 16-2 show example PWM frequencies and resolutions for a device operating at 4 MIPS and 10 MIPS, respectively.

### EQUATION 16-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

$$Maximum PWM Resolution (bits) = \frac{\left(\frac{FCY}{FPWM \bullet (Timer Prescale Value)}\right)}{\log_{10}^{(2)}} bits$$

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

### EXAMPLE 16-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

TCY = 2 \* TOSC = 62.5 ns

PWM Period = 1/PWM Frequency = 1/52.08 kHz = 19.2 ms

PWM Period =  $(PR2 + 1) \bullet TCY \bullet (Timer2 Prescale Value)$

$19.2 \ \mu s = (PR2 + 1) \cdot 62.5 \ ns \cdot 1$

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution =  $log_{10}(FCY/FPWM)/log_{10}2)$  bits

$= (\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2) \text{ bits}$

= 8.3 bits

**Note 1:** Based on Tcy = 2 \* Tosc; Doze mode and PLL are disabled.

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |  |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|--|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |  |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |  |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |  |

### TABLE 16-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz)<sup>(1)</sup>

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 16-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

- 11111 = This OC module<sup>(1)</sup>

- 11110 = OCTRIG1 external input

- 11101 = OCTRIG2 external input

- 11100 = CTMU<sup>(2)</sup>

- 11011 = A/D<sup>(2)</sup>

- $11010 = \text{Comparator } 3^{(2)}$

- 11001 = Comparator  $2^{(2)}$ 11000 = Comparator  $1^{(2)}$

- 10111 = SCCP5 capture/compare

- 10110 = SCCP4 capture/compare

- 10110 = SCCP3 capture/compare

- 10100 = SCCP2 capture/compare

- 10011 = MCCP1 capture/compare

- 10010 = Input Capture 3<sup>(2)</sup>

- 10001 =Input Capture 2<sup>(2)</sup>

- 10000 =Input Capture 1<sup>(2)</sup>

- 01111 = SCCP7 capture/compare

- 01110 = SCCP6 capture/compare

- 01101 = Timer3

- 01100 = Timer2

- 01011 = Timer1

- 01010 = SCCP7 sync/trigger

- 01001 = SCCP6 sync/trigger

- 01000 = SCCP5 sync/trigger

- 00111 = SCCP4 sync/trigger

- 00110 = SCCP3 sync/trigger

- 00101 = SCCP2 sync/trigger

- 00100 = MCCP1 sync/trigger

- 00011 =Output Compare  $5^{(1)}$

- 00010 = Output Compare 3<sup>(1)</sup> 00001 = Output Compare 1<sup>(1)</sup>

- 00000 = Not synchronized to any other module

- **Note 1:** Never use an OCx module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as trigger sources only and never as sync sources.

- 3: The DCB<1:0> bits are double-buffered in PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

### REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

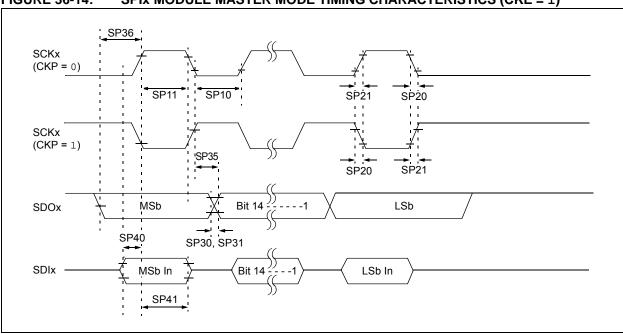

| bit 9         | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <u>Master Mode:</u><br>1 = Input data is sampled at the end of data output time                                                                                                                                                     |

|               | 0 = Input data is sampled at the middle of data output time                                                                                                                                                                         |

|               | Slave Mode:                                                                                                                                                                                                                         |

|               | Input data is always sampled at the middle of data output time, regardless of the SMP setting.                                                                                                                                      |

| bit 8         | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                                      |

|               | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                          |

| bit 7         | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                           |

|               | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select input<br>0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

| bit 6         | CKP: Clock Polarity Select bit                                                                                                                                                                                                      |

|               | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                            |

| bit 5         | MSTEN: Master Mode Enable bit                                                                                                                                                                                                       |

|               | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                   |

| bit 4         | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                                 |

|               | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                    |

| bit 3         | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                                |

|               | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                    |

| bit 2         | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                      |

|               | 1 = REFO is used by the BRG<br>0 = Fosc/2 is used by the BRG                                                                                                                                                                        |

| bit 1         | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                             |

|               | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                                  |

| bit 0         | ENHBUF: Enhanced Buffer Enable bit                                                                                                                                                                                                  |

|               | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                               |

| Note 1:<br>2: | When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.<br>When $FRMEN = 1$ SSEN is not used                                                                                           |

- EN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

#### REGISTER 23-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 8 | <b>G2D1N:</b> Gate 2 Data Source 1 Negated Enable bit<br>1 = Data Source 1 inverted signal is enabled for Gate 2<br>0 = Data Source 1 inverted signal is disabled for Gate 2 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 | G1D4T: Gate 1 Data Source 4 True Enable bit                                                                                                                                  |

|       | <ul> <li>1 = Data Source 4 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 4 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 6 | G1D4N: Gate 1 Data Source 4 Negated Enable bit                                                                                                                               |

|       | <ul> <li>1 = Data Source 4 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 4 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 5 | G1D3T: Gate 1 Data Source 3 True Enable bit                                                                                                                                  |

|       | <ul> <li>1 = Data Source 3 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 3 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 4 | G1D3N: Gate 1 Data Source 3 Negated Enable bit                                                                                                                               |

|       | <ul> <li>1 = Data Source 3 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 3 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                                                  |

|       | <ul> <li>1 = Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 2 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                                               |

|       | <ul> <li>1 = Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 2 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                                                  |

|       | <ul> <li>1 = Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 1 inverted signal is disabled for Gate 1</li> </ul>                                |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                                               |

|       | <ul> <li>1 = Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = Data Source 1 inverted signal is disabled for Gate 1</li> </ul>                                |

| Mode of     | KEVMOD 4.0  |                     | Key                                        | Source                                    | OTP Address |  |

|-------------|-------------|---------------------|--------------------------------------------|-------------------------------------------|-------------|--|

| Operation   | KEYMOD<1:0> | KEYSRC<3:0> -       | SKEYEN = 0                                 | SKEYEN = 1                                | OTF Address |  |

|             |             | 0000 <b>(1)</b>     | CRYKE                                      | _                                         |             |  |

|             |             | 0001                | AES Key #1 Key Config Error <sup>(2)</sup> |                                           | <127:0>     |  |

|             |             | 0010                | AES Key #2                                 |                                           | <255:128>   |  |

|             |             | 0011                | AES                                        | Key #3                                    | <383:256>   |  |

|             |             | 0100                | AES                                        | Key #4                                    | <511:384>   |  |

| 128-Bit AES | 00          | 1001                | AES Key                                    | / #5 (RAM)                                | <127:0>     |  |

|             |             | 1010                | AES Key #6 (RAM)                           |                                           | <255:128>   |  |

|             |             | 1011                | AES Key                                    | / #7 (RAM)                                | <383:256>   |  |

|             |             | 1100                | AES Key                                    | / #8 (RAM)                                | <511:384>   |  |

|             |             | 1111                | Rese                                       | Reserved <sup>(2)</sup>                   |             |  |

|             |             | All Others          | Key Config Error <sup>(2)</sup>            |                                           | _           |  |

|             |             | <sub>0000</sub> (1) | CRYKEY<191:0>                              |                                           | _           |  |

|             |             | 0001                | AES Key #1                                 | ES Key #1 Key Config Error <sup>(2)</sup> |             |  |

|             |             | 0010                | AES Key #2                                 |                                           | <383:192>   |  |

| 192-Bit AES | 01          | 1001                | AES Key                                    | / #3 (RAM)                                | <191:0>     |  |

|             |             | 1010                |                                            | / #4 (RAM)                                | <383:192>   |  |

|             |             | 1111                | Rese                                       | erved <sup>(2)</sup>                      | _           |  |

|             |             | All Others          | Key Con                                    | ifig Error <sup>(2)</sup>                 | _           |  |

|             |             | 0000 <b>(1)</b>     | CRYKE                                      | Y<255:0>                                  | —           |  |

|             |             | 0001                | AES Key #1                                 | Key Config Error <sup>(2)</sup>           | <255:0>     |  |

|             |             | 0010                | AES                                        | Key #2                                    | <511:256>   |  |

| 256-Bit AES | 10          | 1001                | AES Key                                    | / #3 (RAM)                                | <255:0>     |  |

|             |             | 1010                | AES Key #4 (RAM)                           |                                           | <511:256>   |  |

|             |             | 1111                | Rese                                       | erved <sup>(2)</sup>                      |             |  |

|             |             | All Others          |                                            | ifig Error <sup>(2)</sup>                 |             |  |

| (Reserved)  | 11          | xxxx                | Key Con                                    | ifig Error <sup>(2)</sup>                 |             |  |

#### TABLE 25-2: AES KEY MODE/SOURCE SELECTION

Note 1: This configuration is considered a key configuration error (KEYFAIL bit is set) if SWKYDIS is also set.

2: The KEYFAIL bit (CRYSTAT<1>) is set when these configurations are selected and remains set until a valid configuration is selected.

### REGISTER 29-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

| R/W-0         | R/W-0                                                            | R/W-0                                                           | U-0              | U-0              | U-0             | R/W-0, HS        | R-0, HSC       |

|---------------|------------------------------------------------------------------|-----------------------------------------------------------------|------------------|------------------|-----------------|------------------|----------------|

| CON           | COE                                                              | CPOL                                                            | —                | —                | _               | CEVT             | COUT           |

| bit 15        |                                                                  |                                                                 |                  |                  |                 |                  | bit 8          |

|               |                                                                  |                                                                 |                  |                  |                 |                  |                |

| R/W-0         | R/W-0                                                            | U-0                                                             | R/W-0            | U-0              | U-0             | R/W-0            | R/W-0          |

| EVPOL1        | EVPOL0                                                           | _                                                               | CREF             | —                | _               | CCH1             | CCH0           |

| bit 7         |                                                                  |                                                                 |                  |                  |                 |                  | bit 0          |

|               |                                                                  |                                                                 |                  |                  |                 |                  |                |

| Legend:       |                                                                  | HS = Hardware                                                   | Settable bit     | HSC = Hardw      | /are Settable/0 | Clearable bit    |                |

| R = Readable  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                 |                  |                  | ad as '0'       |                  |                |

| -n = Value at | POR                                                              | '1' = Bit is set                                                |                  | '0' = Bit is cle | ared            | x = Bit is unkn  | own            |

|               |                                                                  |                                                                 |                  |                  |                 |                  |                |

| bit 15        | CON: Compa                                                       | arator Enable bit                                               |                  |                  |                 |                  |                |

|               |                                                                  | ator is enabled                                                 |                  |                  |                 |                  |                |

|               | 0 = Compara                                                      | ator is disabled                                                |                  |                  |                 |                  |                |

| bit 14        |                                                                  | arator Output Ena                                               |                  |                  |                 |                  |                |

|               |                                                                  | ator output is pres<br>ator output is inte                      |                  | OUT pin          |                 |                  |                |

| bit 13        | CPOL: Com                                                        | parator Output Po                                               | plarity Select b | bit              |                 |                  |                |

|               |                                                                  | ator output is inve<br>ator output is not                       |                  |                  |                 |                  |                |

| bit 12-10     | -                                                                | nted: Read as '0'                                               |                  |                  |                 |                  |                |

| bit 9         | -                                                                | parator Event bit                                               |                  |                  |                 |                  |                |

|               | 1 = Compara<br>are disal                                         | ator event that is<br>bled until the bit i<br>ator event has no | s cleared        | POL<1:0> has c   | occurred; subs  | sequent triggers | and interrupts |

| bit 8         | -                                                                | parator Output bi                                               |                  |                  |                 |                  |                |

| bito          | When CPOL                                                        | -                                                               |                  |                  |                 |                  |                |

|               | 1 = VIN + > VI                                                   |                                                                 |                  |                  |                 |                  |                |

|               | 0 = VIN + < VI                                                   | IN-                                                             |                  |                  |                 |                  |                |

|               | When CPOL                                                        |                                                                 |                  |                  |                 |                  |                |

|               | 1 = VIN+ < VI<br>0 = VIN+ > VI                                   |                                                                 |                  |                  |                 |                  |                |

| bit 7-6       | • • • • • •                                                      | Trigger/Event/l                                                 | nterrunt Polar   | ity Select hits  |                 |                  |                |

|               |                                                                  | /event/interrupt is                                             |                  | •                | the comparat    | or output (while | CEVT = 0       |

|               |                                                                  | /event/interrupt is                                             |                  |                  |                 |                  | 0211 0)        |

|               |                                                                  | _ = 0 (non-inverte                                              |                  |                  | ·               |                  |                |

|               | -                                                                | -low transition or                                              | •                |                  |                 |                  |                |

|               |                                                                  | = 1 (inverted po                                                |                  |                  |                 |                  |                |

|               |                                                                  | high transition or                                              | -                |                  |                 |                  |                |

|               |                                                                  | /event/interrupt is                                             |                  | transition of th | e comparator    | output:          |                |

|               |                                                                  | <u>= 0 (non-inverte</u><br>high transition or                   |                  |                  |                 |                  |                |

|               |                                                                  | $_{-}$ = 1 (inverted po                                         | -                |                  |                 |                  |                |

|               |                                                                  | -low transition on                                              |                  |                  |                 |                  |                |

|               | 00 = Trigger/                                                    | /event/interrupt g                                              | eneration is di  | sabled           |                 |                  |                |

| bit 5         | Unimplemer                                                       | nted: Read as '0'                                               |                  |                  |                 |                  |                |

|               |                                                                  |                                                                 |                  |                  |                 |                  |                |

NOTES:

### REGISTER 33-5: FOSC: OSCILLATOR CONFIGURATION WORD

| U-1          | U-1                                                              | U-1                                           | U-1                  | U-1               | U-1              | U-1             | U-1          |  |  |  |

|--------------|------------------------------------------------------------------|-----------------------------------------------|----------------------|-------------------|------------------|-----------------|--------------|--|--|--|

| _            | —                                                                | _                                             | _                    | —                 |                  | _               |              |  |  |  |

| bit 23       |                                                                  |                                               |                      |                   |                  |                 | bit 16       |  |  |  |

|              |                                                                  |                                               |                      |                   |                  |                 |              |  |  |  |

| U-1          | U-1                                                              | U-1                                           | U-1                  | U-1               | U-1              | U-1             | U-1          |  |  |  |

|              | _                                                                |                                               |                      |                   |                  |                 | —            |  |  |  |

| bit 15       |                                                                  |                                               |                      |                   |                  |                 | bit 8        |  |  |  |

| R/PO-1       | R/PO-1                                                           | R/PO-1                                        | R/PO-1               | R/PO-1            | R/PO-1           | R/PO-1          | R/PO-1       |  |  |  |

| FCKSM1       | FCKSM0                                                           | IOL1WAY                                       | PLLSS <sup>(1)</sup> | SOSCSEL           | OSCIOFCN         | POSCMOD1        | POSCMODO     |  |  |  |

| bit 7        |                                                                  |                                               |                      | 1                 |                  |                 | bit (        |  |  |  |

| <u> </u>     |                                                                  |                                               | <b>0</b>             |                   |                  |                 |              |  |  |  |

| Legend:      | 1. 1.9                                                           | PO = Program                                  |                      |                   |                  |                 |              |  |  |  |

|              | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                               |                      |                   |                  |                 |              |  |  |  |

| -n = Value a | IT POR                                                           | '1' = Bit is set                              |                      | '0' = Bit is cle  | ared             | x = Bit is unkr | IOWN         |  |  |  |

| bit 23-8     | Unimplemen                                                       | ted: Read as '                                | 1'                   |                   |                  |                 |              |  |  |  |

| bit 7-6      | -                                                                |                                               |                      | afe Clock Monit   | tor Configuratio | on bits         |              |  |  |  |

|              |                                                                  |                                               | -                    | Monitor are disa  | -                |                 |              |  |  |  |

|              |                                                                  | •                                             |                      | Clock Monitor     |                  |                 |              |  |  |  |

|              | 00 = Clock sv                                                    | witching is enal                              | oled, Fail-Safe      | Clock Monitor     | is enabled       |                 |              |  |  |  |