Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

|                            |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb406-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ256GA412/GB412 FAMILY: 100-PIN

| Factures                                       |                  |                  | PIC24FJXX                                                 | XGA/GB410      |                |        |  |

|------------------------------------------------|------------------|------------------|-----------------------------------------------------------|----------------|----------------|--------|--|

| Features                                       | 64GA             | 128GA            | 256GA                                                     | 64GB           | 128GB          | 256GB  |  |

| Operating Frequency                            |                  | •                | DC - 3                                                    | 32 MHz         | •              |        |  |

| Program Memory (bytes)                         | 64K              | 128K             | 256K                                                      | 64K            | 128K           | 256K   |  |

| Program Memory (instructions)                  | 22,016           | 44,032           | 88,064                                                    | 22,016         | 44,032         | 88,064 |  |

| Data Memory (bytes)                            | 8K               | 10               | 6K                                                        | 8K             | 16             | 5K     |  |

| Interrupt Sources (soft vectors/<br>NMI traps) |                  |                  | 113 (                                                     | 107/6)         |                |        |  |

| I/O Ports                                      |                  |                  | Ports A, B,                                               | C, D, E, F, G  |                |        |  |

| Total I/O Pins                                 |                  | 85               |                                                           |                | 84             |        |  |

| Remappable Pins                                |                  |                  | 44 (32 I/Os,                                              | 12 input only) |                |        |  |

| Timers:                                        |                  |                  |                                                           |                |                |        |  |

| Total Number (16-bit)                          |                  |                  | 19                                                        | 1,2)           |                |        |  |

| 32-Bit (from paired 16-bit timers)             |                  |                  | (                                                         | 9              |                |        |  |

| Input Capture w/Timer Channels                 |                  | 6 <sup>(2)</sup> |                                                           |                |                |        |  |

| Output Compare/PWM Channels                    |                  |                  | 6                                                         | (2)            |                |        |  |

| Capture/Compare/PWM/Timer:                     |                  |                  |                                                           |                |                |        |  |

| Single Output (SCCP)                           | 6 <sup>(2)</sup> |                  |                                                           |                |                |        |  |

| Multiple Output (MCCP)                         |                  |                  | 1                                                         | (2)            |                |        |  |

| Serial Communications:                         |                  |                  |                                                           |                |                |        |  |

| UART                                           |                  |                  | 6                                                         | (2)            |                |        |  |

| SPI (3-wire/4-wire)                            |                  |                  | 4                                                         | (2)            |                |        |  |

| I <sup>2</sup> C                               |                  |                  | ;                                                         | 3              |                |        |  |

| USB On-The-Go                                  |                  | No               |                                                           |                | Yes            |        |  |

| Cryptographic Engine                           |                  |                  | Y                                                         | es             |                |        |  |

| Parallel Communications<br>(EPMP/PSP)          |                  |                  | Y                                                         | es             |                |        |  |

| 10/12-Bit Analog-to-Digital                    |                  |                  | 2                                                         | 4              |                |        |  |

| Converter (A/D) (input channels)               |                  |                  |                                                           |                |                |        |  |

| Digital-to-Analog Converter (DAC)              |                  |                  |                                                           | 1              |                |        |  |

| Analog Comparators                             |                  |                  | ;                                                         | 3              |                |        |  |

| CTMU Interface                                 |                  |                  |                                                           | es             |                |        |  |

| LCD Controller (available pixels)              |                  |                  | 512 (64 SE                                                | G x 8 COM)     |                |        |  |

| JTAG Boundary Scan                             |                  |                  |                                                           | es             |                |        |  |

| Resets (and delays)                            | C                | MCLR, WI         | POR, VBAT F<br>OT, Illegal Opc<br>Traps, Config<br>OST, P | ode, REPEAT    | Instruction,   | n,     |  |

| Instruction Set                                | 7                | 7 Base Instru    | ctions, Multiple                                          |                | Mode Variation | าร     |  |

| Packages                                       |                  |                  |                                                           | n TQFP         |                |        |  |

Note 1: Includes the Timer modes of the SCCP and MCCP modules.

**<sup>2:</sup>** Some instantiations of these modules are only available through remappable pins.

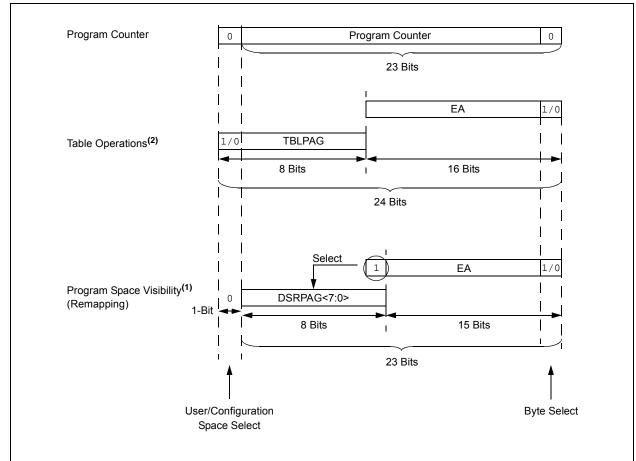

Note 1: DSRPAG<8> acts as word select. DSRPAG<9> should always be '1' to map program memory to data memory.

2: The instructions, TBLRDH/TBLWTH/TBLRDL/TBLWTL, decide if the higher or lower word of program memory is accessed. TBLRDH/TBLWTH instructions access the higher word and TBLRDL/TBLWTL instructions access the lower word. Table Read operations are permitted in the configuration memory space.

#### 5.1.6 CHANNEL PRIORITY

Each DMA channel functions independently of the others, but also competes with the others for access to the data and DMA buses. When access collisions occur, the DMA Controller arbitrates between the channels using a user-selectable priority scheme. Two schemes are available:

- Round Robin: When two or more channels collide, the lower numbered channel receives priority on the first collision. On subsequent collisions, the higher numbered channels each receive priority based on their channel number.

- Fixed: When two or more channels collide, the lowest numbered channel always receives priority, regardless of past history; however, any channel being actively processed is not available for an immediate retrigger. If a higher priority channel is continually requesting service, it will be scheduled for service after the next lower priority channel with a pending request.

### 5.2 Typical Setup

To set up a DMA channel for a basic data transfer:

- Enable the DMA Controller (DMAEN = 1) and select an appropriate channel priority scheme by setting or clearing PRSSEL.

- 2. Program DMAH and DMAL with appropriate upper and lower address boundaries for data RAM operations.

- 3. Select the DMA channel to be used and disable its operation (CHEN = 0).

- Program the appropriate source and destination addresses for the transaction into the channel's DMASRCn and DMADSTn registers. For PIA Addressing mode, use the base address value.

- Program the DMACNTn register for the number of triggers per transfer (One-Shot or Continuous modes) or the number of words (bytes) to be transferred (Repeated modes).

- 6. Set or clear the SIZE bit to select the data size.

- 7. Program the TRMODE<1:0> bits to select the Data Transfer mode.

- 8. Program the SAMODE<1:0> and DAMODE<1:0> bits to select the addressing mode.

- 9. Enable the DMA channel by setting CHEN.

- 10. Enable the trigger source interrupt.

#### 5.3 Peripheral Module Disable

Unlike other peripheral modules, the channels of the DMA Controller cannot be individually powered down using the Peripheral Module Disable (PMD) registers. Instead, the channels are controlled as two groups. The DMA0MD bit (PMD7<4>) selectively controls DMACH0 through DMACH3. The DMA1MD bit (PMD7<5>) controls DMACH4 and DMACH5. Setting both bits effectively disables the DMA Controller.

### 5.4 Registers

The DMA Controller uses a number of registers to control its operation. The number of registers depends on the number of channels implemented for a particular device.

There are always four module-level registers (one control and three buffer/address):

- DMACON: DMA Engine Control Register (Register 5-1)

- DMAH and DMAL: DMA High and Low Address Limit Registers

- · DMABUF: DMA Transfer Data Buffer

Each of the DMA channels implements five registers (two control and three buffer/address):

- DMACHn: DMA Channel n Control Register (Register 5-2)

- DMAINTn: DMA Channel n Interrupt Register (Register 5-3)

- DMASRCn: DMA Data Source Address Pointer for Channel n Register

- DMADSTn: DMA Data Destination Source for Channel n Register

- DMACNTn: DMA Transaction Counter for Channel n Register

For PIC24FJ256GA412/GB412 family devices, there are a total of 34 registers.

#### REGISTER 8-13: IFS7: INTERRUPT FLAG STATUS REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | JTAGIF | U6ERIF | U6TXIF | U6RXIF | U5ERIF | U5TXIF |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5 JTAGIF: JTAG Controller Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 4 U6ERIF: UART6 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 U6TXIF: UART6 Transmitter Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 U6RXIF: UART6 Receiver Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 **U5ERIF:** UART5 Error Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 U5TXIF: UART5 Transmitter Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

#### REGISTER 8-20: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

| R/W-0  | R/W-0   | R/W-0    | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|--------|---------|----------|-----|-----|-------|-----|-------|

| U5RXIE | RTCTSIE | I2C3BCIE | _   | _   | FSTIE | _   |       |

| bit 15 |         |          |     |     |       |     | bit 8 |

| U-0   | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|--------|-------|--------|--------|--------|--------|

| _     | CCT2IE | CCT1IE | LCDIE | CLC4IE | CLC3IE | CLC2IE | CLC1IE |

| bit 7 |        |        |       |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 U5RXIE: UART5 Receiver Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 14 RTCTSIE: RTCC Timestamp Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 13 I2C3BCIE: I2C3 Bus Collision Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 12-11 Unimplemented: Read as '0'

bit 10 **FSTIE:** FRC Self-Tune Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 9-7 **Unimplemented:** Read as '0'

bit 6 CCT2IE: SCCP2 Timer Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 5 **CCT1IE:** MCCP1 Timer Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 4 LCDIE: LCD Controller Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 3 CLC4IE: CLC4 Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 2 CLC3IE: CLC3 Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 1 CLC2IE: CLC2 Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 0 **CLC1IE:** CLC1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-26: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----|-------|-------|-------|

| _      | CNIP2 | CNIP1 | CNIP0 | _   | CMIP2 | CMIP1 | CMIP0 |

| bit 15 |       |       |       |     |       |       | bit 8 |

| U-0   | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|-------|----------|----------|----------|-----|----------|----------|----------|

| _     | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _   | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 |

| bit 7 |          |          |          |     |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 CNIP<2:0>: Input Change Notification Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 **CMIP<2:0>:** Comparator Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 MI2C1IP<2:0>: Master I2C1 Event Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 SI2C1IP<2:0>: Slave I2C1 Event Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-28: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|-------|-------|-------|-----|--------|--------|--------|

| _      | T4IP2 | T4IP1 | T4IP0 | _   | OC4IP2 | OC4IP1 | OC4IP0 |

| bit 15 |       |       |       |     |        |        | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | OC3IP2 | OC3IP1 | OC3IP0 | _   | DMA2IP2 | DMA2IP1 | DMA2IP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **T4IP<2:0>:** Timer4 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 OC3IP<2:0>: Output Compare Channel 3 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 DMA2IP<2:0>: DMA Channel 2 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

.

:

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### **REGISTER 8-31: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9**

| U-0    | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|-----|--------|--------|--------|

| _      | IC5IP2 | IC5IP1 | IC5IP0 | _   | IC4IP2 | IC4IP1 | IC4IP0 |

| bit 15 |        |        |        |     |        |        | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|--------|--------|--------|-----|---------|---------|---------|

| _     | IC3IP2 | IC3IP1 | IC3IP0 | _   | DMA3IP2 | DMA3IP1 | DMA3IP0 |

| bit 7 |        |        |        |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 IC5IP<2:0>: Input Capture Channel 5 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 Unimplemented: Read as '0'

bit 10-8 IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 IC3IP<2:0>: Input Capture Channel 3 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 DMA3IP<2:0>: DMA Channel 3 Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### **REGISTER 8-39: IPC17: INTERRUPT PRIORITY CONTROL REGISTER 17**

| U-0    | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|--------|----------|----------|----------|-----|----------|----------|----------|

| _      | MI2C3IP2 | MI2C3IP1 | MI2C3IP0 | _   | SI2C3IP2 | SI2C3IP1 | SI2C3IP0 |

| bit 15 |          |          |          |     |          |          | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 MI2C3IP<2:0>: Master I2C3 Event Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 Unimplemented: Read as '0'

bit 10-8 SI2C3IP<2:0>: Slave I2C3 Event Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-0 Unimplemented: Read as '0'

### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

OSCCON is protected by a write lock to prevent inadvertent clock switches. See **Section 9.4 "Clock Switching Operation"** for more information.

The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately ±1.5%. It also controls the FRC self-tuning features, described in **Section 9.5** "FRC Active Clock Tuning".

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/SO-0  | R/W-0                 | R-0 <sup>(3)</sup> | U-0 | R/CO-0 | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|--------------------|-----|--------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK               | _   | CF     | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                    |     |        |        |        | bit 0 |

| Legend:           | CO = Clearable Only bit | SO = Settable Only bit     |                    |

|-------------------|-------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 COSC<2:0>: Current Oscillator Selection bits

111 = Fast RC Oscillator with Postscaler (FRCDIV)

110 = Reserved

101 = Low-Power RC Oscillator (LPRC)

100 = Secondary Oscillator (SOSC)

011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)(4)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

111 = Fast RC Oscillator with Postscaler (FRCDIV)

110 = Reserved

101 = Low-Power RC Oscillator (LPRC)

100 = Secondary Oscillator (SOSC)

011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)(4)

000 = Fast RC Oscillator (FRC)

Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- 4: The default divisor of the postscaler is 2, which will generate a 4 MHz clock to the PLL module.

#### REGISTER 14-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0                | R/W-0                | R/W-0                |

|--------|--------|--------|--------|-----|----------------------|----------------------|----------------------|

| OETRIG | OSCNT2 | OSCNT1 | OSCNT0 | _   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> |

| bit 15 |        |        |        |     |                      |                      | bit 8                |

| U-0   | U-0 | R/W-0  | R/W-0                 | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  |

|-------|-----|--------|-----------------------|---------|---------|------------------------|------------------------|

| _     | _   | POLACE | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7 |     |        |                       |         |         |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **OETRIG:** CCPx Dead-Time Select bit

1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered

0 = Normal output pin operation

bit 14-12 OSCNT<2:0>: One-Shot Event Count bits

111 = Extends one-shot event by 7 time base periods (8 time base periods total)

110 = Extends one-shot event by 6 time base periods (7 time base periods total)

101 = Extends one-shot event by 5 time base periods (6 time base periods total)

100 = Extends one-shot event by 4 time base periods (5 time base periods total)

011 = Extends one-shot event by 3 time base periods (4 time base periods total)

010 = Extends one-shot event by 2 time base periods (3 time base periods total)

001 = Extends one-shot event by 1 time base period (2 time base periods total)

000 = Does not extend one-shot trigger event

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OUTM<2:0>: PWMx Output Mode Control bits<sup>(1)</sup>

111 = Reserved

110 = Output Scan mode

101 = Brush DC Output mode, forward

100 = Brush DC Output mode, reverse

011 = Reserved

010 = Half-Bridge Output mode

001 = Push-Pull Output mode

000 = Steerable Single Output mode

bit 7-6 **Unimplemented:** Read as '0'

bit 5 POLACE: CCPx Output Pins, OCMx, OCMxA, OCMxC and OCMxE, Polarity Control bit

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 4 **POLBDF:** CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit<sup>(1)</sup>

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 3-2 PSSACE<1:0>: PWMx Output Pins, OCMx, OCMxA, OCMxC and OCMxE, Shutdown State Control bits

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are tri-stated when a shutdown event occurs

bit 1-0 PSSBDF<1:0>: PWMx Output Pins, OCxB, OCxD, and OCxF, Shutdown State Control bits<sup>(1)</sup>

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are in a high-impedance state when a shutdown event occurs

**Note 1:** These bits are implemented in MCCPx modules only.

| PICZ4FJ. | 236G <i>P</i> | 412/0 | <b>7</b> D412 | FAIVIII | LY |  |

|----------|---------------|-------|---------------|---------|----|--|

| NOTES:   |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

|          |               |       |               |         |    |  |

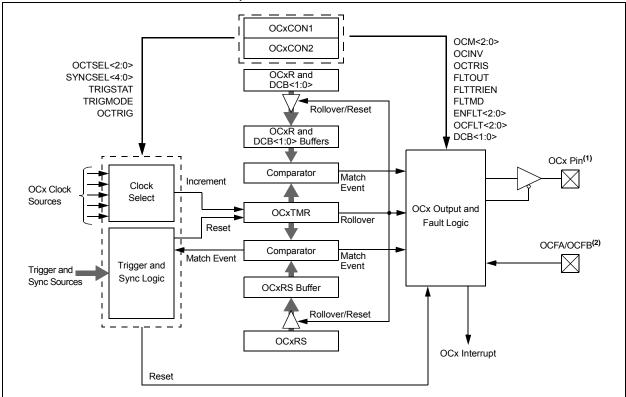

FIGURE 16-2: OUTPUT COMPARE x BLOCK DIAGRAM (DOUBLE-BUFFERED, 16-BIT PWM MODE)

- Note 1: The OCx outputs must be assigned to an available RPn pin before use. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- 2: The OCFA/OCFB Fault inputs must be assigned to an available RPn/RPIn pin before use. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

#### 16.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timery Period register. The PWM period can be calculated using Equation 16-1.

## EQUATION 16-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1] \cdot TCY \cdot (Timer Prescale Value)$

where: PWM Frequency = 1/[PWM Period]

Note 1: Based on Tcy = Tosc \* 2; Doze mode

and PLL are disabled.

Note: A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7 written into the PRy register, will yield a period consisting of 8 time base cycles.

### REGISTER 17-1: SPIXCON1L: SPIX CONTROL REGISTER 1 LOW (CONTINUED)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master Mode:

1 = Input data is sampled at the end of data output time0 = Input data is sampled at the middle of data output time

Slave Mode:

Input data is always sampled at the middle of data output time, regardless of the SMP setting.

bit 8 CKE: SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Transmit happens on transition from active clock state to Idle clock state

0 = Transmit happens on transition from Idle clock state to active clock state

bit 7 SSEN: Slave Select Enable bit (Slave mode)<sup>(2)</sup>

1 =  $\overline{SSx}$  pin is used by the macro in Slave mode;  $\overline{SSx}$  pin is used as the slave select input

$0 = \overline{SSx}$  pin is not used by the macro ( $\overline{SSx}$  pin will be controlled by the port I/O)

bit 6 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level 0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

bit 4 DISSDI: Disable SDIx Input Port bit

1 = SDIx pin is not used by the module; pin is controlled by port function

0 = SDIx pin is controlled by the module

bit 3 DISSCK: Disable SCKx Output Port bit

1 = SCKx pin is not used by the module; pin is controlled by port function

0 = SCKx pin is controlled by the module

bit 2 MCLKEN: Master Clock Enable bit (3)

1 = REFO is used by the BRG

0 = Fosc/2 is used by the BRG

bit 1 SPIFE: Frame Sync Pulse Edge Select bit

1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock

0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock

bit 0 **ENHBUF:** Enhanced Buffer Enable bit

1 = Enhanced Buffer mode is enabled

0 = Enhanced Buffer mode is disabled

Note 1: When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

2: When FRMEN = 1, SSEN is not used.

3: MCLKEN can only be written when the SPIEN bit = 0.

4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

### REGISTER 23-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| G4D4T  | G4D4N | G4D3T | G4D3N | G4D2T | G4D2N | G4D1T | G4D1N |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15 | <b>G4D4T:</b> Gate 4 Data Source 4 True Enable bit 1 = Data Source 4 inverted signal is enabled for Gate 4                                 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

|        | 0 = Data Source 4 inverted signal is disabled for Gate 4                                                                                   |

| bit 14 | G4D4N: Gate 4 Data Source 4 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 4 inverted signal is enabled for Gate 4</li><li>0 = Data Source 4 inverted signal is disabled for Gate 4</li></ul> |

| bit 13 | G4D3T: Gate 4 Data Source 3 True Enable bit                                                                                                |

|        | <ul><li>1 = Data Source 3 inverted signal is enabled for Gate 4</li><li>0 = Data Source 3 inverted signal is disabled for Gate 4</li></ul> |

| bit 12 | G4D3N: Gate 4 Data Source 3 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 3 inverted signal is enabled for Gate 4</li><li>0 = Data Source 3 inverted signal is disabled for Gate 4</li></ul> |

| bit 11 | G4D2T: Gate 4 Data Source 2 True Enable bit                                                                                                |

|        | <ul><li>1 = Data Source 2 inverted signal is enabled for Gate 4</li><li>0 = Data Source 2 inverted signal is disabled for Gate 4</li></ul> |

| bit 10 | G4D2N: Gate 4 Data Source 2 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 2 inverted signal is enabled for Gate 4</li><li>0 = Data Source 2 inverted signal is disabled for Gate 4</li></ul> |

| bit 9  | G4D1T: Gate 4 Data Source 1 True Enable bit                                                                                                |

|        | <ul><li>1 = Data Source 1 inverted signal is enabled for Gate 4</li><li>0 = Data Source 1 inverted signal is disabled for Gate 4</li></ul> |

| bit 8  | G4D1N: Gate 4 Data Source 1 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 1 inverted signal is enabled for Gate 4</li><li>0 = Data Source 1 inverted signal is disabled for Gate 4</li></ul> |

| bit 7  | G3D4T: Gate 3 Data Source 4 True Enable bit                                                                                                |

|        | <ul><li>1 = Data Source 4 inverted signal is enabled for Gate 3</li><li>0 = Data Source 4 inverted signal is disabled for Gate 3</li></ul> |

| bit 6  | G3D4N: Gate 3 Data Source 4 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 4 inverted signal is enabled for Gate 3</li><li>0 = Data Source 4 inverted signal is disabled for Gate 3</li></ul> |

| bit 5  | G3D3T: Gate 3 Data Source 3 True Enable bit                                                                                                |

|        | <ul><li>1 = Data Source 3 inverted signal is enabled for Gate 3</li><li>0 = Data Source 3 inverted signal is disabled for Gate 3</li></ul> |

| bit 4  | G3D3N: Gate 3 Data Source 3 Negated Enable bit                                                                                             |

|        | <ul><li>1 = Data Source 3 inverted signal is enabled for Gate 3</li><li>0 = Data Source 3 inverted signal is disabled for Gate 3</li></ul> |

### REGISTER 23-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit              |

|-------|----------------------------------------------------------|

|       | 1 = Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit           |

|       | 1 = Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit              |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit           |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 3 |

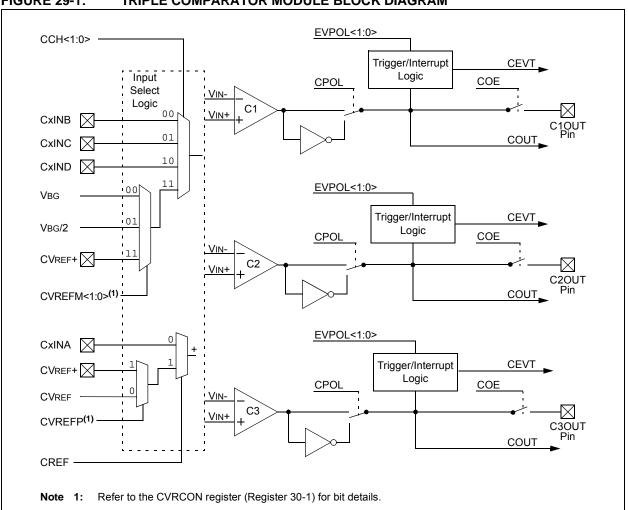

# 29.0 TRIPLE COMPARATOR MODULE

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Scalable Comparator Module" (DS39734). The information in this data sheet supersedes the information in the FRM.

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and VREF+) and a

voltage reference input from one of the internal band gap references or the comparator voltage reference generator (VBG, VBG/2 and CVREF).

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 29-1. Diagrams of the possible individual comparator configurations are shown in Figure 29-2.

Each comparator has its own control register, CMxCON (Register 29-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 29-2).

#### FIGURE 29-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

|        | J230C | JA4 1 Z/ | <b>GD4</b> 12 | Z FAIVI |  |

|--------|-------|----------|---------------|---------|--|

| NOTES: |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

|        |       |          |               |         |  |

#### REGISTER 33-2: FBSLIM: BOOT SEGMENT LIMIT CONFIGURATION WORD

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-1    | U-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1      | R/PO-1 | R/PO-1 |

|--------|-----|-----|--------|--------|-------------|--------|--------|

| _      | _   | _   |        |        | BSLIM<12:8> |        |        |

| bit 15 |     |     |        |        |             |        | bit 8  |

| R/PO-1     | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |  |

|------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| BSLIM<7:0> |        |        |        |        |        |        |        |  |  |

| bit 7      |        |        |        |        |        |        | bit 0  |  |  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-13 **Unimplemented:** Read as '1'

bit 12-0 **BSLIM<12:0>:** Boot Segment Upper Address Limit bits

Defines the address of the last page of the Boot Segment plus 1, when the Boot Segment is instantiated

(BSEN = 0). The stored value is the inverse of the actual address value.

#### REGISTER 33-3: FSIGN: SIGNATURE CONFIGURATION WORD

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   |     |     |     | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| r-x    | U-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

**Legend:** r = Reserved bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-16 Unimplemented: Read as '1'

bit 15 Reserved: The value is unknown; program as '0'

bit 14-0 **Unimplemented:** Read as '1'

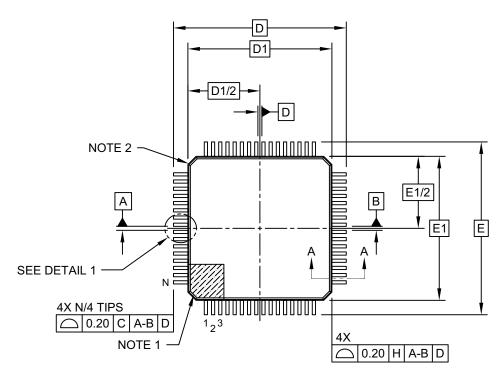

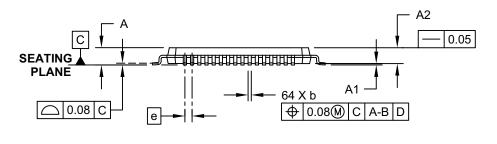

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2