Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb410-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin | Function                                                                | Pin       | Function                                           |

|-----|-------------------------------------------------------------------------|-----------|----------------------------------------------------|

| 1   | SEG50/OCM1C/CTED3/IOCG15/RG15                                           | 51        | SEG12/RP16/USBID/IOCF3/RF3                         |

| 2   | VDD                                                                     | 52        | SEG40/ <b>RP30</b> /IOCF2/RF2                      |

| 3   | LCDBIAS2/IC4/CTED4/PMD5/IOCE5/RE5                                       | 53        | SEG41/ <b>RP15</b> /IOCF8/RF8                      |

| 4   | LCDBIAS1/SCL3/IC5/PMD6/IOCE6/RE6                                        | 54        | VBUS/IOCF7/RF7                                     |

| 5   | LCDBIAS0/SDA3/IC6/PMD7/IOCE7/RE7                                        | 55        | VUSB3V3                                            |

| 6   | SEG32/RPI38/OCM1D/IOCC1/RC1                                             | 56        | D-/IOCG3/RG3                                       |

| 7   | SEG51/RPI39/IOCC2/RC2                                                   | 57        | D+/IOCG2/RG2                                       |

| 8   | SEG33/RPI40/IOCC3/RC3                                                   | 58        | SEG55/SCL2/IOCA2/RA2                               |

| 9   | SEG52/AN16/RPI41/PMCS2/IOCC4/RC4                                        | 59        | SEG56/SDA2/PMA20/IOCA3/RA3                         |

| 10  | SEG0/AN17/C1IND/RP21/ICM1/OCM1A/PMA5/IOCG6/RG6                          | 60        | TDI/PMA21/IOCA4/RA4                                |

| 11  | VLCAP1/AN18/C1INC/RP26/OCM1B/PMA4/IOCG7/RG7                             | 61        | TDO/SEG28/IOCA5/RA5                                |

| 12  | VLCAP2/AN19/C2IND/RP19/ICM2/OCM2/PMA3/IOCG8/RG8                         | 62        | VDD                                                |

| 13  | MCLR                                                                    | 63        | OSCI/CLKI/IOCC12/RC12                              |

| 14  | SEG1/AN20/C1INC/C2INC/C3INC/ <b>RP27</b> /DAC1/PMA2/PMALU/<br>IOCG9/RG9 | 64        | OSCO/CLKO/IOCC15/RC15                              |

| 15  | Vss                                                                     | 65        | Vss                                                |

| 16  | VDD                                                                     | 66        | SEG42/RPI36/SCL1/PMA22/IOCA14/RA14                 |

| 17  | TMS/SEG48/CTED14/IOCA0/RA0                                              | 67        | SEG43/RPI35/SDA1/PMBE1/IOCA15/RA15                 |

| 18  | SEG34/RPI33/PMCS1/IOCE8/RE8                                             | 68        | SEG13/CLC4OUT/RP2/RTCC/U6RTS/U6BCLK/ICM5/IOCD8/RD8 |

| 19  | SEG35/AN21/RPI34/PMA19/IOCE9/RE9                                        | 69        | SEG14/ <b>RP4</b> /PMACK2/IOCD9/RD9                |

| 20  | PGEC3/SEG2/AN5/C1INA/RP18/ICM3/OCM3/IOCB5/RB5                           | 70        | SEG15/C3IND/RP3/PMA15/APMCS2/IOCD10/RD10           |

| 21  | PGED3/SEG3/AN4/C1INB/RP28/USBOEN/IOCB4/RB4                              | 71        | SEG16/C3INC/RP12/PMA14/PMCS/APMCS1/IOCD11/RD11     |

| 22  | SEG4/AN3/C2INA/IOCB3/RB3                                                | 72        | SEG17/CLC3OUT/RP11/U6CTS/ICM6/INT0/IOCD0/RD0       |

| 23  | SEG5/AN2/CTCMP/C2INB/RP13/CTED13/IOCB2/RB2                              | 73        | SOSCI/IOCC13/RC13                                  |

| 24  | PGEC1/SEG6/VREF-/CVREF-/AN1/AN1-/RP1/CTED12/IOCB1/RB1                   | 74        | SOSCO/SCLKI/RPI37/PWRLCLK/IOCC14/RC14              |

| 25  | PGED1/SEG7/VREF+/CVREF+/DVREF+/AN0/RP0/IOCB0/RB0                        | 75        | Vss                                                |

| 26  | PGEC2/LCDBIAS3/AN6/RP6/IOCB6/RB6                                        | 76        | SEG20/RP24/U5TX/ICM4/IOCD1/RD1                     |

| 27  | PGED2/SEG63/AN7/RP7/U6TX/IOCB7/RB7                                      | 77        | SEG21/ <b>RP23</b> /PMACK1/IOCD2/RD2               |

| 28  | SEG36/VREF-/CVREF-/PMA7/IOCA9/RA9                                       | 78        | SEG22/RP22/ICM7/PMBE0/IOCD3/RD3                    |

| 29  | SEG37/VREF+/CVREF+/DVREF+/PMA6/IOCA10/RA10                              | 79        | SEG44/RPI42/PMD12/IOCD12/RD12                      |

| 30  | AVDD                                                                    | 80        | SEG45/PMD13/IOCD13/RD13                            |

| 31  | AVss                                                                    | 81        | SEG23/RP25/PMWR/PMENB/IOCD4/RD4                    |

| 32  | COM7/SEG31/AN8/RP8/PWRGT/IOCB8/RB8                                      | 82        | SEG24/ <b>RP20</b> /PMRD/PMWR/IOCD5/RD5            |

| 33  | COM6/SEG30/AN9/TMPR/RP9/T1CK/IOCB9/RB9                                  | 83        | SEG25/C3INB/U5RX/OC4/PMD14/IOCD6/RD6               |

| 34  | COM5/SEG29/CVREF/AN10/SDO4/PMA13/IOCB10/RB10                            | 84        | SEG26/C3INA/U5RTS/U5BCLK/OC5/PMD15/IOCD7/RD7       |

| 35  | AN11/REFI1/SS4/FSYNC4/PMA12/IOCB11/RB11                                 | 85        | VCAP                                               |

| 36  | Vss                                                                     | 86        | VBAT                                               |

| 37  | VDD                                                                     | 87        | SEG27/U5CTS/OC6/PMD11/IOCF0/RF0                    |

| 38  | TCK/IOCA1/RA1                                                           | 88        | COM4/SEG47/SCK4/PMD10/IOCF1/RF1                    |

| 39  | SEG53/ <b>RP31</b> /IOCF13/RF13                                         | 89        | SEG46/PMD9/IOCG1/RG1                               |

| 40  | SEG54/ <b>RPI32</b> /CTED7/PMA18/IOCF12/RF12                            | 90        | SEG49/PMD8/IOCG0/RG0                               |

| 41  | SEG18/AN12/U6RX/CTED2/PMA11/IOCB12/RB12                                 | 91        | SEG57/AN23/OCM1E/IOCA6/RA6                         |

| 42  | SEG19/AN13/SDI4/CTED1/PMA10/IOCB13/RB13                                 | 92        | SEG58/AN22/OCM1F/PMA17/IOCA7/RA7                   |

| 43  | SEG8/AN14/ <b>RP14</b> /CTED5/CTPLS/PMA1/PMALH/IOCB14/RB14              | 93        | COM3/PMD0/IOCE0/RE0                                |

| 44  | SEG9/AN15/RP29/CTED6/PMA0/PMALL/IOCB15/RB15                             | 94        | COM2/PMD1/IOCE1/RE1                                |

| 45  | Vss                                                                     | 95        | SEG59/CTED11/PMA16/IOCG14/RG14                     |

| 46  | VDD                                                                     | 96        | SEG60/IOCG12/RG12                                  |

| 47  | SEG38/ <b>RPI43</b> /IOCD14/RD14                                        | 97        | SEG61/CTED10/IOCG13/RG13                           |

|     |                                                                         | -         | COM1/PMD2/IOCE2/RE2                                |

|     | SEG39/ <b>RP5</b> /IOCD15/RD15                                          | <u>yx</u> |                                                    |

| 48  | SEG39/ <b>RP5</b> /IOCD15/RD15<br>SEG10/ <b>RP10</b> /PMA9/IOCF4/RF4    | 98<br>99  | COM0/CTED9/PMD3/IOCE3/RE3                          |

#### TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR PIC24FJXXXGB410 DEVICES

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select functions.

# 5.0 DIRECT MEMORY ACCESS CONTROLLER (DMA)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Direct Memory Access Controller (DMA)" (DS39742). The information in this data sheet supersedes the information in the FRM.

The Direct Memory Access Controller (DMA) is designed to service high data throughput peripherals operating on the SFR bus, allowing them to access data memory directly and alleviating the need for CPU intensive management. By allowing these data intensive peripherals to share their own data path, the main data bus is also deloaded, resulting in additional power savings.

The DMA Controller functions both as a peripheral and a direct extension of the CPU. It is located on the microcontroller data bus between the CPU and DMA-enabled peripherals, with direct access to SRAM. This partitions the SFR bus into two buses, allowing the DMA Controller access to the DMA-capable peripherals located on the new DMA SFR bus. The controller serves as a master device on the DMA SFR bus, controlling data flow from DMA-capable peripherals. The controller also monitors CPU instruction processing directly, allowing it to be aware of when the CPU requires access to peripherals on the DMA bus and automatically relinquishing control to the CPU as needed. This increases the effective bandwidth for handling data without DMA operations causing a processor stall. This makes the controller essentially transparent to the user.

The DMA Controller has these features:

- Six Multiple Independent and Independently Programmable Channels

- Concurrent Operation with the CPU (no DMA caused Wait states)

- DMA Bus Arbitration

- Five Programmable Address modes

- · Four Programmable Transfer modes

- Four Flexible Internal Data Transfer modes

- · Byte or Word Support for Data Transfer

- 16-Bit Source and Destination Address Register for Each Channel, Dynamically Updated and Reloadable

- 16-Bit Transaction Count Register, Dynamically Updated and Reloadable

- Upper and Lower Address Limit Registers

- Counter Half-Full Level Interrupt

- Software Triggered Transfer

- Null Write mode for Symmetric Buffer Operations

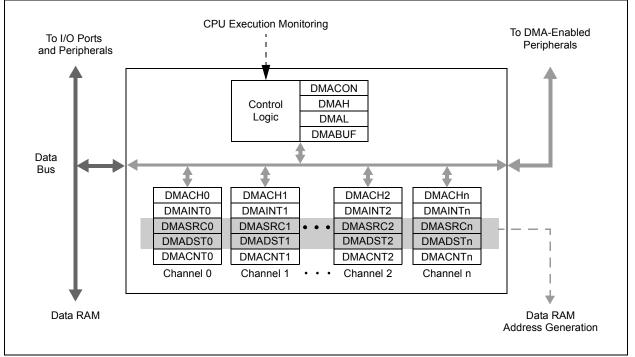

A simplified block diagram of the DMA Controller is shown if Figure 5-1.

# FIGURE 5-1: DMA FUNCTIONAL BLOCK DIAGRAM

## 5.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction. In addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- Source and destination (SFRs and data RAM)

- · Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (Fixed Address or Address Blocks with or without Address Increment/Decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

#### 5.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 07FFh) or the data RAM space (0800h to FFFFh) can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 5-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

### 5.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-size transactions. When byte-size transactions are chosen, the LSb of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

### 5.1.3 TRIGGER SOURCE

The DMA Controller can use 63 of the device's interrupt sources to initiate a transaction. The DMA trigger sources occur in reverse order than their natural interrupt priority and are shown in Table 5-1. Since the source and destination addresses for any transaction can be programmed independently of the trigger source, the DMA Controller can use any trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

#### 5.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each trigger.

- One-Shot: A single transaction occurs for each trigger.

- Continuous: A series of back-to-back transactions occur for each trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per trigger, until the DMA channel is disabled.

All transfer modes allow the option to have the source and destination addresses, and counter value, automatically reloaded after the completion of a transaction; Repeated mode transfers do this automatically.

### 5.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- · Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range of source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA-capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

For PIC24FJ256GA412/GB412 family devices, the 12-bit A/D Converter module is the only PIA-capable peripheral. Details for its use in PIA mode are provided in **Section 27.0 "12-Bit A/D Converter with Threshold Detect"**.

| REGISTER      | 5-2: DMAC                       | CHn: DMA Cł                           | HANNEL n C      | ONTROL RE         | GISTER            |                       |                        |

|---------------|---------------------------------|---------------------------------------|-----------------|-------------------|-------------------|-----------------------|------------------------|

| U-0           | U-0                             | U-0                                   | r-0             | U-0               | R/W-0             | R/W-0                 | R/W-0                  |

| _             | _                               | —                                     | —               | _                 | NULLW             | RELOAD <sup>(1)</sup> | CHREQ <sup>(3)</sup>   |

| bit 15        |                                 |                                       |                 |                   |                   |                       | bit                    |

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0           | R/W-0             | R/W-0             | R/W-0                 | R/W-0                  |

| SAMODE1       | SAMODE0                         | DAMODE1                               | DAMODE0         | TRMODE1           | TRMODE0           | SIZE                  | CHEN                   |

| bit 7         |                                 |                                       |                 |                   |                   |                       | bit                    |

| Legend:       |                                 | r = Reserved                          | bit             |                   |                   |                       |                        |

| R = Readable  | e bit                           | W = Writable                          | bit             | U = Unimplen      | nented bit, read  | d as '0'              |                        |

| -n = Value at | POR                             | '1' = Bit is set                      |                 | '0' = Bit is clea | ared              | x = Bit is unkn       | own                    |

|               |                                 |                                       | .1              |                   |                   |                       |                        |

| bit 15-13     | -                               | ted: Read as '(                       | ).              |                   |                   |                       |                        |

| bit 12        | Reserved: Ma                    |                                       | .,              |                   |                   |                       |                        |

| bit 11        | -                               | ted: Read as '(                       |                 |                   |                   |                       |                        |

| bit 10        |                                 | Write Mode bit<br>write is initiate   |                 | for over write    |                   |                       |                        |

|               |                                 | write is initiate                     |                 |                   | e to DIVIADS IT   | I                     |                        |

| bit 9         |                                 | dress and Cou                         |                 | )                 |                   |                       |                        |

|               |                                 |                                       |                 |                   | reloaded to th    | eir previous va       | lues upon th           |

|               |                                 | e next operation                      |                 | •                 |                   |                       | (0)                    |

|               |                                 |                                       |                 |                   | ded on the star   | t of the next ope     | eration <sup>(2)</sup> |

| bit 8         |                                 | A Channel Soft                        | •               |                   |                   |                       |                        |

|               |                                 | equest is initiate<br>request is pend |                 | automatically of  | cleared upon c    | ompletion of a [      | OMA transfer           |

| bit 7-6       | SAMODE<1:0                      | 0>: Source Add                        | lress Mode Se   | lection bits      |                   |                       |                        |

|               |                                 | Cn is used in P                       |                 |                   |                   |                       |                        |

|               |                                 | Cn is decremen<br>Cn is incremen      |                 |                   |                   |                       |                        |

|               |                                 | Cn remains un                         |                 |                   |                   | mpletion              |                        |

| bit 5-4       |                                 | 0>: Destination                       | -               | -                 |                   |                       |                        |

|               |                                 | Tn is used in P                       |                 |                   |                   | nchanged              |                        |

|               | 10 = DMADS                      | Tn is decremer                        | nted based on   | the SIZE bit aft  | ter a transfer co | ompletion             |                        |

|               |                                 | Tn is incremen                        |                 |                   |                   | mpletion              |                        |

| hit 2 2       |                                 | Tn remains und                        | -               | -                 | Dietion           |                       |                        |

| bit 3-2       |                                 | 0>: Transfer Mo                       |                 | nis               |                   |                       |                        |

|               | 10 = Continuo                   | ed Continuous r                       | noue            |                   |                   |                       |                        |

|               |                                 | ed One-Shot mo                        | ode             |                   |                   |                       |                        |

|               | 00 = One-Sho                    | ot mode                               |                 |                   |                   |                       |                        |

| bit 1         | SIZE: Data Si                   | ze Selection bi                       | t               |                   |                   |                       |                        |

|               | 1 = Byte (8-bi<br>0 = Word (16- |                                       |                 |                   |                   |                       |                        |

| bit 0         | CHEN: DMA                       | Channel Enable                        | e bit           |                   |                   |                       |                        |

|               | 1 = The corre                   | sponding chan                         | nel is enabled  |                   |                   |                       |                        |

|               |                                 | sponding chan                         |                 |                   |                   |                       |                        |

| Note 1: O     | nly the original D              | MACNTn is rec                         | uired to be sto | red to recover fl | he original DMA   | SRCn and DM           | ADSTn value            |

|               | MACNTn will alv                 |                                       | -               |                   | -                 |                       |                        |

|               | e number of tra                 | -                                     |                 |                   | -                 |                       |                        |

### REGISTER 5-2: DMACHn: DMA CHANNEL n CONTROL REGISTER

### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

|                                     | Vector | IDO # | IVT     | Inte     | Interrupt Bit Locations |              |  |  |

|-------------------------------------|--------|-------|---------|----------|-------------------------|--------------|--|--|

| Interrupt Source                    | Number | IRQ # | Address | Flag     | Enable                  | Priority     |  |  |

| MCCP1 Capture/Compare               | 71     | 63    | 000092h | IFS3<15> | IEC3<15>                | IPC15<14:12> |  |  |

| MCCP1 Timer                         | 109    | 101   | 0000DEh | IFS6<5>  | IEC6<5>                 | IPC25<6:4>   |  |  |

| SCCP2 Capture/Compare               | 72     | 64    | 000094h | IFS4<0>  | IEC4<0>                 | IPC16<2:0>   |  |  |

| SCCP2 Timer                         | 110    | 102   | 0000E0h | IFS6<6>  | IEC6<6>                 | IPC25<10:8>  |  |  |

| SCCP3 Capture/Compare               | 102    | 94    | 0000D0h | IFS5<14> | IEC5<14>                | IPC23<10:8>  |  |  |

| SCCP3 Timer                         | 51     | 43    | 00006Ah | IFS2<11> | IEC2<11>                | IPC10<14:12> |  |  |

| SCCP4 Capture/Compare               | 103    | 95    | 0000D2h | IFS5<15> | IEC5<15>                | IPC23<14:12> |  |  |

| SCCP4 Timer                         | 52     | 44    | 00006Ch | IFS2<12> | IEC2<12>                | IPC11<2:0>   |  |  |

| Output Compare 1                    | 10     | 2     | 000018h | IFS0<2>  | IEC0<2>                 | IPC0<10:8>   |  |  |

| Output Compare 2                    | 14     | 6     | 000020h | IFS0<6>  | IEC0<6>                 | IPC1<10:8>   |  |  |

| Output Compare 3                    | 33     | 25    | 000046h | IFS1<9>  | IEC1<9>                 | IPC6<6:4>    |  |  |

| Output Compare 4                    | 34     | 26    | 000048h | IFS1<10> | IEC1<10>                | IPC6<10:8>   |  |  |

| Output Compare 5                    | 49     | 41    | 000066h | IFS2<9>  | IEC2<9>                 | IPC10<6:4>   |  |  |

| Output Compare 6                    | 50     | 42    | 000068h | IFS2<10> | IEC2<10>                | IPC10<10:8>  |  |  |

| Real-Time Clock and Calendar (RTCC) | 70     | 62    | 000090h | IFS3<14> | IEC3<14>                | IPC15<10:8>  |  |  |

| RTCC Timestamp                      | 118    | 110   | 0000F0h | IFS6<14> | IEC6<14>                | IPC27<10:8>  |  |  |

| SCCP5 Capture/Compare               | 30     | 22    | 000040h | IFS1<6>  | IEC1<6>                 | IPC5<10:8>   |  |  |

| SCCP6 Capture/Compare               | 31     | 23    | 000042h | IFS1<7>  | IEC1<7>                 | IPC5<14:12>  |  |  |

| SCCP7 Capture/Compare               | 81     | 73    | 0000A6h | IFS4<9>  | IEC4<9>                 | IPC18<6:4>   |  |  |

| SCCP5 Timer                         | 55     | 47    | 000072h | IFS2<15> | IEC2<15>                | IPC11<14:12> |  |  |

| SCCP6 Timer                         | 56     | 48    | 000074h | IFS3<0>  | IEC3<0>                 | IPC12<2:0>   |  |  |

| SCCP7 Timer                         | 59     | 51    | 00007Ah | IFS3<3>  | IEC3<3>                 | IPC12<14:12> |  |  |

| SPI1 General                        | 17     | 9     | 000026h | IFS0<9>  | IEC0<9>                 | IPC2<6:4>    |  |  |

| SPI1 Receive                        | 66     | 58    | 000088h | IFS3<10> | IEC3<10>                | IPC14<10:8>  |  |  |

| SPI1 Transmit                       | 18     | 10    | 000028h | IFS0<10> | IEC0<10>                | IPC2<10:8>   |  |  |

| SPI2 General                        | 40     | 32    | 000054h | IFS2<0>  | IEC2<0>                 | IPC8<2:0>    |  |  |

| SPI2 Receive                        | 67     | 59    | 00008Ah | IFS3<11> | IEC3<11>                | IPC14<14:12> |  |  |

| SPI2 Transmit                       | 41     | 33    | 000056h | IFS2<1>  | IEC2<1>                 | IPC8<6:4>    |  |  |

| SPI3 General                        | 98     | 90    | 0000C8h | IFS5<10> | IEC5<10>                | IPC22<10:8>  |  |  |

| SPI3 Receive                        | 68     | 60    | 00008Ch | IFS3<12> | IEC3<12>                | IPC15<2:0>   |  |  |

| SPI3 Transmit                       | 99     | 91    | 0000CAh | IFS5<11> | IEC5<11>                | IPC22<14:12> |  |  |

| SPI3 Transmit                       | 101    | 93    | 0000CEh | IFS5<13> | IEC5<13>                | IPC23<6:4>   |  |  |

| SPI4 General                        | 100    | 92    | 0000CCh | IFS5<12> | IEC5<12>                | IPC23<2:0>   |  |  |

| SPI4 Receive                        | 65     | 57    | 000086h | IFS3<9>  | IEC3<9>                 | IPC14<6:4>   |  |  |

| Timer1                              | 11     | 3     | 00001Ah | IFS0<3>  | IEC0<3>                 | IPC0<14:12>  |  |  |

| Timer2                              | 15     | 7     | 000022h | IFS0<7>  | IEC0<7>                 | IPC1<14:12>  |  |  |

| Timer3                              | 16     | 8     | 000024h | IFS0<8>  | IEC0<8>                 | IPC2<2:0>    |  |  |

| Timer4                              | 35     | 27    | 00004Ah | IFS1<11> | IEC1<11>                | IPC6<14:12>  |  |  |

| Timer5                              | 36     | 28    | 00004Ch | IFS1<12> | IEC1<12>                | IPC7<2:0>    |  |  |

| UART1 Error                         | 73     | 65    | 000096h | IFS4<1>  | IEC4<1>                 | IPC16<6:4>   |  |  |

| UART1 Receiver                      | 19     | 11    | 00002Ah | IFS0<11> | IEC0<11>                | IPC2<14:12>  |  |  |

| UART1 Transmitter                   | 20     | 12    | 00002Ch | IFS0<12> | IEC0<12>                | IPC3<2:0>    |  |  |

| UART2 Error                         | 74     | 66    | 000098h | IFS4<2>  | IEC4<2>                 | IPC16<10:8>  |  |  |

| UART2 Receiver                      | 38     | 30    | 000050h | IFS1<14> | IEC1<14>                | IPC7<10:8>   |  |  |

| UART2 Transmitter                   | 39     | 31    | 000052h | IFS1<15> | IEC1<15>                | IPC7<14:12>  |  |  |

## TABLE 11-11: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| Input Name                   | Function Name | Register      | Function Mapping Bits |

|------------------------------|---------------|---------------|-----------------------|

| CCP Clock Input A            | TCKIA         | RPINR12<5:0>  | TCKIAR<5:0>           |

| CCP Clock Input B            | TCKIB         | RPINR12<13:8> | TCKIBR<5:0>           |

| CLC Input A                  | CLCINA        | RPINR25<5:0>  | CLCINAR<5:0>          |

| CLC Input B                  | CLCINB        | RPINR25<13:8> | CLCINBR<5:0>          |

| External Interrupt 1         | INT1          | RPINR0<13:8>  | INT1R<5:0>            |

| External Interrupt 2         | INT2          | RPINR1<5:0>   | INT2R<5:0>            |

| External Interrupt 3         | INT3          | RPINR1<13:8>  | INT3R<5:0>            |

| External Interrupt 4         | INT4          | RPINR2<5:0>   | INT4R<5:0>            |

| Generic Timer External input | TMRCK         | RPINR23<13:8> | TXCKR<5:0>            |

| Input Capture 1              | IC1           | RPINR7<5:0>   | IC1R<5:0>             |

| Input Capture 2              | IC2           | RPINR7<13:8>  | IC2R<5:0>             |

| Input Capture 3              | IC3           | RPINR8<5:0>   | IC3R<5:0>             |

| Output Compare Fault A       | OCFA          | RPINR11<5:0>  | OCFAR<5:0>            |

| Output Compare Fault B       | OCFB          | RPINR11<13:8> | OCFBR<5:0>            |

| Output Compare Trigger 1     | OCTRIG1       | RPINR0<5:0>   | OCTRIG1R<5:0>         |

| Output Compare Trigger 1     | OCTRIG2       | RPINR2<13:8>  | OCTRIG2R<5:0>         |

| SPI1 Clock Input             | SCK1IN        | RPINR20<13:8> | SCK1R<5:0>            |

| SPI1 Data Input              | SDI1          | RPINR20<5:0>  | SDI1R<5:0>            |

| SPI1 Slave Select            | SS1IN         | RPINR21<5:0>  | SS1R<5:0>             |

| SPI2 Clock Input             | SCK2IN        | RPINR22<13:8> | SCK2R<5:0>            |

| SPI2 Data Input              | SDI2          | RPINR22<5:0>  | SDI2R<5:0>            |

| SPI2 Slave Select            | SS2IN         | RPINR23<5:0>  | SS2R<5:0>             |

| SPI3 Clock Input             | SCK3IN        | RPINR28<13:8> | SCK3R<5:0>            |

| SPI3 Data Input              | SDI3          | RPINR28<5:0>  | SDI3R<5:0>            |

| SPI3 Slave Select            | SS3IN         | RPINR29<5:0>  | SS3R<5:0>             |

| Timer2 External Clock        | T2CK          | RPINR3<5:0>   | T2CKR<5:0>            |

| Timer3 External Clock        | T3CK          | RPINR3<13:8>  | T3CKR<5:0>            |

| Timer4 External Clock        | T4CK          | RPINR4<5:0>   | T4CKR<5:0>            |

| Timer5 External Clock        | T5CK          | RPINR4<13:8>  | T5CKR<5:0>            |

| UART1 Clear-to-Send          | U1CTS         | RPINR18<13:8> | U1CTSR<5:0>           |

| UART1 Receive                | U1RX          | RPINR18<5:0>  | U1RXR<5:0>            |

| UART2 Clear-to-Send          | U2CTS         | RPINR19<13:8> | U2CTSR<5:0>           |

| UART2 Receive                | U2RX          | RPINR19<5:0>  | U2RXR<5:0>            |

| UART3 Clear-to-Send          | U3CTS         | RPINR21<13:8> | U3CTSR<5:0>           |

| UART3 Receive                | U3RX          | RPINR17<13:8> | U3RXR<5:0>            |

| UART4 Clear-to-Send          | U4CTS         | RPINR27<13:8> | U4CTSR<5:0>           |

| UART4 Receive                | U4RX          | RPINR27<5:0>  | U4RXR<5:0>            |

### 11.5.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the Peripheral Pin Selects are not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '111111' and all RPORx registers reset to '000000', all Peripheral Pin Select inputs are tied to Vss, and all Peripheral Pin Select outputs are disconnected.

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset. For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing-critical, it must be executed as an assembly language routine in the same manner as changes to the oscillator configuration. If the bulk of the application is written in 'C', or another high-level language, the unlock sequence should be performed by writing in-line assembly.

Choosing the configuration requires the review of all Peripheral Pin Selects and their pin assignments, especially those that will not be used in the application. In all cases, unused pin-selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn/RPIn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pin-selectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use. Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled as if it were tied to a fixed pin. Where this happens in the application code (immediately following a device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that Peripheral Pin Select functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as a digital I/O when used with a Peripheral Pin Select.

Example 11-4 shows a configuration for bidirectional communication with flow control using UART1. The following input and output functions are used:

- Input Functions: U1RX, U1CTS

- Output Functions: U1TX, U1RTS

#### EXAMPLE 11-4: CONFIGURING UART1 INPUT AND OUTPUT FUNCTIONS

```

// Unlock Registers

__builtin_write_OSCCONL(OSCCON & 0xbf);

// Configure Input Functions (Table 11-11)

// Assign U1RX To Pin RP0

RPINR18bits.U1RXR = 0;

// Assign UlCTS To Pin RP1

RPINR18bits.U1CTSR = 1;

// Configure Output Functions (Table 11-12)

// Assign U1TX To Pin RP2

RPOR1bits.RP2R = 3;

// Assign UlRTS To Pin RP3

RPOR1bits.RP3R = 4;

// Lock Registers

asm volatile ("MOV #OSCCON, w1

n''

"MOV

#0x46, w2

\n"

"MOV

#0x57, w3

\n"

"MOV.b w2, [w1]

\n"

"MOV.b w3, [w1]

\n"

"BSET OSCCON, #6");

// or use the XC16 built-in macro:

// __builtin_write_OSCCONL(OSCCON | 0x40);

```

| U-0             | U-0           | R/W-0            | R/W-0          | R/W-0                              | R/W-0          | R/W-0              | R/W-0          |  |

|-----------------|---------------|------------------|----------------|------------------------------------|----------------|--------------------|----------------|--|

| —               | —             | RP1R5            | RP1R4          | RP1R3                              | RP1R2          | RP1R1              | RP1R0          |  |

| bit 15          |               |                  |                |                                    |                |                    | bit 8          |  |

|                 |               |                  |                |                                    |                |                    |                |  |

| U-0             | U-0           | R/W-0            | R/W-0          | R/W-0                              | R/W-0          | R/W-0              | R/W-0          |  |

| —               | —             | RP0R5            | RP0R4          | RP0R3                              | RP0R2          | RP0R1              | RP0R0          |  |

| bit 7           |               |                  |                |                                    |                |                    | bit 0          |  |

|                 |               |                  |                |                                    |                |                    |                |  |

| Legend:         |               |                  |                |                                    |                |                    |                |  |

| R = Readable    | bit           | W = Writable     | bit            | U = Unimplemented bit, read as '0' |                |                    |                |  |

| -n = Value at F | POR           | '1' = Bit is set |                | '0' = Bit is clea                  | ared           | x = Bit is unknown |                |  |

|                 |               |                  |                |                                    |                |                    |                |  |

| bit 15-14       | Unimplement   | ted: Read as 'd  | )'             |                                    |                |                    |                |  |

| bit 13-8        | RP1R<5:0>: F  | RP1 Output Pir   | n Mapping bits |                                    |                |                    |                |  |

|                 | Peripheral Ou | tput Number n    | is assigned to | pin, RP1 (see T                    | able 11-12 for | peripheral func    | tion numbers). |  |

#### REGISTER 11-23: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 5-0 | RP0R<5:0>: RP0 Output Pin Mapping bits                                                                |

|---------|-------------------------------------------------------------------------------------------------------|

|         | Peripheral Output Number n is assigned to pin, RP0 (see Table 11-12 for peripheral function numbers). |

## REGISTER 11-24: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |              |                  |           |       |  |

|------------------------------------|-------|--------------|-----------------------------------------|--------------|------------------|-----------|-------|--|

| R = Readable                       | e bit | W = Writable | bit                                     | U = Unimplen | nented bit, read | ad as '0' |       |  |

| Legend:                            |       |              |                                         |              |                  |           |       |  |

|                                    |       |              |                                         |              |                  |           |       |  |

| bit 7                              |       |              |                                         |              | •                |           | bit   |  |

| _                                  | _     | RP2R5        | RP2R4                                   | RP2R3        | RP2R2            | RP2R1     | RP2R0 |  |

| U-0                                | U-0   | R/W-0        | R/W-0                                   | R/W-0        | R/W-0            | R/W-0     | R/W-0 |  |

|                                    |       |              |                                         |              |                  |           |       |  |

| bit 15                             |       |              |                                         |              |                  |           | bit   |  |

|                                    | _     | RP3R5        | RP3R4                                   | RP3R3        | RP3R2            | RP3R1     | RP3R0 |  |

| U-0                                | U-0   | R/W-0        | R/W-0                                   | R/W-0        | R/W-0            | R/W-0     | R/W-0 |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Unimplemented: Read as '0'

Peripheral Output Number n is assigned to pin, RP3 (see Table 11-12 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP2 (see Table 11-12 for peripheral function numbers).

bit 7-6

| U-0                                                            | U-0         | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |

|----------------------------------------------------------------|-------------|------------------|--------|------------------------------------|--------|--------------------|--------|--|--|--|

|                                                                | _           | RP17R5           | RP17R4 | RP17R3                             | RP17R2 | RP17R1             | RP17R0 |  |  |  |

| bit 15                                                         |             |                  |        |                                    |        |                    | bit 8  |  |  |  |

|                                                                |             |                  |        |                                    |        |                    |        |  |  |  |

| U-0                                                            | U-0         | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |

| —                                                              | —           | RP16R5           | RP16R4 | RP16R3                             | RP16R2 | RP16R1             | RP16R0 |  |  |  |

| bit 7                                                          |             |                  |        |                                    |        |                    | bit 0  |  |  |  |

|                                                                |             |                  |        |                                    |        |                    |        |  |  |  |

| Legend:                                                        |             |                  |        |                                    |        |                    |        |  |  |  |

| R = Readable                                                   | e bit       | W = Writable I   | oit    | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

| -n = Value at                                                  | POR         | '1' = Bit is set |        | '0' = Bit is clea                  | ared   | x = Bit is unknown |        |  |  |  |

|                                                                |             |                  |        |                                    |        |                    |        |  |  |  |

| bit 15-14                                                      | Unimplement | ted: Read as 'd  | )'     |                                    |        |                    |        |  |  |  |

| bit 13-8 <b>RP17R&lt;5:0&gt;:</b> RP17 Output Pin Mapping bits |             |                  |        |                                    |        |                    |        |  |  |  |

### REGISTER 11-31: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| bit 7-6 | Unimplemented: Read as '0'                                                                             |

|---------|--------------------------------------------------------------------------------------------------------|

| bit 5-0 | RP16R<5:0>: RP16 Output Pin Mapping bits                                                               |

|         | Peripheral Output Number n is assigned to pin, RP16 (see Table 11-12 for peripheral function numbers). |

Peripheral Output Number n is assigned to pin, RP17 (see Table 11-12 for peripheral function numbers).

## REGISTER 11-32: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0                                | U-0   | R/W-0        | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |  |

|------------------------------------|-------|--------------|--------|-----------------------------------------|--------|--------|--------|--|

|                                    | —     | RP19R5       | RP19R4 | RP19R3                                  | RP19R2 | RP19R1 | RP19R0 |  |

| bit 15                             |       |              |        |                                         |        |        | bit 8  |  |

|                                    |       |              |        |                                         |        |        |        |  |

| U-0                                | U-0   | R/W-0        | R/W-0  | R/W-0                                   | R/W-0  | R/W-0  | R/W-0  |  |

| —                                  | —     | RP18R5       | RP18R4 | RP18R3                                  | RP18R2 | RP18R1 | RP18R0 |  |

| bit 7                              |       |              |        |                                         |        |        | bit 0  |  |

|                                    |       |              |        |                                         |        |        |        |  |

| Legend:                            |       |              |        |                                         |        |        |        |  |

| R = Readable                       | e bit | W = Writable | bit    | U = Unimplemented bit, read as '0'      |        |        |        |  |

| -n = Value at POR '1' = Bit is set |       |              |        | '0' = Bit is cleared x = Bit is unknown |        |        |        |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP19R<5:0>:** RP19 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP19 (see Table 11-12 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP18R<5:0>:** RP18 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP18 (see Table 11-12 for peripheral function numbers).

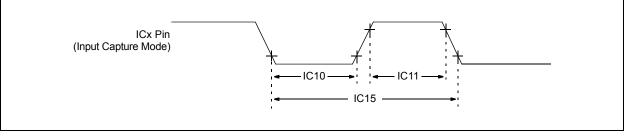

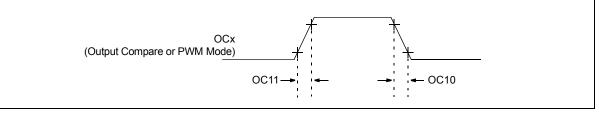

### REGISTER 14-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

- bit 3-0 MOD<3:0>: CCPx Mode Select bits

- For CCSEL = 1 (Input Capture Modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

- For CCSEL = 0 (Output Compare/Timer Modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Variable Frequency Pulse mode

- 0110 = Center-Aligned Pulse Compare mode, buffered

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode, toggles output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode, drives output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode, drives output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

#### TABLE 14-5: CLC CLOCK SOURCE SELECTION (CLKSEL<2:0> = 011)

| MCCPx/SCCPx Module          | MCCP1 | SCCP2 | SCCP3 | SCCP4 | SCCP5 | SCCP6 | SCCP7 |

|-----------------------------|-------|-------|-------|-------|-------|-------|-------|

| CLC Module for Clock Source | 1     | 2     | 3     | 1     | 2     | 3     | 4     |

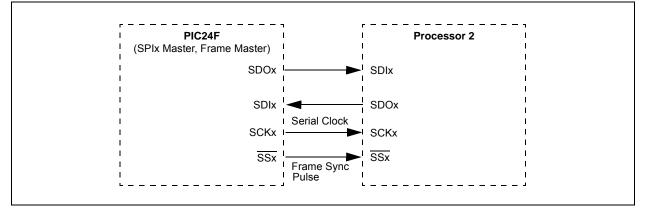

### FIGURE 17-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

BDs have a fixed relationship to a particular endpoint, depending on the buffering configuration. Table 20-2 provides the mapping of BDs to endpoints. This relationship also means that gaps may occur in the BDT if endpoints are not enabled contiguously. This, theoretically, means that the BDs for disabled endpoints could be used as buffer space. In practice, users should avoid using such spaces in the BDT unless a method of validating BD addresses is implemented.

### 20.2.1 BUFFER OWNERSHIP

Because the buffers and their BDs are shared between the CPU and the USB module, a simple semaphore mechanism is used to distinguish which is allowed to update the BD and associated buffers in memory. This is done by using the UOWN bit as a semaphore to distinguish which is allowed to update the BD and associated buffers in memory. UOWN is the only bit that is shared between the two configurations of BDnSTAT.

When UOWN is clear, the BD entry is "owned" by the microcontroller core. When the UOWN bit is set, the BD entry and the buffer memory are "owned" by the USB peripheral. The core should not modify the BD or its

corresponding data buffer during this time. Note that the microcontroller core can still read BDnSTAT while the SIE owns the buffer and vice versa.

The Buffer Descriptors have a different meaning based on the source of the register update. Register 20-1 and Register 20-2 show the differences in BDnSTAT depending on its current "ownership".

When UOWN is set, the user can no longer depend on the values that were written to the BDs. From this point, the USB module updates the BDs as necessary, overwriting the original BD values. The BDnSTAT register is updated by the SIE with the token PID and the transfer count is updated.

## 20.2.2 DMA INTERFACE

The USB OTG module uses a dedicated DMA to access both the BDT and the endpoint data buffers. Since part of the address space of the DMA is dedicated to the Buffer Descriptors, a portion of the memory connected to the DMA must comprise a contiguous address space, properly mapped for the access by the module.

|          |                |                 |                     | BDs Ass             | signed to Endpoi  | int            |                |                                   |  |  |  |  |  |

|----------|----------------|-----------------|---------------------|---------------------|-------------------|----------------|----------------|-----------------------------------|--|--|--|--|--|

| Endpoint | Moo<br>(No Pin | de 0<br>g-Pong) | Moo<br>(Ping-Pong o | de 1<br>on EP0 OUT) | Mod<br>(Ping-Pong |                | (Ping-Pong     | de 3<br>on All Other<br>cept EP0) |  |  |  |  |  |

|          | Out            | In              | Out                 | In                  | Out               | In             | Out            | In                                |  |  |  |  |  |

| 0        | 0              | 1               | 0 (E), 1 (O)        | 2                   | 0 (E), 1 (O)      | 2 (E), 3 (O)   | 0              | 1                                 |  |  |  |  |  |

| 1        | 2              | 3               | 3                   | 4                   | 4 (E), 5 (O)      | 6 (E), 7 (O)   | 2 (E), 3 (O)   | 4 (E), 5 (O)                      |  |  |  |  |  |

| 2        | 4              | 5               | 5                   | 6                   | 8 (E), 9 (O)      | 10 (E), 11 (O) | 6 (E), 7 (O)   | 8 (E), 9 (O)                      |  |  |  |  |  |

| 3        | 6              | 7               | 7                   | 8                   | 12 (E), 13 (O)    | 14 (E), 15 (O) | 10 (E), 11 (O) | 12 (E), 13 (O)                    |  |  |  |  |  |

| 4        | 8              | 9               | 9                   | 10                  | 16 (E), 17 (O)    | 18 (E), 19 (O) | 14 (E), 15 (O) | 16 (E), 17 (O)                    |  |  |  |  |  |

| 5        | 10             | 11              | 11                  | 12                  | 20 (E), 21 (O)    | 22 (E), 23 (O) | 18 (E), 19 (O) | 20 (E), 21 (O)                    |  |  |  |  |  |

| 6        | 12             | 13              | 13                  | 14                  | 24 (E), 25 (O)    | 26 (E), 27 (O) | 22 (E), 23 (O) | 24 (E), 25 (O)                    |  |  |  |  |  |

| 7        | 14             | 15              | 15                  | 16                  | 28 (E), 29 (O)    | 30 (E), 31 (O) | 26 (E), 27 (O) | 28 (E), 29 (O)                    |  |  |  |  |  |

| 8        | 16             | 17              | 17                  | 18                  | 32 (E), 33 (O)    | 34 (E), 35 (O) | 30 (E), 31 (O) | 32 (E), 33 (O)                    |  |  |  |  |  |

| 9        | 18             | 19              | 19                  | 20                  | 36 (E), 37 (O)    | 38 (E), 39 (O) | 34 (E), 35 (O) | 36 (E), 37 (O)                    |  |  |  |  |  |

| 10       | 20             | 21              | 21                  | 22                  | 40 (E), 41 (O)    | 42 (E), 43 (O) | 38 (E), 39 (O) | 40 (E), 41 (O)                    |  |  |  |  |  |

| 11       | 22             | 23              | 23                  | 24                  | 44 (E), 45 (O)    | 46 (E), 47 (O) | 42 (E), 43 (O) | 44 (E), 45 (O)                    |  |  |  |  |  |

| 12       | 24             | 25              | 25                  | 26                  | 48 (E), 49 (O)    | 50 (E), 51 (O) | 46 (E), 47 (O) | 48 (E), 49 (O)                    |  |  |  |  |  |

| 13       | 26             | 27              | 27                  | 28                  | 52 (E), 53 (O)    | 54 (E), 55 (O) | 50 (E), 51 (O) | 52 (E), 53 (O)                    |  |  |  |  |  |

| 14       | 28             | 29              | 29                  | 30                  | 56 (E), 57 (O)    | 58 (E), 59 (O) | 54 (E), 55 (O) | 56 (E), 57 (O)                    |  |  |  |  |  |

| 15       | 30             | 31              | 31                  | 32                  | 60 (E), 61 (O)    | 62 (E), 63 (O) | 58 (E), 59 (O) | 60 (E), 61 (O)                    |  |  |  |  |  |

## TABLE 20-2: ASSIGNMENT OF BUFFER DESCRIPTORS FOR THE DIFFERENT BUFFERING MODES

**Legend:** (E) = Even transaction buffer, (O) = Odd transaction buffer

### REGISTER 20-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0                    | U-0                                                                    | U-0                                    | U-0                                 | U-0                                                                           | U-0            | U-0            | U-0   |  |  |  |

|------------------------|------------------------------------------------------------------------|----------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|----------------|----------------|-------|--|--|--|

| _                      | —                                                                      | —                                      | —                                   | —                                                                             | —              | —              | _     |  |  |  |

| bit 15                 |                                                                        |                                        |                                     |                                                                               |                |                | bit 8 |  |  |  |

|                        |                                                                        |                                        |                                     |                                                                               |                |                |       |  |  |  |

| R/W-0                  | R/W-0                                                                  | U-0                                    | R/W-0                               | U-0                                                                           | U-0            | R/W-0          | R/W-0 |  |  |  |

| UTEYE                  | UOEMON <sup>(1)</sup>                                                  |                                        | USBSIDL                             | —                                                                             | —              | PPB1           | PPB0  |  |  |  |

| bit 7                  |                                                                        |                                        |                                     |                                                                               |                |                | bit   |  |  |  |

|                        |                                                                        |                                        |                                     |                                                                               |                |                |       |  |  |  |

| Legend:<br>R = Readabl | le hit                                                                 | W = Writable                           | hit                                 | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                |                |       |  |  |  |

| -n = Value at          |                                                                        | '1' = Bit is set                       |                                     | •                                                                             | •              |                |       |  |  |  |

|                        | IFUR                                                                   |                                        |                                     |                                                                               | areu           |                | IOWIT |  |  |  |

| bit 15-8               | Unimplemen                                                             | ted: Read as                           | 0'                                  |                                                                               |                |                |       |  |  |  |

| bit 7                  | •                                                                      | UTEYE: USB Eye Pattern Test Enable bit |                                     |                                                                               |                |                |       |  |  |  |

| SIC 1                  | 1 = Eye pattern test is enabled                                        |                                        |                                     |                                                                               |                |                |       |  |  |  |

|                        | 0 = Eye pattern test is disabled                                       |                                        |                                     |                                                                               |                |                |       |  |  |  |

| bit 6                  | UOEMON: USB OE Monitor Enable bit <sup>(1)</sup>                       |                                        |                                     |                                                                               |                |                |       |  |  |  |

|                        | $1 = \overline{OE} \text{ signa}$<br>$0 = \overline{OE} \text{ signa}$ |                                        | dicates interval                    | s during which                                                                | the D+/D- line | es are driving |       |  |  |  |

| bit 5                  | Unimplemen                                                             | ted: Read as '                         | 0'                                  |                                                                               |                |                |       |  |  |  |

| bit 4                  | USBSIDL: US                                                            | SB OTG Stop i                          | n Idle Mode bit                     |                                                                               |                |                |       |  |  |  |

|                        |                                                                        |                                        | peration when t<br>ation in Idle mo | he device enter<br>de                                                         | rs Idle mode   |                |       |  |  |  |

| bit 3-2                | Unimplemen                                                             | ted: Read as '                         | 0'                                  |                                                                               |                |                |       |  |  |  |

| bit 1-0                | <b>PPB&lt;1:0&gt;:</b> P                                               | ing-Pong Buffe                         | ers Configuratio                    | on bits                                                                       |                |                |       |  |  |  |

|                        |                                                                        |                                        |                                     | abled for Endpo                                                               |                |                |       |  |  |  |

|                        |                                                                        |                                        |                                     | abled for all end                                                             |                |                |       |  |  |  |

|                        |                                                                        |                                        | Buffers are ena<br>Buffers are dis  | abled for OUT E<br>abled                                                      | inapoint u     |                |       |  |  |  |

|                        |                                                                        | a ing i ong                            |                                     |                                                                               |                |                |       |  |  |  |

Note 1: This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

## REGISTER 20-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| STALLIF   | —   | RESUMEIF  | IDLEIF    | TRNIF     | SOFIF     | UERRIF    | URSTIF    |

| bit 7     |     |           |           |           |           |           | bit 0     |

| Legend:          | HS = Hardware Settable b   | HS = Hardware Settable bit            |  |  |  |  |  |

|------------------|----------------------------|---------------------------------------|--|--|--|--|--|

| R = Readable bit | K = Write '1' to Clear bit | U = Unimplemented bit, read as '0'    |  |  |  |  |  |

| -n = Value at PO | R '1' = Bit is set         | '1' = Bit is set '0' = Bit is cleared |  |  |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                                                                                                                                          |

|          | <ul> <li>1 = A STALL handshake was sent by the peripheral during the handshake phase of the transaction in<br/>Device mode</li> <li>0 = A STALL handshake has not been sent</li> </ul>                                                                                                                                                          |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 5    | RESUMEIF: Resume Interrupt bit                                                                                                                                                                                                                                                                                                                  |

| bito     | <ul> <li>1 = A K-state is observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed)</li> <li>0 = No K-state is observed</li> </ul>                                                                                                                                                              |

| bit 4    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                                                                                                                                                                               |

|          | <ul> <li>1 = Idle condition is detected (constant Idle state of 3 ms or more)</li> <li>0 = No Idle condition is detected</li> </ul>                                                                                                                                                                                                             |

| bit 3    | TRNIF: Token Processing Complete Interrupt bit                                                                                                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Processing of the current token is complete; read the U1STAT register for endpoint information</li> <li>0 = Processing of the current token is not complete; clear the U1STAT register or load the next token from STAT (clearing this bit causes the STAT FIFO to advance)</li> </ul>                                             |

| bit 2    | SOFIF: Start-of-Frame Token Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | 1 = A Start-of-Frame token is received by the peripheral or the Start-of-Frame threshold is reached by<br>the host                                                                                                                                                                                                                              |

|          | 0 = No Start-of-Frame token is received or threshold reached                                                                                                                                                                                                                                                                                    |

| bit 1    | UERRIF: USB Error Condition Interrupt bit                                                                                                                                                                                                                                                                                                       |

|          | <ul> <li>1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set<br/>this bit</li> </ul>                                                                                                                                                                                                          |

|          | 0 = No unmasked error condition has occurred                                                                                                                                                                                                                                                                                                    |

| bit 0    | URSTIF: USB Reset Interrupt bit                                                                                                                                                                                                                                                                                                                 |

|          | 1 = Valid USB Reset has occurred for at least 2.5 μs; Reset state must be cleared before this bit can be reasserted                                                                                                                                                                                                                             |

|          | <ul> <li>0 = No USB Reset has occurred; individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared</li> </ul> |

|          | Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause                                                                                                                |

all set bits, at the moment of the write, to become cleared.

| R/W-0                                                                     | R/W-0                                                              | R/W-0                                                                                                                                                                                              | r-0            | R/W-0             | R/W-0                      | U-0                 | U-0           |  |  |  |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|----------------------------|---------------------|---------------|--|--|--|--|