Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb410t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TADLE 1-4:    | 1             | n/Pad Numl             |       |     |                |                           |

|---------------|---------------|------------------------|-------|-----|----------------|---------------------------|

| Pin Function  |               | 64-Pin 100-Pin 121-Pin |       |     | Input Buffer   | Description               |

|               | TQFP          | TQFP                   | TFBGA | I/O | input Builer   |                           |

| IOCD0         | 46            | 72                     | D9    | I   | ST             | PORTD Interrupt-on-Change |

| IOCD1         | 49            | 76                     | A11   | I   | ST             |                           |

| IOCD2         | 50            | 77                     | A10   | I   | ST             |                           |

| IOCD3         | 51            | 78                     | B9    | I   | ST             |                           |

| IOCD4         | 52            | 81                     | C8    | I   | ST             |                           |

| IOCD5         | 53            | 82                     | B8    | I   | ST             |                           |

| IOCD6         | 54            | 83                     | D7    | I   | ST             |                           |

| IOCD7         | 55            | 84                     | C7    | I   | ST             |                           |

| IOCD8         | 42            | 68                     | E9    | I   | ST             |                           |

| IOCD9         | 43            | 69                     | E10   | I   | ST             |                           |

| IOCD10        | 44            | 70                     | D11   | I   | ST             |                           |

| IOCD11        | 45            | 71                     | C11   | I   | ST             |                           |

| IOCD12        | —             | 79                     | A9    | I   | ST             |                           |

| IOCD13        | —             | 80                     | D8    | I   | ST             |                           |

| IOCD14        | —             | 47                     | L9    | I   | ST             |                           |

| IOCD15        | —             | 48                     | K9    | I   | ST             |                           |

| IOCE0         | 60            | 93                     | 1E3   | I   | ST             | PORTE Interrupt-on-Change |

| IOCE1         | 61            | 94                     | E15   | I   | ST             |                           |

| IOCE2         | 62            | 98                     | E19   | I   | ST             |                           |

| IOCE3         | 63            | 99                     | E30   | I   | ST             |                           |

| IOCE4         | 64            | 100                    | E31   | I   | ST             |                           |

| IOCE5         | 1             | 3                      | D3    | I   | ST             |                           |

| IOCE6         | 2             | 4                      | C1    | I   | ST             |                           |

| IOCE7         | 3             | 5                      | D2    | I   | ST             |                           |

| IOCE8         | —             | 18                     | G1    | I   | ST             |                           |

| IOCE9         | —             | 19                     | G2    | I   | ST             |                           |

| IOCF0         | 58            | 87                     | B6    | I   | ST             | PORTF Interrupt-on-Change |

| IOCF1         | 59            | 88                     | A6    | I   | ST             |                           |

| IOCF2         | 34            | 52                     | K11   | I   | ST             |                           |

| IOCF3         | 33            | 51                     | K10   | I   | ST             |                           |

| IOCF4         | 31            | 49                     | L10   | I   | ST             |                           |

| IOCF5         | 32            | 50                     | L11   | I   | ST             |                           |

| IOCF6         | 35            | 55                     | H9    | I   | ST             |                           |

| IOCF7         | _             | 54                     | H8    | I   | ST             |                           |

| IOCF8         | —             | 53                     | J10   | I   | ST             |                           |

| IOCF12        | —             | 40                     | K6    | I   | ST             |                           |

| IOCF13        | _             | 39                     | L6    | I   | ST             |                           |

| Legend: TTL = | TTL input buf | fer                    |       |     | ST = Schmitt T | rigger input buffer       |

### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

| TABLE 1-J.   | 1              | 0000412         |                  |     |              |                                                     |

|--------------|----------------|-----------------|------------------|-----|--------------|-----------------------------------------------------|

|              | Pin            | /Pad Numl       | ber              |     |              |                                                     |

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                                         |

| PMA8         | 32             | 50              | L11              | I/O | DIG/ST/TTL   | Parallel Master Port Address (Demultiplexed         |

| PMA9         | 31             | 49              | L10              | I/O | DIG/ST/TTL   | Master mode) or Address/Data (Multiplexed           |

| PMA10        | 28             | 42              | L7               | I/O | DIG/ST/TTL   | Master modes)                                       |

| PMA11        | 27             | 41              | J7               | I/O | DIG/ST/TTL   |                                                     |

| PMA12        | 24             | 35              | K5               | I/O | DIG/ST/TTL   |                                                     |

| PMA13        | 23             | 34              | H5               | I/O | DIG/ST/TTL   |                                                     |

| PMA16        | _              | 95              | C4               | 0   | DIG          |                                                     |

| PMA17        | _              | 92              | B5               | 0   | DIG          |                                                     |

| PMA18        | _              | 40              | K6               | 0   | DIG          |                                                     |

| PMA19        | _              | 19              | G2               | 0   | DIG          |                                                     |

| PMA2/PMALU   | 8              | 14              | F3               | 0   | DIG          | Parallel Master Port Address<2>/Address Latch Upper |

| PMA3         | 6              | 12              | F2               | 0   | DIG          | Parallel Master Port Address                        |

| PMA4         | 5              | 11              | F4               | 0   | DIG          |                                                     |

| PMA5         | 4              | 10              | E3               | 0   | DIG          |                                                     |

| PMA20        | —              | 59              | G10              | 0   | DIG          | Parallel Master Port Address (Demultiplexed         |

| PMA21        | —              | 60              | G11              | 0   | DIG          | Master mode) or Address/Data (Multiplexed           |

| PMA22        | —              | 66              | E11              | 0   | DIG          | Master modes)                                       |

| PMACK1       | 50             | 77              | A10              | I   | ST/TTL       | Parallel Master Port Acknowledge Input 1            |

| PMACK2       | 43             | 69              | E10              | I   | ST/TTL       | Parallel Master Port Acknowledge Input 2            |

| PMBE0        | 51             | 78              | B9               | 0   | DIG          | Parallel Master Port Byte Enable 0 Strobe           |

| PMBE1        | —              | 67              | E8               | 0   | DIG          | Parallel Master Port Byte Enable 1 Strobe           |

| PMCS1        | —              | 18              | G1               | 0   | DIG          | Parallel Master Port Chip Select 1 Strobe           |

| PMCS2        | —              | 9               | E!               | 0   | DIG          | Parallel Master Port Chip Select 2 Strobe           |

| PMD0         | 60             | 93              | A4               | I/O | DIG/ST/TTL   | Parallel Master Port Data (Demultiplexed            |

| PMD1         | 61             | 94              | B4               | I/O | DIG/ST/TTL   | Master mode) or Address/Data (Multiplexed           |

| PMD2         | 62             | 98              | B3               | I/O | DIG/ST/TTL   | Master modes)                                       |

| PMD3         | 63             | 99              | A2               | I/O | DIG/ST/TTL   |                                                     |

| PMD4         | 64             | 100             | A1               | I/O | DIG/ST/TTL   |                                                     |

| PMD5         | 1              | 3               | D3               | I/O | DIG/ST/TTL   |                                                     |

| PMD6         | 2              | 4               | C1               | I/O | DIG/ST/TTL   |                                                     |

| PMD7         | 3              | 5               | D2               | I/O | DIG/ST/TTL   |                                                     |

| PMD8         | —              | 90              | A5               | I/O | DIG/ST/TTL   |                                                     |

| PMD9         | —              | 89              | E6               | I/O | DIG/ST/TTL   |                                                     |

| PMD10        | _              | 88              | A6               | I/O | DIG/ST/TTL   |                                                     |

| PMD11        | _              | 87              | B6               | I/O | DIG/ST/TTL   |                                                     |

| PMD12        | —              | 79              | A9               | I/O | DIG/ST/TTL   |                                                     |

| PMD13        | _              | 80              | D8               | I/O | DIG/ST/TTL   |                                                     |

| PMD14        | _              | 83              | D7               | I/O | DIG/ST/TTL   |                                                     |

| PMD15        | _              | 84              | C7               | I/O | DIG/ST/TTL   |                                                     |

# TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

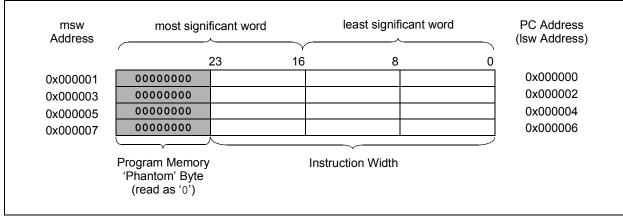

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 000000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVTs). The main IVT has a static location, from 000004h to 0000FFh. The Alternate IVT has a configurable location and is optionally enabled. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 8.0 "Interrupt Controller"**.

# 4.1.3 SINGLE AND DUAL PARTITION MEMORY ORGANIZATION

The PIC24FJ256GA412/GB412 family of devices supports a Single Partition Flash mode and two Dual Partition Flash modes. The Dual Partition modes allow the device to be programmed with two separate applications to facilitate bootloading or to allow an application to be programmed at run-time without stalling the CPU.

In the Dual Partition modes, the device's memory is divided evenly into two physical sections, known as Partition 1 and Partition 2. Each of these partitions contains its own program memory and Configuration Words. During program execution, the code on only one of these panels is executed; this is the Active Partition. The other partition, or the Inactive Partition, is not used, but can be programmed.

The Active Partition is always mapped to logical address, 000000h, while the Inactive Partition will always be mapped to logical address, 400000h. Note that even when the code partitions are switched between active and inactive by the user, the address of the Active Partition will still be 000000h and the address of the Inactive Partition will still be at 400000h. Figure 4-3 compares the mapping of the user memory space in Single and Dual Partition devices.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| Register     | Address  | All Resets                              | Register                 | Address | All Resets                              | Register              | Address | All Resets                              |

|--------------|----------|-----------------------------------------|--------------------------|---------|-----------------------------------------|-----------------------|---------|-----------------------------------------|

| DMA (Continu | ued)     |                                         | CRYTXTB6                 | 564     | *****                                   | U1EP8 <sup>(1)</sup>  | 5B2     | 000000000000000000000000000000000000000 |

| DMAINT5      | 500      | 000000000000000000000000000000000000000 | CRYTXTB7                 | 566     | *****                                   | U1EP9 <sup>(1)</sup>  | 5B4     | 000000000000000000000000000000000000000 |

| DMASRC5      | 502      | 000000000000000000000000000000000000000 | CRYTXTC0                 | 558     | *****                                   | U1EP10 <sup>(1)</sup> | 5B6     | 000000000000000000000000000000000000000 |

| DMADST5      | 504      | 000000000000000000000000000000000000000 | CRYTXTC1                 | 56A     | *****                                   | U1EP11 <sup>(1)</sup> | 5B8     | 000000000000000000                      |

| DMACNT5      | 506      | 000000000000000000000000000000000000000 | CRYTXTC2                 | 56C     | *****                                   | U1EP12 <sup>(1)</sup> | 5BA     | 000000000000000000000000000000000000000 |

| Cryptographi | c Engine |                                         | CRYTXTC3                 | 56E     | *****                                   | U1EP13 <sup>(1)</sup> | 5BC     | 000000000000000000000000000000000000000 |

| CRYCONL      | 51C      | x0xxxx0xxxxxxxxx                        | CRYTXTC4                 | 570     | *****                                   | U1EP14 <sup>(1)</sup> | 5BE     | 000000000000000000000000000000000000000 |

| CRYCONH      | 51E      | 0xxxxxxxx0xxxx                          | CRYTXTC5                 | 572     | *****                                   | U1EP15 <sup>(1)</sup> | 5C0     | 000000000000000000000000000000000000000 |

| CRYSTAT      | 520      | 00000000xxxx0xxx                        | CRYTXTC6                 | 574     | *****                                   | LCD Controll          | er      |                                         |

| CRYOTP       | 524      | 00000000xxxxxxxx                        | CRYTXTC7                 | 576     | *****                                   | LCDCON                | 5C2     | 00000000000000000000(2)                 |

| CRYKEY0      | 528      | *****                                   | USB                      |         |                                         | LCDREF                | 5C4     | 00000000000000000000(2)                 |

| CRYKEY1      | 52A      | ****                                    | U1OTGIR <sup>(1)</sup>   | 578     | 000000000000000000000000000000000000000 | LCDPS                 | 5C6     | 0000000000000000000(2)                  |

| CRYKEY2      | 52C      | *****                                   | U1OTGIE <sup>(1)</sup>   | 57A     | 000000000000000000000000000000000000000 | LCDDATA0              | 5C8     | 0000000000000000000000(2)               |

| CRYKEY3      | 52E      | *****                                   | U1OTGSTAT <sup>(1)</sup> | 57C     | 000000000000000000000000000000000000000 | LCDDATA1              | 5CA     | 00000000000000000000(2)                 |

| CRYKEY4      | 530      | *****                                   | U1OTGCON <sup>(1)</sup>  | 57E     | 000000000000000000000000000000000000000 | LCDDATA2              | 5CC     | 00000000000000000000(2)                 |

| CRYKEY5      | 532      | *****                                   | U1PWRC <sup>(1)</sup>    | 580     | 0000000x0000000                         | LCDDATA3              | 5CE     | 0000000000000000000000(2)               |

| CRYKEY6      | 534      | *****                                   | U1IR <sup>(1)</sup>      | 582     | 000000000000000000000000000000000000000 | LCDDATA4              | 5D0     | 000000000000000000000(2)                |

| CRYKEY7      | 536      | *****                                   | U1IE <sup>(1)</sup>      | 584     | 000000000000000000000000000000000000000 | LCDDATA5              | 5D2     | 000000000000000000000(2)                |

| CRYKEY8      | 538      | *****                                   | U1EIR <sup>(1)</sup>     | 586     | 000000000000000000000000000000000000000 | LCDDATA6              | 5D4     | 0000000000000000000000(2)               |

| CRYKEY9      | 53A      | ****                                    | U1EIE <sup>(1)</sup>     | 588     | 000000000000000000000000000000000000000 | LCDDATA7              | 5D6     | 0000000000000000000000(2)               |

| CRYKEY10     | 53C      | ****                                    | U1STAT <sup>(1)</sup>    | 58A     | 000000000000000000000000000000000000000 | LCDDATA8              | 5D8     | 00000000000000000000(2)                 |

| CRYKEY11     | 53E      | ****                                    | U1CON <sup>(1)</sup>     | 58C     | 0000000xx000000                         | LCDDATA9              | 5DA     | 000000000000000000000000000000000000000 |

| CRYKEY12     | 540      | ****                                    | U1ADDR <sup>(1)</sup>    | 58E     | 000000000xxxxxxx                        | LCDDATA10             | 5DC     | 0000000000000000000000(2)               |

| CRYKEY13     | 542      | ****                                    | U1BDTP1 <sup>(1)</sup>   | 590     | 000000000000000000000000000000000000000 | LCDDATA11             | 5DE     | 00000000000000000000000(2)              |

| CRYKEY14     | 544      | ****                                    | U1FRML <sup>(1)</sup>    | 592     | 000000000000000000000000000000000000000 | LCDDATA12             | 5E0     | 00000000000000000000(2)                 |

| CRYKEY15     | 546      | ****                                    | U1FRMH <sup>(1)</sup>    | 594     | 000000000000000000000000000000000000000 | LCDDATA13             | 5E2     | 00000000000000000000(2)                 |

| CRYTXTA0     | 548      | ****                                    | U1TOK <sup>(1)</sup>     | 596     | 000000000000000000000000000000000000000 | LCDDATA14             | 5E4     | 0000000000000000000000(2)               |

| CRYTXTA1     | 54A      | ****                                    | U1SOF <sup>(1)</sup>     | 598     | 000000000000000000000000000000000000000 | LCDDATA15             | 5E6     | 0000000000000000000000(2)               |

| CRYTXTA2     | 54C      | ****                                    | U1BDTP2 <sup>(1)</sup>   | 59A     | 000000000000000000000000000000000000000 | LCDDATA16             | 5E8     | 0000000000000000000000(2)               |

| CRYTXTA3     | 54E      | ****                                    | U1BDTP3 <sup>(1)</sup>   | 59C     | 000000000000000000000000000000000000000 | LCDDATA17             | 5EA     | 00000000000000000000(2)                 |

| CRYTXTA4     | 550      | ****                                    | U1CNFG1 <sup>(1)</sup>   | 59E     | 000000000000000000000000000000000000000 | LCDDATA18             | 5EC     | 00000000000000000000(2)                 |

| CRYTXTA5     | 552      | ****                                    | U1CNFG2 <sup>(1)</sup>   | 5A0     | 000000000000000000000000000000000000000 | LCDDATA19             | 5EE     | 00000000000000000000(2)                 |

| CRYTXTA6     | 554      | ****                                    | U1EP0 <sup>(1)</sup>     | 5A2     | 000000000000000000000000000000000000000 | LCDDATA20             | 5F0     | 000000000000000000000(2)                |

| CRYTXTA7     | 556      | ****                                    | U1EP1 <sup>(1)</sup>     | 5A4     | 000000000000000000000000000000000000000 | LCDDATA21             | 5F2     | 000000000000000000000(2)                |

| CRYTXTB0     | 558      | *****                                   | U1EP2 <sup>(1)</sup>     | 5A6     | 000000000000000000000000000000000000000 | LCDDATA22             | 5F4     | 00000000000000000000(2)                 |

| CRYTXTB1     | 55A      | ****                                    | U1EP3 <sup>(1)</sup>     | 5A8     | 000000000000000000000000000000000000000 | LCDDATA23             | 5F6     | 00000000000000000000(2)                 |

| CRYTXTB2     | 55C      | ****                                    | U1EP4 <sup>(1)</sup>     | 5AA     | 000000000000000000000000000000000000000 | LCDDATA24             | 5F8     | 000000000000000000000000000000000000000 |

| CRYTXTB3     | 55E      | ****                                    | U1EP5 <sup>(1)</sup>     | 5AC     | 000000000000000000000000000000000000000 | LCDDATA25             | 5FA     | 00000000000000000000(2)                 |

| CRYTXTB4     | 560      | ****                                    | U1EP6 <sup>(1)</sup>     | 5AE     | 000000000000000000000000000000000000000 | LCDDATA26             | 5FC     | 00000000000000000000(2)                 |

| CRYTXTB5     | 562      | ****                                    | U1EP7 <sup>(1)</sup>     | 5B0     | 000000000000000000000000000000000000000 | LCDDATA27             | 5FE     | 000000000000000000(2)                   |

### TABLE 4-10:SFR BLOCK 500h

**Legend:** x = unknown or indeterminate value. Reset and address values are in hexadecimal.

Note 1: Implemented in PIC24FJXXXGB4XX devices only.

2: LCD registers are only reset on a device POR.

## REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| •      |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(1)</sup> | —   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit     |                    |  |  |

|-------------------|------------------|-----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |  |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-2 for bit description.

| U-0                 | R/W-1                                                                                                                                           | R/W-0                                                                                                                                                                                                                        | R/W-0                                                                                     | U-0                       | R/W-1            | R/W-0           | R/W-0    |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------|------------------|-----------------|----------|

| —                   | MI2C3IP2                                                                                                                                        | MI2C3IP1                                                                                                                                                                                                                     | MI2C3IP0                                                                                  |                           | SI2C3IP2         | SI2C3IP1        | SI2C3IP0 |

| bit 15              |                                                                                                                                                 | •                                                                                                                                                                                                                            | 1                                                                                         |                           |                  | I               | bit 8    |

|                     |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 |          |

| U-0                 | U-0                                                                                                                                             | U-0                                                                                                                                                                                                                          | U-0                                                                                       | U-0                       | U-0              | U-0             | U-0      |

| _                   | —                                                                                                                                               | —                                                                                                                                                                                                                            | _                                                                                         |                           |                  | _               | _        |

| bit 7               |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 | bit 0    |

|                     |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 |          |

| Legend:             |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 |          |

| R = Readabl         | e bit                                                                                                                                           | W = Writable                                                                                                                                                                                                                 | bit                                                                                       | •                         | mented bit, read | d as '0'        |          |

| -n = Value at       | POR                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                             |                                                                                           | '0' = Bit is cle          | ared             | x = Bit is unkn | iown     |

|                     |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 |          |

|                     |                                                                                                                                                 |                                                                                                                                                                                                                              |                                                                                           |                           |                  |                 |          |

| bit 15              | -                                                                                                                                               | ted: Read as '                                                                                                                                                                                                               |                                                                                           |                           |                  |                 |          |

|                     | MI2C3IP<2:0                                                                                                                                     | >: Master I2C3                                                                                                                                                                                                               | Event Interrup                                                                            | •                         |                  |                 |          |

| bit 15<br>bit 14-12 | MI2C3IP<2:0                                                                                                                                     |                                                                                                                                                                                                                              | Event Interrup                                                                            | •                         |                  |                 |          |

|                     | MI2C3IP<2:0                                                                                                                                     | >: Master I2C3                                                                                                                                                                                                               | Event Interrup                                                                            | •                         |                  |                 |          |

|                     | MI2C3IP<2:0                                                                                                                                     | >: Master I2C3                                                                                                                                                                                                               | Event Interrup                                                                            | •                         |                  |                 |          |

|                     | MI2C3IP<2:0<br>111 = Interru                                                                                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1                                                                                                                                                                     | Event Interrup                                                                            | •                         |                  |                 |          |

| bit 14-12           | MI2C3IP<2:0<br>111 = Interru                                                                                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                                                                                                 | Event Interrup<br>highest priority<br>abled                                               | •                         |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen                                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                                                                                                       | Event Interrup<br>highest priority<br>abled                                               | r interrupt)              |                  |                 |          |

| bit 14-12           | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: Slave I2C3 E                                                                                                           | Event Interrup<br>highest priority<br>abled                                               | <sup>o</sup> riority bits |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                                                                                                       | Event Interrup<br>highest priority<br>abled                                               | <sup>o</sup> riority bits |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: Slave I2C3 E                                                                                                           | Event Interrup<br>highest priority<br>abled                                               | <sup>o</sup> riority bits |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:                                                    | >: Master I2C3<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: Slave I2C3 E                                                                                                           | Event Interrup<br>highest priority<br>abled                                               | <sup>o</sup> riority bits |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:<br>111 = Interru<br>001 = Interru                  | <ul> <li>&gt;: Master I2C3</li> <li>pt is Priority 7 (</li> <li>pt is Priority 1</li> <li>pt source is dis</li> <li>ted: Read as '(</li> <li>: Slave I2C3 E</li> <li>pt is Priority 7 (</li> <li>pt is Priority 1</li> </ul> | Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt F<br>highest priority | <sup>o</sup> riority bits |                  |                 |          |

| bit 14-12<br>bit 11 | MI2C3IP<2:0<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>SI2C3IP<2:0:<br>111 = Interru<br>001 = Interru<br>001 = Interru | <ul> <li>&gt;: Master I2C3</li> <li>pt is Priority 7 (</li> <li>pt is Priority 1</li> <li>pt source is dis</li> <li>ted: Read as '(</li> <li>&gt;: Slave I2C3 E</li> <li>pt is Priority 7 (</li> </ul>                       | Event Interrup<br>highest priority<br>abled<br>b<br>twent Interrupt F<br>highest priority | <sup>o</sup> riority bits |                  |                 |          |

| U-0          | R/W-1               | R/W-0                                 | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |

|--------------|---------------------|---------------------------------------|-------------------|------------------|-----------------|-----------------|---------|--|--|

| —            | SPI3TXIP2           | SPI3TXIP1                             | SPI3TXIP0         | —                | SPI3IP2         | SPI3IP1         | SPI3IP0 |  |  |

| bit 15       |                     | •                                     | •                 |                  |                 |                 |         |  |  |

|              |                     |                                       |                   |                  |                 |                 |         |  |  |

| U-0          | R/W-1               | R/W-0                                 | R/W-0             | U-0              | R/W-1           | R/W-0           | R/W-0   |  |  |

|              | U4TXIP2             | U4TXIP1                               | U4TXIP0           |                  | U4RXIP2         | U4RXIP1         | U4RXIP0 |  |  |

| bit 7        |                     |                                       |                   |                  |                 |                 | bit     |  |  |

| Legend:      |                     |                                       |                   |                  |                 |                 |         |  |  |

| R = Readab   | le bit              | W = Writable                          | bit               | U = Unimple      | mented bit, rea | d as '0'        |         |  |  |

| -n = Value a | t POR               | '1' = Bit is set                      |                   | '0' = Bit is cle | eared           | x = Bit is unkr | iown    |  |  |

| bit 15       | Unimplement         | ted: Read as '                        | ז'                |                  |                 |                 |         |  |  |

| bit 14-12    | -                   | 0>: SPI3 Trans                        |                   | riority bits     |                 |                 |         |  |  |

|              |                     | ot is Priority 7 (                    | -                 | -                |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | 001 = Interrup      | ot is Priority 1                      |                   |                  |                 |                 |         |  |  |

|              | 000 = Interrup      | ot source is dis                      | abled             |                  |                 |                 |         |  |  |

| bit 11       | Unimplement         | ted: Read as '                        | כי                |                  |                 |                 |         |  |  |

| bit 10-8     | SPI3IP<2:0>:        | SPI3 General                          | Interrupt Priori  | ity bits         |                 |                 |         |  |  |

|              | 111 = Interrup      | ot is Priority 7(                     | highest priority  | interrupt)       |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | 001 = Interrup      | ot is Priority 1<br>ot source is dis  | abled             |                  |                 |                 |         |  |  |

| bit 7        | •                   | ted: Read as '                        |                   |                  |                 |                 |         |  |  |

| bit 6-4      | -                   | : UART4 Trans                         |                   | t Priority bits  |                 |                 |         |  |  |

|              |                     | ot is Priority 7 (                    | -                 | -                |                 |                 |         |  |  |

|              | •                   | , , , , , , , , , , , , , , , , , , , | 0 1 9             | 1,               |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •<br>001 = Interrup | ot is Priority 1                      |                   |                  |                 |                 |         |  |  |

|              |                     | ot source is dis                      | abled             |                  |                 |                 |         |  |  |

| bit 3        | Unimplement         | ted: Read as '                        | כי                |                  |                 |                 |         |  |  |

| bit 2-0      | U4RXIP<2:0>         | UART4 Rece                            | eiver Interrupt F | Priority bits    |                 |                 |         |  |  |

|              | 111 = Interrup      | ot is Priority 7 (                    | highest priority  | interrupt)       |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •                   |                                       |                   |                  |                 |                 |         |  |  |

|              | •<br>001 = Interrup | ot is Priority 1                      |                   |                  |                 |                 |         |  |  |

# REGISTER 8-44: IPC22: INTERRUPT PRIORITY CONTROL REGISTER 22

| U-0    | U-0    | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 | -<br>- |        | •      | •      |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| U-0    | U-0    | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

#### REGISTER 11-21: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK3R<5:0>: Assign SPI3 Clock Input (SCK3IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 11-22: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS3R5 | SS3R4 | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS3IN) to Corresponding RPn or RPIn Pin bits

| R/W-0                 | R/W-0                                                                                                                   | U-0                                                         | U-0                | R/W-0               | R/W-0               | R/W-0               | R/W-0               |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------|---------------------|---------------------|---------------------|---------------------|--|--|

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                                                                                                   | _                                                           | _                  | OPS3 <sup>(3)</sup> | OPS2 <sup>(3)</sup> | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |  |  |

| bit 15                |                                                                                                                         |                                                             |                    | 0.00                | 0.02                | 0.01                | bit 8               |  |  |

|                       |                                                                                                                         |                                                             |                    |                     |                     |                     |                     |  |  |

| R/W-0                 | R/W-0                                                                                                                   | R/W-0                                                       | R/W-0              | R/W-0               | R/W-0               | R/W-0               | R/W-0               |  |  |

| TRIGEN                | ONESHOT                                                                                                                 | ALTSYNC                                                     | SYNC4              | SYNC3               | SYNC2               | SYNC1               | SYNC0               |  |  |

| bit 7                 |                                                                                                                         |                                                             |                    |                     |                     |                     | bit 0               |  |  |

|                       |                                                                                                                         |                                                             |                    |                     |                     |                     |                     |  |  |

| Legend:               |                                                                                                                         |                                                             |                    |                     |                     |                     |                     |  |  |

| R = Readable          |                                                                                                                         | W = Writable b                                              | bit                | •                   | nented bit, read    |                     |                     |  |  |

| -n = Value at         | POR                                                                                                                     | '1' = Bit is set                                            |                    | '0' = Bit is clea   | ared                | x = Bit is unkno    | own                 |  |  |

| bit 15                |                                                                                                                         | tput Postscaler                                             | Source Solee       | + hit(1)            |                     |                     |                     |  |  |

| DICTO                 |                                                                                                                         | ostscaler scales                                            |                    |                     | 2                   |                     |                     |  |  |

|                       |                                                                                                                         | ostscaler scales                                            | 00                 |                     | 5                   |                     |                     |  |  |

| bit 14                | RTRGEN: Re                                                                                                              | trigger Enable b                                            | oit <sup>(2)</sup> |                     |                     |                     |                     |  |  |

|                       |                                                                                                                         | e can be retrigg                                            |                    |                     |                     |                     |                     |  |  |

|                       |                                                                                                                         | e may not be re                                             |                    | n TRIGEN bit =      | = 1                 |                     |                     |  |  |

| bit 13-12             | -                                                                                                                       | ted: Read as '0                                             |                    |                     | 2)                  |                     |                     |  |  |

| bit 11-8              |                                                                                                                         | CCPx Interrupt                                              | •                  |                     | 5)                  |                     |                     |  |  |

|                       |                                                                                                                         | upt every 16th t<br>upt every 15th t                        |                    |                     |                     |                     |                     |  |  |

|                       | 0011 = Interru                                                                                                          | upt every 5th tin<br>upt every 4th tin<br>upt every 3rd tir | ne base period     | d match or 4th i    | • •                 |                     |                     |  |  |

|                       |                                                                                                                         | upt every 2nd til<br>upt after each ti                      |                    |                     |                     |                     |                     |  |  |

| bit 7                 |                                                                                                                         | Px Trigger Enat                                             |                    | aa.to op.           |                     |                     |                     |  |  |

|                       | 1 = Trigger op                                                                                                          | operation of time base is enabled                           |                    |                     |                     |                     |                     |  |  |

|                       | 0 = Trigger operation of time base is disabled                                                                          |                                                             |                    |                     |                     |                     |                     |  |  |

| bit 6                 | <b>ONESHOT:</b> One-Shot Mode Enable bit<br>1 = One-Shot Trigger mode is enabled; trigger duration is set by OSCNT<2:0> |                                                             |                    |                     |                     |                     |                     |  |  |

|                       |                                                                                                                         | t Trigger mode<br>t Trigger mode                            |                    | ger duration is     | set by USCN         | <2:0>               |                     |  |  |

| bit 5                 | ALTSYNC: CO                                                                                                             | CPx Clock Sele                                              | ect bits           |                     |                     |                     |                     |  |  |

|                       |                                                                                                                         | ate signal is use<br>ule synchroniza                        |                    |                     |                     |                     |                     |  |  |

| bit 4-0               | SYNC<4:0>:                                                                                                              | CCPx Synchror                                               | nization Source    | e Select bits       |                     |                     |                     |  |  |

|                       |                                                                                                                         | 6 for the definit                                           |                    |                     |                     |                     |                     |  |  |

| Note 1: Th            | nis control bit ha                                                                                                      | s no function in                                            | Input Capture      | modes               |                     |                     |                     |  |  |

|                       | nis control bit ha                                                                                                      |                                                             |                    |                     |                     |                     |                     |  |  |

| <b>3:</b> O           | utput postscale s<br>put Capture mod                                                                                    | settings, from 1:                                           |                    |                     | vill result in a FI | FO buffer overflo   | ow for              |  |  |

#### REGISTER 14-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

| SYNC<4:0>             | Synchronization Source                                     |

|-----------------------|------------------------------------------------------------|

| 00000                 | None; Timer with Rollover on CCPxPRH/L Match or FFFFh      |

| 00001                 | Module's Own Timer Sync Out                                |

| 00010                 | MCCP1 Sync Output                                          |

| 00011                 | SCCP2 Sync Output                                          |

| 00100                 | SCCP3 Sync Output                                          |

| 00101                 | SCCP4 Sync Output                                          |

| 00110                 | SCCP5 Sync Output                                          |

| 00111                 | SCCP6 Sync Output                                          |

| 01000                 | SCCP7 Sync Output                                          |

| 01001                 | INT0                                                       |

| 01010                 | INT1                                                       |

| 01011                 | INT2                                                       |

| 01100 <b>to</b> 01111 | Unused                                                     |

| 10000                 | CLC1 Output <sup>(1)</sup>                                 |

| 10010                 | CLC2 Output <sup>(1)</sup>                                 |

| 10011                 | CLC3 Output <sup>(1)</sup>                                 |

| 10100                 | CLC4 Output <sup>(1)</sup>                                 |

| 10101 <b>to</b> 10111 | Unused                                                     |

| 11000                 | Comparator 3 Trigger                                       |

| 11001                 | Comparator 2 Trigger                                       |

| 11010                 | Comparator 1 Trigger                                       |

| 11011                 | A/D <sup>(1)</sup>                                         |

| 11100                 | CTMU Trigger                                               |

| 11101 and 11110       | Unused                                                     |

| 11111                 | None; Timer with Auto-Rollover (FFFFh $\rightarrow$ 0000h) |

### TABLE 14-6: SYNCHRONIZATION SOURCES

**Note 1:** These sources are only available when the source module is being used in a Synchronous mode.

#### REGISTER 17-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0          | U-0                                        | U-0                        | U-0             | U-0               | U-0              | U-0             | U-0     |  |

|--------------|--------------------------------------------|----------------------------|-----------------|-------------------|------------------|-----------------|---------|--|

| _            | _                                          | _                          | _               | —                 | _                | _               | _       |  |

| bit 15       |                                            |                            |                 |                   |                  |                 | bit 8   |  |

|              |                                            |                            |                 |                   |                  |                 |         |  |

| U-0          | U-0                                        | U-0                        | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |

| 0-0          | 0-0                                        | 0-0                        | N/W-0           |                   | LENGTH<4:0>      |                 | FV/VV-0 |  |

| _            | —                                          |                            |                 | VVI               | LENGTH<4:0>      | (-,-)           |         |  |

| bit 7        |                                            |                            |                 |                   |                  |                 | bit 0   |  |

|              |                                            |                            |                 |                   |                  |                 |         |  |

| Legend:      |                                            |                            |                 |                   |                  |                 |         |  |

| R = Readab   | ole bit                                    | W = Writable               | bit             | U = Unimplen      | nented bit, read | l as '0'        |         |  |

| -n = Value a | at POR                                     | '1' = Bit is set           | t               | '0' = Bit is clea | ared             | x = Bit is unkn | lown    |  |

| -            |                                            |                            |                 |                   |                  |                 |         |  |

| bit 15-5     | Unimplemen                                 | nted: Read as '            | 0'              |                   |                  |                 |         |  |

|              | =                                          |                            |                 | :4-(1.2)          |                  |                 |         |  |

| bit 4-0      |                                            | 4:0>: Variable             | word Length b   | 115(.,=/          |                  |                 |         |  |

|              | 11111 = 32-                                |                            |                 |                   |                  |                 |         |  |

|              | 11110 = 31-bit data                        |                            |                 |                   |                  |                 |         |  |

|              | 11101 = 30-bit data<br>11100 = 29-bit data |                            |                 |                   |                  |                 |         |  |

|              |                                            |                            |                 |                   |                  |                 |         |  |

|              | 11011 = 28-bit data<br>11010 = 27-bit data |                            |                 |                   |                  |                 |         |  |

|              | 11010 <b>– 27-bit data</b>                 |                            |                 |                   |                  |                 |         |  |

|              | 11000 = 25-bit data                        |                            |                 |                   |                  |                 |         |  |

|              | 10111 = 24-bit data                        |                            |                 |                   |                  |                 |         |  |

|              | 10110 <b>= 23-bit data</b>                 |                            |                 |                   |                  |                 |         |  |

|              | 10101 <b>= 22-bit</b> data                 |                            |                 |                   |                  |                 |         |  |

|              |                                            | 10100 <b>= 21-bit data</b> |                 |                   |                  |                 |         |  |

|              | 10011 <b>= 20-bit data</b>                 |                            |                 |                   |                  |                 |         |  |

|              | 10010 = <b>19-bit</b> data                 |                            |                 |                   |                  |                 |         |  |

|              | 10001 = 18-                                |                            |                 |                   |                  |                 |         |  |

|              | 10000 = 17-l<br>01111 = 16-l               |                            |                 |                   |                  |                 |         |  |

|              | 01111 = 10-1<br>01110 = 15-1               |                            |                 |                   |                  |                 |         |  |

|              |                                            |                            |                 |                   |                  |                 |         |  |

|              | 01101 = 14-bit data<br>01100 = 13-bit data |                            |                 |                   |                  |                 |         |  |

|              | 01000 = 13-bit data<br>01011 = 12-bit data |                            |                 |                   |                  |                 |         |  |

|              | 01011 = 12-bit data                        |                            |                 |                   |                  |                 |         |  |

|              | 01001 = 10-bit data                        |                            |                 |                   |                  |                 |         |  |

|              | 01000 <b>= 9-b</b> i                       | it data                    |                 |                   |                  |                 |         |  |

|              | 00111 = 8-bit data                         |                            |                 |                   |                  |                 |         |  |

|              | 00110 <b>= 7-b</b> i                       |                            |                 |                   |                  |                 |         |  |

|              | 00101 <b>= 6-b</b> i                       |                            |                 |                   |                  |                 |         |  |

|              | 00100 <b>= 5-b</b> i                       |                            |                 |                   |                  |                 |         |  |

|              | 00011 = <b>4</b> -bi                       |                            |                 |                   |                  |                 |         |  |

|              | 00010 = 3-bi                               |                            |                 |                   |                  |                 |         |  |

|              | 00001 = 2-bi                               | it data<br>e MODE<32,16    | > hite in SDIVC | ON11 211.105      |                  |                 |         |  |

|              | 00000 = 366                                | 5 IVIODES32, 10            |                 | UNIL 11.102       |                  |                 |         |  |

- **Note 1:** These bits are effective when AUDEN = 0 only.

- 2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

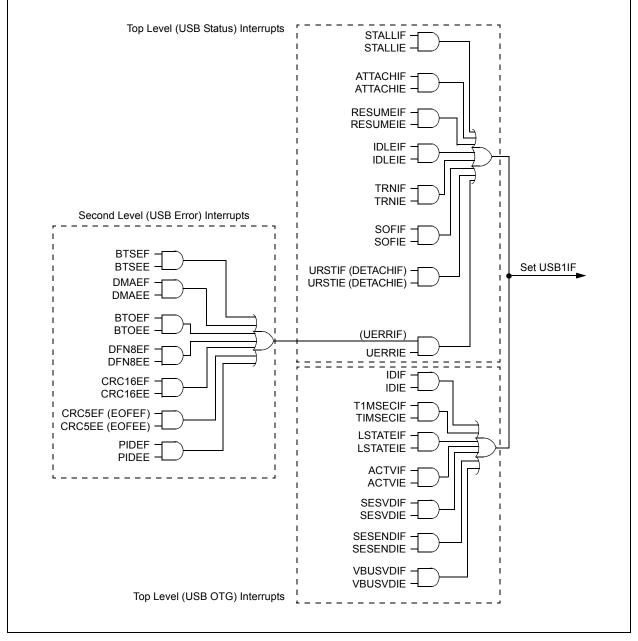

### 20.3 USB Interrupts

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 20-8 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers.

An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level. Unlike the device-level interrupt flags in the IFSx registers, USB interrupt flags in the U1IR registers can only be cleared by writing a '1' to the bit position.

Interrupts may be used to trap routine events in a USB transaction. Figure 20-9 provides some common events within a USB frame and their corresponding interrupts.

# FIGURE 20-8: USB OTG INTERRUPT FUNNEL

### REGISTER 20-8: U1CON: USB CONTROL REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | _   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |