Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 101                                                                            |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb412-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Pir            | /Pad Numl       | ber |     |              |                                                                               |

|--------------|----------------|-----------------|-----|-----|--------------|-------------------------------------------------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP |     | I/O | Input Buffer | Description                                                                   |

| IOCG0        | _              | 90              | A5  | I   | ST           | PORTG Interrupt-on-Change                                                     |

| IOCG1        | _              | 89              | E6  | I   | ST           |                                                                               |

| IOCG2        | 37             | 57              | H10 | I   | ST           | 1                                                                             |

| IOCG3        | 36             | 56              | J11 | I   | ST           | 1                                                                             |

| IOCG6        | 4              | 10              | E3  | I   | ST           | 1                                                                             |

| IOCG7        | 5              | 11              | F4  | I   | ST           | ]                                                                             |

| IOCG8        | 6              | 12              | F2  | I   | ST           | ]                                                                             |

| IOCG9        | 8              | 14              | F3  | I   | ST           | ]                                                                             |

| IOCG12       | —              | 96              | E17 | I   | ST           |                                                                               |

| IOCG13       | —              | 97              | E18 | I   | ST           |                                                                               |

| IOCG14       | —              | 95              | E16 | I   | ST           |                                                                               |

| IOCG15       | _              | 1               | B2  | I   | ST           |                                                                               |

| IOCH1        | —              | _               | B1  | I   | ST           | PORTH Interrupt-on-Change                                                     |

| IOCH2        | _              | _               | D4  | I   | ST           | ]                                                                             |

| IOCH3        | _              |                 | G4  | I   | ST           | ]                                                                             |

| IOCH4        | _              |                 | H3  | I   | ST           | ]                                                                             |

| IOCH5        | —              | —               | H4  | I   | ST           |                                                                               |

| IOCH6        | —              | _               | L5  | I   | ST           |                                                                               |

| IOCH7        | —              | _               | J5  | I   | ST           |                                                                               |

| IOCH8        | —              | _               | H7  | Ι   | ST           |                                                                               |

| IOCH9        | _              | —               | J8  | Ι   | ST           |                                                                               |

| IOCH10       | _              | —               | J9  | Ι   | ST           |                                                                               |

| IOCH11       | —              | _               | G8  | I   | ST           |                                                                               |

| IOCH12       | —              | —               | F7  | I   | ST           |                                                                               |

| IOCH13       | —              | —               | C9  | I   | ST           |                                                                               |

| IOCH14       |                | —               | A8  | I   | ST           |                                                                               |

| IOCH15       |                | —               | F6  | I   | ST           |                                                                               |

| IOCJ0        | —              | —               | E13 | I   | ST           | PORTJ Interrupt-on-Change                                                     |

| IOCJ1        |                | —               | E14 | I   | ST           |                                                                               |

| LCDBIAS0     | 3              | 5               | D2  | 0   | ANA          | Bias Inputs for LCD Driver Charge Pump                                        |

| LCDBIAS1     | 2              | 4               | C1  | 0   | ANA          |                                                                               |

| LCDBIAS2     | 1              | 3               | D3  | 0   | ANA          |                                                                               |

| LCDBIAS3     | 17             | 26              | L1  | 0   | ANA          |                                                                               |

| LVDIN        | 64             | 100             | E31 | I   | ANA          | Low-Voltage Detect Input                                                      |

| MCLR         | 7              | 13              | F1  | I   | ST/STMV      | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OC4          | 54             | 83              | D7  | 0   | DIG          | Output Compare 4 Output                                                       |

| OC5          | 55             | 84              | C7  | 0   | DIG          | Output Compare 5 Output                                                       |

| OC6          | 58             | 87              | B6  | 0   | DIG          | Output Compare 6 Output                                                       |

### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

|                 | Pin/Pad Number |                 |                  |     |                |                     |

|-----------------|----------------|-----------------|------------------|-----|----------------|---------------------|

| Pin Function    | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer   | Description         |

| RH1             | _              |                 | B1               | I/O | DIG/ST         | PORTH Digital I/Os  |

| RH2             | _              | _               | D4               | I/O | DIG/ST         |                     |

| RH3             | _              | _               | G4               | I/O | DIG/ST         |                     |

| RH4             | _              | _               | H3               | I/O | DIG/ST/TTL     |                     |

| RH5             | _              | _               | H4               | I/O | DIG/ST         |                     |

| RH6             | _              | _               | L5               | I/O | DIG/ST         |                     |

| RH7             | _              | _               | J5               | I/O | DIG/ST         |                     |

| RH8             |                | _               | H7               | I/O | DIG/ST         |                     |

| RH9             | _              | _               | J8               | I/O | DIG/ST         |                     |

| RH10            | _              | _               | J9               | I/O | DIG/ST         |                     |

| RH11            |                | _               | G8               | I/O | DIG/ST         |                     |

| RH12            | _              | _               | F7               | I/O | DIG/ST         |                     |

| RH13            | _              | _               | C9               | I/O | DIG/ST         |                     |

| RH14            | —              | _               | A8               | I/O | DIG/ST         |                     |

| RH15            | —              | _               | F6               | I/O | DIG/ST         | ]                   |

| RJ0             | —              | _               | D5               | I/O | DIG/ST         | PORTJ Digital I/Os  |

| RJ1             | —              | _               | E5               | I/O | DIG/ST         | 1                   |

| legend: TTI = 1 | TI input buf   | for             |                  |     | ST - Schmitt T | rigger input buffer |

### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

|               | 1              | n/Pad Numb      |                  |     |                          |                                            |  |

|---------------|----------------|-----------------|------------------|-----|--------------------------|--------------------------------------------|--|

| Pin Function  | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer             | Description                                |  |

| RPI32         | _              | 40              | K6               | I   | ST                       | Remappable Peripherals (Input only)        |  |

| RPI33         | —              | 18              | G1               | I   | ST                       |                                            |  |

| RPI34         | —              | 19              | G2               | I   | ST                       |                                            |  |

| RPI35         | _              | 67              | E8               | I   | ST                       |                                            |  |

| RPI36         | —              | 66              | E11              | I   | ST                       |                                            |  |

| RPI37         | 48             | 74              | B11              | I   | ST                       |                                            |  |

| RPI38         | _              | 6               | D1               | I   | ST                       |                                            |  |

| RPI39         | _              | 7               | E4               | I   | ST                       |                                            |  |

| RPI40         | _              | 8               | E2               | I   | ST                       |                                            |  |

| RPI41         | _              | 9               | E1               | I   | ST                       |                                            |  |

| RPI42         | _              | 79              | A9               | I   | ST                       |                                            |  |

| RPI43         | —              | 47              | L9               | I   | ST                       |                                            |  |

| RTCC          | 42             | 68              | E9               | 0   | DIGMV                    | Real-Time Clock Alarm/Seconds Pulse Output |  |

| SCK4          | 59             | 88              | A6               | I/O | DIG/ST                   | SPI4 Clock                                 |  |

| SCL1          | 37             | 57              | H10              | I/O | DIG/I <sup>2</sup> C/SMB | I2C1 Synchronous Serial Clock Input/Output |  |

| SCL2          | 32             | 58              | H11              | I/O | DIG/I <sup>2</sup> C/SMB | I2C2 Synchronous Serial Clock Input/Output |  |

| SCL3          | 2              | 4               | C1               | I/O | DIG/I <sup>2</sup> C/SMB | I2C3 Synchronous Serial Clock Input/Output |  |

| SDA1          | 36             | 56              | J11              | I/O | DIG/I <sup>2</sup> C/SMB | I2C1 Data Input/Output                     |  |

| SDA2          | 31             | 59              | G10              | I/O | DIG/I <sup>2</sup> C/SMB | I2C2 Data Input/Output                     |  |

| SDA3          | 3              | 5               | D2               | I/O | DIG/I <sup>2</sup> C/SMB | I2C3 Data Input/Output                     |  |

| SDI4          | 28             | 42              | L7               | I   | ST                       | SPI4 Data Input                            |  |

| SDO4          | 23             | 34              | H5               | 0   | DIG                      | SPI4 Data Output                           |  |

| Legend: TTL = | TTL input buf  | fer             |                  |     | ST = Schmitt T           | rigger input buffer                        |  |

#### **TABLE 1-4:** PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

|              | Pin/Pad Number |                 |                  |     |              |                                           |  |

|--------------|----------------|-----------------|------------------|-----|--------------|-------------------------------------------|--|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                               |  |

| CLKI         | 39             | 63              | F9               | _   | _            | Main Clock Input Connection               |  |

| CLKO         | 40             | 64              | F11              | 0   | DIG          | System Clock Output                       |  |

| COM0         | 63             | 99              | A2               | 0   | ANA          | LCD Driver Common Outputs                 |  |

| COM1         | 62             | 98              | B3               | 0   | ANA          |                                           |  |

| COM2         | 61             | 94              | B4               | 0   | ANA          |                                           |  |

| COM3         | 60             | 93              | A4               | 0   | ANA          |                                           |  |

| COM4         | 59             | 88              | B1               | 0   | ANA          |                                           |  |

| COM5         | 23             | 34              | D4               | 0   | ANA          |                                           |  |

| COM6         | 22             | 33              | G4               | 0   | ANA          |                                           |  |

| COM7         | 21             | 32              | H3               | 0   | ANA          |                                           |  |

| CTCMP        | 14             | 23              | J2               | 0   | ANA          | CTMU Comparator 2 Input (Pulse mode)      |  |

| CTED1        | 28             | 42              | L7               | I   | ST           | CTMU External Edge Inputs                 |  |

| CTED2        | 27             | 41              | J7               | I   | ST           |                                           |  |

| CTED3        | _              | 1               | B2               | I   | ST           |                                           |  |

| CTED4        | 1              | 3               | D3               | I   | ST           |                                           |  |

| CTED5        | 29             | 43              | K7               | I   | ST           |                                           |  |

| CTED6        | 30             | 44              | L8               | I   | ST           |                                           |  |

| CTED7        | -              | 40              | K6               | I   | ST           |                                           |  |

| CTED8        | 64             | 100             | A1               | I   | ST           |                                           |  |

| CTED9        | 63             | 99              | A2               | I   | ST           |                                           |  |

| CTED10       | —              | 97              | A3               | I   | ST           |                                           |  |

| CTED11       | _              | 95              | C4               | I   | ST           |                                           |  |

| CTED12       | 15             | 24              | K1               | I   | ST           |                                           |  |

| CTED13       | 14             | 23              | J2               | I   | ST           |                                           |  |

| CTED14       | _              | 17              | G3               | I   | ST           |                                           |  |

| CTPLS        | 29             | 43              | K7               | 0   | DIG          | CTMU Pulse Output                         |  |

| CVREF        | 23             | 34              | H5               | 0   | ANA          | Comparator Voltage Reference Output       |  |

| CVREF+       | 16             | 25,29           | K2,K3            | I   | ANA          | Comparator Voltage Reference (high) Input |  |

| CVREF-       | 15             | 24,28           | K1,L2            | I   | ANA          | Comparator Voltage Reference (low) Input  |  |

| D+           | 37             | 57              | H10              | I/O | XCVR         | USB D-                                    |  |

| D-           | 36             | 56              | J11              | I/O | XCVR         | ]                                         |  |

| DAC1         | 8              | 14              | F3               | 0   | ANA          | DAC1 Analog Output                        |  |

| DVREF+       | 16             | 25,29           | K2,K3            | I   | ANA          | DAC External Reference                    |  |

| IC4          | 1              | 3               | D3               | I   | ST           | Input Capture 4                           |  |

| IC5          | 2              | 4               | C1               | I   | ST           | Input Capture 5                           |  |

| IC6          | 3              | 5               | D2               | I   | ST           | Input Capture 6                           |  |

### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

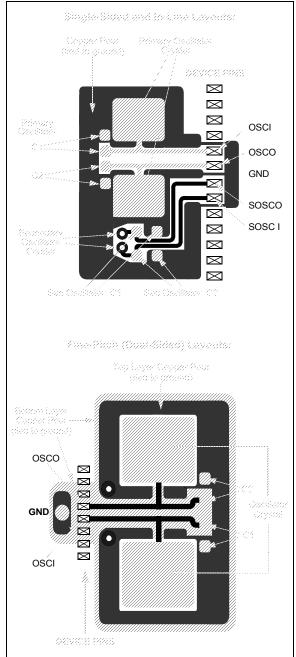

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

- AN1798, "Crystal Selection for Low-Power Secondary Oscillator"

### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## 4.1.4 FLASH CONFIGURATION WORDS

In PIC24FJ256GA412/GB412 family devices, the top nine words of on-chip program memory are reserved for configuration information. On device Reset, the configuration information is copied into the actual Configuration registers, located in configuration space.

The address range of the Flash Configuration Words for devices in the PIC24FJ256GA412/GB412 family are shown in Table 4-2. Their location in the memory map is shown with the other memory vectors in Figure 4-1. Additional details on the device Configuration Words are provided in **Section 33.0 "Special Features"**.

### 4.1.4.1 Dual Partition Configuration Words

In Dual Partition Flash modes, each partition has its own set of Flash Configuration Words. The full set of Configuration registers in the Active Partition is used to determine the device's configuration; the Configuration Words in the Inactive Partition are used to determine the device's configuration when that partition becomes active. However, some of the Configuration registers in the Inactive Partition (FSEC, FBSLIM and FSIGN) may be used to determine how the Active Partition is able or allowed to access the Inactive Partition.

### 4.1.5 ONE-TIME-PROGRAMMABLE (OTP) MEMORY

PIC24FJ256GA412/GB412 family devices provide 384 bytes of One-Time-Programmable (OTP) memory, located at addresses, 801380h through 8013FEh. This memory can be used for persistent storage of application-specific information that will not be erased by reprogramming the device. This includes many types of information, such as (but not limited to):

- Application checksums

- Code revision information

- Product information

- Serial numbers

- System manufacturing dates

- · Manufacturing lot numbers

OTP memory may be programmed in any mode, including user RTSP mode, but it cannot be erased. Data is not cleared by a Chip Erase. Once programmed, it cannot be rewritten.

Do not perform repeated write operations on the OTP.

|                       | Program           | Configuration Wo | rd Address Range              |

|-----------------------|-------------------|------------------|-------------------------------|

| Device Family         | Memory<br>(Words) | Single Partition | Dual Partition <sup>(1)</sup> |

| PIC24FJ64GA4XX/GB4XX  | 22,016            | 00AF80h:00AFB0h  | 005780h:0057FCh               |

| PIC24FJ128GA4XX/GB4XX | 44,032            | 015780h:0157B0h  | 00AB80h:00ABFCh               |

| PIC24FJ256GA4XX/GB4XX | 88,065            | 02AF80h:02AFB0h  | 015780h:0157FCh               |

### TABLE 4-2: FLASH CONFIGURATION WORDS FOR PIC24FJ256GA412/GB412 FAMILY DEVICES

**Note 1:** Addresses for the Active Partition are shown. For the Inactive Partitions, add 400000h.

## 5.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction. In addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- Source and destination (SFRs and data RAM)

- · Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (Fixed Address or Address Blocks with or without Address Increment/Decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

### 5.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 07FFh) or the data RAM space (0800h to FFFFh) can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 5-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

### 5.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-size transactions. When byte-size transactions are chosen, the LSb of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

### 5.1.3 TRIGGER SOURCE

The DMA Controller can use 63 of the device's interrupt sources to initiate a transaction. The DMA trigger sources occur in reverse order than their natural interrupt priority and are shown in Table 5-1. Since the source and destination addresses for any transaction can be programmed independently of the trigger source, the DMA Controller can use any trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

### 5.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each trigger.

- One-Shot: A single transaction occurs for each trigger.

- Continuous: A series of back-to-back transactions occur for each trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per trigger, until the DMA channel is disabled.

All transfer modes allow the option to have the source and destination addresses, and counter value, automatically reloaded after the completion of a transaction; Repeated mode transfers do this automatically.

### 5.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- · Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range of source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA-capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

For PIC24FJ256GA412/GB412 family devices, the 12-bit A/D Converter module is the only PIA-capable peripheral. Details for its use in PIA mode are provided in **Section 27.0 "12-Bit A/D Converter with Threshold Detect"**.

### REGISTER 8-27: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

|                     | R/W-1                                                                                                                | R/W-0                                                                                                                                                    | R/W-0                                                                                              | U-0              | R/W-1            | R/W-0           | R/W-0   |

|---------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|---------|

| _                   | CCP6IP2                                                                                                              | CCP6IP1                                                                                                                                                  | CCP6IP0                                                                                            |                  | CCP5IP2          | CCP5IP1         | CCP5IP0 |

| bit 15              |                                                                                                                      |                                                                                                                                                          |                                                                                                    |                  |                  |                 | bit 8   |

| U-0                 | U-0                                                                                                                  | U-0                                                                                                                                                      | U-0                                                                                                | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                   |                                                                                                                      | _                                                                                                                                                        | _                                                                                                  | _                | INT1IP2          | INT1IP1         | INT1IP0 |

| bit 7               |                                                                                                                      |                                                                                                                                                          |                                                                                                    |                  |                  |                 | bit 0   |

| Legend:             |                                                                                                                      |                                                                                                                                                          |                                                                                                    |                  |                  |                 |         |

| R = Readab          | ole bit                                                                                                              | W = Writable I                                                                                                                                           | bit                                                                                                | U = Unimplen     | nented bit, read | l as '0'        |         |

| -n = Value a        | at POR                                                                                                               | '1' = Bit is set                                                                                                                                         |                                                                                                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                     | 001 = Interru                                                                                                        | nt is Driarity 1                                                                                                                                         |                                                                                                    |                  |                  |                 |         |

|                     |                                                                                                                      | pt source is dis                                                                                                                                         |                                                                                                    |                  |                  |                 |         |

| bit 11              | Unimplemen                                                                                                           | pt source is dis<br>ted: Read as 'o                                                                                                                      | )'                                                                                                 |                  | ( hite           |                 |         |

| bit 11<br>bit 10-8  | Unimplemen<br>CCP5IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru                                                | pt source is dis<br>ted: Read as '(<br>: SCCP5 Captu<br>pt is Priority 7 (                                                                               | <sub>)</sub> ,<br>ure/Compare I<br>highest priority                                                | • •              | / bits           |                 |         |

| bit 10-8            | Unimplemen<br>CCP5IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                               | pt source is dis<br>ted: Read as '(<br>: SCCP5 Capti<br>pt is Priority 7 (<br>pt is Priority 1                                                           | <sub>)</sub> ,<br>ure/Compare I<br>highest priority<br>abled                                       | • •              | ∕ bits           |                 |         |

| bit 10-8<br>bit 7-3 | Unimplemen<br>CCP5IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0>: | pt source is dis<br>ted: Read as 'c<br>: SCCP5 Captu<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                       | <sub>)</sub> ,<br>ure/Compare I<br>highest priority<br>abled<br><sub>)</sub> ,<br>upt 1 Priority b | r interrupt)     | y bits           |                 |         |

|                     | Unimplemen<br>CCP5IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>INT1IP<2:0>: | pt source is dis<br>ted: Read as '(<br>: SCCP5 Captu<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>External Intern | <sub>)</sub> ,<br>ure/Compare I<br>highest priority<br>abled<br><sub>)</sub> ,<br>upt 1 Priority b | r interrupt)     | γ bits           |                 |         |

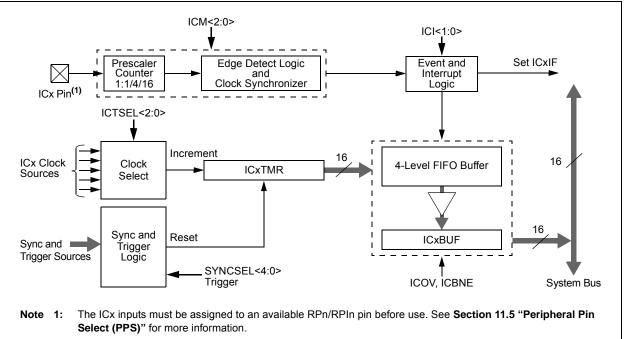

## 15.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture with Dedicated Timer" (DS70000352). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ256GA412/GB412 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-Configurable for 32-Bit Operation in All Modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output compare Operation, with up to 30 User-Selectable Sync/Trigger Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- · Configurable Interrupt Generation

- Up to 6 Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

The module is controlled through two registers: ICxCON1 (Register 15-1) and ICxCON2 (Register 15-2). A general block diagram of the module is shown in Figure 15-1.

## 15.1 General Operating Modes

### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSEL<4:0> bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

# PIC24FJ256GA412/GB412 FAMILY

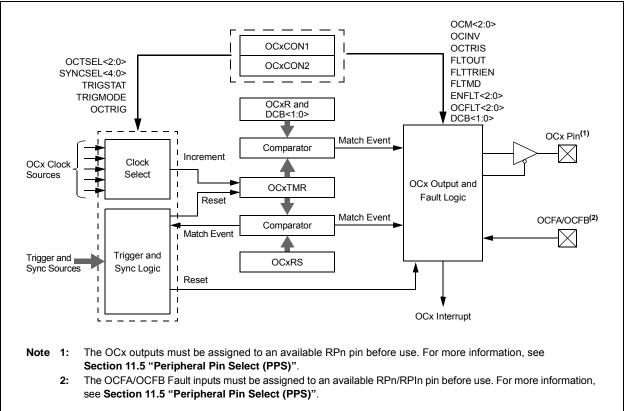

### FIGURE 16-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

## 16.2 Compare Operations

In Compare mode (Figure 16-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no sync/trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bits for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a trigger source event occurs.

# PIC24FJ256GA412/GB412 FAMILY

To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

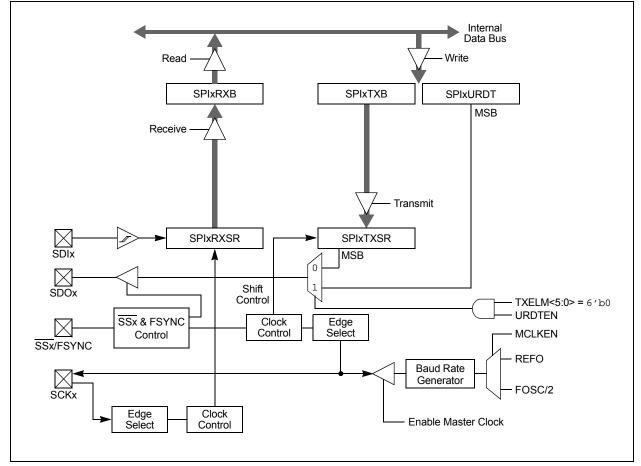

## FIGURE 17-1: SPIx MODULE BLOCK DIAGRAM (STANDARD MODE)

SPIxCON1H: SPIx CONTROL REGISTER 1 HIGH

| R/W-0               | R/W-0                          | R/W-0                               | R/W-0                       | R/W-0                      | R/W-0                 | R/W-0            | R/W-0          |

|---------------------|--------------------------------|-------------------------------------|-----------------------------|----------------------------|-----------------------|------------------|----------------|

| AUDEN <sup>(1</sup> | I) SPISGNEXT                   | IGNROV                              | IGNTUR                      | AUDMONO <sup>(2)</sup>     | URDTEN <sup>(3)</sup> | AUDMOD1(4)       | AUDMOD0(4)     |

| bit 15              |                                |                                     |                             |                            |                       | I                | bit 8          |

|                     |                                |                                     |                             |                            |                       |                  |                |

| R/W-0               | R/W-0                          | R/W-0                               | R/W-0                       | R/W-0                      | R/W-0                 | R/W-0            | R/W-0          |

| FRMEN               | FRMSYNC                        | FRMPOL                              | MSSEN                       | FRMSYPW                    | FRMCNT2               | FRMCNT1          | FRMCNT0        |

| bit 7               |                                |                                     |                             | -                          |                       | 1                | bit C          |

|                     |                                |                                     |                             |                            |                       |                  |                |

| Legend:             |                                |                                     |                             |                            |                       |                  |                |

| R = Reada           | able bit                       | W = Writable I                      | oit                         | U = Unimpleme              | ented bit, read       | as '0'           |                |

| -n = Value          | at POR                         | '1' = Bit is set                    |                             | '0' = Bit is clear         |                       | x = Bit is unkr  | iown           |

|                     |                                |                                     |                             |                            |                       |                  | -              |

| bit 15              | AUDEN: Aud                     | io Codec Suppo                      | ort Enable bit <sup>(</sup> | 1)                         |                       |                  |                |

|                     |                                |                                     |                             | ntrols the directio        | n of both SCK         | x and frame (a.l | k.a. LRC). and |

|                     |                                |                                     |                             | , FRMSYNC = M              |                       |                  |                |

|                     | 0                              | s of their actua                    |                             |                            |                       |                  |                |

|                     |                                | otocol is disable                   |                             |                            |                       |                  |                |

| bit 14              |                                | -                                   |                             | Read Data Enabl            | le bit                |                  |                |

|                     |                                | n RX FIFO is sig<br>n RX FIFO is no |                             | d                          |                       |                  |                |

| bit 13              |                                | ore Receive Ov                      | 0                           | eu                         |                       |                  |                |

| DIL 13              | •                              |                                     |                             | critical error; duri       | na POV data           | in the EIEO is r | ot overwritten |

|                     |                                | ceive data                          |                             |                            |                       |                  |                |

|                     |                                | a critical error                    | that stops SP               | l operation                |                       |                  |                |

| bit 12              | IGNTUR: Igno                   | ore Transmit Ur                     | nderrun bit                 |                            |                       |                  |                |

|                     |                                |                                     |                             | critical error and         | d data indicate       | ed by URDTEN     | is transmitted |

|                     |                                | SPIxTXB is not                      |                             |                            |                       |                  |                |

|                     |                                | a critical error                    | -                           | -                          |                       |                  |                |

| bit 11              |                                | Audio Data For                      |                             |                            |                       |                  |                |

|                     | 1 = Audio dat<br>0 = Audio dat |                                     | each data wo                | rd is transmitted          | on both left ar       | id right channel | S)             |

| bit 10              |                                | ansmit Underru                      | n Data Enable               | hit(3)                     |                       |                  |                |

|                     |                                |                                     |                             | ter during Transn          | nit Underrun o        | onditions        |                |

|                     |                                |                                     | •                           | Transmit Under             |                       |                  |                |

| bit 9-8             | AUDMOD<1:                      | 0>: Audio Proto                     | col Mode Sel                | ection bits <sup>(4)</sup> |                       |                  |                |

|                     | 11 = PCM/DS                    |                                     |                             |                            |                       |                  |                |

|                     |                                |                                     |                             | nctions as if SPIF         |                       |                  |                |

|                     |                                |                                     |                             | tions as if SPIFE          |                       |                  | value          |

| L:1 7               |                                |                                     |                             | f SPIFE = 0, rega          | ardiess of its a      | ctual value      |                |

| bit 7               |                                | ned SPIx Supp                       |                             | nin in used as the         |                       | ut/output/       |                |

|                     |                                | SPIX support is e                   |                             | pin is used as the         | e FSTNC Inpu          | il/output)       |                |

|                     |                                |                                     |                             |                            |                       |                  |                |

|                     | AUDEN can only                 |                                     |                             |                            |                       |                  |                |

|                     | AUDMONO can                    | •                                   |                             | EN bit = 0 and is          | only valid for        | AUDEN = 1.       |                |

| 3:                  | URDTEN is only                 |                                     |                             |                            | بالم ممارينية ال      |                  | _ 1 \\/!       |

| 4:                  | AUDMOD<1:0>                    | can only be writ                    | ten when the                | SPIEN DIT = 0 an           | iu is only valid      | when AUDEN       | =⊥.vvnen       |

#### AUDMOD<1:0> can only be written when the SPIEN bit = 0 and is only valid when AUDEN = 1. When 4:

NOT in PCM/DSP mode, this module functions as if FRMSYPW = 1, regardless of its actual value.

REGISTER 17-2:

### REGISTER 19-2: UxSTAL: UARTx STATUS LOW AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                                                                                                                                                                                                      |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receive buffer and the RSR to the empty state</li> </ul>                                                                                                                                                                               |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1: | The value of this bit only affects the transmit properties of the module when the IrDA encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                                      |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

### REGISTER 19-3: UxSTAH: UARTx STATUS HIGH AND CONTROL REGISTER

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADMASK7 | ADMASK6 | ADMASK5 | ADMASK4 | ADMASK3 | ADMASK2 | ADMASK1 | ADMASK0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|----------|----------|----------|----------|----------|----------|----------|

| ADMADDF | ADMADDR6 | ADMADDR5 | ADMADDR4 | ADMADDR3 | ADMADDR2 | ADMADDR1 | ADMADDR0 |

| bit 7   |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8 | ADMASK<7:0>: ADMADDR<7:0> Masking bits                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Corresponding ADMADDRx bit is used to detect the address match                                                                       |

|          | 0 = Corresponding ADMADDRx bit is not used to detect the address match                                                                   |

| bit 7-0  | ADMADDR<7:0>: Address Detect Task Off-Load bits                                                                                          |

|          | Used with the ADMASK<7:0> bits to off-load the task of detecting the address character from the<br>processor during Address Detect mode. |

### 20.4.2 RECEIVING AN IN TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the *"USB 2.0 Specification"*.

- 2. Create a data buffer and populate it with the data to send to the host.

- 3. In the appropriate (even or odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- When the USB module receives an IN token, it automatically transmits the data in the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Token Complete Interrupt Flag, TRNIF (U1IR<3>).

## 20.4.3 RECEIVING AN OUT TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer with the amount of data you are expecting from the host.

- 3. In the appropriate (even or odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- 4. When the USB module receives an OUT token, it automatically receives the data sent by the host to the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Token Complete Interrupt Flag, TRNIF (U1IR<3>).

## 20.5 Host Mode Operation

The following sections describe how to perform common Host mode tasks. In Host mode, USB transfers are invoked explicitly by the host software. The host software is responsible for the Acknowledge portion of the transfer. Also, all transfers are performed using the USB Endpoint 0 Control register (U1EP0) and Buffer Descriptors.

### 20.5.1 ENABLE HOST MODE AND DISCOVER A CONNECTED DEVICE

- Enable Host mode by setting the HOSTEN bit (U1CON<3>). This causes the Host mode control bits in other USB OTG registers to become available.

- Enable the D+ and D- pull-down resistors by setting the DPPULDWN and DMPULDWN bits (U10TGCON<5:4>). Disable the D+ and Dpull-up resistors by clearing the DPPULUP and DMPULUP bits (U10TGCON<7:6>).

- At this point, SOF generation begins with the SOF counter loaded with 12,000. Eliminate noise on the USB by clearing the SOFEN bit (U1CON<0>) to disable Start-of-Frame (SOF) packet generation.

- 4. Enable the device attached interrupt by setting the ATTACHIE bit (U1IE<6>).

- Wait for the device attached interrupt (U1IR<6> = 1). This is signaled by the USB device changing the state of D+ or D- from '0' to '1' (SE0 to J-state). After it occurs, wait 100 ms for the device power to stabilize.

- Check the state of the JSTATE and SE0 bits in U1CON. If the JSTATE bit (U1CON<7>) is '0', the connecting device is low speed. If the connecting device is low speed, set the LSPDEN and LSPD bits (U1ADDR<7> and U1EP0<7>) to enable low-speed operation.

- Reset the USB device by setting the USBRST bit (U1CON<4>) for at least 50 ms, sending Reset signaling on the bus. After 50 ms, terminate the Reset by clearing USBRST.

- 8. In order to keep the connected device from going into suspend, enable the SOF packet generation by setting the SOFEN bit.

- 9. Wait 10 ms for the device to recover from Reset.

- 10. Perform enumeration as described by Chapter 9 of the "USB 2.0 Specification".

### 24.3 Power Control

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current lower power mode.

To use this feature:

- 1. Enable the RTCC (RTCEN = 1).

- 2. Set the PWCEN bit (RTCCON1L<10>).

- 3. Configure the RTCC pin to drive the PWC control signal (RTCOE = 1 and OUTSEL<2:0> = 011).

The polarity of the PWC control signal is selected by the PWCPOL bit (RTCCON1L<9>). An active-low or active-high signal may be used with the appropriate external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin, in order to drive the ground pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

Once the RTCC and PWC are enabled and running, the PWC logic will generate a control output and a sample gate output. The control output is driven out on the RTCC pin (when RTCOE = 1 and OUTSEL<2:0> = 011) and is used to power-up or power-down the device, as described above.

Once the control output is asserted, the Stability Window begins, in which the external device is given enough time to power-up and provide a stable output.

Once the output is stable, the RTCC provides a sample gate during the Sample Window. The use of this sample gate depends on the external device being used, but typically, it is used to mask out one or more wake-up signals from the external device.

Finally, both the Stability and the Sample Windows close after the expiration of the Sample Window, and the external device is powered down.

### 24.3.1 POWER CONTROL CLOCK SOURCE

The Stability and Sample Windows are controlled by the PWCSAMP<7:0> and PWCSTAB<7:0> bits field in the RTCCON3L register (RTCCON3L<15:8> and <7:0>, respectively). As both the Stability and Sample Windows are defined in terms of the RTCC clock, their absolute values vary by the value of the PWC clock base period. The 8-bit magnitude of PWCSTABx and PWCSAMPx allows for a window size of 0 to 255 clock periods.

The period of the PWC clock can also be adjusted with a 1:1, 1:16, 1:64 or 1:256 prescaler, determined by the PWCPS<1:0> bits (RTCCON2L<7:6>).

In addition, certain values for the PWCSTABx and PWCSAMPx fields have specific control meanings in determining power control operations. If either bit field is 00h, the corresponding window is inactive. In addition, if the PWCSTABx field is FFh, the Stability Window remains active continuously, even if power control is disabled.

## 24.4 Event Timestamping

The RTCC includes two sets of Timestamp registers that may be used for the capture of Time and Date register values when an external input signal is received. The RTCC triggers the timestamps for two events:

- For Timestamp A, a falling edge on the TMPR pin

- For Timestamp B, when the devices transition from VDD to VBAT power

A Timestamp A event can be triggered while running the device in VBAT mode if the TMPR pin is pulled up to VBAT.

### 24.4.1 TIMESTAMP OPERATION

The event input is enabled for timestamping using the TSAEN bit (RTCCON1L<0>). When the timestamp event occurs, the present time and date values are stored in the TSATIMEL/H and TSADATEL/H registers, the TSAEVT status bit (RTCSTATL<3>) becomes set and an RTCC interrupt occurs. A new timestamp capture event cannot occur until the user clears the TSAEVT status bit.

### 24.4.2 MANUAL TIMESTAMP

The current time and date may be captured in the TSATIMEL/H and TSADATEL/H registers by writing a '1' to the TSAEVT bit location while the timestamp functionality is enabled (TSAEN = 1). This write will not set the TSAEVT bit, but it will initiate a timestamp capture. The TSAEVT bit will be set when the capture operation is complete. The user must poll the TSAEVT bit to determine when the capture operation is complete.

After the Timestamp registers have been read, the TSAEVT bit should be cleared to allow further hardware or software timestamp capture events.

# PIC24FJ256GA412/GB412 FAMILY

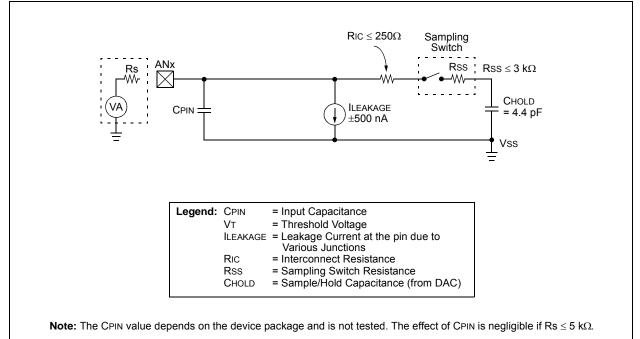

## FIGURE 27-3: 10-BIT A/D CONVERTER ANALOG INPUT MODEL

## EQUATION 27-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$$ADCS = \frac{TAD}{TCY} - 1$$

Note: Based on TCY = 2/FOSC; Doze mode and PLL are disabled.

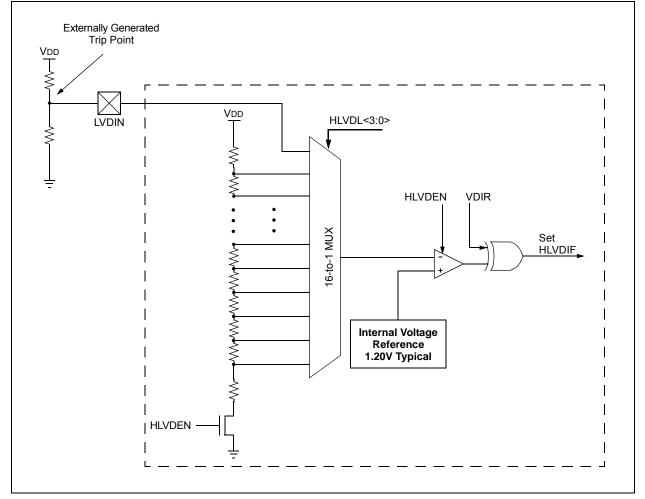

## 32.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the High/Low-Voltage Detect, refer to the "dsPIC33/PIC24 Family Reference Manual", "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725). The information in this data sheet supersedes the information in the FRM. The High/Low-Voltage Detect (HLVD) module is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 32-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

### FIGURE 32-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

## 36.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FJ256GA412/GB412 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FJ256GA412/GB412 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                       | -40°C to +100°C                                    |

|----------------------------------------------------------------------|----------------------------------------------------|

| Storage temperature                                                  |                                                    |

|                                                                      |                                                    |

| Voltage on VDD with respect to Vss                                   |                                                    |

| Voltage on any general purpose digital or analog pin (not 5.5V toler |                                                    |

| Voltage on any general purpose digital or analog pin (5.5V tolerant, | including MCLR) with respect to Vss:               |

| When VDD = 0V:                                                       | -0.3V to + 4.0V                                    |

| When $VDD \ge 2.0V$ :                                                | -0.3V to +6.0V                                     |

| Voltage on AVDD with respect to VSS                                  | (VDD – 0.3V) to (lesser of: 4.0V or (VDD + 0.3V))  |

| Voltage on AVss with respect to Vss                                  | -0.3V to +0.3V                                     |

| Voltage on VBAT with respect to Vss                                  |                                                    |

| Voltage on VUSB3V3 with respect to VSS                               | (VCAP – 0.3V) to +4.0V                             |

| Voltage on VBUS with respect to VSS                                  | -0.3V to +6.0V                                     |

| Voltage on D+ or D- with respect to Vss:                             |                                                    |

| $(0\Omega \text{ source impedance})$ (Note 1)                        | 0.5V to (VUSB3V3 + 0.5V)                           |

| (Source Impedance $\geq$ 28 $\Omega$ , VUSB3V3 $\geq$ 3.0V)          | 1.0V to +4.6V                                      |

| Maximum current out of Vss pin                                       |                                                    |

| Maximum current into VDD pin (Note 2)                                | 250 mA                                             |

| Maximum output current sunk by any I/O pin                           |                                                    |

| Maximum output current sourced by any I/O pin                        |                                                    |