Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga406t-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin | Function                                       | Pin | Function                                                       |

|-----|------------------------------------------------|-----|----------------------------------------------------------------|

| A1  | SEG62/LVDIN/CTED8/PMD4/IOCE4/RE4               | E1  | SEG52/AN16/RPI41/PMCS2/IOCC4/RC4                               |

| A2  | COM0/CTED9/PMD3/IOCE3/RE3                      | E2  | SEG33/RPI40/IOCC3/RC3                                          |

| A3  | SEG61/CTED10/IOCG13/RG13                       | E3  | SEG0/AN17/C1IND/RP21/ICM1/OCM1A/PMA5/IOCG6/RG6                 |

| A4  | COM3/PMD0/IOCE0/RE0                            | E4  | SEG51/RPI39/IOCC2/RC2                                          |

| A5  | SEG49/PMD8/IOCG0/RG0                           | E5  | IOCJ1/RJ1                                                      |

| A6  | SEG47/SCK4/PMD10/IOCF1/RF1                     | E6  | SEG46/PMD9/IOCG1/RG1                                           |

| A7  | VBAT                                           | E7  | VDD                                                            |

| A8  | IOCH14/RH14                                    | E8  | SEG43/RPI35/PMBE1/IOCA15/RA15                                  |

| A9  | SEG44/RPI42/PMD12/IOCD12/RD12                  | E9  | SEG13/CLC4OUT/RP2/RTCC/U6RTS/U6BCLK/ICM5/IOCD8/RD8             |

| A10 | SEG21/RP23/PMACK1/IOCD2/RD2                    | E10 | SEG14/RP4/PMACK2/IOCD9/RD9                                     |

| A11 | SEG20/RP24/U5TX/ICM4/IOCD1/RD1                 | E11 | SEG42/ <b>RPI36</b> /PMA22/IOCA14/RA14                         |

| B1  | COM4/IOCH1/RH1                                 | F1  | MCLR                                                           |

| B2  | SEG50/OCM1C/CTED3/IOCG15/RG15                  | F2  | VLCAP2/AN19/C2IND/RP19/ICM2/OCM2/PMA3/IOCG8/RG8                |

| B3  | COM1/PMD2/IOCE2/RE2                            | F3  | SEG1/AN20/C1INC/C2INC/C3INC/RP27/DAC1/PMA2/PMALU/<br>IOCG9/RG9 |

| B4  | COM2/PMD1/IOCE1/RE1                            | F4  | VLCAP1/AN18/C1INC/RP26/OCM1B/PMA4/IOCG7/RG7                    |

| B5  | SEG58/AN22/OCM1F/PMA17/IOCA7/RA7               | F5  | Vss                                                            |

| B6  | SEG27/U5CTS/OC6/PMD11/IOCF0/RF0                | F6  | IOCH15/RH15                                                    |

| B7  | VCAP                                           | F7  | IOCH12/RH12                                                    |

| B8  | SEG24/RP20/PMRD/PMWR/IOCD5/RD5                 | F8  | VDD                                                            |

| B9  | SEG22/RP22/ICM7/PMBE0/IOCD3/RD3                | F9  | OSCI/CLKI/IOCC12/RC12                                          |

| B10 | Vss                                            | F10 | Vss                                                            |

| B11 | SOSCO/SCLKI/RPI37/PWRLCLK/IOCC14/RC14          | F11 | OSCO/CLKO/IOCC15/RC15                                          |

| C1  | LCDBIAS1/SCL3/IC5/PMD6/IOCE6/RE6               | G1  | SEG34/RPI33/PMCS1/IOCE8/RE8                                    |

| C2  | Vdd                                            | G2  | SEG35/AN21/RPI34/PMA19/IOCE9/RE9                               |

| C3  | SEG60/IOCG12/RG12                              | G3  | TMS/SEG48/CTED14/IOCA0/RA0                                     |

| C4  | SEG59/CTED11/PMA16/IOCG14/RG14                 | G4  | COM6/IOCH3/RH3                                                 |

| C5  | SEG57/AN23/OCM1E/IOCA6/RA6                     | G5  | VDD                                                            |

| C6  | Vss                                            | G6  | Vss                                                            |

| C7  | SEG26/C3INA/U5RTS/U5BCLK/OC5/PMD15/IOCD7/RD7   | G7  | Vss                                                            |

| C8  | SEG23/RP25/PMWR/PMENB/IOCD4/RD4                | G8  | IOCH11/RH11                                                    |

| C9  | IOCH13/RH13                                    | G9  | TDO/SEG28/IOCA5/RA5                                            |

| C10 | SOSCI/IOCC13/RC13                              | G10 | SEG56/SDA2/PMA20/IOCA3/RA3                                     |

| C11 | SEG16/C3INC/RP12/PMA14/PMCS/APMCS1/IOCD11/RD11 | G11 | TDI/PMA21/IOCA4/RA4                                            |

| D1  | SEG32/RPI38/OCM1D/IOCC1/RC1                    | H1  | PGEC3/SEG2/AN5/C1INA/RP18/ICM3/OCM3/IOCB5/RB5                  |

| D2  | LCDBIAS0/SDA3/IC6/PMD7/IOCE7/RE7               | H2  | PGED3/SEG3/AN4/C1INB/RP28/IOCB4/RB4                            |

| D3  | LCDBIAS2/IC4/CTED4/PMD5/IOCE5/RE5              | H3  | COM7/IOCH4/RH4                                                 |

| D4  | COM5/IOCH2/RH2                                 | H4  | IOCH5/RH5                                                      |

| D5  | IOCJ0/RJ0                                      | H5  | SEG29/CVREF/AN10/SDO4/PMA13/IOCB10/RB10                        |

| D6  | Vdd                                            | H6  | VDD                                                            |

| D7  | SEG25/C3INB/U5RX/OC4/PMD14/IOCD6/RD6           | H7  | IOCH8/RH8                                                      |

| D8  | SEG45/PMD13/IOCD13/RD13                        | H8  | IOCF7/RF7                                                      |

| D9  | SEG17/CLC3OUT/RP11/U6CTS/ICM6/INT0/IOCD0/RD0   | H9  | IOCF6/RF6                                                      |

| D10 | Vss                                            | H10 | SCL1/IOCG2/RG2                                                 |

| D11 | SEG15/C3IND/RP3/PMA15/APMCS2/IOCD10/RD10       | H11 | SEG55/SCL2/IOCA2/RA2                                           |

## TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR PIC24FJXXXGA412

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select functions.

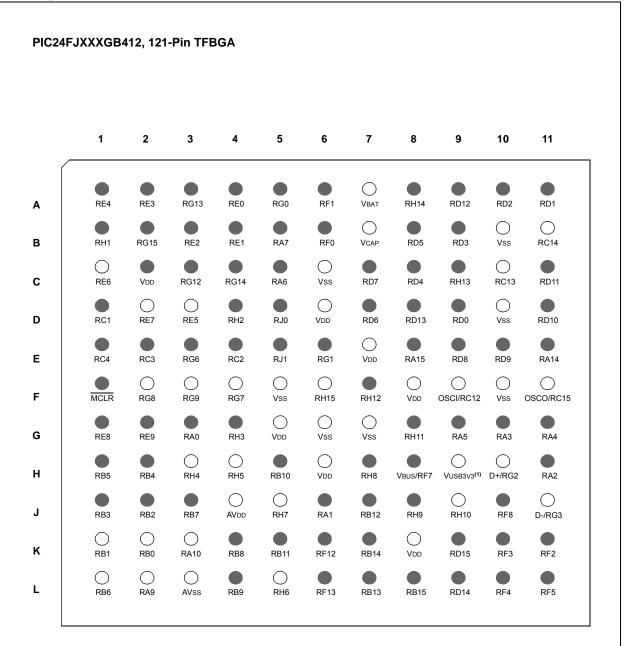

## **Pin Diagrams (Continued)**

Legend: Shaded balls indicate pins tolerant to up to +5.5 VDC. See Table 6 for a complete description of pin functions. Note 1: PIC24FJ256GB412 devices use VUSB3V3 instead of RF6.

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA406

- 06 PIC24FJ64GB406

- PIC24FJ128GA406

PIC24FJ256GA406

- PIC24FJ128GB406

PIC24FJ256GB406

- PIC24FJ64GA410

PIC24FJ64GB410

- PIC24FJ128GA410

PIC24FJ128GB410

- PIC24FJ256GA410

- PIC24FJ256GB410

- PIC24FJ64GA412

- PIC24FJ64GB412

- PIC24FJ128GA412PIC24FJ256GA412

- PIC24FJ128GB412

PIC24FJ256GB412

- The PIC24FJ256GA412/GB412 family expands the capabilities of the PIC24F family by adding a complete selection of advanced analog peripherals to its existing digital features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals, USB On-The-Go (OTG) and a built-in LCD Controller and driver, makes this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

# 1.1 Core Features

## 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

# 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ256GA412/GB412 family of devices incorporates a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep, with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC, for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC), to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, the PIC24FJ256GA412/ GB412 devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

## 1.1.3 DUAL PARTITION FLASH PROGRAM MEMORY

A brand new feature to the PIC24F family is the use of Dual Partition Flash program memory technology. This allows PIC24FJ256GA412/GB412 family devices a range of new operating options not available before:

- Dual Partition Operation, which can store two different applications in their own code partition, and allows for the support of robust bootloader applications and enhanced security

- Live Update Operation, which allows the main application to continue operation while the second Flash partition is being reprogrammed – all without adding Wait states to code execution

- Direct Run-Time Programming from Data RAM, with the option of data compression in the RAM image

PIC24FJ256GA412/GB412 family devices can also operate with their two Flash partitions as one large program memory, providing space for large and complex applications.

|              | Pi             | n/Pad Num       | ber              | l/O Ir |              |                            |

|--------------|----------------|-----------------|------------------|--------|--------------|----------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA |        | Input Buffer | Description                |

| SEG0         | 4              | 10              | E3               | 0      | ANA          | LCD Driver Segment Outputs |

| SEG1         | 8              | 14              | F3               | 0      | ANA          |                            |

| SEG2         | 11             | 20              | H1               | 0      | ANA          |                            |

| SEG3         | 12             | 21              | H2               | 0      | ANA          |                            |

| SEG4         | 13             | 22              | J1               | 0      | ANA          |                            |

| SEG5         | 14             | 23              | J2               | 0      | ANA          | 1                          |

| SEG6         | 15             | 24              | K1               | 0      | ANA          | 1                          |

| SEG7         | 16             | 25              | K2               | 0      | ANA          | 1                          |

| SEG8         | 29             | 43              | K7               | 0      | ANA          |                            |

| SEG9         | 30             | 44              | L8               | 0      | ANA          | ]                          |

| SEG10        | 31             | 49              | L10              | 0      | ANA          | ]                          |

| SEG11        | 32             | 50              | L11              | 0      | ANA          | ]                          |

| SEG12        | 33             | 51              | K10              | 0      | ANA          |                            |

| SEG13        | 42             | 68              | E9               | 0      | ANA          | ]                          |

| SEG14        | 43             | 69              | E10              | 0      | ANA          | ]                          |

| SEG15        | 44             | 70              | D11              | 0      | ANA          |                            |

| SEG16        | 45             | 71              | C11              | 0      | ANA          |                            |

| SEG17        | 46             | 72              | D9               | 0      | ANA          |                            |

| SEG18        | 27             | 41              | J7               | 0      | ANA          |                            |

| SEG19        | 28             | 42              | L7               | 0      | ANA          | ]                          |

| SEG20        | 49             | 76              | A11              | 0      | ANA          |                            |

| SEG21        | 50             | 77              | A10              | 0      | ANA          |                            |

| SEG22        | 51             | 78              | B9               | 0      | ANA          |                            |

| SEG23        | 52             | 81              | C8               | 0      | ANA          |                            |

| SEG24        | 53             | 82              | B8               | 0      | ANA          |                            |

| SEG25        | 54             | 83              | D7               | 0      | ANA          |                            |

| SEG26        | 55             | 84              | C7               | 0      | ANA          |                            |

| SEG27        | 58             | 87              | B6               | 0      | ANA          |                            |

| SEG28        | —              | 61              | G9               | 0      | ANA          |                            |

| SEG29        | 23             | 34              | H5               | 0      | ANA          |                            |

| SEG30        | 22             | 33              | L4               | 0      | ANA          |                            |

| SEG31        | 21             | 32              | K4               | 0      | ANA          |                            |

| SEG32        | —              | 6               | D1               | 0      | ANA          |                            |

| SEG33        | —              | 8               | E2               | 0      | ANA          |                            |

| SEG34        | -              | 18              | G1               | 0      | ANA          |                            |

| SEG35        | —              | 19              | G2               | 0      | ANA          |                            |

| SEG36        |                | 28              | L2               | 0      | ANA          |                            |

| SEG37        | —              | 29              | K3               | 0      | ANA          |                            |

| SEG38        |                | 47              | L9               | 0      | ANA          |                            |

| SEG39        |                | 48              | K9               | 0      | ANA          |                            |

| SEG40        | 34             | 52              | K11              | 0      | ANA          |                            |

### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: T

TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

| U-0                                   | R/W-1                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                              | R/W-0                                                                                                           | U-0                                                                  | R/W-1            | R/W-0           | R/W-0  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|-----------------|--------|

| _                                     | CCT3IP2                                                                                                                                                                                                         | CCT3IP1                                                                                                                                                                                                                                            | CCT3IP0                                                                                                         |                                                                      | OC6IP2           | OC6IP1          | OC6IP0 |

| bit 15                                |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 | bit    |

| U-0                                   | R/W-1                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                              | R/W-0                                                                                                           | U-0                                                                  | R/W-1            | R/W-0           | R/W-0  |

|                                       | OC5IP2                                                                                                                                                                                                          | OC5IP1                                                                                                                                                                                                                                             | OC5IP0                                                                                                          |                                                                      | IC6IP2           | IC6IP1          | IC6IP0 |

| bit 7                                 | 000112                                                                                                                                                                                                          | 00011                                                                                                                                                                                                                                              |                                                                                                                 |                                                                      | 10011 2          |                 | bit    |

|                                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 | Dit    |

| Legend:                               |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 |        |

| R = Readab                            | ole bit                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                       | bit                                                                                                             | U = Unimple                                                          | mented bit, read | d as '0'        |        |

| -n = Value a                          | it POR                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                   |                                                                                                                 | '0' = Bit is cle                                                     | ared             | x = Bit is unkn | iown   |

|                                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 |        |

| bit 15                                | -                                                                                                                                                                                                               | ted: Read as '                                                                                                                                                                                                                                     |                                                                                                                 |                                                                      |                  |                 |        |

| bit 14-12                             |                                                                                                                                                                                                                 | SCCP3 Time                                                                                                                                                                                                                                         | -                                                                                                               | -                                                                    |                  |                 |        |

|                                       | 111 = Interru                                                                                                                                                                                                   | pt is Priority 7 (                                                                                                                                                                                                                                 | highest priority                                                                                                | y interrupt)                                                         |                  |                 |        |

|                                       | •                                                                                                                                                                                                               |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 |        |

|                                       | •                                                                                                                                                                                                               |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 |        |

|                                       | 001 = Interru                                                                                                                                                                                                   |                                                                                                                                                                                                                                                    |                                                                                                                 |                                                                      |                  |                 |        |

|                                       |                                                                                                                                                                                                                 | pt source is dis                                                                                                                                                                                                                                   | abled                                                                                                           |                                                                      |                  |                 |        |

|                                       |                                                                                                                                                                                                                 | 4 · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                            | . 1                                                                                                             |                                                                      |                  |                 |        |

|                                       | -                                                                                                                                                                                                               | ted: Read as '                                                                                                                                                                                                                                     |                                                                                                                 |                                                                      |                  |                 |        |

|                                       | OC6IP<2:0>:                                                                                                                                                                                                     | Output Compa                                                                                                                                                                                                                                       | ire Channel 6                                                                                                   | =                                                                    | ty bits          |                 |        |

|                                       | OC6IP<2:0>:                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    | ire Channel 6                                                                                                   | =                                                                    | ty bits          |                 |        |

|                                       | OC6IP<2:0>:                                                                                                                                                                                                     | Output Compa                                                                                                                                                                                                                                       | ire Channel 6                                                                                                   | =                                                                    | ty bits          |                 |        |

| bit 11<br>bit 10-8                    | OC6IP<2:0>:<br>111 = Interru                                                                                                                                                                                    | Output Compa<br>pt is Priority 7 (                                                                                                                                                                                                                 | ire Channel 6                                                                                                   | =                                                                    | ty bits          |                 |        |

|                                       | OC6IP<2:0>:<br>111 = Interru                                                                                                                                                                                    | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                                                                                                                                             | ire Channel 6<br>highest priorit                                                                                | =                                                                    | ty bits          |                 |        |

| bit 10-8                              | OC6IP<2:0>:<br>111 = Interru                                                                                                                                                                                    | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                                                                                                                         | ire Channel 6<br>highest priority<br>abled                                                                      | =                                                                    | ty bits          |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru                                                                                                                                                                                    | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                                                                                                                               | ire Channel 6<br>highest priorit<br>abled                                                                       | y interrupt)                                                         |                  |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:                                                                                                                     | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0<br>Output Compa                                                                                                                               | abled<br>"highest priority"<br>abled<br>"<br>The Channel 5                                                      | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:                                                                                                                     | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                                                                                                                               | abled<br>"highest priority"<br>abled<br>"<br>The Channel 5                                                      | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:                                                                                                                     | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0<br>Output Compa                                                                                                                               | abled<br>"highest priority"<br>abled<br>"<br>The Channel 5                                                      | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru                                                                                                    | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0<br>Output Compa<br>pt is Priority 7 (                                                                                                         | abled<br>"highest priority"<br>abled<br>"<br>The Channel 5                                                      | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7                     | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru                                                                                   | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                                     | ire Channel 6<br>highest priority<br>abled<br>o'<br>ire Channel 5<br>highest priority                           | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4          | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru                                                                  | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                  | abled<br>highest priority<br>abled<br>b<br>highest priority                                                     | y interrupt)<br>Interrupt Priori                                     |                  |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen                                   | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                         | abled<br>bighest priority<br>abled<br>b'<br>re Channel 5<br>highest priority<br>abled                           | y interrupt)<br>Interrupt Priori<br>y interrupt)                     | ty bits          |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>IC6IP<2:0>: I                                   | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>nput Capture C                     | abled<br>highest priority<br>abled<br>of<br>highest priority<br>abled<br>of<br>Channel 6 Inter                  | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>rupt Priority bi | ty bits          |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>IC6IP<2:0>: I                                   | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                         | abled<br>highest priority<br>abled<br>of<br>highest priority<br>abled<br>of<br>Channel 6 Inter                  | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>rupt Priority bi | ty bits          |                 |        |

|                                       | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>IC6IP<2:0>: I                                   | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>nput Capture C                     | abled<br>highest priority<br>abled<br>of<br>highest priority<br>abled<br>of<br>Channel 6 Inter                  | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>rupt Priority bi | ty bits          |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>IC6IP<2:0>: I<br>111 = Interru                  | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>nput Capture C<br>pt is Priority 7 ( | abled<br>highest priority<br>abled<br>of<br>highest priority<br>abled<br>of<br>Channel 6 Inter                  | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>rupt Priority bi | ty bits          |                 |        |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | OC6IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC5IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>IC6IP<2:0>: I<br>111 = Interru<br>001 = Interru | Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>nput Capture C<br>pt is Priority 7 ( | abled<br>highest priority<br>abled<br>b'<br>tre Channel 5<br>highest priority<br>abled<br>b'<br>Channel 6 Inter | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>rupt Priority bi | ty bits          |                 |        |

## REGISTER 8-32: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

# TABLE 11-4: PORTC REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | ange   |         |        |         |         |    |    |   |   | Bits |   |   |             |         |        |   |   |

|------------------|--------|---------|--------|---------|---------|----|----|---|---|------|---|---|-------------|---------|--------|---|---|

| Register<br>Name | Bit Ra | 15      | 14     | 13      | 12      | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4           | 4 3 2 1 |        |   | 0 |

| ANSC             | 15:0   | —       |        | —       | —       | —  |    |   | — | _    |   | — | ANSC<4:1>   |         |        | — |   |

| TRISC            | 15:0   | TRISC15 |        | —       | TRISC12 | —  |    | - | — |      |   | — | TRISC<4:1>  |         |        | — |   |

| PORTC            | 15:0   |         | PORTC  | <15:12> |         | —  |    |   | — | _    |   | — | PORTC<4:1>  |         |        |   |   |

| LATC             | 15:0   | LATC15  |        |         | LATC12  | —  |    |   | — | _    |   | — | LATC<4:1>   |         |        |   |   |

| ODCC             | 15:0   | ODCC15  |        |         | ODCC12  | —  |    |   | — | _    |   | — |             | ODCC    | <4:1>  |   |   |

| IOCPC            | 15:0   |         | IOCPC< | <15:12> |         | —  |    |   | — | _    |   | — |             | IOCPC   | <4:1>  |   |   |

| IOCNC            | 15:0   |         | IOCNC< | <15:12> |         | —  |    |   | — | _    |   | — | IOCNC<4:1>  |         |        |   |   |

| IOCFC            | 15:0   |         | IOCFC< | :15:12> |         | —  |    |   | — | _    |   | — | IOCFC<4:1>  |         |        |   |   |

| IOCPUC           | 15:0   |         | IOCPUC | <15:12> |         | —  |    |   | — | _    |   | — | IOCPUC<4:1> |         |        | — |   |

| IOCPDC           | 15:0   |         | IOCPDC | <15:12> |         | _  |    |   | _ | _    |   | - |             | IOCPD   | C<4:1> |   | — |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

# TABLE 11-5: PORTD REGISTER MAP<sup>(1)</sup>

| ster<br>ne       | ange      |                                                                                                                                                     |              |  |  |  |  |  |     | Bits       |   |   |  |  |  |

|------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|-----|------------|---|---|--|--|--|

| Register<br>Name | Bit Range | 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1 |              |  |  |  |  |  |     |            |   | 0 |  |  |  |

| ANSD             | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | A   | NSD<15:0>  |   |   |  |  |  |

| TRISD            | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | TF  | RISD<15:0> |   |   |  |  |  |

| PORTD            | 15:0      |                                                                                                                                                     | PORTD<15:0>  |  |  |  |  |  |     |            |   |   |  |  |  |

| LATD             | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | L   | ATD<15:0>  |   |   |  |  |  |

| ODCD             | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | O   | DCD<15:0>  |   |   |  |  |  |

| IOCPD            | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | 10  | CPD<15:0>  |   |   |  |  |  |

| IOCND            | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | 10  | CND<15:0>  |   |   |  |  |  |

| IOCFD            | 15:0      |                                                                                                                                                     | IOCFD<15:0>  |  |  |  |  |  |     |            |   |   |  |  |  |

| IOCPUD           | 15:0      |                                                                                                                                                     | IOCPUD<15:0> |  |  |  |  |  |     |            |   |   |  |  |  |

| IOCPDD           | 15:0      |                                                                                                                                                     |              |  |  |  |  |  | 100 | CPDD<15:0> | > |   |  |  |  |

**Legend:** — = unimplemented, read as '0'.

Note 1: PORT register maps show full pin count devices. Please refer to Table 1-4 and Table 1-5 for pin count-specific PORT I/O implementation.

# 14.5 Auxiliary Output

The MCCPx and SCCPx modules have an auxiliary (secondary) output that provides other peripherals access to internal module signals. The auxiliary output is intended to connect to other MCCP or SCCP modules, or other digital peripherals, to provide these types of functions:

- Time Base Synchronization

- Peripheral Trigger and Clock Inputs

- Signal Gating

The type of output signal is selected using the AUXOUT<1:0> control bits (CCPxCON2H<4:3>). The type of output signal is also dependent on the module operating mode.

On the PIC24FJ256GA412/GB412 family of devices, only the CTMU discharge trigger has access to the auxiliary output signal.

| AUXOUT<1:0> | CCSEL | MOD<3:0> | Comments                  | Signal Description                  |

|-------------|-------|----------|---------------------------|-------------------------------------|

| 00          | х     | xxxx     | Auxiliary output disabled | No Output                           |

| 01          | 0     | 0000     | Time Base modes           | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Special Event Trigger Output        |

| 11          |       |          |                           | No Output                           |

| 01          | 0     | 0001     | Output Compare modes      | Time Base Period Reset or Rollover  |

| 10          |       | through  |                           | Output Compare Event Signal         |

| 11          |       | 1111     |                           | Output Compare Signal               |

| 01          | 1     | xxxx     | Input Capture modes       | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Reflects the Value of the ICDIS bit |

| 11          |       |          |                           | Input Capture Event Signal          |

## TABLE 14-4: AUXILIARY OUTPUT

# 16.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Output Compare with Dedicated Timer" (DS70005159). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ256GA412/GB412 family all feature six independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-Configurable for 32-Bit Operation in All Modes by Cascading Two Adjacent Modules

- Synchronous and Trigger Modes of Output Compare Operation, with up to 31 User-Selectable Trigger/Sync Sources Available

- Two Separate Period Registers (a main register, OCxR, and a secondary register, OCxRS) for Greater Flexibility in Generating Pulses of Varying Widths

- Configurable for Single Pulse or Continuous Pulse Generation on an Output Event, or Continuous PWM Waveform Generation

- Up to 6 Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

## 16.1 General Operating Modes

### 16.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSEL<4:0> bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

## 16.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module, Output Compare x (OCx), provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module, Output Compare y (OCy), provides the Most Significant 16 bits. Wrap arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more information on cascading, refer to the *"dsPIC33/PIC24 Family Reference Manual",* **"Output Compare with Dedicated Timer"** (DS70005159).

To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L and SPIxCON1H registers with the MSTEN bit (SPIxCON1L<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTATL<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 5. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF registers.

- 2. If using interrupts:

- a) Clear the SPIxBUFL and SPIxBUFH registers.

- b) Set the interrupt enable bits in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with the MSTEN bit (SPIxCON1L<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1L<8>) is set, then the SSEN bit (SPIxCON1L<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

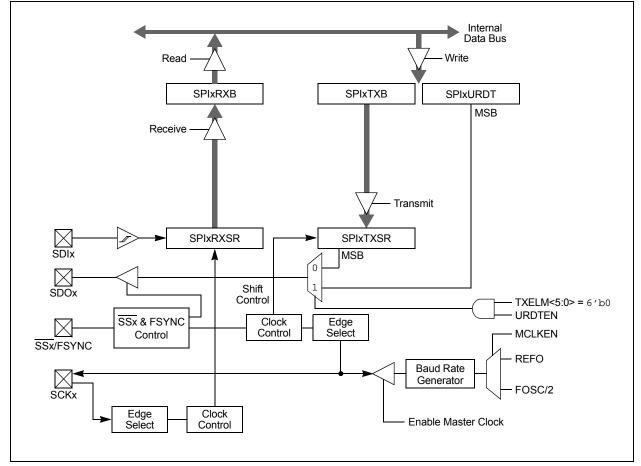

# FIGURE 17-1: SPIx MODULE BLOCK DIAGRAM (STANDARD MODE)

To set up the SPIx module for Audio mode:

- 1. Clear the SPIxBUFL and SPIxBUFH registers.

- 2. If using interrupts:

- a) Clear the interrupt flag bits in the respective IFSx register.

- b) Set the interrupt enable bits in the respective IECx register.

- a) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1L, SPIxCON1H and SPIxCON2L registers with AUDEN (SPIxCON1H<15>) = 1.

- 4. Clear the SPIROV bit (SPIxSTATL<6>).

- Enable SPIx operation by setting the SPIEN bit (SPIxCON1L<15>).

- 6. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL and SPIxBUFH registers.

## REGISTER 17-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| Legend:             |       |         |        |                         |                         |       |                    |

|---------------------|-------|---------|--------|-------------------------|-------------------------|-------|--------------------|

| bit 7               |       |         |        |                         |                         |       | bit 0              |

| SSEN <sup>(2)</sup> | CKP   | MSTEN   | DISSDI | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE | ENHBUF             |

| R/W-0               | R/W-0 | R/W-0   | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| bit 15              |       |         |        |                         |                         |       | bit 8              |

| SPIEN               |       | SPISIDL | DISSDO | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP   | CKE <sup>(1)</sup> |

| R/W-0               | U-0   | R/W-0   | R/W-0  | R/W-0                   | R/W-0                   | R/W-0 | R/W-0              |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15 SPIEN: SPIx On bit

- 1 = Enables module

- 0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR modifications

#### bit 14 Unimplemented: Read as '0'

- bit 13 SPISIDL: SPIx Stop in Idle Mode bit

- 1 = Halts in CPU Idle mode

- 0 = Continues to operate in CPU Idle mode

#### bit 12 DISSDO: Disable SDOx Output Port bit

1 = SDOx pin is not used by the module; pin is controlled by port function

### 0 = SDOx pin is controlled by the module

#### bit 11-10 MODE32 and MODE16: Serial Word Length Select bits<sup>(1,4)</sup>

| MODE32 | MODE16 | AUDEN | Communication                                         |  |  |  |  |  |

|--------|--------|-------|-------------------------------------------------------|--|--|--|--|--|

| 1      | x      |       | 32-Bit                                                |  |  |  |  |  |

| 0      | 1      | 0     | 16-Bit                                                |  |  |  |  |  |

| 0      | 0      |       | 8-Bit                                                 |  |  |  |  |  |

| 1      | 1      |       | 24-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 1      | 0      | 1     | 32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 0      | 1      | T     | 16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |  |  |  |  |  |

| 0      | 0      |       | 16-Bit FIFO, 16-Bit Channel/32-Bit Frame              |  |  |  |  |  |

#### **Note 1:** When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.

- 2: When FRMEN = 1, SSEN is not used.

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

### 20.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the "On-The-Go Supplement" to the "USB 2.0 Specification" for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition, via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power down the VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation and drives Reset signaling.

# 20.7 USB OTG Module Registers

There are a total of 37 memory-mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 20-1 and Register 20-2, are shown separately in Section 20.2 "USB Buffer Descriptors and the BDT".

All USB OTG registers are implemented in the Least Significant Byte (LSB) of the register. Bits in the upper byte are unimplemented and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

The registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment.

- U1FRML and U1FRMH: Contain the 11-bit byte counter for the current data frame.

# REGISTER 20-7: U1CON: USB CONTROL REGISTER (DEVICE MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R-x, HSC | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

|-------|----------|--------|-----|--------|--------|--------|-------|

| —     | SE0      | PKTDIS | _   | HOSTEN | RESUME | PPBRST | USBEN |

| bit 7 |          |        |     |        |        |        | bit 0 |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6    | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                           |

|          | <ul> <li>1 = Single-ended zero is active on the USB bus</li> <li>0 = No single-ended zero is detected</li> </ul>                                                                                               |

| bit 5    | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                            |

|          | <ul> <li>1 = SIE token and packet processing are disabled; automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing are enabled</li> </ul>                                |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 3    | HOSTEN: Host Mode Enable bit                                                                                                                                                                                   |

|          | <ul> <li>1 = USB host capability is enabled; pull-downs on D+ and D- are activated in hardware</li> <li>0 = USB host capability is disabled</li> </ul>                                                         |

| bit 2    | RESUME: Resume Signaling Enable bit                                                                                                                                                                            |

|          | 1 = Resume signaling is activated                                                                                                                                                                              |

|          | 0 = Resume signaling is disabled                                                                                                                                                                               |

| bit 1    | PPBRST: Ping-Pong Buffers Reset bit                                                                                                                                                                            |

|          | <ul> <li>1 = Resets all Ping-Pong Buffer Pointers to the even BD banks</li> <li>0 = Ping-Pong Buffer Pointers are not reset</li> </ul>                                                                         |

| bit 0    | USBEN: USB Module Enable bit                                                                                                                                                                                   |

|          | <ul> <li>1 = USB module and supporting circuitry are enabled (device attached); D+ pull-up is activated in hardware</li> <li>0 = USB module and supporting circuitry are disabled (device detached)</li> </ul> |

## REGISTER 20-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0                    | U-0                                                                                                                                      | U-0              | U-0                                 | U-0                               | U-0            | U-0                | U-0   |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|-----------------------------------|----------------|--------------------|-------|--|--|--|--|

| _                      | —                                                                                                                                        | —                | —                                   | —                                 | —              | —                  | _     |  |  |  |  |

| bit 15                 |                                                                                                                                          |                  |                                     |                                   |                |                    | bit 8 |  |  |  |  |

|                        |                                                                                                                                          |                  |                                     |                                   |                |                    |       |  |  |  |  |

| R/W-0                  | R/W-0                                                                                                                                    | U-0              | R/W-0                               | U-0                               | U-0            | R/W-0              | R/W-0 |  |  |  |  |

| UTEYE                  | UOEMON <sup>(1)</sup>                                                                                                                    | —                | USBSIDL                             | —                                 | —              | PPB1               | PPB0  |  |  |  |  |

| bit 7                  |                                                                                                                                          |                  |                                     |                                   |                |                    | bit   |  |  |  |  |

|                        |                                                                                                                                          |                  |                                     |                                   |                |                    |       |  |  |  |  |

| Legend:<br>R = Readabl | le hit                                                                                                                                   | W = Writable     | hit                                 | U = Unimplerr                     | onted hit rea  | ad as 'O'          |       |  |  |  |  |

| -n = Value at          |                                                                                                                                          | '1' = Bit is set |                                     | $0^{\circ} = \text{Bit is clear}$ |                | x = Bit is unknown |       |  |  |  |  |

|                        | IFUR                                                                                                                                     |                  |                                     |                                   | areu           |                    | IOWIT |  |  |  |  |

| bit 15-8               | Unimplemen                                                                                                                               | ted: Read as     | 0'                                  |                                   |                |                    |       |  |  |  |  |

| bit 7                  | •                                                                                                                                        |                  |                                     |                                   |                |                    |       |  |  |  |  |

| SIC 1                  | <b>UTEYE:</b> USB Eye Pattern Test Enable bit<br>1 = Eye pattern test is enabled                                                         |                  |                                     |                                   |                |                    |       |  |  |  |  |

|                        | 0 = Eye pattern test is disabled                                                                                                         |                  |                                     |                                   |                |                    |       |  |  |  |  |

| bit 6                  | <b>UOEMON:</b> USB $\overline{OE}$ Monitor Enable bit <sup>(1)</sup>                                                                     |                  |                                     |                                   |                |                    |       |  |  |  |  |

|                        | $1 = \overline{OE} \text{ signa}$<br>$0 = \overline{OE} \text{ signa}$                                                                   |                  | dicates interval                    | s during which                    | the D+/D- line | es are driving     |       |  |  |  |  |