Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                          |

| Number of I/O              | 85                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga410-i-pt |

TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

|                 | Pin/Pad Number |                 |                  |     |              |                           |

|-----------------|----------------|-----------------|------------------|-----|--------------|---------------------------|

| Pin Function    | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description               |

| IOCC1           | <u> </u>       | 6               | D1               | I   | ST           | PORTC Interrupt-on-Change |

| IOCC2           | _              | 7               | E4               | 1   | ST           |                           |

| IOCC3           | _              | 8               | E2               | 1   | ST           |                           |

| IOCC4           | _              | 9               | E!               | I   | ST           |                           |

| IOCC12          | 39             | 63              | F9               | I   | ST           |                           |

| IOCC13          | 47             | 73              | C10              | 1   | ST           |                           |

| IOCC14          | 48             | 74              | B11              | I   | ST           |                           |

| IOCC15          | 40             | 64              | F11              | - 1 | ST           |                           |

| IOCD0           | 46             | 72              | D9               | I   | ST           | PORTD Interrupt-on-Change |

| IOCD1           | 49             | 76              | A11              | 1   | ST           |                           |

| IOCD2           | 50             | 77              | A10              | I   | ST           |                           |

| IOCD3           | 51             | 78              | В9               | I   | ST           |                           |

| IOCD4           | 52             | 81              | C8               | I   | ST           |                           |

| IOCD5           | 53             | 82              | B8               | I   | ST           |                           |

| IOCD6           | 54             | 83              | D7               | - 1 | ST           |                           |

| IOCD7           | 55             | 84              | C7               | I   | ST           |                           |

| IOCD8           | 42             | 68              | E9               | I   | ST           |                           |

| IOCD9           | 43             | 69              | E10              | I   | ST           |                           |

| IOCD10          | 44             | 70              | D11              | 1   | ST           |                           |

| IOCD11          | 45             | 71              | C11              | I   | ST           |                           |

| IOCD12          | _              | 79              | A9               | I   | ST           |                           |

| IOCD13          | _              | 80              | D8               | 1   | ST           |                           |

| IOCD14          | _              | 47              | L9               | 1   | ST           |                           |

| IOCD15          | _              | 48              | K9               | 1   | ST           |                           |

| IOCE0           | 60             | 93              | A4               | 1   | ST           | PORTE Interrupt-on-Change |

| IOCE1           | 61             | 94              | B4               | 1   | ST           |                           |

| IOCE2           | 62             | 98              | В3               | 1   | ST           |                           |

| IOCE3           | 63             | 99              | A2               | ı   | ST           |                           |

| IOCE4           | 64             | 100             | A1               | I   | ST           |                           |

| IOCE5           | 1              | 3               | D3               | I   | ST           |                           |

| IOCE6           | 2              | 4               | C1               | ı   | ST           |                           |

| IOCE7           | 3              | 5               | D2               | I   | ST           |                           |

| IOCE8           | _              | 18              | G1               | I   | ST           |                           |

| IOCE9           | _              | 19              | G2               | ı   | ST           |                           |

| Legende TTL = 1 | CTL input buf  |                 | •                |     |              | Trigger input huffer      |

**Legend:** TTL = TTL input buffer

ANA = Analog-level input/output DIG = Digital input/output

SMB = SMBus

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- · 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

#### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTIBIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multibit arithmetic and logic shifts. Multibit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multibit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

| Instruction | Description                                                 |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|--|--|--|

| ASR         | Arithmetic Shift Right Source register by one or more bits. |  |  |  |  |  |  |

| SL          | Shift Left Source register by one or more bits.             |  |  |  |  |  |  |

| LSR         | Logical Shift Right Source register by one or more bits.    |  |  |  |  |  |  |

TABLE 4-10: SFR BLOCK 500h

| Register     | Address  | All Resets        | Register                 | Address | All Resets        | Register              | Address | All Resets                              |

|--------------|----------|-------------------|--------------------------|---------|-------------------|-----------------------|---------|-----------------------------------------|

| DMA (Continu | ued)     |                   | CRYTXTB6                 | 564     | xxxxxxxxxxxxx     | U1EP8 <sup>(1)</sup>  | 5B2     | 0000000000000000                        |

| DMAINT5      | 500      | 00000000000000000 | CRYTXTB7                 | 566     | xxxxxxxxxxxxx     | U1EP9 <sup>(1)</sup>  | 5B4     | 0000000000000000                        |

| DMASRC5      | 502      | 00000000000000000 | CRYTXTC0                 | 558     | xxxxxxxxxxxxx     | U1EP10 <sup>(1)</sup> | 5B6     | 0000000000000000                        |

| DMADST5      | 504      | 00000000000000000 | CRYTXTC1                 | 56A     | xxxxxxxxxxxxx     | U1EP11 <sup>(1)</sup> | 5B8     | 0000000000000000                        |

| DMACNT5      | 506      | 00000000000000001 | CRYTXTC2                 | 56C     | xxxxxxxxxxxxx     | U1EP12 <sup>(1)</sup> | 5BA     | 0000000000000000                        |

| Cryptographi | c Engine |                   | CRYTXTC3                 | 56E     | xxxxxxxxxxxxxx    | U1EP13 <sup>(1)</sup> | 5BC     | 0000000000000000                        |

| CRYCONL      | 51C      | x0xxxx0xxxxxxxx   | CRYTXTC4                 | 570     | xxxxxxxxxxxxx     | U1EP14 <sup>(1)</sup> | 5BE     | 0000000000000000                        |

| CRYCONH      | 51E      | 0xxxxxxxxx0xxxx   | CRYTXTC5                 | 572     | xxxxxxxxxxxxxx    | U1EP15 <sup>(1)</sup> | 5C0     | 0000000000000000                        |

| CRYSTAT      | 520      | 00000000xxxx0xxx  | CRYTXTC6                 | 574     | xxxxxxxxxxxxx     | LCD Controll          | er      |                                         |

| CRYOTP       | 524      | 00000000xxxxxxx   | CRYTXTC7                 | 576     | xxxxxxxxxxxxx     | LCDCON                | 5C2     | 000000000000000000000000000000000000000 |

| CRYKEY0      | 528      | xxxxxxxxxxxxx     | USB                      |         |                   | LCDREF                | 5C4     | 000000000000000000000000000000000000000 |

| CRYKEY1      | 52A      | xxxxxxxxxxxxxx    | U1OTGIR <sup>(1)</sup>   | 578     | 00000000000000000 | LCDPS                 | 5C6     | 00000000000000000000000000000000000000  |

| CRYKEY2      | 52C      | xxxxxxxxxxxxx     | U1OTGIE <sup>(1)</sup>   | 57A     | 00000000000000000 | LCDDATA0              | 5C8     | 000000000000000000000000000000000000000 |

| CRYKEY3      | 52E      | xxxxxxxxxxxxx     | U1OTGSTAT <sup>(1)</sup> | 57C     | 00000000000000000 | LCDDATA1              | 5CA     | 00000000000000000000000000000000000000  |

| CRYKEY4      | 530      | xxxxxxxxxxxxxx    | U1OTGCON <sup>(1)</sup>  | 57E     | 00000000000000000 | LCDDATA2              | 5CC     | 00000000000000000000000000000000000000  |

| CRYKEY5      | 532      | xxxxxxxxxxxxx     | U1PWRC <sup>(1)</sup>    | 580     | 00000000x0000000  | LCDDATA3              | 5CE     | 000000000000000000000000000000000000000 |

| CRYKEY6      | 534      | xxxxxxxxxxxxx     | U1IR <sup>(1)</sup>      | 582     | 00000000000000000 | LCDDATA4              | 5D0     | 000000000000000000000000000000000000000 |

| CRYKEY7      | 536      | xxxxxxxxxxxxx     | U1IE <sup>(1)</sup>      | 584     | 00000000000000000 | LCDDATA5              | 5D2     | 000000000000000000000000000000000000000 |

| CRYKEY8      | 538      | xxxxxxxxxxxxx     | U1EIR <sup>(1)</sup>     | 586     | 00000000000000000 | LCDDATA6              | 5D4     | 000000000000000000000000000000000000000 |

| CRYKEY9      | 53A      | xxxxxxxxxxxxx     | U1EIE <sup>(1)</sup>     | 588     | 00000000000000000 | LCDDATA7              | 5D6     | 000000000000000000000000000000000000000 |

| CRYKEY10     | 53C      | xxxxxxxxxxxxx     | U1STAT <sup>(1)</sup>    | 58A     | 00000000000000000 | LCDDATA8              | 5D8     | 000000000000000000000000000000000000000 |

| CRYKEY11     | 53E      | xxxxxxxxxxxxx     | U1CON <sup>(1)</sup>     | 58C     | 00000000xx0000000 | LCDDATA9              | 5DA     | 000000000000000000000000000000000000000 |

| CRYKEY12     | 540      | xxxxxxxxxxxxx     | U1ADDR <sup>(1)</sup>    | 58E     | 000000000xxxxxx   | LCDDATA10             | 5DC     | 000000000000000000000000000000000000000 |

| CRYKEY13     | 542      | xxxxxxxxxxxxxx    | U1BDTP1 <sup>(1)</sup>   | 590     | 00000000000000000 | LCDDATA11             | 5DE     | 00000000000000000000000000000000000000  |

| CRYKEY14     | 544      | xxxxxxxxxxxxxx    | U1FRML <sup>(1)</sup>    | 592     | 00000000000000000 | LCDDATA12             | 5E0     | 00000000000000000000000000000000000000  |

| CRYKEY15     | 546      | xxxxxxxxxxxxxx    | U1FRMH <sup>(1)</sup>    | 594     | 00000000000000000 | LCDDATA13             | 5E2     | 00000000000000000000000000000000000000  |

| CRYTXTA0     | 548      | xxxxxxxxxxxxx     | U1TOK <sup>(1)</sup>     | 596     | 00000000000000000 | LCDDATA14             | 5E4     | 00000000000000000000000000000000000000  |

| CRYTXTA1     | 54A      | xxxxxxxxxxxxxx    | U1SOF <sup>(1)</sup>     | 598     | 00000000000000000 | LCDDATA15             | 5E6     | 00000000000000000000000000000000000000  |

| CRYTXTA2     | 54C      | xxxxxxxxxxxxxx    | U1BDTP2 <sup>(1)</sup>   | 59A     | 00000000000000000 | LCDDATA16             | 5E8     | 00000000000000000000000000000000000000  |

| CRYTXTA3     | 54E      | xxxxxxxxxxxxx     | U1BDTP3 <sup>(1)</sup>   | 59C     | 00000000000000000 | LCDDATA17             | 5EA     | 00000000000000000000000000000000000000  |

| CRYTXTA4     | 550      | xxxxxxxxxxxxxx    | U1CNFG1 <sup>(1)</sup>   | 59E     | 00000000000000000 | LCDDATA18             | 5EC     | 00000000000000000000000000000000000000  |

| CRYTXTA5     | 552      | xxxxxxxxxxxxxx    | U1CNFG2 <sup>(1)</sup>   | 5A0     | 00000000000000000 | LCDDATA19             | 5EE     | 00000000000000000000000000000000000000  |

| CRYTXTA6     | 554      | xxxxxxxxxxxxx     | U1EP0 <sup>(1)</sup>     | 5A2     | 00000000000000000 | LCDDATA20             | 5F0     | 000000000000000000000000000000000000000 |

| CRYTXTA7     | 556      | xxxxxxxxxxxxx     | U1EP1 <sup>(1)</sup>     | 5A4     | 00000000000000000 | LCDDATA21             | 5F2     | 000000000000000000000000(2)             |

| CRYTXTB0     | 558      | xxxxxxxxxxxxx     | U1EP2 <sup>(1)</sup>     | 5A6     | 00000000000000000 | LCDDATA22             | 5F4     | 000000000000000000000000(2)             |

| CRYTXTB1     | 55A      | xxxxxxxxxxxxx     | U1EP3 <sup>(1)</sup>     | 5A8     | 00000000000000000 | LCDDATA23             | 5F6     | 00000000000000000000000(2)              |

| CRYTXTB2     | 55C      | xxxxxxxxxxxxxx    | U1EP4 <sup>(1)</sup>     | 5AA     | 00000000000000000 | LCDDATA24             | 5F8     | 00000000000000000000000000000000000000  |

| CRYTXTB3     | 55E      | xxxxxxxxxxxxx     | U1EP5 <sup>(1)</sup>     | 5AC     | 00000000000000000 | LCDDATA25             | 5FA     | 000000000000000000000000000000000000000 |

| CRYTXTB4     | 560      | xxxxxxxxxxxxx     | U1EP6 <sup>(1)</sup>     | 5AE     | 00000000000000000 | LCDDATA26             | 5FC     | 000000000000000000000000000000000000000 |

| CRYTXTB5     | 562      | xxxxxxxxxxxxx     | U1EP7 <sup>(1)</sup>     | 5B0     | 00000000000000000 | LCDDATA27             | 5FE     | 000000000000000000000000(2)             |

$\textbf{Legend:} \ \ \textbf{x} = \text{unknown or indeterminate value. Reset and address values are in hexadecimal.}$

Note 1: Implemented in PIC24FJXXXGB4XX devices only.

2: LCD registers are only reset on a device POR.

#### 8.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS70000600). The information in this data sheet supersedes the information in the FRM.

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- Up to 8 Processor Exceptions and Software Traps

- · Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with up to 118 Vectors

- Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority

Level

- Alternate Interrupt Vector Table (AIVT) for Debug Support

- · Fixed Interrupt Entry and Return Latencies

#### 8.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 8-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 source interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ256GA412/GB412 family devices implement non-maskable traps and unique interrupts. These are summarized in Table 8-1 and Table 8-2.

## 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The ALTIVT (INTCON2<8>) control bit provides access to the AIVT. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application, and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the PC to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

Note:

Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-14: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0    | R/W-0  | R/W-0 |

|--------|--------|-------|--------|--------|----------|--------|-------|

| NVMIE  | DMA1IE | AD1IE | U1TXIE | U1RXIE | SPI1TXIE | SPI1IE | T3IE  |

| bit 15 |        |       |        |        |          |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0, | R/W-0 | R/W-0  |

|-------|-------|-------|--------|-------|--------|-------|--------|

| T2IE  | OC2IE | IC2IE | DMA0IE | T1IE  | OC1IE  | IC1IE | INT0IE |

| bit 7 |       |       | •      |       |        |       | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 **NVMIE:** Flash Memory Write/Program Done Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 14 DMA1IE: DMA Channel 1 Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 13 **AD1IE:** 12-Bit Pipeline A/D Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 12 **U1TXIE:** UART1 Transmitter Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 11 **U1RXIE:** UART1 Receiver Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 10 SPI1TXIE: SPI1 Transmit Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 9 SPI1IE: SPI1 General Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 8 T3IE: Timer3 Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 7 T2IE: Timer2 Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 6 OC2IE: Output Compare Channel 2 Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled bit 5 IC2IE: Input Capture Channel 2 Interrupt Enable bit 1 = Interrupt request is enabled 0 = Interrupt request is not enabled DMA0IE: DMA Channel 0 Interrupt Flag Enable bit bit 4 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

A recommended code sequence for a clock switch includes the following:

- Disable interrupts during the OSCCON register unlock and write sequence.

- 2. Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON

in two back-to-back instructions.

- Set the OSWEN bit in the instruction immediately following the unlock sequence.

- Continue to execute code that is not clock-sensitive (optional).

- Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch

was successful. If OSWEN is still set, then

check the LOCK bit to determine the cause of

the failure

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

# EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

```

;Place the new oscillator selection in WO

;OSCCONH (high byte) Unlock Sequence

#OSCCONH, w1

MOV

MOV

#0x78, w2

MOV

#0x9A, w3

MOV.b

w2, [w1]

MOV.b

w3, [w1]

;Set new oscillator selection

MOV.b

WREG, OSCCONH

;OSCCONL (low byte) unlock sequence

MOV

#OSCCONL, w1

MOV

#0x46, w2

MOV

#0x57, w3

w2, [w1]

MOV.b

MOV.b

w3, [w1]

;Start oscillator switch operation

OSCCON,#0

```

#### 9.5 FRC Active Clock Tuning

PIC24FJ256GA412/GB412 family devices include an automatic mechanism to calibrate the FRC during run time. This system uses active clock tuning from a source of known accuracy to maintain the FRC within a very narrow margin of its nominal 8 MHz frequency. This allows for a frequency accuracy that is well within the requirements of the "USB 2.0 Specification", regarding full-speed USB devices.

Note:

The self-tune feature maintains sufficient accuracy for operation in USB Device mode. For applications that function as a USB host, a high-accuracy clock source (±0.05%) is still required.

The self-tune system is controlled by the bits in the upper half of the OSCTUN register. Setting the STEN bit (OSCTUN<15>) enables the self-tuning feature, allowing the hardware to calibrate to a source selected by the STSRC bit (OSCTUN<12>). When STSRC = 1, the system uses the Start-of-Frame (SOF) packets from an external USB host for its source. When STSRC = 0, the system uses the crystal-controlled SOSC for its calibration source. Regardless of the source, the system uses the TUN<5:0> bits (OSCTUN<5:0>) to change the FRC Oscillator's frequency. Frequency monitoring and adjustment is dynamic, occurring continuously during run time. While the system is active, the TUNx bits cannot be written to by software.

Note:

To use the USB as a reference clock tuning source (STSRC = 1), the micro-controller must be configured for USB device operation and connected to a non-suspended USB host or hub port.

If the SOSC is to be used as the reference clock tuning source (STSRC = 0), the SOSC must also be enabled for clock tuning to occur.

The self-tune system can generate a hardware interrupt, FSTIF. The interrupt can result from a drift of the FRC from the reference by greater than 0.2%, in either direction, or whenever the frequency deviation is beyond the ability of the TUNx bits to correct (i.e., greater than 1.5%). The STLOCK and STOR status bits (OSCTUN<11,9>) are used to indicate these conditions.

The STLPOL and STORPOL bits (OSCTUN<10,8>) configure the FSTIF interrupt to occur in the presence or the absence of the conditions. It is the user's responsibility to monitor both the STLOCK and STOR bits to determine the exact cause of the interrupt.

Note:

The STLPOL and STORPOL bits should be ignored when the self-tune system is disabled (STEN = 0).

#### 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

# 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits, which decides if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

# 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Information on voltage tolerance is provided in the pinout diagrams in the beginning of this data sheet. For more information, refer to **Section 36.0** "**Electrical Characteristics**" for more details.

TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

| Pin Function   | ANSx<br>Setting | TRISx<br>Setting | Comments                                                                                                                             |

|----------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1               | 1                | It is recommended to keep ANSx = 1.                                                                                                  |

| Analog Output  | 1               | 1                | It is recommended to keep ANSx = 1.                                                                                                  |

| Digital Input  | 0               | 1                | Firmware must wait at least one instruction cycle after configuring a pin as a digital input before a valid input value can be read. |

| Digital Output | 0               | 0                | Make sure to disable the analog output function on the pin if any is present.                                                        |

#### REGISTER 14-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0        | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0                | R/W-0                | R/W-0                |  |

|--------------|--------|--------|--------|-----|----------------------|----------------------|----------------------|--|

| OETRIG       | OSCNT2 | OSCNT1 | OSCNT0 | _   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> |  |

| bit 15 bit 8 |        |        |        |     |                      |                      |                      |  |

| U-0   | U-0 | R/W-0  | R/W-0                 | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  |

|-------|-----|--------|-----------------------|---------|---------|------------------------|------------------------|

| _     | _   | POLACE | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7 |     |        |                       |         |         |                        | bit 0                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **OETRIG:** CCPx Dead-Time Select bit

1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered

0 = Normal output pin operation

bit 14-12 OSCNT<2:0>: One-Shot Event Count bits

111 = Extends one-shot event by 7 time base periods (8 time base periods total)

110 = Extends one-shot event by 6 time base periods (7 time base periods total)

101 = Extends one-shot event by 5 time base periods (6 time base periods total)

100 = Extends one-shot event by 4 time base periods (5 time base periods total)

011 = Extends one-shot event by 3 time base periods (4 time base periods total)

010 = Extends one-shot event by 2 time base periods (3 time base periods total)

001 = Extends one-shot event by 1 time base period (2 time base periods total)

000 = Does not extend one-shot trigger event

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OUTM<2:0>: PWMx Output Mode Control bits<sup>(1)</sup>

111 = Reserved

110 = Output Scan mode

101 = Brush DC Output mode, forward

100 = Brush DC Output mode, reverse

011 = Reserved

010 = Half-Bridge Output mode

001 = Push-Pull Output mode

000 = Steerable Single Output mode

bit 7-6 **Unimplemented:** Read as '0'

bit 5 POLACE: CCPx Output Pins, OCMx, OCMxA, OCMxC and OCMxE, Polarity Control bit

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 4 **POLBDF:** CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit<sup>(1)</sup>

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 3-2 PSSACE<1:0>: PWMx Output Pins, OCMx, OCMxA, OCMxC and OCMxE, Shutdown State Control bits

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are tri-stated when a shutdown event occurs

bit 1-0 PSSBDF<1:0>: PWMx Output Pins, OCxB, OCxD, and OCxF, Shutdown State Control bits<sup>(1)</sup>

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are in a high-impedance state when a shutdown event occurs

**Note 1:** These bits are implemented in MCCPx modules only.

#### REGISTER 18-2: I2CxCONH: I2Cx CONTROL REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   |     | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | PCIE  | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6 **PCIE:** Stop Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only).

1 = Enables interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled

bit 5 **SCIE**: Start Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled

bit 4 **BOEN:** Buffer Overwrite Enable bit (I<sup>2</sup>C Slave mode only)

1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state of the I2COV bit only if RBF bit = 0

0 = I2CxRCV is only updated when I2COV is clear

bit 3 SDAHT: SDAx Hold Time Selection bit

1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx

0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

bit 2 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

If, on the rising edge of SCLx, SDAx is sampled low when the module is outputting a high state, the BCL bit is set and the bus goes Idle. This detection mode is only valid during data and ACK transmit sequences.

1 = Enables slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a matching received address byte; SCKREL bit (I2CxCONH<12>) will be cleared and the SCLx will be held low

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a received data byte; slave hardware clears the SCKREL bit (I2CxCONH<12>) and SCLx is held low

0 = Data holding is disabled

#### REGISTER 22-4: LCDSEx: LCD SEGMENT x ENABLE REGISTER

| R/W-0                     | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

|---------------------------|----------|----------|----------|----------|----------|---------|---------|

| SE(n+15) <sup>(1,2)</sup> | SE(n+14) | SE(n+13) | SE(n+12) | SE(n+11) | SE(n+10) | SE(n+9) | SE(n+8) |

| bit 15                    |          |          |          |          |          |         | bit 8   |

| R/W-0   | R/W-0 |

|---------|---------|---------|---------|---------|---------|---------|-------|

| SE(n+7) | SE(n+6) | SE(n+5) | SE(n+4) | SE(n+3) | SE(n+2) | SE(n+1) | SE(n) |

| bit 7   |         |         |         |         |         |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **SE(n+15):SE(n)**: Segment Enable bits

For LCDSE0: n = 0For LCDSE1: n = 16For LCDSE2: n = 32For LCDSE3:  $n = 48^{(1,2)}$

1 = Segment function of the pin is enabled, digital I/O is disabled

0 = Segment function of the pin is disabled, digital I/O is enabled

Note 1: SE63 (LCDSE3<15>) is not implemented.

2: For the SEG49 to work correctly, the JTAG needs to be disabled.

#### REGISTER 22-5: LCDDATAX: LCD DATA x REGISTER

| R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0    | R/W-0    |

|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| S(n+15)Cy | S(n+14)Cy | S(n+13)Cy | S(n+12)Cy | S(n+11)Cy | S(n+10)Cy | S(n+9)Cy | S(n+8)Cy |

| bit 15    |           |           |           |           |           |          | bit 8    |

| R/W-0    | R/W-0  |

|----------|----------|----------|----------|----------|----------|----------|--------|

| S(n+7)Cy | S(n+6)Cy | S(n+5)Cy | S(n+4)Cy | S(n+3)Cy | S(n+2)Cy | S(n+1)Cy | S(n)Cy |

| bit 7    |          |          |          |          |          |          | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 S(n+15)Cy:S(n)Cy: Pixel On bits

For Registers, LCDDATA0 through LCDDATA3: n = (16x), y = 0

For Registers, LCDDATA4 through LCDDATA7: n = (16(x - 4)), y = 1

For Registers, LCDDATA8 through LCDDATA11: n = (16(x - 8)), y = 2

For Registers, LCDDATA12 through LCDDATA15: n = (16(x - 12)), y = 3

For Registers, LCDDATA16 through LCDDATA19: n = (16(x - 16)), y = 4

For Registers, LCDDATA20 through LCDDATA23: n = (16(x - 20)), y = 5

For Registers, LCDDATA24 through LCDDATA27: n = (16(x - 24)), y = 6

For Registers, LCDDATA28 through LCDDATA31: n = (16(x - 28)), y = 7

1 = Pixel is on

0 = Pixel is off

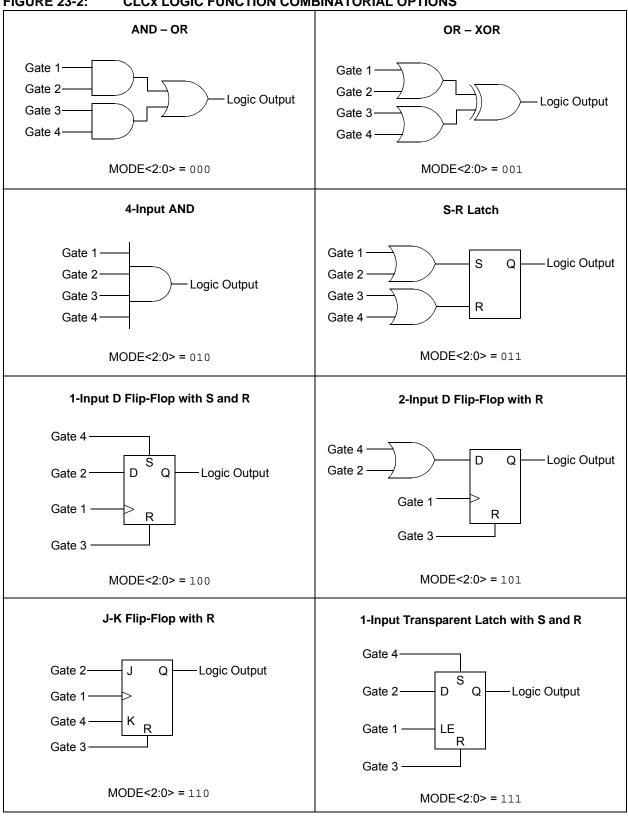

**FIGURE 23-2: CLCx LOGIC FUNCTION COMBINATORIAL OPTIONS**

### REGISTER 24-4: RTCCON2H: RTCC CONTROL REGISTER 2 (HIGH)<sup>(1)</sup>

| R/W-0     | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|

| DIV<15:8> |       |       |       |       |       |       |       |  |

| bit 15    |       |       |       |       |       |       |       |  |

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | DIV   | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 DIV<15:0>: Clock Divide bits

Sets the period of the clock divider counter; value should cause a nominal 1/2 second underflow.

**Note 1:** A write to this register is only allowed when WRLOCK = 1.

### REGISTER 24-5: RTCCON3L: RTCC CONTROL REGISTER 3 (LOW)<sup>(1)</sup>

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSAMP7 | PWCSAMP6 | PWCSAMP5 | PWCSAMP4 | PWCSAMP3 | PWCSAMP2 | PWCSAMP1 | PWCSAMP0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **PWCSAMP<7:0>:** Power Control Sample Time Window bits

11111111 = Sample input is always allowed (not gated)

11111110 = Sample Time Window is 254 TPWC

• • •

00000010 = Sample Time Window is 2 TPWC

00000001 = Sample Time Window is 1 TPWC

00000000 = Sample input is always gated

bit 7-0 **PWCSTAB<7:0>:** Power Control Stability Time bits

11111111 = Stability Time Window is 255 TPWC

11111110 = Stability Time Window is 254 TPWC

• • •

00000010 = Stability Time Window is 2 TPWC

00000001 = Stability Time Window is 1 TPWC

00000000 = No Stability Time Window

Note 1: The Sample Window always starts when the Stability Window timer expires, except when its initial value is 00h.

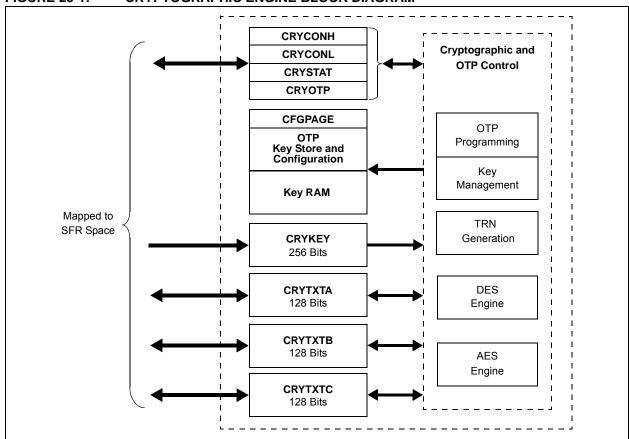

### 25.0 CRYPTOGRAPHIC ENGINE

Note:

This data sheet summarizes the features of the PIC24FJ256GA412/GB412 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Cryptographic Engine" (DS70005133) which is available from the Microchip web site (www.microchip.com).

The Cryptographic Engine provides a new set of data security options. Using its own free-standing state machines, the engine can independently perform NIS standard encryption and decryption of data independently of the CPU. This eliminates the concerns of excessive CPU or program memory overhead that encryption and decryption would otherwise require, while enhancing the application's security.

The primary features of the Cryptographic Engine are:

- Memory-Mapped, 128-Bit and 256-Bit Memory Spaces for Encryption/Decryption Data

- Multiple Options for Key Storage, Selection and Management

- · Support for Internal Context Saving

- · Session Key Encryption and Loading

- · Half-Duplex Operation

- DES and Triple DES (3DES) Encryption and Decryption (64-bit block size):

- Supports 64-bit keys and 2-key or 3-key Triple DES

- AES Encryption and Decryption (128-bit block size):

- Supports key sizes of 128, 192 or 256 bits

- Supports ECB, CBC, CFB, OFB and CTR Modes for Both DES and AES Standards

- · Programmatically Secure Key Storage:

- 512-byte OTP array for key storage, not readable from other memory spaces

- 32-bit Configuration Page

- Independent, 512-byte Key RAM for volatile key storage

- Simple in-module programming interface

- Supports Key Encryption Key (KEK)

- Support for True Random Number Generation (TRNG) and Pseudorandom Number Generation (PRNG), NIST SP800-90 Compliant

- Hardware Anti-Tamper Feature for Additional Data Security

A simplified block diagram of the Cryptographic Engine is shown in Figure 25-1.

#### FIGURE 25-1: CRYPTOGRAPHIC ENGINE BLOCK DIAGRAM

# 25.11 Programming CFGPAGE (Page 0) Configuration Bits

- If not already set, set the CRYON bit. Set KEYPG<3:0> to '0000'.

- Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- 3. Write the data to be programmed into the Configuration Page into CRYTXTC<31:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- 4. Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- Once all programming has completed, set the CRYREAD bit to reload the values from the on-chip storage. A read operation must be performed to complete programming.

Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status by performing a read operation on the array.

Note: If the device enters Sleep mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

### 25.12 Programming Keys

- 1. If not already set, set the CRYON bit.

- Configure KEYPG<3:0> to the page you want to program.

- Select the key storage destination using the KEYPSEL bit (CRYOTP<8>).

- 4. Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- 5. Write the data to be programmed into the Configuration Page into CRYTXTC<63:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 7. Repeat Steps 2 through 5 for each OTP array page to be programmed.

- Once all programming has completed, set the CRYREAD bit to reload the values from the on-chip storage. A read operation must be performed to complete programming.

Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 10. For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status by performing a read operation on the array.

Note: If the device enters Sleep mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

#### REGISTER 28-1: DACxCON: DACx CONTROL REGISTER (CONTINUED)

```

bit 6-2

DACTSEL<4:0>: DAC Trigger Source Select bits

= Unimplemented

. . .

10010

10001 = External Interrupt 1 (INT1)

10000 = SCCP7

01111 = SCCP6

01110 = SCCP5

01101 = SCCP4

01100 = SCCP3

01011 = SCCP2

01010 = MCCP1

01001 = Unimplemented

01000 = Timer5 match

00111 = Timer4 match

00110 = Timer3 match

00101 = Timer2 match

00100 = Timer1 match

00011 = A/D conversion done

00010 = Comparator 3 trigger

00001 = Comparator 2 trigger

00000 = Comparator 1 trigger

bit 1-0

DACREF<1:0>: DAC Reference Source Select bits

11 = 2.4V internal band gap (2 * VBG)(1)

10 = AVDD

01 = DVREF+

00 = Reference is not connected (lowest power but no DAC functionality)

```

Note 1: The internal band gap reference is automatically enabled whenever the DAC is enabled.

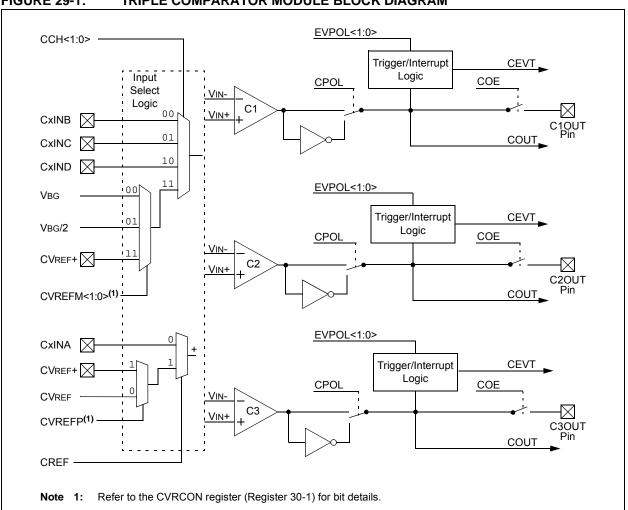

# 29.0 TRIPLE COMPARATOR MODULE

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Scalable Comparator Module" (DS39734). The information in this data sheet supersedes the information in the FRM.

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and VREF+) and a

voltage reference input from one of the internal band gap references or the comparator voltage reference generator (VBG, VBG/2 and CVREF).

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 29-1. Diagrams of the possible individual comparator configurations are shown in Figure 29-2.

Each comparator has its own control register, CMxCON (Register 29-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 29-2).

#### FIGURE 29-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

#### REGISTER 31-2: CTMUCON1H: CTMU CONTROL 1 HIGH REGISTER

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|---------|----------|----------|----------|----------|----------|----------|

| EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT |

| bit 15  |         |          |          |          |          |          | bit 8    |

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0   |

|---------|---------|----------|----------|----------|----------|-----|-------|

| EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _   | _     |

| bit 7   |         |          |          |          |          |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **EDG1MOD:** Edge 1 Edge-Sensitive Select bit

1 = Input is edge-sensitive0 = Input is level-sensitive

bit 14 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 is programmed for a positive edge response 0 = Edge 1 is programmed for a negative edge response

bit 13-10 EDG1SEL<3:0>: Edge 1 Source Select bits

1111 = Comparator 3 output

1110 = Comparator 2 output

1101 = Comparator 1 output

1100 = IC3

1011 = IC2

1010 = IC1

1001 **= CTED8**

1000 **= CTED7**

0111 = CTED6 0110 = CTED5

0110 - OTEDO

0101 = CTED4 0100 = CTED3

0011 **= CTED1**

0010 = CTED2

0001 = OC1

0000 = Timer1 match

bit 9 **EDG2STAT:** Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control current source.

1 = Edge 2 has occurred

0 = Edge 2 has not occurred

bit 8 EDG1STAT: Edge 1 Status bit

Indicates the status of Edge 1 and can be written to control current source.

1 = Edge 1 has occurred

0 = Edge 1 has not occurred

bit 7 **EDG2MOD:** Edge 2 Edge-Sensitive Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 6 EDG2POL: Edge 2 Polarity Select bit

1 = Edge 2 is programmed for a positive edge response

0 = Edge 2 is programmed for a negative edge response

#### **REGISTER 33-12: FBOOT: BOOT MODE CONFIGURATION WORD**

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-1          | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

|              |     | _   | _   | _   | _   |     |     |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1     | R/PO-1 |  |

|-------|-----|-----|-----|-----|-----|------------|--------|--|

| _     | _   | _   | _   | _   | _   | BTMOD<1:0> |        |  |

| bit 7 |     |     |     |     |     |            | bit 0  |  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-2 **Unimplemented:** Read as '1'

bit 1-0 **BTMOD<1:0>:** Boot Mode Select bits

11 = Standard (Single Partition Flash) mode

10 = Dual Partition Flash mode

01 = Protected Dual Partition Flash mode

00 = Reserved, do not use

TABLE 36-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                     | Standard Operating Conditions: 2.0V<br>Operating temperature -40° |                    |     |       | to 3.6V (unless otherwise stated) $C \le TA \le +85^{\circ}C$ for Industrial |  |

|--------------------|--------|---------------------|-------------------------------------------------------------------|--------------------|-----|-------|------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic      | Min                                                               | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                   |  |

|                    | Vol    | Output Low Voltage  |                                                                   |                    |     |       |                                                                              |  |

| DO10               |        | I/O Ports           | _                                                                 | _                  | 0.4 | V     | IOL = 6.6 mA, VDD = 3.6V                                                     |  |

|                    |        |                     | _                                                                 | _                  | 0.4 | V     | IOL = 5.0 mA, VDD = 2V                                                       |  |

| DO16               |        | OSCO/CLKO           | _                                                                 | _                  | 0.4 | V     | IOL = 6.6 mA, VDD = 3.6V                                                     |  |

|                    |        |                     | _                                                                 | _                  | 0.4 | V     | IOL = 5.0 mA, VDD = 2V                                                       |  |

|                    | Vон    | Output High Voltage |                                                                   |                    |     |       |                                                                              |  |

| DO20               |        | I/O Ports           | 3.0                                                               | _                  | _   | V     | IOH = -3.0 mA, VDD = 3.6V                                                    |  |

|                    |        |                     | 2.4                                                               | _                  | _   | V     | IOH = -6.0 mA, VDD = 3.6V                                                    |  |

|                    |        |                     | 1.65                                                              | _                  | _   | V     | IOH = -1.0 mA, VDD = 2V                                                      |  |

|                    |        |                     | 1.4                                                               | _                  | _   | V     | IOH = -3.0 mA, VDD = 2V                                                      |  |

| DO26               |        | OSCO/CLKO           | 2.4                                                               | _                  | _   | V     | IOH = -6.0 mA, VDD = 3.6V                                                    |  |

|                    |        |                     | 1.4                                                               | _                  | _   | V     | IOH = -1.0 mA, VDD = 2V                                                      |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

TABLE 36-10: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHARACTERISTICS |        | Standard<br>Operatin                 | -     | _                  |     | 2.0V to 3.6V (unless otherwise stated) $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial |                                         |

|--------------------|--------|--------------------------------------|-------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Param<br>No.       | Symbol | Characteristic                       | Min   | Typ <sup>(1)</sup> | Max | Units                                                                                                             | Conditions                              |

|                    |        | Program Flash Memory                 |       |                    |     |                                                                                                                   |                                         |

| D130               | EР     | Cell Endurance                       | 20000 |                    | _   | E/W                                                                                                               | -40°C to +85°C                          |

| D131               | VPR    | VDD for Read                         | VMIN  | _                  | 3.6 | V                                                                                                                 | VміN = Minimum operating voltage        |

| D132B              |        | VDD for Self-Timed Write             | VMIN  | _                  | 3.6 | V                                                                                                                 | VміN = Minimum operating voltage        |

| D133A              | Tıw    | Self-Timed Word Write<br>Cycle Time  | _     | 20                 | _   | μS                                                                                                                |                                         |

|                    |        | Self-Timed Row Write<br>Cycle Time   | _     | 1.5                | _   | ms                                                                                                                |                                         |

| D133B              | TIE    | Self-Timed Page Erase<br>Time        | 20    | _                  | 40  | ms                                                                                                                |                                         |

| D134               | TRETD  | Characteristic Retention             | 20    | _                  | _   | Year                                                                                                              | If no other specifications are violated |

| D135               | IDDP   | Supply Current During<br>Programming | _     | 5                  | _   | mA                                                                                                                |                                         |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

| NOTES: |  |  |  |

|--------|--|--|--|

| VO1E3. |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |