Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                          |

| Number of I/O              | 102                                                                           |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 121-TFBGA                                                                     |

| Supplier Device Package    | 121-TFBGA (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga412-i-bg |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

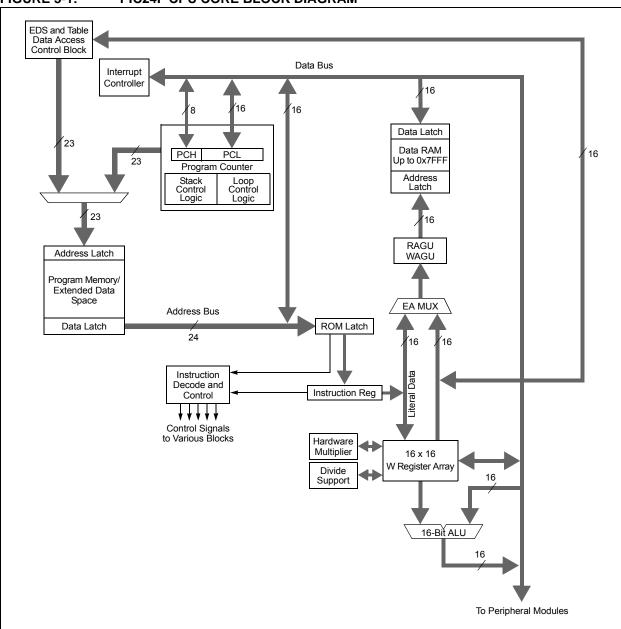

# FIGURE 3-1: PIC24F CPU CORE BLOCK DIAGRAM

| TABLE 3-1: | <b>CPU CORE REGISTERS</b> |

|------------|---------------------------|

|            |                           |

| Register(s) Name | Description                        |

|------------------|------------------------------------|

| W0 through W15   | Working Register Array             |

| PC               | 23-Bit Program Counter             |

| SR               | ALU STATUS Register                |

| SPLIM            | Stack Pointer Limit Value Register |

| TBLPAG           | Table Memory Page Address Register |

| RCOUNT           | REPEAT Loop Counter Register       |

| CORCON           | CPU Control Register               |

| DISICNT          | Disable Interrupt Count Register   |

| DSRPAG           | Data Space Read Page Register      |

| DSWPAG           | Data Space Write Page Register     |

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are described in **Section 6.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address (TBLPAG) register. TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only Table Read operations will execute in the configuration memory space where Device IDs are located. Table Write operations are not allowed.

|       | 9203<br>(A)               | gram Space                                                               |                                     |                                             |                     |

|-------|---------------------------|--------------------------------------------------------------------------|-------------------------------------|---------------------------------------------|---------------------|

|       |                           |                                                                          |                                     |                                             |                     |

| 23 25 | 9<br>0200005<br>0200005 _ |                                                                          | 23                                  |                                             | 8 0                 |

|       | 200000k                   | versen<br>versen<br>versen<br>versen<br>vine address ha<br>wine the care | defined by 1995<br>alions are chose | )<br>)<br>flori is distanti<br>REUPAO conje | ined by the data EA |

# FIGURE 4-11: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

|                   | Vector       | 100 # | IVT     | Interrupt Bit Locations |          |              |  |

|-------------------|--------------|-------|---------|-------------------------|----------|--------------|--|

| Interrupt Source  | Number IRQ # |       | Address | Flag                    | Enable   | Priority     |  |

| UART3 Error       | 89           | 81    | 0000B6h | IFS5<1>                 | IEC5<1>  | IPC20<6:4>   |  |

| UART3 Receiver    | 90           | 82    | 0000B8h | IFS5<2>                 | IEC5<2>  | IPC20<10:8>  |  |

| UART3 Transmitter | 91           | 83    | 0000BAh | IFS5<3>                 | IEC5<3>  | IPC20<14:12> |  |

| UART4 Error       | 95           | 87    | 0000C2h | IFS5<7>                 | IEC5<7>  | IPC21<14:12> |  |

| UART4 Receiver    | 96           | 88    | 0000C4h | IFS5<8>                 | IEC5<8>  | IPC22<2:0>   |  |

| UART4 Transmitter | 97           | 89    | 0000C6h | IFS5<9>                 | IEC5<9>  | IPC22<6:4>   |  |

| UART5 Error       | 121          | 113   | 0000F6h | IFS7<1>                 | IEC7<1>  | IPC28<6:4>   |  |

| UART5 Receive     | 119          | 111   | 0000F2h | IFS6<15>                | IEC6<15> | IPC27<14:12> |  |

| UART5 Transmit    | 120          | 112   | 0000F4h | IFS7<0>                 | IEC7<0>  | IPC28<2:0>   |  |

| UART6 Error       | 124          | 116   | 0000FCh | IFS7<4>                 | IEC7<4>  | IPC29<2:0>   |  |

| UART6 Receive     | 122          | 114   | 0000F8h | IFS7<2>                 | IEC7<2>  | IPC28<10:8>  |  |

| UART6 Transmit    | 123          | 113   | 0000FAh | IFS7<3>                 | IEC7<3>  | IPC28<14:12> |  |

| USB               | 94           | 86    | 0000C0h | IFS5<6>                 | IEC5<6>  | IPC21<10:8>  |  |

## REGISTER 8-9: IFS3: INTERRUPT FLAG STATUS REGISTER 3 (CONTINUED)

- bit 2 MI2C2IF: Master I2C2 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 SI2C2IF: Slave I2C2 Event Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 CCT6IF: SCCP6 Timer Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER         | 8-26: IPC4:                                 |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|------------------|-----------------|----------|--|--|--|

| U-0              | R/W-1                                       | R/W-0                                                                                                   | R/W-0                         | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |

| _                | CNIP2                                       | CNIP1                                                                                                   | CNIP0                         | —                 | CMIP2            | CMIP1           | CMIP0    |  |  |  |

| bit 15           |                                             |                                                                                                         |                               |                   |                  |                 | bit      |  |  |  |

| U-0              | R/W-1                                       | R/W-0                                                                                                   | R/W-0                         | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |

| 0-0              | MI2C1IP2                                    | MI2C1IP1                                                                                                | MI2C1IP0                      | 0-0               | SI2C1IP2         | SI2C1IP1        | SI2C1IP0 |  |  |  |

|                  | IVII2CTIP2                                  | WIZCTFT                                                                                                 | IVIIZG HFU                    |                   | 3120 TIF2        | SIZCTIFT        | 1        |  |  |  |

| bit 7            |                                             |                                                                                                         |                               |                   |                  |                 | bit      |  |  |  |

| Legend:          |                                             |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

| R = Readab       | le bit                                      | W = Writable I                                                                                          | oit                           | U = Unimpler      | mented bit, read | d as '0'        |          |  |  |  |

| -n = Value a     | t POR                                       | '1' = Bit is set                                                                                        |                               | '0' = Bit is cle  | ared             | x = Bit is unkn | iown     |  |  |  |

|                  |                                             |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

| bit 15           | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |

| bit 14-12        | CNIP<2:0>:                                  | nput Change N                                                                                           | otification Inte              | rrupt Priority bi | ts               |                 |          |  |  |  |

|                  | 111 = Interru                               | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1          |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  |                                             | pt source is dis                                                                                        | abled                         |                   |                  |                 |          |  |  |  |

| bit 11           | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |

| bit 10-8         | CMIP<2:0>: (                                | Comparator Inte                                                                                         | errupt Priority I             | oits              |                  |                 |          |  |  |  |

|                  | 111 = Interru                               | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  | •                                           |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1          |                                                                                                         |                               |                   |                  |                 |          |  |  |  |

|                  | 000 = Interru                               | pt source is dis                                                                                        | abled                         |                   |                  |                 |          |  |  |  |

| bit 7            | Unimplemen                                  | ted: Read as 'o                                                                                         | )'                            |                   |                  |                 |          |  |  |  |

| bit 6-4          | MI2C1IP<2:0                                 | >: Master I2C1                                                                                          | Event Interrup                | ot Priority bits  |                  |                 |          |  |  |  |

|                  | 111 = Interru                               | at in Dainait 7 (                                                                                       |                               |                   |                  |                 |          |  |  |  |

|                  |                                             | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  | •                                           | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  | •                                           | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  | •<br>•<br>001 = Interru                     | pt is Priority 7 (                                                                                      | highest priority              | / interrupt)      |                  |                 |          |  |  |  |

|                  |                                             |                                                                                                         |                               | / interrupt)      |                  |                 |          |  |  |  |

| bit 3            | 000 = Interru                               | pt is Priority 1                                                                                        | abled                         | / interrupt)      |                  |                 |          |  |  |  |

|                  | 000 = Interru<br>Unimplemen                 | pt is Priority 1<br>pt source is dis                                                                    | abled                         |                   |                  |                 |          |  |  |  |

| bit 3<br>bit 2-0 | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0                                          | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br>t <b>ed:</b> Read as '0<br>>: Slave I2C1 E                      | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br>t <b>ed:</b> Read as '0<br>>: Slave I2C1 E                      | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>SI2C1IP<2:0: | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '0<br>>: Slave I2C1 E<br>pt is Priority 7 ( | abled<br>,'<br>vent Interrupt | Priority bits     |                  |                 |          |  |  |  |

# REGISTER 8-26: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | R/W-1                                                               | R/W-0                                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|--------------|---------------------------------------------------------------------|------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| _            | CCP4IP2                                                             | CCP4IP1                                                    | CCP4IP0          | _                | CCP3IP2          | CCP3IP1         | CCP3IP0 |  |  |  |  |

| bit 15       |                                                                     |                                                            |                  |                  |                  |                 | bit 8   |  |  |  |  |

|              |                                                                     |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| U-0          | R/W-1                                                               | R/W-0                                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

| —            | SPI4TXIP2                                                           | SPI4TXIP1                                                  | SPI4TXIP0        | —                | SPI4IP2          | SPI4IP1         | SPI4IP0 |  |  |  |  |

| bit 7        |                                                                     |                                                            |                  |                  |                  |                 | bit 0   |  |  |  |  |

| Legend:      |                                                                     |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| R = Readab   | ole bit                                                             | W = Writable                                               | bit              | U = Unimplei     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value a | at POR                                                              | '1' = Bit is set                                           |                  | '0' = Bit is cle | eared            | x = Bit is unkn | iown    |  |  |  |  |

|              |                                                                     |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| bit 15       | Unimplemen                                                          | ted: Read as '                                             | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 14-12    |                                                                     | <ul> <li>SCCP4 Capt</li> </ul>                             | •                | •                | ty bits          |                 |         |  |  |  |  |

|              | 111 = Interru                                                       | pt is Priority 7 (                                         | highest priority | interrupt)       |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                   | •                                                          |                  |                  |                  |                 |         |  |  |  |  |

|              | 001 = Interru<br>000 = Interru                                      | pt is Priority 1<br>pt source is dis                       | abled            |                  |                  |                 |         |  |  |  |  |

| bit 11       | Unimplemen                                                          | ted: Read as '                                             | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 10-8     | CCP3IP<2:0>                                                         | CCP3IP<2:0>: SCCP3 Capture/Compare Interrupt Priority bits |                  |                  |                  |                 |         |  |  |  |  |

|              | 111 = Interru                                                       | pt is Priority 7 (                                         | highest priority | interrupt)       |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| bit 7        |                                                                     | ted: Read as '                                             |                  |                  |                  |                 |         |  |  |  |  |

| bit 6-4      | -                                                                   | 0>: SPI4 Trans                                             |                  | riority hits     |                  |                 |         |  |  |  |  |

|              |                                                                     | pt is Priority 7 (                                         |                  | -                |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            | 5                |                  |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | •<br>001 = Interru                                                  | pt is Priority 1<br>pt source is dis                       | abled            |                  |                  |                 |         |  |  |  |  |

| bit 3        |                                                                     | ted: Read as '                                             |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0      |                                                                     | SPI4 General                                               |                  | tv bits          |                  |                 |         |  |  |  |  |

|              |                                                                     | pt is Priority 7 (                                         |                  | -                |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                   |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|              | 001 = Interru                                                       | pt is Priority 1                                           |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                     | pt source is dis                                           | abled            |                  |                  |                 |         |  |  |  |  |

|              |                                                                     |                                                            |                  |                  |                  |                 |         |  |  |  |  |

#### REGISTER 8-45: IPC23: INTERRUPT PRIORITY CONTROL REGISTER 23

| R-0           | r-0                                                                                                                 | R/W-0                    | U-0              | R-0                                                     | R-0                | R-0                | R-0            |

|---------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|---------------------------------------------------------|--------------------|--------------------|----------------|

| CPUIRQ        | —                                                                                                                   | VHOLD                    | _                | ILR3                                                    | ILR2               | ILR1               | ILR0           |

| bit 15        |                                                                                                                     |                          |                  |                                                         |                    |                    | bit 8          |

|               |                                                                                                                     |                          |                  |                                                         |                    |                    |                |

| U-0           | R-0                                                                                                                 | R-0                      | R-0              | R-0                                                     | R-0                | R-0                | R-0            |

|               | VECNUM6                                                                                                             | VECNUM5                  | VECNUM4          | VECNUM3                                                 | VECNUM2            | VECNUM1            | VECNUM0        |

| bit 7         |                                                                                                                     |                          |                  |                                                         |                    |                    | bit C          |

| Lowende       |                                                                                                                     |                          | h :4             |                                                         |                    |                    |                |

| Legend:       | - h:t                                                                                                               | r = Reserved             |                  |                                                         | a anta d hit was a |                    |                |

| R = Readabl   |                                                                                                                     | W = Writable             | DIt              | •                                                       | nented bit, read   |                    |                |

| -n = Value at | POR                                                                                                                 | '1' = Bit is set         |                  | '0' = Bit is clea                                       | ared               | x = Bit is unkr    | iown           |

| bit 15        |                                                                                                                     |                          | from Interrupt ( |                                                         | hit                |                    |                |

| DIL 15        |                                                                                                                     |                          | •                | Controller CPU<br>has not yet bee                       |                    | ed by the CPU      | · this hannens |

|               |                                                                                                                     | • •                      |                  | e interrupt prio                                        | •                  |                    |                |

|               |                                                                                                                     | upt request is u         | Ų                |                                                         | 5                  |                    |                |

| bit 14        | Reserved: Ma                                                                                                        | aintain as '0'           |                  |                                                         |                    |                    |                |

| bit 13        | VHOLD: Vect                                                                                                         | or Number Cap            | oture Configura  | ation bit                                               |                    |                    |                |

|               | 0 = VECNUM                                                                                                          | 1<6:0> bits con          | tain the value o | of the highest p<br>of the last Ackno<br>be CBU, even i | owledged interr    | upt (i.e., the las |                |

| bit 12        | has occurred with higher priority than the CPU, even if other interrupts are pending)<br>Unimplemented: Read as '0' |                          |                  |                                                         |                    |                    |                |

| bit 11-8      | -                                                                                                                   | w CPU Interru            |                  | l bits                                                  |                    |                    |                |

|               |                                                                                                                     | Interrupt Priorit        | •                |                                                         |                    |                    |                |

|               | •                                                                                                                   | ·                        | -                |                                                         |                    |                    |                |

|               | •                                                                                                                   |                          |                  |                                                         |                    |                    |                |

|               | •<br>0001 = CPU                                                                                                     | Interrupt Priorit        | v Level is 1     |                                                         |                    |                    |                |

|               |                                                                                                                     | Interrupt Priorit        |                  |                                                         |                    |                    |                |

| bit 7         | Unimplement                                                                                                         | ted: Read as '           | )'               |                                                         |                    |                    |                |

| bit 6-0       | VECNUM<6:0                                                                                                          | <b>)&gt;:</b> Vector Num | ber of Pending   | g Interrupt or La                                       | ast Acknowledg     | ged Interrupt bi   | ts             |

|               | When VHOLD                                                                                                          |                          |                  |                                                         |                    |                    |                |

|               |                                                                                                                     |                          | (from 0 to 118)  | of the last inte                                        | rrupt to occur.    |                    |                |

|               | When VHOLD                                                                                                          |                          | (from 0 to 119)  | of the interrup                                         | t request curro    | ntly being bong    | llod           |

|               |                                                                                                                     |                          |                  | or the interrup                                         | i request curre    |                    | 11EU.          |

## REGISTER 8-52: INTTREG: INTERRUPT CONTROLLER TEST REGISTER

| R/W-0        | U-0                 | U-0                                                                                                                                                                                                | R/W-0            | R/W-0                                 | U-0             | U-0                  | U-0       |  |  |

|--------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|-----------------|----------------------|-----------|--|--|

| DSEN         | —                   | —                                                                                                                                                                                                  | RTCCMD           | KEYRAMEN                              | —               | _                    | _         |  |  |

| bit 15       |                     |                                                                                                                                                                                                    |                  |                                       |                 |                      | bit 8     |  |  |

|              |                     |                                                                                                                                                                                                    |                  |                                       | <b>D</b> # 44 0 |                      |           |  |  |

| U-0          | U-0                 | U-0                                                                                                                                                                                                | U-0              | U-0                                   | R/W-0           | R/W-0                | R/C-0, HS |  |  |

|              | —                   | —                                                                                                                                                                                                  |                  | —                                     | WAKEDIS         | DSBOR <sup>(2)</sup> | RELEASE   |  |  |

| bit 7        |                     |                                                                                                                                                                                                    |                  |                                       |                 |                      | bit (     |  |  |

| Legend:      |                     | C = Clearable                                                                                                                                                                                      | bit              | HS = Hardwar                          | e Settable bit  |                      |           |  |  |

| R = Readab   | le bit              | W = Writable                                                                                                                                                                                       | bit              | U = Unimplem                          | ented bit, read | as '0'               |           |  |  |

| -n = Value a | t POR               | '1' = Bit is set                                                                                                                                                                                   |                  | '0' = Bit is clea                     | red             | x = Bit is unkr      | nown      |  |  |

| bit 14-13    | 0 = Enters no       | rmal Sleep on                                                                                                                                                                                      | execution of PI  |                                       |                 |                      |           |  |  |

|              |                     |                                                                                                                                                                                                    |                  |                                       |                 |                      |           |  |  |

| bit 14-13    | -                   | ted: Read as '                                                                                                                                                                                     |                  |                                       |                 |                      |           |  |  |

| bit 12       |                     | CC Module Di                                                                                                                                                                                       | sable bit        |                                       |                 |                      |           |  |  |

|              | 1 = Module is       |                                                                                                                                                                                                    | sources are e    | nahled                                |                 |                      |           |  |  |

| bit 11       | •                   |                                                                                                                                                                                                    |                  | AM Deep Sleep                         | Enable bit      |                      |           |  |  |

|              | 1 = Power is r      | maintained to k                                                                                                                                                                                    | Key RAM during   | g Deep Sleep al<br>Ind VBAT modes     | nd VBAT modes   | i                    |           |  |  |

| bit 10-3     |                     | ted: Read as '                                                                                                                                                                                     |                  |                                       |                 |                      |           |  |  |

| bit 2        | WAKEDIS: EX         | kternal Wake-u                                                                                                                                                                                     | ip Source Disa   | ble bit                               |                 |                      |           |  |  |

|              |                     |                                                                                                                                                                                                    |                  | nd ignored durin<br>Id can be used t  | <b>v</b> , ,    |                      | an        |  |  |

| bit 1        |                     | p Sleep BOR E                                                                                                                                                                                      |                  |                                       |                 |                      | γ         |  |  |

|              |                     |                                                                                                                                                                                                    |                  | ent was detecte                       | d during Deep S | Sleep                |           |  |  |

|              |                     | <ul> <li>1 = The DSBOR was active and a BOR event was detected during Deep Sleep</li> <li>0 = The DSBOR was not active, or was active, but did not detect a BOR event during Deep Sleep</li> </ul> |                  |                                       |                 |                      |           |  |  |

| bit 0        | RELEASE: 1/0        | O Pin State Re                                                                                                                                                                                     | lease bit        |                                       |                 |                      |           |  |  |

|              | 0 = Releases        |                                                                                                                                                                                                    | their state prev | is maintain their<br>ious to Deep Sle |                 |                      |           |  |  |

|              | Il register bits ar |                                                                                                                                                                                                    |                  | POR event outsig                      | •               | •                    |           |  |  |

# REGISTER 10-1: DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

2: Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms the POR.

# 11.4 Interrupt-on-Change (IOC)

The interrupt-on-change function of the I/O ports allows the PIC24FJ256GA412/GB412 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on any of the input port pins. This feature is capable of detecting input Change-of-States, even in Sleep mode when the clocks are disabled.

Interrupt-on-change functionality is globally enabled by setting the IOCON bit in the PADCON register (Register 11-1). Functionality is then enabled for a particular pin by setting the IOCPx and/or IOCNx register bit for that pin. Setting a value of '1' in the IOCPx register enables interrupts for low-to-high transitions, while setting a value of '1' in the IOCNx register enables interrupts for high-to-low transitions. Setting a value of '1' in both register bits will enable interrupts for either case (e.g., a pulse on the pin will generate two interrupts).

When an interrupt request is generated for a pin, the corresponding status flag bit in the IOCFx register will be set, indicating that a Change-of-State occurred on that pin. The IOCFx register bit will remain set until cleared by writing a zero to it. When any IOCFx flag bit in a given port is set, the corresponding IOCPxF bit in the IOCSTAT register (Register 11-2) will also be set. This flag indicates that a change was detected on one of the bits on the given port. The IOCPxF flag will be cleared when all IOCFx<br/>(1000) bits are cleared.

Multiple individual status flags can be cleared by writing a zero to one or more bits using a Read-Modify-Write operation. If another edge is detected on a pin whose status bit is being cleared during the Read-Modify-Write sequence, the associated change flag will still be set at the end of the Read-Modify-Write sequence. The user should use the instruction sequence (or equivalent) shown in Example 11-1 to clear the Interrupt-on-Change Status registers.

At the end of this sequence, the W0 register will contain a zero for each bit for which the port pin had a change detected. In this way, any indication of a pin changing will not be lost.

Due to the asynchronous and real-time nature of the interrupt-on-change, the value read on the port pins may not indicate the state of the port when the change was detected, as a second change can occur during the interval between clearing the flag and reading the port. It is up to the user code to handle this case if it is a possibility in their application. To keep this interval to a minimum, it is recommended that any code modifying the IOCFx registers be run either in the interrupt handler or with interrupts disabled.

#### 11.4.1 PULL-UPS AND PULL-DOWNS

Each IOC pin has both a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source connected to the pin, while the pull-downs act as a current sink connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected.

The pull-ups and pull-downs are separately enabled using the IOCPUx registers (for pull-ups) and the IOCPDx registers (for pull-downs). Each IOC pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

Note: Pull-ups and pull-downs on pins should always be disabled whenever the pin is configured as a digital output.

## EXAMPLE 11-1: IOC STATUS READ/CLEAR IN ASSEMBLY

| MOV 0xFFFF,  | ; Initial mask value 0xFFFF -> W0      |

|--------------|----------------------------------------|

| XOR IOCFx, W | ; WO has '1' for each bit set in IOCFx |

| AND IOCFx    | ; IOCFx & WO ->IOCFx                   |

#### EXAMPLE 11-2: PORT READ/WRITE IN ASSEMBLY

| ĺ | MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|---|------|------------|-----------------------------------|

|   | MOV  | W0, TRISB  | ; and PORTB<7:0> as outputs       |

|   | NOP  |            | ; Delay 1 cycle                   |

|   | BTSS | PORTB, #13 | ; Next Instruction                |

#### EXAMPLE 11-3: PORT READ/WRITE IN 'C'

| TRISB = 0xFF00;                    | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------------------------------------|--------------------------------------------------------------|

| Nop();                             | // Delay 1 cycle                                             |

| <pre>If (PORTBbits.RB13){ };</pre> | // Next Instruction                                          |

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 1111

- 1111x = Reserved

- 11101 = Reserved 11100 = CTMU<sup>(1)</sup>

- $11001 = A/D^{(1)}$

- 11010 = Comparator 3<sup>(1)</sup>

- $11001 = \text{Comparator } 2^{(1)}$

- 11000 = Comparator 1<sup>(1)</sup>

- 10111 = SCCP5 capture/compare

- 10110 = SCCP4 capture/compare

- 10101 = SCCP3 capture/compare

- 10100 = SCCP2 capture/compare

- 10011 = MCCP1 capture/compare

- 10010 = Input Capture 3<sup>(2)</sup>

- 10001 =Input Capture  $2^{(2)}_{(2)}$

- 10000 = Input Capture 1<sup>(2)</sup>

- 01111 = SCCP7 capture/compare

- 01110 = SCCP6 capture/compare

- 01101 = Timer3

- 01100 = Timer2

- 01011 = Timer1

- 01010 = SCCP7 sync/trigger

- 01001 = SCCP6 sync/trigger

- 01000 = SCCP5 sync/trigger

- 00111 = SCCP4 sync/trigger

- 00110 = SCCP3 sync/trigger 00101 = SCCP2 sync/trigger

- 10101 = SCCP2 sync/trigger

- 00100 = MCCP1 sync/trigger 00011 = Output Compare 3

- 00011 = Output Compare 3

- 00001 = Output Compare 1

- 00000 = Not synchronized to any other module

- Note 1: Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an ICx module as its own trigger source by selecting this mode.

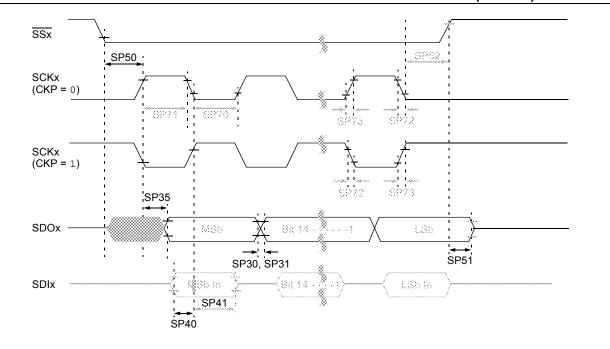

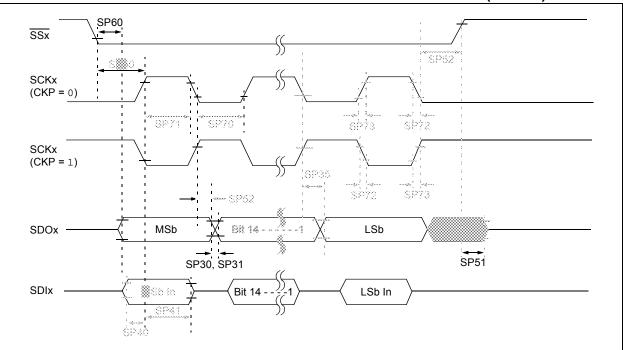

## REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 9         | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <u>Master Mode:</u><br>1 = Input data is sampled at the end of data output time                                                                                                                                                     |

|               | 0 = Input data is sampled at the middle of data output time                                                                                                                                                                         |

|               | Slave Mode:                                                                                                                                                                                                                         |

|               | Input data is always sampled at the middle of data output time, regardless of the SMP setting.                                                                                                                                      |

| bit 8         | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                                      |

|               | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                          |

| bit 7         | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                           |

|               | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select input<br>0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

| bit 6         | CKP: Clock Polarity Select bit                                                                                                                                                                                                      |

|               | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                            |

| bit 5         | MSTEN: Master Mode Enable bit                                                                                                                                                                                                       |

|               | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                   |

| bit 4         | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                                 |

|               | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                    |

| bit 3         | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                                |

|               | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                    |

| bit 2         | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                      |

|               | 1 = REFO is used by the BRG<br>0 = Fosc/2 is used by the BRG                                                                                                                                                                        |

| bit 1         | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                             |

|               | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                                  |

| bit 0         | ENHBUF: Enhanced Buffer Enable bit                                                                                                                                                                                                  |

|               | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                               |

| Note 1:<br>2: | When AUDEN (SPIxCON1H<15>) = 1, this module functions as if CKE = 0, regardless of its actual value.<br>When $FRMEN = 1$ SSEN is not used                                                                                           |

- EN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows FRMSYPW.

## REGISTER 27-2: AD1CON2: A/D CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit <sup>(1)</sup>                                         |

|-------|------------------------------------------------------------------------------------------|

|       | 1 = Starts buffer filling at ADC1BUF0 on first interrupt and ADC1BUF13 on next interrupt |

|       | 0 = Always starts filling buffer at ADC1BUF0                                             |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                             |

|       | 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample  |

|       | 0 = Always uses channel input selects for Sample A                                       |

**Note 1:** These bits are only applicable when the buffer is used in FIFO mode (BUFREGEN = 0). In addition, BUFS is only used when BUFM = 1.

#### REGISTER 27-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0  | R-0    | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|--------|-------|-------|-------|-------|-------|

| ADRC   | EXTSAM | PUMPEN | SAMC4 | SAMC3 | SAMC2 | SAMC1 | SAMC0 |

| bit 15 | •      | •      |       |       |       |       | bit 8 |

|        |        |        |       |       |       |       |       |

| R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| ADCS7  | ADCS6  | ADCS5  | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0 |

| bit 7  | •      |        |       | •     |       |       | bit 0 |

|        |        |        |       |       |       |       | DILU  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 15   | ADRC: A/D Conversion Clock Source bit<br>1 = RC clock                                                         |

|----------|---------------------------------------------------------------------------------------------------------------|

|          | 0 = Clock derived from system clock                                                                           |

| bit 14   | EXTSAM: Extended Sampling Time bit                                                                            |

|          | 1 = A/D is still sampling after SAMP = 0<br>0 = A/D is finished sampling                                      |

| bit 13   | PUMPEN: Charge Pump Enable bit                                                                                |

|          | <ol> <li>1 = Charge pump for switches is enabled</li> <li>0 = Charge pump for switches is disabled</li> </ol> |

| bit 12-8 | SAMC<4:0>: Auto-Sample Time Select bits                                                                       |

|          | 11111 <b>= 31 T</b> AD                                                                                        |

|          | •••                                                                                                           |

|          | 00001 = 1 TAD                                                                                                 |

|          | 00000 = 0 TAD                                                                                                 |

| bit 7-0  | ADCS<7:0>: A/D Conversion Clock Select bits                                                                   |

|          | 11111111 = 256 • TCY = TAD                                                                                    |

|          | •••                                                                                                           |

|          | 00000001 = 2. TCY = TAD                                                                                       |

|          | 00000000 = TCY = TAD                                                                                          |

| R/W-0         | R/W-0                                                                                              | R/W-0                                                     | R/W-0  | R/W-0                            | R/W-0  | R/W-0              | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------|----------------------------------|--------|--------------------|--------|--|--|--|--|

| CH0NB2        | CH0NB1                                                                                             | CH0NB0                                                    | CH0SB4 | CH0SB3                           | CH0SB2 | CH0SB1             | CH0SB0 |  |  |  |  |

| bit 15        |                                                                                                    |                                                           |        | ·                                |        | •                  | bit 8  |  |  |  |  |

|               |                                                                                                    |                                                           |        |                                  |        |                    |        |  |  |  |  |

| R/W-0         | R/W-0                                                                                              | R/W-0                                                     | R/W-0  | R/W-0                            | R/W-0  | R/W-0              | R/W-0  |  |  |  |  |

| CH0NA2        | CH0NA1                                                                                             | CH0NA0                                                    | CH0SA4 | CH0SA3                           | CH0SA2 | CH0SA1             | CH0SA0 |  |  |  |  |

| bit 7         |                                                                                                    |                                                           |        |                                  |        |                    | bit 0  |  |  |  |  |

|               |                                                                                                    |                                                           |        |                                  |        |                    |        |  |  |  |  |

| Legend:       |                                                                                                    |                                                           |        |                                  |        |                    |        |  |  |  |  |

| R = Readable  | e bit                                                                                              | W = Writable bit                                          |        | U = Unimplemented bit, read as ' |        | l as '0'           |        |  |  |  |  |

| -n = Value at | POR                                                                                                | '1' = Bit is set                                          |        | '0' = Bit is cleared             |        | x = Bit is unknown |        |  |  |  |  |

| bit 15-13     | 1xx = Unimpl<br>011 = Unimpl<br>010 = AN1<br>001 = Unimpl<br>000 = VREF-//                         | emented<br>emented<br>emented<br>AVss                     | -      | ive Input Select                 |        |                    |        |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: Sample B Channel 0 Positive Input Select bits<br>See Table 27-2 for available options. |                                                           |        |                                  |        |                    |        |  |  |  |  |

| bit 7-5       | CH0NA<2:0>: Sample A Channel 0 Negative Input Select bits<br>Same definitions as for CHONB<2:0>.   |                                                           |        |                                  |        |                    |        |  |  |  |  |

| bit 4-0       | CH0SA<4:0>                                                                                         | CH0SA<4:0>: Sample A Channel 0 Positive Input Select bits |        |                                  |        |                    |        |  |  |  |  |

|               |                                                                                                    |                                                           |        |                                  |        |                    |        |  |  |  |  |

#### REGISTER 27-6: AD1CHS: A/D SAMPLE SELECT REGISTER

Same definitions as for CHOSB<4:0>.

| TABI F 27-2. | POSITIVE CHANNEL SELECT OPTIONS (CHOSA<4:0> OR CHOSB<4:0>) |

|--------------|------------------------------------------------------------|

|              |                                                            |

| CH0SA<4:0> or<br>CH0SB<4:0> | Analog Channel                                 | CH0SA<4:0> or<br>CH0SB<4:0> | Analog Channel |  |

|-----------------------------|------------------------------------------------|-----------------------------|----------------|--|

| 11111                       | VBAT/2 <sup>(1)</sup>                          | 01111                       | AN15           |  |

| 11110                       | AVDD <sup>(1)</sup>                            | 01110                       | AN14           |  |

| 11101                       | AVss <sup>(1)</sup>                            | 01101                       | AN13           |  |

| 11100                       | VBG <sup>(1)</sup>                             | 01100                       | AN12           |  |

| 11011                       | Reserved                                       | 01011                       | AN11           |  |

| 11010                       | Reserved                                       | 01010                       | AN10           |  |

| 11001                       | CTMU                                           | CTMU 01001                  |                |  |

| 11000                       | 0 CTMU Temperature Sensor <sup>(2)</sup> 01000 |                             | AN8            |  |

| 10111                       | AN23 <sup>(3)</sup>                            | 00111                       | AN7            |  |

| 10110                       | AN22 <sup>(3)</sup>                            | 00110                       | AN6            |  |

| 10101                       | AN21 <sup>(3)</sup>                            | 00101                       | AN5            |  |

| 10100                       | AN20 <sup>(3)</sup>                            | 00100                       | AN4            |  |

| 10011                       | AN19 <sup>(3)</sup>                            | 00011                       | AN3            |  |

| 10010                       | AN18 <sup>(3)</sup>                            | 00010                       | AN2            |  |

| 10001                       | AN17 <sup>(3)</sup>                            | 00001                       | AN1            |  |

| 10000                       | AN16 <sup>(3)</sup>                            | 00000                       | AN0            |  |

**Note 1:** These input channels do not have corresponding memory-mapped result buffers.

2: Temperature sensor does not require AD1CTMENL<13> to be set.

**3:** These channels are not implemented in 64-pin devices.

| U-0          | R/W-0                                                                                                                             | R/W-0                                 | R/W-0           | U-0                                | U-0             | R/W-0              | R/W-0   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|------------------------------------|-----------------|--------------------|---------|

|              |                                                                                                                                   | CTMEN<30:28                           | >               |                                    |                 | CTMEN              | <25:24> |

| bit 15       |                                                                                                                                   |                                       |                 |                                    |                 |                    | bit 8   |

|              |                                                                                                                                   |                                       |                 |                                    |                 |                    |         |

| R/W-0        | R/W-0                                                                                                                             | R/W-0                                 | R/W-0           | R/W-0                              | R/W-0           | R/W-0              | R/W-0   |

|              |                                                                                                                                   |                                       | CTMEN           | <23:16> <sup>(1)</sup>             |                 |                    |         |

| bit 7        |                                                                                                                                   |                                       |                 |                                    |                 |                    | bit 0   |

|              |                                                                                                                                   |                                       |                 |                                    |                 |                    |         |

| Legend:      |                                                                                                                                   |                                       |                 |                                    |                 |                    |         |

| R = Readab   | ole bit                                                                                                                           | W = Writable I                        | oit             | U = Unimplemented bit, read as '0' |                 |                    |         |