Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuils                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                          |

| Number of I/O              | 52                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | · ·                                                                           |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 64-QFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb406-i-mr |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | PIC24FJ230GB412 FAIWIL I |                 |                  |     |              |                           |  |

|--------------|--------------------------|-----------------|------------------|-----|--------------|---------------------------|--|

| Din Eurotian | Pin/Pad Number           |                 |                  |     | Innut Duffer | Description               |  |

| Pin Function | 64-Pin<br>TQFP           | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description               |  |

| IOCC1        | _                        | 6               | D1               | I   | ST           | PORTC Interrupt-on-Change |  |

| IOCC2        | _                        | 7               | E4               | I   | ST           |                           |  |

| IOCC3        | _                        | 8               | E2               | I   | ST           |                           |  |

| IOCC4        | _                        | 9               | E!               | I   | ST           |                           |  |

| IOCC12       | 39                       | 63              | F9               | I   | ST           |                           |  |

| IOCC13       | 47                       | 73              | C10              | I   | ST           |                           |  |

| IOCC14       | 48                       | 74              | B11              | I   | ST           |                           |  |

| IOCC15       | 40                       | 64              | F11              | I   | ST           |                           |  |

| IOCD0        | 46                       | 72              | D9               | I   | ST           | PORTD Interrupt-on-Change |  |

| IOCD1        | 49                       | 76              | A11              | I   | ST           | 1                         |  |

| IOCD2        | 50                       | 77              | A10              | I   | ST           | 1                         |  |

| IOCD3        | 51                       | 78              | B9               | I   | ST           |                           |  |

| IOCD4        | 52                       | 81              | C8               | I   | ST           |                           |  |

| IOCD5        | 53                       | 82              | B8               | I   | ST           |                           |  |

| IOCD6        | 54                       | 83              | D7               | I   | ST           |                           |  |

| IOCD7        | 55                       | 84              | C7               | I   | ST           |                           |  |

| IOCD8        | 42                       | 68              | E9               | I   | ST           |                           |  |

| IOCD9        | 43                       | 69              | E10              | I   | ST           |                           |  |

| IOCD10       | 44                       | 70              | D11              | I   | ST           |                           |  |

| IOCD11       | 45                       | 71              | C11              | I   | ST           |                           |  |

| IOCD12       | _                        | 79              | A9               | I   | ST           |                           |  |

| IOCD13       | _                        | 80              | D8               | I   | ST           |                           |  |

| IOCD14       | _                        | 47              | L9               | I   | ST           |                           |  |

| IOCD15       | -                        | 48              | K9               | I   | ST           | 1                         |  |

| IOCE0        | 60                       | 93              | A4               | I   | ST           | PORTE Interrupt-on-Change |  |

| IOCE1        | 61                       | 94              | B4               | I   | ST           | 1                         |  |

| IOCE2        | 62                       | 98              | B3               | I   | ST           | 1                         |  |

| IOCE3        | 63                       | 99              | A2               | I   | ST           | 1                         |  |

| IOCE4        | 64                       | 100             | A1               | I   | ST           |                           |  |

| IOCE5        | 1                        | 3               | D3               | I   | ST           | ]                         |  |

| IOCE6        | 2                        | 4               | C1               | I   | ST           | 1                         |  |

| IOCE7        | 3                        | 5               | D2               | I   | ST           | 1                         |  |

| IOCE8        | _                        | 18              | G1               | I   | ST           | ]                         |  |

| IOCE9        | _                        | 19              | G2               | I   | ST           | 1                         |  |

#### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend:

TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

|              | Pir            | n/Pad Numl      | per              |     |              |                                                 |

|--------------|----------------|-----------------|------------------|-----|--------------|-------------------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                                     |

| PMRD/PMWR    | 53             | 82              | B8               | I/O | DIG/ST/TTL   | Parallel Master Port Read Strobe/Write Strobe   |

| PMWR/PMENB   | 52             | 81              | C8               | I/O | DIG/ST/TTL   | Parallel Master Port Write Strobe/Enable Strobe |

| PWRGT        | 21             | 32              | K4               | 0   | DIGMV        | Real-Time Clock Power Control Output            |

| PWRLCLK      | 48             | 74              | B11              | I   | STMV         | Real-Time Clock 50/60 Hz Clock Input            |

| RA0          | _              | 17              | G3               | I/O | DIG/ST       | PORTA Digital I/Os                              |

| RA1          | _              | 38              | J6               | I/O | DIG/ST       |                                                 |

| RA2          | _              | 58              | H11              | I/O | DIG/ST/TTL   |                                                 |

| RA3          | _              | 59              | G10              | I/O | DIG/ST/TTL   |                                                 |

| RA4          | _              | 60              | G11              | I/O | DIG/ST       |                                                 |

| RA5          | _              | 61              | G9               | I/O | DIG/ST       |                                                 |

| RA6          | _              | 91              | C5               | I/O | DIG/ST       |                                                 |

| RA7          | —              | 92              | B5               | I/O | DIG/ST       |                                                 |

| RA9          | _              | 28              | L2               | I/O | DIG/ST/TTL   |                                                 |

| RA10         | _              | 29              | K3               | I/O | DIG/ST       |                                                 |

| RA14         | —              | 66              | E11              | I/O | DIG/ST/TTL   |                                                 |

| RA15         | _              | 67              | E8               | I/O | DIG/ST/TTL   |                                                 |

| RB0          | 16             | 25              | K2               | I/O | DIG/ST       | PORTB Digital I/Os                              |

| RB1          | 15             | 24              | K1               | I/O | DIG/ST       |                                                 |

| RB2          | 14             | 23              | J2               | I/O | DIG/ST/TTL   |                                                 |

| RB3          | 13             | 22              | J1               | I/O | DIG/ST/TTL   |                                                 |

| RB4          | 12             | 21              | H2               | I/O | DIG/ST/TTL   |                                                 |

| RB5          | 11             | 20              | H1               | I/O | DIG/ST/TTL   |                                                 |

| RB6          | 17             | 26              | L1               | I/O | DIG/ST       |                                                 |

| RB7          | 18             | 27              | J3               | I/O | DIG/ST/TTL   |                                                 |

| RB8          | 21             | 32              | K4               | I/O | DIG/ST       |                                                 |

| RB9          | 22             | 33              | L4               | I/O | DIG/ST       |                                                 |

| RB10         | 23             | 34              | H5               | I/O | DIG/ST       |                                                 |

| RB11         | 24             | 35              | K5               | I/O | DIG/ST       |                                                 |

| RB12         | 27             | 41              | J7               | I/O | DIG/ST       |                                                 |

| RB13         | 28             | 42              | L7               | I/O | DIG/ST       |                                                 |

| RB14         | 29             | 43              | K7               | I/O | DIG/ST       |                                                 |

| RB15         | 30             | 44              | L8               | I/O | DIG/ST       |                                                 |

| RC1          | _              | 6               | D1               | I/O | DIG/ST       | PORTC Digital I/Os                              |

| RC2          | _              | 7               | E4               | I/O | DIG/ST       |                                                 |

| RC3          | —              | 8               | E2               | I/O | DIG/ST       | ]                                               |

| RC4          | —              | 9               | E!               | I/O | DIG/ST       | 1                                               |

| RC12         | 39             | 63              | F9               | I/O | DIG/ST       | 1                                               |

| RC13         | 47             | 73              | C10              | I   | ST           | 1                                               |

| RC14         | 48             | 74              | B11              | I   | ST           | 1                                               |

| RC15         | 40             | 64              | F11              | I/O | DIG/ST       | 1                                               |

#### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer

ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated transceiver

#### **Pin/Pad Number Pin Function** I/O Input Buffer Description 64-Pin 100-Pin 121-Pin TQFP TQFP TFBGA RD0 46 72 D9 I/O DIG/ST PORTD Digital I/Os DIG/ST RD1 49 76 A11 I/O RD2 I/O DIG/ST 50 77 A10 RD3 51 78 В9 I/O DIG/ST RD4 I/O 52 81 C8 DIG/ST I/O DIG/ST RD5 53 B8 82 RD6 54 83 D7 I/O DIG/ST RD7 55 84 C7 I/O DIG/ST RD8 42 68 E9 I/O DIG/ST RD9 43 69 E10 I/O DIG/ST **RD10** 44 70 D11 I/O DIG/ST **RD11** 45 71 C11 I/O DIG/ST **RD12** 79 A9 I/O DIG/ST **RD13** 80 D8 I/O DIG/ST \_\_\_\_ RD14 DIG/ST 47 L9 I/O RD15 I/O 48 K9 DIG/ST RE0 I/O DIG/ST 60 93 A4 PORTE Digital I/Os RE1 61 94 Β4 I/O DIG/ST RE2 62 98 B3 I/O DIG/ST RE3 63 99 A2 I/O DIG/ST RE4 64 100 A1 I/O DIG/ST RE5 1 3 D3 I/O DIG/ST C1 RE6 2 4 I/O DIG/ST RE7 3 5 D2 I/O DIG/ST RE8 18 G1 I/O DIG/ST \_\_\_\_ RE9 19 G2 I/O DIG/ST REFI1 24 35 K5 ST **Reference Clock Input** T RF0 B6 I/O DIG/ST PORTF Digital I/Os 58 87 RF1 I/O DIG/ST 59 88 A6 RF2 K11 I/O DIG/ST 52 RF3 33 51 K10 I/O DIG/ST/TTL RF4 31 49 L10 I/O DIG/ST RF5 32 50 L11 I/O DIG/ST RF6 I/O DIG/ST \_ \_ RF7 H8 I/O DIG/ST 34 54 RF8 53 J10 I/O DIG/ST **RF12** 40 K6 I/O DIG/ST **RF13** 39 L6 I/O DIG/ST \_\_\_\_

### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

## 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space (DS) during code execution.

### 4.1 **Program Memory Space**

The program address memory space of the PIC24FJ256GA412/GB412 family devices is 4M instructions. The space is addressable by a 24-bit value

derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.4** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

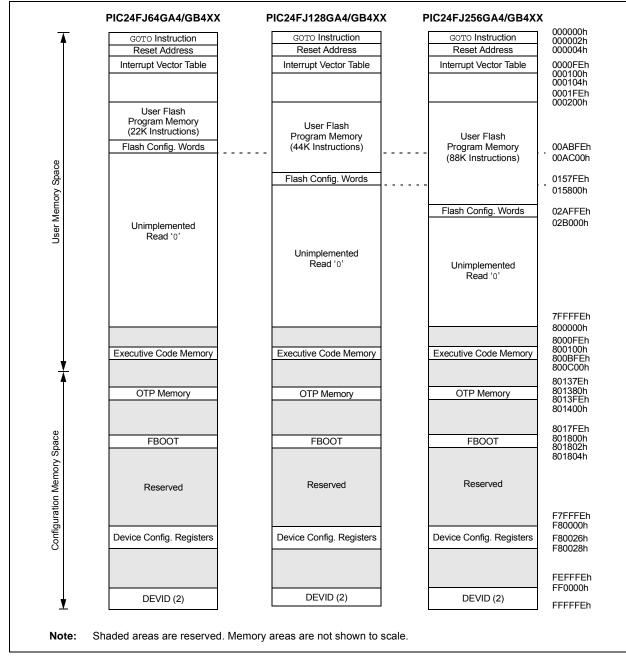

Memory maps for PIC24FJ256GA412/GB412 family devices are shown in Figure 4-1.

| TABLE 4-5: SFR BLOCK 0000 |         |                                         |               |          |                                         |          |         |                    |

|---------------------------|---------|-----------------------------------------|---------------|----------|-----------------------------------------|----------|---------|--------------------|

| Register                  | Address | All Resets                              | Register      | Address  | All Resets                              | Register | Address | All Resets         |

| Core                      |         |                                         | Interrupt Cor | ntroller |                                         | IPC7     | 0B6     | 0100010001000100   |

| WREG0                     | 000     | 000000000000000000000000000000000000000 | INTCON1       | 080      | 000000000000000000000000000000000000000 | IPC8     | 0B8     | 0100010001000100   |

| WREG1                     | 002     | 000000000000000000000000000000000000000 | INTCON2       | 082      | 10000000000000000                       | IPC9     | 0BA     | 0100010001000100   |

| WREG2                     | 004     | 000000000000000000000000000000000000000 | INTCON4       | 086      | 000000000000000000000000000000000000000 | IPC10    | 0BC     | 0100010001000100   |

| WREG3                     | 006     | 000000000000000000000000000000000000000 | IFS0          | 088      | 000000000000000000000000000000000000000 | IPC11    | 0BE     | 0100010001000100   |

| WREG4                     | 008     | 000000000000000000000000000000000000000 | IFS1          | 08A      | 000000000000000000000000000000000000000 | IPC12    | 0C0     | 0100010001000100   |

| WREG5                     | 00A     | 000000000000000000000000000000000000000 | IFS2          | 08C      | 000000000000000000000000000000000000000 | IPC13    | 0C2     | 0100010001000000   |

| WREG6                     | 00C     | 000000000000000000000000000000000000000 | IFS3          | 08E      | 000000000000000000000000000000000000000 | IPC14    | 0C4     | 0100010001000100   |

| WREG7                     | 00E     | 000000000000000000000000000000000000000 | IFS4          | 090      | 000000000000000000000000000000000000000 | IPC15    | 0C6     | 0100010001000100   |

| WREG8                     | 010     | 000000000000000000000000000000000000000 | IFS5          | 092      | 000000000000000000000000000000000000000 | IPC16    | 0C8     | 0100010001000100   |

| WREG9                     | 012     | 000000000000000000000000000000000000000 | IFS6          | 094      | 000000000000000000000000000000000000000 | IPC17    | 0CA     | 0100010000000000   |

| WREG10                    | 014     | 000000000000000000000000000000000000000 | IFS7          | 096      | 000000000000000000000000000000000000000 | IPC18    | 0CC     | 0000000001000100   |

| WREG11                    | 016     | 000000000000000000000000000000000000000 | IEC0          | 098      | 000000000000000000000000000000000000000 | IPC19    | 0CE     | 0000010001000000   |

| WREG12                    | 018     | 000000000000000000000000000000000000000 | IEC1          | 09A      | 000000000000000000000000000000000000000 | IPC20    | 0D0     | 0100010001000000   |

| WREG13                    | 01A     | 000000000000000000000000000000000000000 | IEC2          | 09C      | 000000000000000000000000000000000000000 | IPC21    | 0D2     | 0100010001000100   |

| WREG14                    | 01C     | 000000000000000000000000000000000000000 | IEC3          | 09E      | 000000000000000000000000000000000000000 | IPC22    | 0D4     | 0100010001000100   |

| WREG15                    | 01E     | 000000000000000000000000000000000000000 | IEC4          | 0A0      | 000000000000000000000000000000000000000 | IPC23    | 0D6     | 0100010001000100   |

| SPLIM                     | 020     | xxxxxxxxxxxxxxx0                        | IEC5          | 0A2      | 000000000000000000000000000000000000000 | IPC24    | 0D8     | 0100010001000100   |

| PCL                       | 02E     | 000000000000000000000000000000000000000 | IEC6          | 0A4      | 000000000000000000000000000000000000000 | IPC25    | 0DA     | 0000010001000100   |

| PCH                       | 030     | 000000000000000000000000000000000000000 | IEC7          | 0A6      | 000000000000000000000000000000000000000 | IPC26    | 0DC     | 0000010000000000   |

| DSRPAG                    | 032     | 000000000000000000000000000000000000000 | IPC0          | 0A8      | 0100010001000100                        | IPC27    | 0DE     | 0100010001000000   |

| DSWPAG                    | 034     | 000000000000000000000000000000000000000 | IPC1          | 0AA      | 0100010001000100                        | IPC28    | 0E0     | 0100010001000100   |

| RCOUNT                    | 036     | *****                                   | IPC2          | 0AC      | 0100010001000100                        | IPC29    | 0E2     | 000000001000100    |

| SR                        | 042     | 000000000000000000000000000000000000000 | IPC3          | 0AE      | 0100010001000100                        | INTTREG  | 0E4     | 000000000000000000 |

| CORCON                    | 044     | 000000000000000000000000000000000000000 | IPC4          | 0B0      | 0100010001000100                        |          |         |                    |

| DISICNT                   | 052     | 00xxxxxxxxxxxx                          | IPC5          | 0B2      | 0100010000000100                        |          |         |                    |

| TBLPAG                    | 054     | 000000000000000000000000000000000000000 | IPC6          | 0B4      | 0100010001000100                        |          |         |                    |

TABLE 4-5: SFR BLOCK 000h

Legend: x = unknown or indeterminate value. Reset and address values are in hexadecimal.

#### REGISTER 5-1: DMACON: DMA ENGINE CONTROL REGISTER

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| DMAEN  | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | —   | —   | —   | _   | PRSSEL |

| bit 7 |     |     |     |     |     |     | bit 0  |

### Legend:

| Ecgena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 DMAEN: DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round robin scheme

0 = Fixed priority scheme

| TABLE 8-2: IMPLEMENTED IN            | Vector |       | IVT     | Interrupt Bit Locations |          |              |  |

|--------------------------------------|--------|-------|---------|-------------------------|----------|--------------|--|

| Interrupt Source                     | Number | IRQ # | Address | Flag                    | Enable   | Priority     |  |

| ADC1 Interrupt                       | 21     | 13    | 00002Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>    |  |

| CLC1                                 | 104    | 96    | 0000D4h | IFS6<0>                 | IEC6<0>  | IPC24<2:0>   |  |

| CLC2                                 | 105    | 97    | 0000D6h | IFS6<1>                 | IEC6<1>  | IPC24<6:4>   |  |

| CLC3                                 | 106    | 98    | 0000D8h | IFS6<2>                 | IEC6<2>  | IPC24<10:8>  |  |

| CLC4                                 | 107    | 99    | 0000DAh | IFS6<3>                 | IEC6<3>  | IPC24<14:12> |  |

| Comparator Event                     | 26     | 18    | 000038h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>   |  |

| CRC Generator                        | 75     | 67    | 00009Ah | IFS4<3>                 | IEC4<3>  | IPC16<14:12> |  |

| Crypto Buffer Ready                  | 42     | 34    | 000058h | IFS2<2>                 | IEC2<2>  | IPC8<10:8>   |  |

| Crypto Operation Done                | 63     | 55    | 000082h | IFS3<7>                 | IEC3<7>  | IPC13<14:12> |  |

| Crypto Key Store Program Done        | 64     | 56    | 000084h | IFS3<8>                 | IEC3<8>  | IPC14<2:0>   |  |

| Crypto Rollover                      | 43     | 35    | 00005Ah | IFS2<3>                 | IEC2<3>  | IPC8<14:12>  |  |

| CTMU Event                           | 85     | 77    | 0000AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>   |  |

| DAC                                  | 86     | 78    | 0000B0h | IFS4<14>                | IEC4<14> | IPC19<10:8>  |  |

| DMA Channel 0                        | 12     | 4     | 00001Ch | IFS0<4>                 | IEC0<4>  | IPC1<2:0>    |  |

| DMA Channel 1                        | 22     | 14    | 000030h | IFS0<14>                | IEC0<14> | IPC3<10:8>   |  |

| DMA Channel 2                        | 32     | 24    | 000044h | IFS1<8>                 | IEC1<8>  | IPC6<2:0>    |  |

| DMA Channel 3                        | 44     | 36    | 00005Ch | IFS2<4>                 | IEC2<4>  | IPC9<2:0>    |  |

| DMA Channel 4                        | 54     | 46    | 000070h | IFS2<14>                | IEC2<14> | IPC11<10:8>  |  |

| DMA Channel 5                        | 69     | 61    | 00008Eh | IFS3<13>                | IEC3<13> | IPC15<6:4>   |  |

| Enhanced Parallel Master Port (EPMP) | 53     | 45    | 00006Eh | IFS2<13>                | IEC2<13> | IPC11<6:4>   |  |

| External Interrupt 0                 | 8      | 0     | 000014h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>    |  |

| External Interrupt 1                 | 28     | 20    | 00003Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>    |  |

| External Interrupt 2                 | 37     | 29    | 00004Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>    |  |

| External Interrupt 3                 | 61     | 53    | 00007Eh | IFS3<5>                 | IEC3<5>  | IPC13<6:4>   |  |

| External Interrupt 4                 | 62     | 54    | 000080h | IFS3<6>                 | IEC3<6>  | IPC13<10:8>  |  |

| Flash Write/Program Done             | 23     | 15    | 000032h | IFS0<15>                | IEC0<15> | IPC3<14:12>  |  |

| FRC Self-Tune                        | 114    | 106   | 0000E8h | IFS6<10>                | IEC6<10> | IPC26<10:8>  |  |

| High/Low-Voltage Detect (HLVD)       | 80     | 72    | 0000A4h | IFS4<8>                 | IEC4<8>  | IPC18<2:0>   |  |

| I2C1 Bus Collision                   | 92     | 84    | 0000BCh | IFS5<4>                 | IEC5<4>  | IPC21<2:0>   |  |

| I2C1 Master Event                    | 25     | 17    | 000036h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>    |  |

| I2C1 Slave Event                     | 24     | 16    | 000034h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>    |  |

| I2C2 Bus Collision                   | 93     | 85    | 0000BEh | IFS5<5>                 | IEC5<5>  | IPC21<6:4>   |  |

| I2C2 Master Event                    | 58     | 50    | 000078h | IFS3<2>                 | IEC3<2>  | IPC12<10:8>  |  |

| I2C2 Slave Event                     | 57     | 49    | 000076h | IFS3<1>                 | IEC3<1>  | IPC12<6:4>   |  |

| I2C3 Master Event                    | 79     | 71    | 0000A2h | IFS4<7>                 | IEC4<7>  | IPC17<14:12> |  |

| I2C3 Slave Event                     | 78     | 70    | 0000A0h | IFS4<6>                 | IEC4<6>  | IPC17<10:8>  |  |

| IC23 Collision                       | 117    | 109   | 0000EEh | IFS6<13>                | IEC6<13> | IPC27<6:4>   |  |

| Input Capture 1                      | 9      | 1     | 000016h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>    |  |

| Input Capture 2                      | 13     | 5     | 00001Eh | IFS0<5>                 | IEC0<5>  | IPC1<6:4>    |  |

| Input Capture 3                      | 45     | 37    | 00005Eh | IFS2<5>                 | IEC2<5>  | IPC9<6:4>    |  |

| Input Capture 4                      | 46     | 38    | 000060h | IFS2<6>                 | IEC2<6>  | IPC9<10:8>   |  |

| Input Capture 5                      | 47     | 39    | 000062h | IFS2<7>                 | IEC2<7>  | IPC9<14:12>  |  |

| Input Capture 6                      | 48     | 40    | 000064h | IFS2<8>                 | IEC2<8>  | IPC10<2:0>   |  |

| Interrupt-on-Change (IOC)            | 27     | 19    | 00003Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12>  |  |

| JTAG                                 | 125    | 117   | 0000FEh | IFS7<5>                 | IEC7<5>  | IPC29<6:4>   |  |

| LCD                                  | 108    | 100   | 0000DCh | IFS6<4>                 | IEC6<4>  | IPC25<2:0>   |  |

#### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS

| REGISTER      | 9-4. KE                 | FUCUNL: REF                               |                 |                   |                  | SISTER          |                 |

|---------------|-------------------------|-------------------------------------------|-----------------|-------------------|------------------|-----------------|-----------------|

| R/W-0         | U-0                     | R/W-0                                     | R/W-0           | R/W-0             | U-0              | R/W-0, HC       | R-0, HSC        |

| ROEN          | —                       | ROSIDL                                    | ROOUT           | ROSLP             | —                | ROSWEN          | ROACTIV         |

| bit 15        |                         |                                           |                 |                   |                  |                 | bit 8           |

|               |                         |                                           |                 |                   | <b>D</b> # 4 / A |                 | <b>B</b> 444 A  |

| U-0           | U-0                     | U-0                                       | U-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0           |

|               | —                       | _                                         | —               | ROSEL3            | ROSEL2           | ROSEL1          | ROSEL0          |

| bit 7         |                         |                                           |                 |                   |                  |                 | bit 0           |

| Legend:       |                         | HC = Hardware                             | e Clearable bit | HSC = Hardw       | are Settable/0   | Clearable bit   |                 |

| R = Readabl   | e bit                   | W = Writable b                            | it              | U = Unimplen      | nented bit, rea  | d as '0'        |                 |

| -n = Value at | POR                     | '1' = Bit is set                          |                 | '0' = Bit is clea |                  | x = Bit is unkr | nown            |

|               |                         |                                           |                 |                   |                  |                 | -               |

| bit 15        | ROEN: Re                | ference Clock En                          | able bit        |                   |                  |                 |                 |

|               | 1 = Refere              | nce Oscillator is e                       | enabled on the  | REFO pin          |                  |                 |                 |

|               | 0 = Refere              | nce Oscillator is o                       | lisabled        |                   |                  |                 |                 |

| bit 14        | Unimplem                | ented: Read as '                          | 0'              |                   |                  |                 |                 |

| bit 13        |                         | Reference Clock S                         | •               |                   |                  |                 |                 |

|               |                         | nce Oscillator cor<br>nce Oscillator is o |                 |                   |                  |                 |                 |

| bit 12        |                         |                                           |                 |                   |                  |                 |                 |

| DILIZ         |                         | leference Clock C<br>nce clock externa    | •               |                   | lo on the DEE    | Onin            |                 |

|               |                         | nce clock externa                         | •               |                   |                  | Opin            |                 |

| bit 11        |                         | eference Clock S                          | •               |                   |                  |                 |                 |

|               |                         | nce Oscillator cor                        | • •             |                   |                  |                 |                 |

|               |                         | nce Oscillator is o                       |                 |                   |                  |                 |                 |

| bit 10        | Unimplem                | ented: Read as '                          | 0'              |                   |                  |                 |                 |

| bit 9         | ROSWEN:                 | Reference Clock                           | Output Enable   | e bit             |                  |                 |                 |

|               |                         | divider change (r                         | • •             | •                 |                  | RODIVx) is requ | lested or is in |

|               |                         | ess (set in softwar<br>divider change ha  |                 |                   | ompletion)       |                 |                 |

| hit 0         |                         | Reference Clock                           |                 | r is not pending  |                  |                 |                 |

| bit 8         |                         | nce clock is active                       |                 |                   |                  |                 |                 |

|               |                         | nce clock is stopp                        |                 |                   | ation may be s   | afely changed   |                 |

| bit 7-4       |                         | ented: Read as '                          |                 | 5                 | ,                | , ,             |                 |

| bit 3-0       |                         | :0>: Reference C                          |                 | lect bits         |                  |                 |                 |

|               | 1111 =                  |                                           |                 |                   |                  |                 |                 |

|               | ••• = Re                | served                                    |                 |                   |                  |                 |                 |

|               | 1001 =                  |                                           |                 |                   |                  |                 |                 |

|               | 1000 = RE<br>0111 = Re  |                                           |                 |                   |                  |                 |                 |

|               |                         | L block (Fixed PL                         | L output freque | ency or 96 MHz    | PLL output)      |                 |                 |

|               | 0101 <b>= Se</b>        | condary Oscillato                         | • •             | 5                 | . ,              |                 |                 |

|               | 0100 = LP               |                                           |                 |                   |                  |                 |                 |

|               | 0011 = FR<br>0010 = Pri | C<br>mary Oscillator                      |                 |                   |                  |                 |                 |

|               |                         | ripheral clock (Fc                        | Y)              |                   |                  |                 |                 |

|               | 0000 <b>= CP</b>        |                                           |                 |                   |                  |                 |                 |

### REGISTER 9-4: REFOCONL: REFERENCE CLOCK CONTROL LOW REGISTER

NOTES:

| U-0          | U-0                           | U-0                                                       | U-0            | U-0               | R/W-0            | U-0             | R/W-0 |  |

|--------------|-------------------------------|-----------------------------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|

| _            | _                             | —                                                         |                |                   | CMPMD            | —               | PMMD  |  |

| bit 15       |                               |                                                           |                |                   |                  |                 | bit 8 |  |

|              |                               |                                                           |                |                   |                  |                 |       |  |

| R/W-0        | R/W-0                         | U-0                                                       | U-0            | R/W-0             | R/W-0            | R/W-0           | U-0   |  |

| CRCMD        | DACMD                         |                                                           |                | U3MD              | I2C3MD           | I2C2MD          | _     |  |

| bit 7        |                               |                                                           |                |                   |                  |                 | bit ( |  |

| Legend:      |                               |                                                           |                |                   |                  |                 |       |  |

| R = Readab   | le bit                        | W = Writable b                                            | it             | U = Unimplen      | nented bit, read | l as '0'        |       |  |

| -n = Value a | t POR                         | '1' = Bit is set                                          |                | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |

|              |                               |                                                           |                |                   |                  |                 |       |  |

| bit 15-11    | Unimplemen                    | ted: Read as '0                                           | 3              |                   |                  |                 |       |  |

| bit 10       | CMPMD: Trip                   | le Comparator N                                           | Module Disabl  | e bit             |                  |                 |       |  |

|              | 1 = Module is                 |                                                           |                |                   |                  |                 |       |  |

| L:1 0        | •                             | ower and clock                                            |                | enabled           |                  |                 |       |  |

| bit 9        | -                             | ted: Read as '0                                           |                |                   |                  |                 |       |  |

| bit 8        | -                             | nced Parallel Ma                                          | aster Port Dis | able bit          |                  |                 |       |  |

|              | 1 = Module is<br>0 = Module p | ower and clock                                            | sources are e  | nabled            |                  |                 |       |  |

| bit 7        | •                             | C Module Disabl                                           |                |                   |                  |                 |       |  |

|              | 1 = Module is                 | s disabled                                                |                |                   |                  |                 |       |  |

|              | 0 = Module p                  | ower and clock                                            | sources are e  | enabled           |                  |                 |       |  |

| bit 6        | DACMD: DAG                    | C Module Disabl                                           | le bit         |                   |                  |                 |       |  |

|              | 1 = Module is                 |                                                           |                |                   |                  |                 |       |  |

|              | •                             | ower and clock                                            |                | enabled           |                  |                 |       |  |

| bit 5-4      | -                             | ted: Read as '0                                           |                |                   |                  |                 |       |  |

| bit 3        |                               | 3 Module Disab                                            | le bit         |                   |                  |                 |       |  |

|              | 1 = Module is                 | s disabled over and clock                                 | sources are e  | nabled            |                  |                 |       |  |

| bit 2        | -                             |                                                           |                |                   |                  |                 |       |  |

|              |                               | I2C3MD: I2C3 Module Disable bit<br>1 = Module is disabled |                |                   |                  |                 |       |  |

|              |                               | ower and clock                                            | sources are e  | enabled           |                  |                 |       |  |

| bit 1        | 12C2MD: 12C2                  | 2 Module Disabl                                           | e bit          |                   |                  |                 |       |  |

|              | 1 = Module is                 |                                                           |                |                   |                  |                 |       |  |

|              | -                             | ower and clock                                            |                | enabled           |                  |                 |       |  |

|              |                               | ted: Read as '0                                           |                |                   |                  |                 |       |  |

### REGISTER 10-6: PMD3: PERIPHERAL MODULE DISABLE REGISTER 3

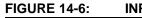

### 14.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 14-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 14-3.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |

|------------------------------|-----------------------|------------------------------------|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |

| 0001                         | 0                     | Every Rising (16-bit capture)      |

| 0001                         | 1                     | Every Rising (32-bit capture)      |

| 0010                         | 0                     | Every Falling (16-bit capture)     |

| 0010                         | 1                     | Every Falling (32-bit capture)     |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |

TABLE 14-3: INPUT CAPTURE MODES

#### **INPUT CAPTURE x BLOCK DIAGRAM**

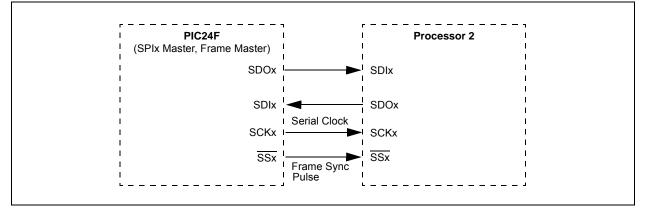

#### FIGURE 17-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

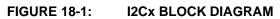

### REGISTER 18-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                                                                                                                                                                          |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                                                                                                                                                                  |

|         | In I <sup>2</sup> C Slave mode only; used in conjunction with the SCKREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                                                                                                                                                                        |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                                                                                                                                                                           |

|         | In I <sup>2</sup> C Master mode during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.<br>In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent |

|         | 0 = ACK is sent                                                                                                                                                                                                                                                                                                                                                                       |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit<br>In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                                                                                                                                  |

| bit 3   | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                   |

|         | 1 = Enables Receive mode for $I^2C$ ; automatically cleared by hardware at end of 8-bit receive data byte 0 = Receive sequence is not in progress                                                                                                                                                                                                                                     |

| bit 2   | <b>PEN:</b> Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                                                                                                                                                                            |

| bit 1   | <b>RSEN:</b> Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                                                                                                                                                                      |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                                                                                                                                                                          |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                                                                                                                                                                      |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

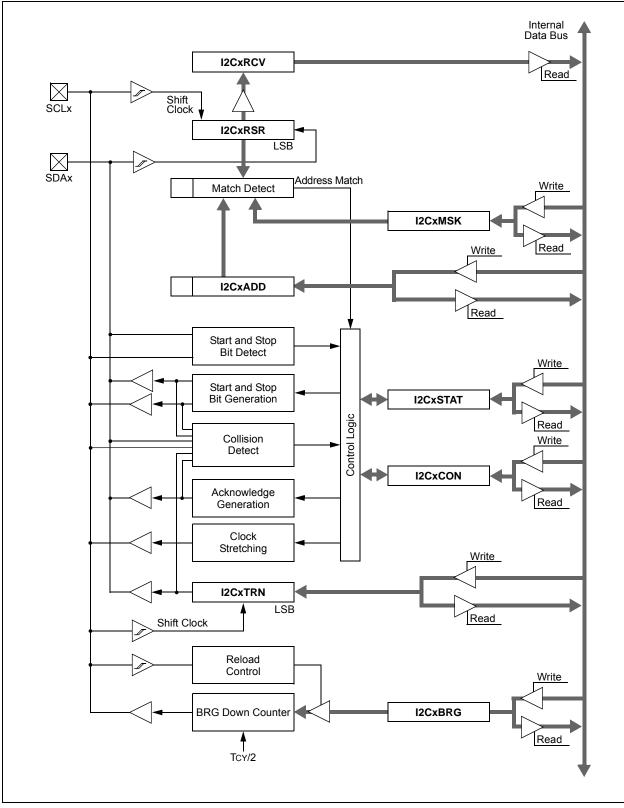

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ256GA412/GB412 family devices are equipped with six UART modules, referred to as UART1 through UART6.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from up to 2.5 Mbps and Down to 38 Hz at 40 MIPS in 16x Mode

- Baud Rates Range from up to 10 Mbps and Down to 152 Hz at 40 MIPS in 4x Mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Mode with Address Detect (9<sup>th</sup> bit = 1)

- Separate Transmit and Receive Interrupts

- Loopback Mode for Diagnostic Support

- · Polarity Control for Transmit and Receive Lines

- Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 19-1. The UARTx module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

Asynchronous Receiver

Note: Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTAL" might refer to the Status Low register for either UART1, UART2, UART3 or UART4.

# REGISTER 22-6: LCDREF: LCD REFERENCE LADDER CONTROL REGISTER

|                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  | TROL REGIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-0                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |