Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                          |

| Number of I/O              | 52                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb406-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA406

- 06 PIC24FJ64GB406

- PIC24FJ128GA406

PIC24FJ256GA406

- PIC24FJ128GB406

PIC24FJ256GB406

- PIC24FJ64GA410

PIC24FJ64GB410

- PIC24FJ128GA410

PIC24FJ128GB410

- PIC24FJ256GA410

- PIC24FJ256GB410

- PIC24FJ64GA412

- PIC24FJ64GB412

- PIC24FJ128GA412PIC24FJ256GA412

- PIC24FJ128GB412

PIC24FJ256GB412

- The PIC24FJ256GA412/GB412 family expands the capabilities of the PIC24F family by adding a complete selection of advanced analog peripherals to its existing digital features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals, USB On-The-Go (OTG) and a built-in LCD Controller and driver, makes this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

## 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

## 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ256GA412/GB412 family of devices incorporates a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep, with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC, for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC), to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, the PIC24FJ256GA412/ GB412 devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

#### 1.1.3 DUAL PARTITION FLASH PROGRAM MEMORY

A brand new feature to the PIC24F family is the use of Dual Partition Flash program memory technology. This allows PIC24FJ256GA412/GB412 family devices a range of new operating options not available before:

- Dual Partition Operation, which can store two different applications in their own code partition, and allows for the support of robust bootloader applications and enhanced security

- Live Update Operation, which allows the main application to continue operation while the second Flash partition is being reprogrammed – all without adding Wait states to code execution

- Direct Run-Time Programming from Data RAM, with the option of data compression in the RAM image

PIC24FJ256GA412/GB412 family devices can also operate with their two Flash partitions as one large program memory, providing space for large and complex applications.

|              | Pir  | Pin/Pad Number64-Pin100-Pin121-PinTQFPTQFPTFBGA |        |   |              |                                     |

|--------------|------|-------------------------------------------------|--------|---|--------------|-------------------------------------|

| Pin Function |      |                                                 |        |   | Input Buffer | Description                         |

| AN0          | 16   | 25                                              | K2     | I | ANA          | A/D Analog Inputs                   |

| AN1          | 15   | 24                                              | K1     | I | ANA          |                                     |

| AN1-         | 15   | 24                                              | K1     | I | ANA          |                                     |

| AN2          | 14   | 23                                              | J2     | I | ANA          |                                     |

| AN3          | 13   | 22                                              | J1     | I | ANA          |                                     |

| AN4          | 12   | 21                                              | H2     | I | ANA          |                                     |

| AN5          | 11   | 20                                              | H1     | I | ANA          |                                     |

| AN6          | 17   | 26                                              | L1     | I | ANA          |                                     |

| AN7          | 18   | 27                                              | J3     | I | ANA          |                                     |

| AN8          | 21   | 32                                              | K4     | I | ANA          |                                     |

| AN9          | 22   | 33                                              | L4     | I | ANA          |                                     |

| AN10         | 23   | 34                                              | H5     | I | ANA          |                                     |

| AN11         | 24   | 35                                              | K5     | I | ANA          |                                     |

| AN12         | 27   | 41                                              | J7     | I | ANA          |                                     |

| AN13         | 28   | 42                                              | L7     | I | ANA          |                                     |

| AN14         | 29   | 43                                              | K7     | I | ANA          |                                     |

| AN15         | 30   | 44                                              | L8     | I | ANA          |                                     |

| AN16         | _    | 9                                               | E1     | I | ANA          |                                     |

| AN17         | _    | 10                                              | E3     | I | ANA          |                                     |

| AN18         | _    | 11                                              | F4     | I | ANA          |                                     |

| AN19         | _    | 12                                              | F2     | I | ANA          |                                     |

| AN20         | _    | 14                                              | F3     | I | ANA          |                                     |

| AN21         | _    | 19                                              | G2     | I | ANA          |                                     |

| AN22         | _    | 92                                              | E11    | I | ANA          |                                     |

| AN23         | —    | 91                                              | E10    | I | ANA          |                                     |

| AVDD         | 19   | 30                                              | J4     | Р | —            | Positive Supply for Analog modules  |

| AVss         | 20   | 31                                              | L3     | Р | —            | Ground Reference for Analog modules |

| C1INA        | 11   | 20                                              | H1     | I | ANA          | Comparator 1 Input A                |

| C1INB        | 12   | 21                                              | H2     | Ι | ANA          | Comparator 1 Input B                |

| C1INC        | 5,8  | 11,14                                           | F4,F3  | Ι | ANA          | Comparator 1 Input C                |

| C1IND        | 4    | 10                                              | E3     | I | ANA          | Comparator 1 Input D                |

| C2INA        | 13   | 22                                              | J1     | Ι | ANA          | Comparator 2 Input A                |

| C2INB        | 14   | 23                                              | J2     | I | ANA          | Comparator 2 Input B                |

| C2INC        | 8    | 14                                              | F3     | I | ANA          | Comparator 2 Input C                |

| C2IND        | 6    | 12                                              | F2     | I | ANA          | Comparator 2 Input D                |

| C3INA        | 55   | 84                                              | C7     | I | ANA          | Comparator 3 Input A                |

| C3INB        | 54   | 83                                              | D7     | I | ANA          | Comparator 3 Input B                |

| C3INC        | 8,45 | 14,71                                           | F3,C11 | I | ANA          | Comparator 3 Input C                |

| C3IND        | 44   | 70                                              | D11    | I | ANA          | Comparator 3 Input D                |

| CLC3OUT      | 46   | 72                                              | D9     | 0 | DIG          | CLC3 Output                         |

| CLC4OUT      | 42   | 68                                              | E9     | 0 | DIG          | CLC4 Output                         |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION

**Legend:** TTL = TTL input buffer

ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

|              | Pir                         | n/Pad Numl | ber | PINOUT DESCRIP |              |                                                                               |  |  |  |

|--------------|-----------------------------|------------|-----|----------------|--------------|-------------------------------------------------------------------------------|--|--|--|

| Pin Function | 64-Pin 100-Pin<br>TQFP TQFP |            |     | I/O            | Input Buffer | Description                                                                   |  |  |  |

| IOCG0        | _                           | 90         | A5  | I              | ST           | PORTG Interrupt-on-Change                                                     |  |  |  |

| IOCG1        | _                           | 89         | E6  | I              | ST           |                                                                               |  |  |  |

| IOCG2        | 37                          | 57         | H10 | I              | ST           | 1                                                                             |  |  |  |

| IOCG3        | 36                          | 56         | J11 | I              | ST           | 1                                                                             |  |  |  |

| IOCG6        | 4                           | 10         | E3  | I              | ST           | 1                                                                             |  |  |  |

| IOCG7        | 5                           | 11         | F4  | I              | ST           | ]                                                                             |  |  |  |

| IOCG8        | 6                           | 12         | F2  | I              | ST           | ]                                                                             |  |  |  |

| IOCG9        | 8                           | 14         | F3  | I              | ST           | ]                                                                             |  |  |  |

| IOCG12       | —                           | 96         | E17 | I              | ST           |                                                                               |  |  |  |

| IOCG13       | —                           | 97         | E18 | I              | ST           |                                                                               |  |  |  |

| IOCG14       | —                           | 95         | E16 | I              | ST           |                                                                               |  |  |  |

| IOCG15       | _                           | 1          | B2  | I              | ST           |                                                                               |  |  |  |

| IOCH1        | —                           | _          | B1  | I              | ST           | PORTH Interrupt-on-Change                                                     |  |  |  |

| IOCH2        | _                           | _          | D4  | I              | ST           | ]                                                                             |  |  |  |

| IOCH3        | _                           |            | G4  | I              | ST           | ]                                                                             |  |  |  |

| IOCH4        | _                           |            | H3  | I              | ST           | ]                                                                             |  |  |  |

| IOCH5        | —                           | —          | H4  | I              | ST           |                                                                               |  |  |  |

| IOCH6        | _                           | _          | L5  | I              | ST           |                                                                               |  |  |  |

| IOCH7        | —                           | _          | J5  | I              | ST           |                                                                               |  |  |  |

| IOCH8        | —                           | _          | H7  | Ι              | ST           |                                                                               |  |  |  |

| IOCH9        | _                           | —          | J8  | Ι              | ST           |                                                                               |  |  |  |

| IOCH10       | _                           | —          | J9  | Ι              | ST           |                                                                               |  |  |  |

| IOCH11       | —                           | _          | G8  | I              | ST           |                                                                               |  |  |  |

| IOCH12       | —                           | —          | F7  | I              | ST           |                                                                               |  |  |  |

| IOCH13       | —                           | —          | C9  | I              | ST           |                                                                               |  |  |  |

| IOCH14       |                             | —          | A8  | I              | ST           |                                                                               |  |  |  |

| IOCH15       |                             | —          | F6  | I              | ST           |                                                                               |  |  |  |

| IOCJ0        | —                           | —          | E13 | I              | ST           | PORTJ Interrupt-on-Change                                                     |  |  |  |

| IOCJ1        |                             | —          | E14 | I              | ST           |                                                                               |  |  |  |

| LCDBIAS0     | 3                           | 5          | D2  | 0              | ANA          | Bias Inputs for LCD Driver Charge Pump                                        |  |  |  |

| LCDBIAS1     | 2                           | 4          | C1  | 0              | ANA          |                                                                               |  |  |  |

| LCDBIAS2     | 1                           | 3          | D3  | 0              | ANA          |                                                                               |  |  |  |

| LCDBIAS3     | 17                          | 26         | L1  | 0              | ANA          |                                                                               |  |  |  |

| LVDIN        | 64                          | 100        | E31 | I              | ANA          | Low-Voltage Detect Input                                                      |  |  |  |

| MCLR         | 7                           | 13         | F1  | I              | ST/STMV      | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |  |  |  |

| OC4          | 54                          | 83         | D7  | 0              | DIG          | Output Compare 4 Output                                                       |  |  |  |

| OC5          | 55                          | 84         | C7  | 0              | DIG          | Output Compare 5 Output                                                       |  |  |  |

| OC6          | 58                          | 87         | B6  | 0              | DIG          | Output Compare 6 Output                                                       |  |  |  |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

## 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                  | U-0                                                                                                   | U-0                                                                                                                                         | U-0            | U-0                | U-0                           | U-0               | R/W-0          |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|-------------------------------|-------------------|----------------|--|--|--|--|

|                      | —                                                                                                     | _                                                                                                                                           | —              |                    |                               |                   | DC             |  |  |  |  |

| bit 15               |                                                                                                       |                                                                                                                                             |                |                    | •                             |                   | bit            |  |  |  |  |

| (4)                  | (4)                                                                                                   | (4)                                                                                                                                         |                |                    |                               |                   |                |  |  |  |  |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                  | R/W-0 <sup>(1)</sup>                                                                                                                        | R-0            | R/W-0              | R/W-0                         | R/W-0             | R/W-0          |  |  |  |  |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>                                                                                   | IPL0 <sup>(2)</sup>                                                                                                                         | RA             | N                  | OV                            | Z                 | С              |  |  |  |  |

| bit 7                |                                                                                                       |                                                                                                                                             |                |                    |                               |                   | bit            |  |  |  |  |

| Legend:              |                                                                                                       |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| R = Readable         | bit                                                                                                   | W = Writable b                                                                                                                              | it             | U = Unimplem       | nented bit, read              | d as '0'          |                |  |  |  |  |

| -n = Value at F      | POR                                                                                                   | '1' = Bit is set                                                                                                                            |                | '0' = Bit is clea  | ared                          | x = Bit is unkr   | nown           |  |  |  |  |

|                      |                                                                                                       |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| bit 15-9             | Unimplemen                                                                                            | ted: Read as '0'                                                                                                                            |                |                    |                               |                   |                |  |  |  |  |

| bit 8                |                                                                                                       | f Carry/Borrow b                                                                                                                            |                |                    |                               |                   |                |  |  |  |  |

|                      | 1 = A carry c                                                                                         | out from the 4 <sup>th</sup> lo                                                                                                             | w-order bit (  | for byte-sized da  | ata) or 8 <sup>th</sup> Iow-o | order bit (for wo | ord-sized data |  |  |  |  |

|                      | of the res                                                                                            | sult occurred                                                                                                                               | th             |                    |                               |                   |                |  |  |  |  |

|                      | 0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| oit 7-5              | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                   |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled                            |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 110 = CPU Interrupt Priority Level is 6 (14)                                                          |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 101 = CPU Interrupt Priority Level is 5 (13)                                                          |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 100 = CPU Interrupt Priority Level is 4 (12)                                                          |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 011 = CPU Interrupt Priority Level is 3 (11)                                                          |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)           |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      |                                                                                                       | nterrupt Priority I<br>nterrupt Priority I                                                                                                  |                |                    |                               |                   |                |  |  |  |  |

| oit 4                |                                                                                                       |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| <i><i></i></i>       | RA: REPEAT Loop Active bit<br>1 = REPEAT loop is in progress                                          |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 0 = REPEAT loop is not in progress                                                                    |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| pit 3                | N: ALU Nega                                                                                           |                                                                                                                                             | -              |                    |                               |                   |                |  |  |  |  |

|                      | 1 = Result was negative                                                                               |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 0 = Result was not negative (zero or positive)                                                        |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

| bit 2                | OV: ALU Overflow bit                                                                                  |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      |                                                                                                       | <ul> <li>Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation</li> <li>No overflow has occurred</li> </ul> |                |                    |                               |                   |                |  |  |  |  |

| bit 1                | Z: ALU Zero bit                                                                                       |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 1 = An operation, which affects the Z bit, has set it at some time in the past                        |                                                                                                                                             |                |                    |                               |                   |                |  |  |  |  |

|                      | 0 = The most                                                                                          | recent operation                                                                                                                            | n, which affe  | cts the Z bit, has | s cleared it (i.e.            | , a non-zero re   | sult)          |  |  |  |  |

| oit O                | C: ALU Carry                                                                                          | //Borrow bit                                                                                                                                |                |                    |                               |                   |                |  |  |  |  |

|                      |                                                                                                       | ut from the Most                                                                                                                            |                |                    |                               |                   |                |  |  |  |  |

|                      | 0 = No carry                                                                                          | out from the Mos                                                                                                                            | st Significant | bit of the result  | occurred                      |                   |                |  |  |  |  |

| Note 1: The          | DI v Statue I                                                                                         | oits are read-only                                                                                                                          |                |                    | 15>) - 1                      |                   |                |  |  |  |  |

|                      |                                                                                                       | -                                                                                                                                           |                | PI 3 Status (C     | -                             | wit to form the C |                |  |  |  |  |

2: The IPLx Status bits are concatenated with the IPL3 Status (CORCON<3>) bit to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

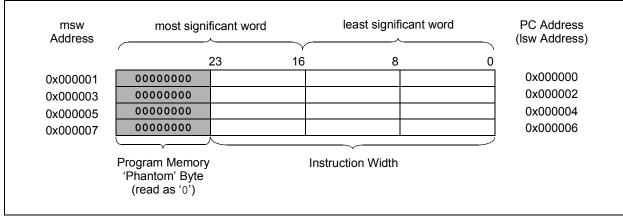

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

#### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 000000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVTs). The main IVT has a static location, from 000004h to 0000FFh. The Alternate IVT has a configurable location and is optionally enabled. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 8.0 "Interrupt Controller"**.

## 4.1.3 SINGLE AND DUAL PARTITION MEMORY ORGANIZATION

The PIC24FJ256GA412/GB412 family of devices supports a Single Partition Flash mode and two Dual Partition Flash modes. The Dual Partition modes allow the device to be programmed with two separate applications to facilitate bootloading or to allow an application to be programmed at run-time without stalling the CPU.

In the Dual Partition modes, the device's memory is divided evenly into two physical sections, known as Partition 1 and Partition 2. Each of these partitions contains its own program memory and Configuration Words. During program execution, the code on only one of these panels is executed; this is the Active Partition. The other partition, or the Inactive Partition, is not used, but can be programmed.

The Active Partition is always mapped to logical address, 000000h, while the Inactive Partition will always be mapped to logical address, 400000h. Note that even when the code partitions are switched between active and inactive by the user, the address of the Active Partition will still be 000000h and the address of the Inactive Partition will still be at 400000h. Figure 4-3 compares the mapping of the user memory space in Single and Dual Partition devices.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| REGISTER 8-10: IFS4: INTERRUPT FLAG STATUS REGISTER 4 |                                                                                                        |                                    |                |                   |                  |                 |        |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| U-0                                                   | R/W-0                                                                                                  | R/W-0                              | U-0            | U-0               | U-0              | R/W-0           | R/W-0  |  |  |  |  |

| _                                                     | DAC1IF                                                                                                 | CTMUIF                             |                |                   |                  | CCP7IF          | HLVDIF |  |  |  |  |

| bit 15                                                |                                                                                                        |                                    |                |                   |                  |                 | bit    |  |  |  |  |

| R/W-0                                                 | R/W-0                                                                                                  | U-0                                | U-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| MI2C3IF                                               | SI2C3IF                                                                                                |                                    | _              | CRCIF             | U2ERIF           | U1ERIF          | CCP2IF |  |  |  |  |

| bit 7                                                 |                                                                                                        |                                    |                |                   |                  |                 | bit    |  |  |  |  |

| Legend:                                               |                                                                                                        |                                    |                |                   |                  |                 |        |  |  |  |  |

| R = Readabl                                           | e bit                                                                                                  | W = Writable b                     | oit            | U = Unimplerr     | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at                                         | POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea |                  | x = Bit is unkr | iown   |  |  |  |  |

| bit 15                                                | Unimplemen                                                                                             | ted: Read as '0                    | ,              |                   |                  |                 |        |  |  |  |  |

| bit 14                                                | -                                                                                                      | C Converter Inte                   |                | atus bit          |                  |                 |        |  |  |  |  |

|                                                       |                                                                                                        | request has occ                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       |                                                                                                        | request has not                    |                |                   |                  |                 |        |  |  |  |  |

| bit 13                                                | CTMUIF: CTI                                                                                            | MU Interrupt Fla                   | ig Status bit  |                   |                  |                 |        |  |  |  |  |

|                                                       | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 12-10                                             | •                                                                                                      | •                                  |                |                   |                  |                 |        |  |  |  |  |

| bit 9                                                 | Unimplemented: Read as '0'<br>CCP7IF: SCCP7 Capture/Compare Interrupt Flag Status bit                  |                                    |                |                   |                  |                 |        |  |  |  |  |

| DIL 9                                                 | 1 = Interrupt request has occurred                                                                     |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 0 = Interrupt request has occurred                                                                     |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 8                                                 | HLVDIF: High/Low-Voltage Detect Interrupt Flag Status bit                                              |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 1 = Interrupt request has occurred                                                                     |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 0 = Interrupt request has not occurred                                                                 |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 7                                                 | MI2C3IF: Master I2C3 Event Interrupt Flag Status bit                                                   |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | <ol> <li>Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>         |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 6                                                 | SI2C3IF: Slave I2C3 Event Interrupt Flag Status bit                                                    |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 1 = Interrupt request has occurred                                                                     |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 0 = Interrupt request has not occurred                                                                 |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 5-4                                               | Unimplemen                                                                                             | ted: Read as '0                    | 3              |                   |                  |                 |        |  |  |  |  |

| bit 3                                                 | CRCIF: CRC Generator Interrupt Flag Status bit                                                         |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | 1 = Interrupt request has occurred                                                                     |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 2                                                 | 0 = Interrupt request has not occurred                                                                 |                                    |                |                   |                  |                 |        |  |  |  |  |

| DIL Z                                                 | U2ERIF: UART2 Error Interrupt Flag Status bit                                                          |                                    |                |                   |                  |                 |        |  |  |  |  |

|                                                       | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol>     |                                    |                |                   |                  |                 |        |  |  |  |  |

| bit 1                                                 | U1ERIF: UAF                                                                                            | RT1 Error Interru                  | upt Flag Statu | s bit             |                  |                 |        |  |  |  |  |

|                                                       |                                                                                                        | request has occ<br>request has not |                |                   |                  |                 |        |  |  |  |  |

| bit 0                                                 | -                                                                                                      | -                                  |                | ot Flag Status bi | t                |                 |        |  |  |  |  |

|                                                       |                                                                                                        | equest has occu                    | • •            |                   |                  |                 |        |  |  |  |  |

|                                                       |                                                                                                        | equest has not o                   |                |                   |                  |                 |        |  |  |  |  |

### REGISTER 8-10: IFS4: INTERRUPT FLAG STATUS REGISTER 4

#### REGISTER 8-19: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5 (CONTINUED)

- bit 3 U3TXIE: UART3 Transmitter Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 2 U3RXIE: UART3 Receiver Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 1 U3ERIE: UART3 Error Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

| U-0          | R/W-1                                                                                                                 | R/W-0               | R/W-0            | U-0             | R/W-1            | R/W-0            | R/W-0            |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|---------------------|------------------|-----------------|------------------|------------------|------------------|--|--|--|--|

| _            | NVMIP2                                                                                                                | NVMIP1              | NVMIP0           | —               | DMA1IP2          | DMA1IP1          | DMA1IP0          |  |  |  |  |

| oit 15       |                                                                                                                       |                     | 1                |                 |                  |                  | bit              |  |  |  |  |

|              | D 44/ 4                                                                                                               | DAMA                | DAMO             |                 | DA4/4            | DAMA             | DAMO             |  |  |  |  |

| U-0          | R/W-1<br>AD1IP2                                                                                                       | R/W-0<br>AD1IP1     | R/W-0<br>AD1IP0  | U-0             | R/W-1<br>U1TXIP2 | R/W-0<br>U1TXIP1 | R/W-0<br>U1TXIP0 |  |  |  |  |

| <br>bit 7    | ADTIFZ                                                                                                                | ADTIFT              | ADTIFU           |                 | UTTAIP2          | UTIAIPT          | bit              |  |  |  |  |

|              |                                                                                                                       |                     |                  |                 |                  |                  | bit              |  |  |  |  |

| Legend:      |                                                                                                                       |                     |                  |                 |                  |                  |                  |  |  |  |  |

| R = Readab   | le bit                                                                                                                | W = Writable        | bit              | U = Unimple     | mented bit, read | d as '0'         |                  |  |  |  |  |

| -n = Value a | t POR                                                                                                                 | '1' = Bit is set    |                  | '0' = Bit is cl | eared            | x = Bit is unkr  | nown             |  |  |  |  |

| bit 15       | Unimplemen                                                                                                            | nted: Read as '     | n'               |                 |                  |                  |                  |  |  |  |  |

| bit 14-11    | -                                                                                                                     | : Flash Memory      |                  | n Interrupt Pri | ority bits       |                  |                  |  |  |  |  |

|              |                                                                                                                       | upt is Priority 7 ( | -                | =               |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     | . , , ,             |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                                                                                    |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              |                                                                                                                       | upt source is dis   | abled            |                 |                  |                  |                  |  |  |  |  |

| bit 7        |                                                                                                                       | nted: Read as '     |                  |                 |                  |                  |                  |  |  |  |  |

| bit 10-8     | DMA1IP<2:0>: DMA Channel 1 Interrupt Priority bits                                                                    |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                            |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                   |                     |                  |                 |                  |                  |                  |  |  |  |  |

| bit 7        |                                                                                                                       | nted: Read as '     |                  |                 |                  |                  |                  |  |  |  |  |

| bit 6-4      | -                                                                                                                     |                     |                  | Priority hits   |                  |                  |                  |  |  |  |  |

|              | AD1IP<2:0>: 12-Bit Pipeline A/D Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              |                                                                                                                       |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                   |                     |                  |                 |                  |                  |                  |  |  |  |  |

| bit 3        |                                                                                                                       | nted: Read as '     |                  |                 |                  |                  |                  |  |  |  |  |

| bit 2-0      | U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits                                                                |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | 111 = Interru                                                                                                         | upt is Priority 7 ( | highest priority | / interrupt)    |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •                                                                                                                     |                     |                  |                 |                  |                  |                  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                                                                                    |                     |                  |                 |                  |                  |                  |  |  |  |  |

#### REGISTER 8-25: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0                          | R/W-1                                                                             | R/W-0                                                                                                                             | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —                            | U2TXIP2                                                                           | U2TXIP1                                                                                                                           | U2TXIP0           | —                | U2RXIP2          | U2RXIP1         | U2RXIP0 |  |  |  |  |

| oit 15                       |                                                                                   |                                                                                                                                   |                   |                  |                  |                 | bit     |  |  |  |  |

| U-0                          | R/W-1                                                                             | R/W-0                                                                                                                             | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|                              | INT2IP2                                                                           | INT2IP1                                                                                                                           | INT2IP0           | 0-0              | T5IP2            | T5IP1           | T5IP0   |  |  |  |  |

| bit 7                        |                                                                                   | 11112111                                                                                                                          | 1111211-0         |                  | 1011 2           |                 | bit     |  |  |  |  |

|                              |                                                                                   |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

| <b>Legend:</b><br>R = Readab | le bit                                                                            | W = Writable                                                                                                                      | bit               | U = Unimple      | mented bit, read | 1 as '0'        |         |  |  |  |  |

| -n = Value a                 |                                                                                   | '1' = Bit is set                                                                                                                  |                   | '0' = Bit is cle |                  | x = Bit is unkr | Iown    |  |  |  |  |

| bit 15                       | Unimplemen                                                                        | ted: Read as '                                                                                                                    | ٥'                |                  |                  |                 |         |  |  |  |  |

| bit 14-12                    | -                                                                                 |                                                                                                                                   |                   | t Priority bits  |                  |                 |         |  |  |  |  |

|                              |                                                                                   | <b>U2TXIP&lt;2:0&gt;:</b> UART2 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled               |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

| bit 11                       |                                                                                   | -                                                                                                                                 |                   |                  |                  |                 |         |  |  |  |  |

| bit 10-8                     | Unimplemented: Read as '0'<br>U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | 111 = Interrupt is Priority 7 (highest priority interrupt)                        |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •<br>001 = Interrupt is Priority 1                                                |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | 000 = Interrupt source is disabled                                                |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

| bit 7                        | Unimplemen                                                                        | ted: Read as '                                                                                                                    | 0'                |                  |                  |                 |         |  |  |  |  |

| bit 6-4                      | INT2IP<2:0>:                                                                      | External Interr                                                                                                                   | rupt 2 Priority b | its              |                  |                 |         |  |  |  |  |

|                              | 111 = Interrupt is Priority 7 (highest priority interrupt)                        |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              |                                                                                   |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled               |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

| bit 3                        | Unimplemen                                                                        | ted: Read as '                                                                                                                    | 0'                |                  |                  |                 |         |  |  |  |  |

| bit 2-0                      | T5IP<2:0>: ⊺                                                                      | imer5 Interrupt                                                                                                                   | Priority bits     |                  |                  |                 |         |  |  |  |  |

|                              |                                                                                   | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | •                                                                                 |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | 001 - Interru                                                                     |                                                                                                                                   |                   |                  |                  |                 |         |  |  |  |  |

|                              | UUL = Interiu                                                                     | pt is Priority 1                                                                                                                  |                   |                  |                  |                 |         |  |  |  |  |

### REGISTER 8-29: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enable bit                                                 |

|-------|------------------------------------------------------------------------------------------|

|       | If FSCM is enabled (FCKSM1 = 1):                                                         |

|       | 1 = Clock and PLL selections are locked                                                  |

|       | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit |

|       | If FSCM is disabled (FCKSM1 = 0):                                                        |

|       | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.  |

| bit 6 | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                               |

|       | 1 = I/O lock is active                                                                   |

|       | 0 = I/O lock is not active                                                               |

| bit 5 | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                 |

|       | 1 = PLL module is in lock or PLL module start-up timer is satisfied                      |

|       | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled          |

| bit 4 | Unimplemented: Read as '0'                                                               |

| bit 3 | CF: Clock Fail Detect bit                                                                |

|       | 1 = FSCM has detected a clock failure                                                    |

|       | 0 = No clock failure has been detected                                                   |

| bit 2 | POSCEN: Primary Oscillator Sleep Enable bit                                              |

|       | 1 = Primary Oscillator continues to operate during Sleep mode                            |

|       | 0 = Primary Oscillator is disabled during Sleep mode                                     |

| bit 1 | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                    |