Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb406t-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3: DEVICE FEATURES FOR THE PIC24FJ256GA412/GB412 FAMILY: 121-PIN

| Feeturer                                                        | PIC24FJXXXGA/GB412 |               |                                  |                                                           |               |        |  |  |  |

|-----------------------------------------------------------------|--------------------|---------------|----------------------------------|-----------------------------------------------------------|---------------|--------|--|--|--|

| Features                                                        | 64GA               | 128GA         | 256GA                            | 64GB                                                      | 128GB         | 256GB  |  |  |  |

| Operating Frequency                                             |                    | •             | DC – 3                           | 32 MHz                                                    |               | -      |  |  |  |

| Program Memory (bytes)                                          | 64K                | 128K          | 256K                             | 64K                                                       | 128K          | 256K   |  |  |  |

| Program Memory (instructions)                                   | 22,016             | 44,032        | 88,064                           | 22,016                                                    | 44,032        | 88,064 |  |  |  |

| Data Memory (bytes)                                             | 8K                 | 10            | 6K                               | 8K                                                        | 10            | 6K     |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                  |                    |               | 113 (1                           | 107/6)                                                    |               |        |  |  |  |

| I/O Ports                                                       |                    |               | Ports A, B, C,                   | D, E, F, G, H,                                            | J             |        |  |  |  |

| Total I/O Pins                                                  |                    | 102           |                                  |                                                           | 101           |        |  |  |  |

| Remappable Pins                                                 |                    |               | 44 (32 I/O, 1                    | 2 input only)                                             |               |        |  |  |  |

| Timers:                                                         |                    |               |                                  |                                                           |               |        |  |  |  |

| Total Number (16-bit)                                           |                    |               | 19                               | (1,2)                                                     |               |        |  |  |  |

| 32-Bit (from paired 16-bit timers)                              |                    |               |                                  | 9                                                         |               |        |  |  |  |

| Input Capture w/Timer Channels                                  |                    |               | -                                | (2)                                                       |               |        |  |  |  |

| Output Compare/PWM Channels                                     |                    |               | 6                                | (2)                                                       |               |        |  |  |  |

| Single Output CCP (SCCP)                                        |                    |               |                                  | 6                                                         |               |        |  |  |  |

| Multiple Output CCP (MCCP)                                      |                    |               |                                  | 1                                                         |               |        |  |  |  |

| Serial Communications:                                          |                    |               |                                  |                                                           |               |        |  |  |  |

| UART                                                            |                    |               | -                                | (2)                                                       |               |        |  |  |  |

| SPI (3-wire/4-wire)                                             |                    |               | 4                                | (2)                                                       |               |        |  |  |  |

| l <sup>2</sup> C                                                |                    |               | :                                | 3                                                         |               |        |  |  |  |

| USB On-The-Go                                                   |                    | No            |                                  |                                                           | Yes           |        |  |  |  |

| Cryptographic Engine                                            |                    |               | Y                                | es                                                        |               |        |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                           |                    |               | Y                                | es                                                        |               |        |  |  |  |

| 10/12-Bit Analog-to-Digital<br>Converter (A/D) (input channels) |                    |               | 2                                | 24                                                        |               |        |  |  |  |

| Digital-to-Analog Converter<br>(DAC)                            |                    |               |                                  | 1                                                         |               |        |  |  |  |

| Analog Comparators                                              |                    |               | ;                                | 3                                                         |               |        |  |  |  |

| CTMU Interface                                                  |                    |               | Y                                | es                                                        |               |        |  |  |  |

| LCD Controller (available pixels)                               |                    |               | 512 (64 SE                       | G x 8 COM)                                                |               |        |  |  |  |

| JTAG Boundary Scan                                              |                    |               | Y                                | es                                                        |               |        |  |  |  |

| Resets (and delays)                                             | C                  | MCLR, WI      | DT, Illegal Opc<br>Traps, Config | POR, BOR, RE<br>code, REPEAT<br>guration Word<br>LL Lock) | Instruction,  | on,    |  |  |  |

| Instruction Set                                                 | 7                  | 7 Base Instru | ctions, Multiple                 | e Addressing I                                            | Mode Variatio | ns     |  |  |  |

| Packages                                                        |                    |               | 121-Pin                          | TFBGA                                                     |               |        |  |  |  |

Note 1: Includes the Timer modes of SCCP and MCCP modules.

**2:** Some instantiations of these modules are only available through remappable pins.

|              | Pir            | /Pad Numl       | ber              |     |              |                                          |

|--------------|----------------|-----------------|------------------|-----|--------------|------------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA | I/O | Input Buffer | Description                              |

| SEG41        | _              | 53              | J10              | 0   | ANA          | LCD Driver Segment Outputs               |

| SEG42        | _              | 66              | E11              | 0   | ANA          |                                          |

| SEG43        | _              | 67              | E8               | 0   | ANA          |                                          |

| SEG44        | —              | 79              | A9               | 0   | ANA          |                                          |

| SEG45        | —              | 80              | D8               | 0   | ANA          |                                          |

| SEG46        | —              | 89              | E6               | 0   | ANA          |                                          |

| SEG47        | 59             | 88              | A6               | 0   | ANA          |                                          |

| SEG48        | —              | 17              | G3               | 0   | ANA          |                                          |

| SEG49        | —              | 90              | A5               | 0   | ANA          |                                          |

| SEG50        | —              | 1               | B2               | 0   | ANA          |                                          |

| SEG51        | —              | 7               | E4               | 0   | ANA          |                                          |

| SEG52        | —              | 9               | E1               | 0   | ANA          |                                          |

| SEG53        | —              | 39              | L6               | 0   | ANA          |                                          |

| SEG54        | _              | 40              | K6               | 0   | ANA          |                                          |

| SEG55        | _              | 58              | H11              | 0   | ANA          |                                          |

| SEG56        | _              | 59              | G10              | 0   | ANA          |                                          |

| SEG57        | _              | 91              | C5               | 0   | ANA          |                                          |

| SEG58        | _              | 92              | B5               | 0   | ANA          |                                          |

| SEG59        | _              | 95              | C4               | 0   | ANA          |                                          |

| SEG60        | _              | 96              | C3               | 0   | ANA          |                                          |

| SEG61        | —              | 97              | A3               | 0   | ANA          |                                          |

| SEG62        | 64             | 100             | A1               | 0   | ANA          |                                          |

| SEG63        | 18             | 27              | J3               | 0   | ANA          |                                          |

| SOSCI        | 47             | 73              | C10              | —   | —            | Secondary Oscillator/Timer1 Clock Input  |

| SOSCO        | 48             | 74              | B11              | —   | —            | Secondary Oscillator/Timer1 Clock Output |

| SS4/FSYNC4   | 24             | 35              | K5               | I/O | DIG/ST       | SPI4 Slave Select/Frame Sync             |

| T1CK         | 22             | 33              | L4               | I   | ST           | Timer1 Clock                             |

| ТСК          | 27             | 38              | J6               | I   | ST           | JTAG Test Clock/Programming Clock Input  |

| TDI          | 28             | 60              | G11              | I   | ST           | JTAG Test Data/Programming Data Input    |

| TDO          | 24             | 61              | G9               | 0   | DIG          | JTAG Test Data Output                    |

| TMPR         | 22             | 33              | L4               | —   | —            | Tamper Detect Input                      |

| TMS          | 23             | 17              | G3               | I   | ST           | JTAG Test Mode Select Input              |

| U5CTS        | 58             | 87              | B6               | I   | ST           | UART5 Clear-to-Send Output               |

| U5RTS/U5BCLK | 55             | 84              | C7               | 0   | DIG          | UART5 Request-to-Send Input              |

| U5RX         | 54             | 83              | D7               | I   | ST           | UART5 Receive Input                      |

| U5TX         | 49             | 76              | A11              | 0   | DIG          | UART5 Transmit Output                    |

| U6CTS        | 46             | 72              | D9               | I   | ST           | UART6 Clear-to-Send Output               |

| U6RTS/U6BCLK | 42             | 68              | E9               | 0   | DIG          | UART6 Request-to-Send Input              |

| U6RX         | 27             | 41              | J7               | I   | ST           | UART6 Receive Input                      |

| U6TX         | 18             | 27              | J3               | 0   | DIG          | UART6 Transmit Output                    |

| USBID        | _              | —               | —                | I   | ST           | USB OTG ID Input                         |

| USBOEN       | _              | _               | _                | 0   | DIG          | USB Output Enable (active-low)           |

| USBOEN       | TTL input buff | <u> </u>        | —                | 0   |              | USB Output Enable (active-low)           |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

|              | Pir            | n/Pad Num          | ber                          |     |              |                                                            |

|--------------|----------------|--------------------|------------------------------|-----|--------------|------------------------------------------------------------|

| Pin Function | 64-Pin<br>TQFP | 100-Pin<br>TQFP    | 121-Pin<br>TFBGA             | I/O | Input Buffer | Description                                                |

| VBAT         | 57             | 86                 | A7                           | Р   | —            | Backup Battery                                             |

| VBUS         | —              | _                  | _                            | Р   | —            | VBUS Supply                                                |

| VCAP         | 56             | 85                 | B7                           | I/O | —            | External Filter Capacitor Connection (regulator enabled)   |

| Vdd          | 10,26,38       | 2,16,37,<br>46,62  | C2,G5,H6,<br>K8,F8,E7        | Р   | —            | Positive Supply for Peripheral Digital Logic and I/O Pins  |

| Vdd          | _              |                    | D6                           | Р   | _            |                                                            |

| VLCAP1       | 5              | 11                 | F4                           | 0   | ANA          | LCD Drive Charge Pump Capacitor Inputs                     |

| VLCAP2       | 6              | 12                 | F2                           | 0   | ANA          |                                                            |

| VREF+        | 16             | 25,29              | K2,K3                        | I   | ANA          | Comparator and A/D Reference Voltage (high)<br>Input       |

| VREF-        | 15             | 24,28              | K1,L2                        | Ι   | ANA          | Comparator and A/D Reference Voltage (low)<br>Input        |

| Vss          | 9,25,41        | 15,36,45,<br>65,75 | F5,G6,G7,<br>F10,D10,<br>B10 | Р   | —            | Ground Reference for Peripheral Digital Logic and I/O Pins |

| Vss          | —              |                    | C6                           | Р   | —            | 1                                                          |

| VUSB3V3      | —              | —                  | —                            | Р   | _            | 3.3V VUSB                                                  |

#### TABLE 1-4: PIC24FJ256GA412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

#### **Pin/Pad Number Pin Function** I/O Input Buffer Description 64-Pin 100-Pin 121-Pin TQFP TQFP TFBGA SEG0 4 10 E3 0 ANA LCD Driver Segment Outputs SEG1 ANA 8 14 F3 0 SEG2 11 20 H1 0 ANA 0 SEG3 12 21 H2 ANA SEG4 13 22 J1 0 ANA 0 SEG5 14 23 J2 ANA SEG6 15 24 K1 0 ANA SEG7 16 25 K2 0 ANA SEG8 29 43 K7 ANA 0 SEG9 30 44 L8 0 ANA SEG10 31 49 L10 ANA 0 SEG11 32 50 L11 0 ANA SEG12 33 51 K10 0 ANA SEG13 42 68 E9 0 ANA SEG14 E10 43 69 0 ANA SEG15 44 70 D11 0 ANA 71 C11 0 SEG16 45 ANA SEG17 46 72 D9 0 ANA SEG18 27 41 J7 0 ANA L7 SEG19 28 42 0 ANA SEG20 49 76 A11 0 ANA SEG21 50 77 A10 0 ANA SEG22 51 78 B9 0 ANA SEG23 52 81 C8 0 ANA SEG24 53 82 B8 0 ANA SEG25 54 83 D7 0 ANA SEG26 55 84 C7 0 ANA SEG27 B6 0 58 87 ANA SEG28 \_\_\_\_ 61 G9 0 ANA 23 SEG29 H5 0 ANA 34 SEG30 22 33 L4 0 ANA 0 SEG31 21 32 K4 ANA SEG32 D1 0 ANA \_\_\_\_ 6 SEG33 8 E2 0 ANA \_\_\_\_ SEG34 18 G1 0 ANA \_\_\_\_ SEG35 19 G2 0 ANA SEG36 28 L2 0 ANA SEG37 29 K3 0 ANA \_\_\_\_ SEG38 47 L9 0 ANA SEG39 \_\_\_\_ 48 K9 0 ANA SEG40 52 K11 0 ANA

#### TABLE 1-5: PIC24FJ256GB412 FAMILY PINOUT DESCRIPTION (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog-level input/output DIG = Digital input/output SMB = SMBus ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated transceiver

#### REGISTER 3-2: CORCON: CPU CORE CONTROL REGISTER

| U-0     | U-0 | U-0           | U-0 | U-0                 | U-0 | U-0 | U-0   |

|---------|-----|---------------|-----|---------------------|-----|-----|-------|

| —       | —   | —             | —   | —                   | _   | —   | —     |

| bit 15  |     |               |     |                     |     |     | bit 8 |

|         |     |               |     |                     |     |     |       |

| U-0     | U-0 | U-0           | U-0 | R/C-0               | r-1 | U-0 | U-0   |

| —       | —   | —             | —   | IPL3 <sup>(1)</sup> | —   | —   | —     |

| bit 7   |     |               |     |                     |     |     | bit 0 |

|         |     |               |     |                     |     |     |       |

| Legend: |     | C = Clearable | bit | r = Reserved I      | bit |     |       |

| Legena:           | C = Clearable bit | r = Reserved bit           |                    |

|-------------------|-------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-1 for bit description.

#### 5.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction. In addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- Source and destination (SFRs and data RAM)

- · Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (Fixed Address or Address Blocks with or without Address Increment/Decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

#### 5.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 07FFh) or the data RAM space (0800h to FFFFh) can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 5-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

#### 5.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-size transactions. When byte-size transactions are chosen, the LSb of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

#### 5.1.3 TRIGGER SOURCE

The DMA Controller can use 63 of the device's interrupt sources to initiate a transaction. The DMA trigger sources occur in reverse order than their natural interrupt priority and are shown in Table 5-1. Since the source and destination addresses for any transaction can be programmed independently of the trigger source, the DMA Controller can use any trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

#### 5.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each trigger.

- One-Shot: A single transaction occurs for each trigger.

- Continuous: A series of back-to-back transactions occur for each trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per trigger, until the DMA channel is disabled.

All transfer modes allow the option to have the source and destination addresses, and counter value, automatically reloaded after the completion of a transaction; Repeated mode transfers do this automatically.

#### 5.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- · Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range of source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA-capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

For PIC24FJ256GA412/GB412 family devices, the 12-bit A/D Converter module is the only PIA-capable peripheral. Details for its use in PIA mode are provided in **Section 27.0 "12-Bit A/D Converter with Threshold Detect"**.

| U-0                                   | R/W-1                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                         | U-0                                                               | R/W-1            | R/W-0           | R/W-0   |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-----------------|---------|

| 0-0                                   | T4IP2                                                                                                                                                                                                      | T4IP1                                                                                                                                                                                                                                                                        | T4IP0                                                                                                                                                         | 0-0                                                               | OC4IP2           | OC4IP1          | OC4IP0  |

| <br>bit 15                            | 1411 2                                                                                                                                                                                                     | 1711 1                                                                                                                                                                                                                                                                       | 1411 0                                                                                                                                                        |                                                                   | 004112           | 004111          | bit     |

|                                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 |         |

| U-0                                   | R/W-1                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                         | U-0                                                               | R/W-1            | R/W-0           | R/W-0   |

| —                                     | OC3IP2                                                                                                                                                                                                     | OC3IP1                                                                                                                                                                                                                                                                       | OC3IP0                                                                                                                                                        |                                                                   | DMA2IP2          | DMA2IP1         | DMA2IP0 |

| bit 7                                 |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 | bit     |

| Legend:                               |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 |         |

| R = Readab                            | ole bit                                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                                                                 | bit                                                                                                                                                           | U = Unimple                                                       | mented bit, read | d as '0'        |         |

| -n = Value a                          | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                             |                                                                                                                                                               | '0' = Bit is cl                                                   | eared            | x = Bit is unkr | iown    |

| hit 15                                | Unimplomon                                                                                                                                                                                                 | ted: Dood on '                                                                                                                                                                                                                                                               | <b>`</b>                                                                                                                                                      |                                                                   |                  |                 |         |

| bit 15<br>bit 14-12                   | -                                                                                                                                                                                                          | ted: Read as 'd<br>imer4 Interrupt                                                                                                                                                                                                                                           |                                                                                                                                                               |                                                                   |                  |                 |         |

| DIL 14-12                             |                                                                                                                                                                                                            | pt is Priority 7 (                                                                                                                                                                                                                                                           | •                                                                                                                                                             | v interrunt)                                                      |                  |                 |         |

|                                       | •                                                                                                                                                                                                          | prist nonty / (                                                                                                                                                                                                                                                              | ingricat priorit                                                                                                                                              | y mterrupt)                                                       |                  |                 |         |

|                                       | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 |         |

|                                       | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 |         |

|                                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                   |                  |                 |         |

|                                       |                                                                                                                                                                                                            | pt is Priority 1                                                                                                                                                                                                                                                             | ahlad                                                                                                                                                         |                                                                   |                  |                 |         |

| hit 11                                | 000 = Interru                                                                                                                                                                                              | pt source is dis                                                                                                                                                                                                                                                             |                                                                                                                                                               |                                                                   |                  |                 |         |

|                                       | 000 = Interru<br>Unimplemen                                                                                                                                                                                | pt source is dis<br>ted: Read as '(                                                                                                                                                                                                                                          | )'                                                                                                                                                            | Interrupt Drier                                                   | ty bita          |                 |         |

|                                       | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                                                                 | pt source is dis<br>ted: Read as '(<br>Output Compa                                                                                                                                                                                                                          | )'<br>Ire Channel 4                                                                                                                                           | •                                                                 | ty bits          |                 |         |

| bit 11<br>bit 10-8                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                                                                 | pt source is dis<br>ted: Read as '(                                                                                                                                                                                                                                          | )'<br>Ire Channel 4                                                                                                                                           | •                                                                 | ty bits          |                 |         |

|                                       | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                                                                 | pt source is dis<br>ted: Read as '(<br>Output Compa                                                                                                                                                                                                                          | )'<br>Ire Channel 4                                                                                                                                           | •                                                                 | ty bits          |                 |         |

|                                       | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>•                                                                                                                                           | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (                                                                                                                                                                                                    | )'<br>Ire Channel 4                                                                                                                                           | •                                                                 | ty bits          |                 |         |

|                                       | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru                                                                                                                                                | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                                                                                                                                | <sub>)</sub> ,<br>ire Channel 4<br>highest priorit <u>i</u>                                                                                                   | •                                                                 | ty bits          |                 |         |

| bit 10-8                              | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru                                                                                                                                                | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                                                                                                            | <sub>o</sub> ,<br>ire Channel 4<br>highest priority<br>abled                                                                                                  | •                                                                 | ty bits          |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen                                                                                                | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(                                                                                                                                         | <sup>D'</sup><br>ire Channel 4<br>highest priority<br>abled                                                                                                   | y interrupt)                                                      |                  |                 |         |

| bit 10-8                              | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                                                                 | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>Output Compa                                                                                                                         | <sup>)</sup><br>ire Channel 4<br>highest priority<br>abled<br>)<br>ire Channel 3                                                                              | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                                                                 | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(                                                                                                                                         | <sup>)</sup><br>ire Channel 4<br>highest priority<br>abled<br>)<br>ire Channel 3                                                                              | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:                                                                                 | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>Output Compa                                                                                                                         | <sup>)</sup><br>ire Channel 4<br>highest priority<br>abled<br>)<br>ire Channel 3                                                                              | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru                                                                | pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (                                                                                     | <sup>)</sup><br>ire Channel 4<br>highest priority<br>abled<br>)<br>ire Channel 3                                                                              | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru                                                                | pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                 | <sup>D'</sup><br>Ire Channel 4<br>highest priorit<br>abled<br>D'<br>Ire Channel 3<br>highest priorit                                                          | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4          | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru                                               | pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                             | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>D'<br>Ire Channel 3<br>highest priority                                                        | y interrupt)<br>Interrupt Priori                                  |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen                | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(                                        | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>highest priority<br>abled<br>D'                                                                | y interrupt)<br>Interrupt Priori<br>y interrupt)                  |                  |                 |         |

| bit 10-8<br>bit 7                     | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>DMA2IP<2:0:                  | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: DMA Channe                                                             | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>D'<br>Ire Channel 3<br>highest priority<br>abled<br>D'<br>el 2 Interrupt F                     | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>Priority bits |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>DMA2IP<2:0:                  | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(                                        | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>D'<br>Ire Channel 3<br>highest priority<br>abled<br>D'<br>el 2 Interrupt F                     | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>Priority bits |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>DMA2IP<2:0:                  | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: DMA Channe                                                             | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>D'<br>Ire Channel 3<br>highest priority<br>abled<br>D'<br>el 2 Interrupt F                     | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>Priority bits |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>001 = Interru<br>Unimplemen<br>DMA2IP<2:0:                  | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: DMA Channe                                                             | <sup>D'</sup><br>Ire Channel 4<br>highest priority<br>abled<br>D'<br>Ire Channel 3<br>highest priority<br>abled<br>D'<br>el 2 Interrupt F                     | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>Priority bits |                  |                 |         |

| bit 10-8<br>bit 7<br>bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interru<br>001 = Interru<br>Unimplemen<br>OC3IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>DMA2IP<2:0:<br>111 = Interru | pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '(<br>>: DMA Channe<br>pt is Priority 7 ( | <sup>b)</sup><br>Ire Channel 4<br>highest priority<br>abled<br>b)<br>Ire Channel 3<br>highest priority<br>abled<br>b)<br>el 2 Interrupt F<br>highest priority | y interrupt)<br>Interrupt Priori<br>y interrupt)<br>Priority bits |                  |                 |         |

#### REGISTER 8-28: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0              | R/W-1                                                                 | R/W-0                                                   | R/W-0                                                | U-0             | R/W-1                      | R/W-0           | R/W-0    |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|-----------------|----------------------------|-----------------|----------|--|--|--|--|--|--|--|

| _                | CCP1IP2                                                               | CCP1IP1                                                 | CCP1IP0                                              | —               | RTCIP2                     | RTCIP1          | RTCIP0   |  |  |  |  |  |  |  |

| oit 15           |                                                                       |                                                         |                                                      |                 |                            |                 | bit      |  |  |  |  |  |  |  |

| U-0              | R/W-1                                                                 | R/W-0                                                   | R/W-0                                                | U-0             | R/W-1                      | R/W-0           | R/W-0    |  |  |  |  |  |  |  |

|                  | DMA5IP2                                                               | DMA5IP1                                                 | DMA5IP0                                              |                 | SPI3RXIP2                  | SPI3RXIP1       | SPI3RXIP |  |  |  |  |  |  |  |

| bit 7            | Divition 2                                                            |                                                         | Division o                                           |                 |                            |                 | bit      |  |  |  |  |  |  |  |

| ~                |                                                                       |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

| Legend:          |                                                                       |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

| R = Readat       | ole bit                                                               | W = Writable                                            | bit                                                  | U = Unimple     | mented bit, read           | 1 as '0'        |          |  |  |  |  |  |  |  |

| -n = Value a     | at POR                                                                | '1' = Bit is set                                        |                                                      | '0' = Bit is cl | eared                      | x = Bit is unkr | iown     |  |  |  |  |  |  |  |

|                  |                                                                       |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 15           | Unimplemen                                                            | ted: Read as '                                          | י'                                                   |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 14-12        |                                                                       | MCCP1 Capt                                              | -                                                    | -               | ity bits                   |                 |          |  |  |  |  |  |  |  |

|                  | 111 = Interru                                                         | pt is Priority 7 (                                      | highest priority                                     | / interrupt)    |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | 001 = Interrupt is Priority 1                                         |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | 000 = Interru                                                         | pt source is dis                                        | abled                                                |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 11           | Unimplemen                                                            | ted: Read as '                                          | כי                                                   |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 10-8         | RTCIP<2:0>:                                                           | Real-Time Clo                                           | ck and Calend                                        | ar Interrupt Pi | riority bits               |                 |          |  |  |  |  |  |  |  |

|                  | 111 = Interru                                                         | pt is Priority 7 (                                      | highest priority                                     | / interrupt)    |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | 001 = Interru                                                         | pt is Priority 1                                        |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  |                                                                       | pt source is dis                                        | abled                                                |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 7            |                                                                       | ted: Read as '                                          |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

| bit 6-4          | -                                                                     | >: DMA Chann                                            |                                                      | riority bits    |                            |                 |          |  |  |  |  |  |  |  |

|                  |                                                                       | pt is Priority 7 (                                      | =                                                    | -               |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     | . , , ,                                                 |                                                      | • • •           |                            |                 |          |  |  |  |  |  |  |  |

|                  | •                                                                     |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | •<br>001 = Interrupt is Priority 1                                    |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  |                                                                       | pt is Phoney 1                                          | abled                                                |                 |                            |                 |          |  |  |  |  |  |  |  |

|                  | 000 - 1000                                                            |                                                         |                                                      |                 |                            |                 |          |  |  |  |  |  |  |  |

| hit 3            |                                                                       | -                                                       |                                                      |                 | Unimplemented: Read as '0' |                 |          |  |  |  |  |  |  |  |

|                  | Unimplemen                                                            | ted: Read as '                                          | כי                                                   | iority hits     |                            |                 |          |  |  |  |  |  |  |  |

|                  | Unimplemen<br>SPI3RXIP<2:                                             | ted: Read as '(<br>0>: SPI3 Recei                       | o'<br>ve Interrupt Pr                                | -               |                            |                 |          |  |  |  |  |  |  |  |

|                  | Unimplemen<br>SPI3RXIP<2:                                             | ted: Read as '                                          | o'<br>ve Interrupt Pr                                | -               |                            |                 |          |  |  |  |  |  |  |  |

| bit 3<br>bit 2-0 | Unimplemen<br>SPI3RXIP<2:                                             | ted: Read as '(<br>0>: SPI3 Recei                       | o'<br>ve Interrupt Pr                                | -               |                            |                 |          |  |  |  |  |  |  |  |

|                  | Unimplemen<br>SPI3RXIP<2:<br>111 = Interru<br>•<br>•                  | ted: Read as 'o<br>0>: SPI3 Recei<br>pt is Priority 7 ( | o'<br>ve Interrupt Pr                                | -               |                            |                 |          |  |  |  |  |  |  |  |

|                  | Unimplemen<br>SPI3RXIP<2:<br>111 = Interru<br>•<br>•<br>001 = Interru | ted: Read as 'o<br>0>: SPI3 Recei<br>pt is Priority 7 ( | <sup>)'</sup><br>ve Interrupt Pr<br>highest priority | -               |                            |                 |          |  |  |  |  |  |  |  |

#### REGISTER 8-37: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0          | U-0           | U-0                   | U-0               | U-0                                     | R/W-1            | R/W-0    | R/W-0  |

|--------------|---------------|-----------------------|-------------------|-----------------------------------------|------------------|----------|--------|

| _            | —             | —                     |                   | —                                       | FSTIP2           | FSTIP1   | FSTIP0 |

| bit 15       |               |                       |                   |                                         |                  |          | bit 8  |

|              |               |                       |                   |                                         |                  |          |        |

| U-0          | U-0           | U-0                   | U-0               | U-0                                     | U-0              | U-0      | U-0    |

| —            | —             | —                     | —                 | —                                       | —                | —        | —      |

| bit 7        |               |                       |                   |                                         |                  |          | bit 0  |

|              |               |                       |                   |                                         |                  |          |        |

| Legend:      |               |                       |                   |                                         |                  |          |        |

| R = Readab   | le bit        | W = Writable          | bit               | U = Unimplem                            | nented bit, read | l as '0' |        |

| -n = Value a | It POR        | '1' = Bit is set      |                   | '0' = Bit is cleared x = Bit is unknown |                  |          |        |

|              |               |                       |                   |                                         |                  |          |        |

| bit 15-11    | Unimplement   | ted: Read as '        | 0'                |                                         |                  |          |        |

| bit 10-8     | FSTIP<2:0>:   | FRC Self-Tune         | e Interrupt Prior | rity bits                               |                  |          |        |

|              | 111 = Interru | pt is Priority 7 (    | highest priority  | / interrupt)                            |                  |          |        |

|              | •             |                       |                   |                                         |                  |          |        |

|              | •             |                       |                   |                                         |                  |          |        |

|              | •             |                       |                   |                                         |                  |          |        |

|              | 001 = Interru |                       | ablad             |                                         |                  |          |        |

|              |               | pt source is dis      |                   |                                         |                  |          |        |

| bit 7-0      | Unimplement   | i ac heag <b>'hat</b> | ∩'                |                                         |                  |          |        |

|              | omplomon      |                       | 0                 |                                         |                  |          |        |

#### REGISTER 8-48: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

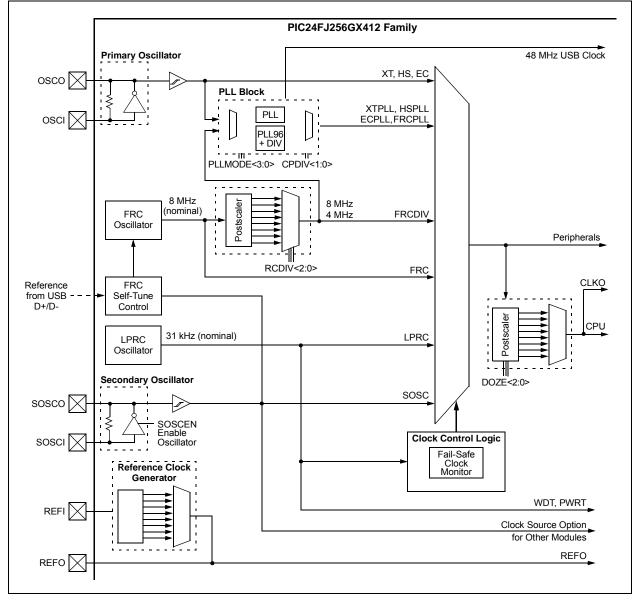

### 9.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Oscillator" (DS39700). The information in this data sheet supersedes the information in the FRM.

The oscillator system for PIC24FJ256GA412/GB412 family devices has the following features:

A Total of Four External and Internal Oscillator Options as Clock Sources, providing 11 Different Clock Modes

- An On-Chip PLL Block to provide a Wide Range of Precise Frequency Options for the System Clock, plus a Stable 48 MHz Clock for USB Devices

- Software-Controllable Switching between Various Clock Sources

- Software-Controllable Postscaler for Selective Clocking of CPU for System Power Savings

- A Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

- A Separate and Independently Configurable Reference Clock for Synchronizing External Hardware

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24FJ256GA412/GB412 FAMILY GENERAL CLOCK DIAGRAM

#### 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

#### 11.2 Configuring Analog Port Pins (ANSx)