Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b/12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

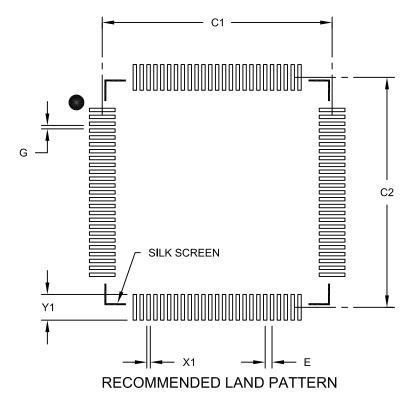

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb406t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | Mem                | nory            |      | Ana                | log P      | eriphe      | erals |           |                  | Digita    | al Per           | ipher | als |           |     |         |               | els)                    | L<br>L            |

|-----------------|--------------------|-----------------|------|--------------------|------------|-------------|-------|-----------|------------------|-----------|------------------|-------|-----|-----------|-----|---------|---------------|-------------------------|-------------------|

| Device          | Program<br>(bytes) | Data<br>(bytes) | Pins | 10/12-Bit A/D (ch) | 10-Bit DAC | Comparators | CTMU  | MCCP/SCCP | 16/32-Bit Timers | NWM-DO/DI | I <sup>2</sup> C | IdS   |     | dSdJ/dWd3 | CLC | DIO ASU | Crypto Engine | LCD Controller (pixels) | Deep Sleep + VBAT |

| PIC24FJ256GA412 | 256K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Y                 |

| PIC24FJ256GA410 | 256K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Υ                 |

| PIC24FJ256GA406 | 256K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Υ             | 248                     | Y                 |

| PIC24FJ128GA412 | 128K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Υ                 |

| PIC24FJ128GA410 | 128K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Υ                 |

| PIC24FJ128GA406 | 128K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 248                     | Υ                 |

| PIC24FJ64GA412  | 64K                | 8K              | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 512                     | Υ                 |

| PIC24FJ64GA410  | 64K                | 8K              | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Ν       | Y             | 480                     | Y                 |

| PIC24FJ64GA406  | 64K                | 8K              | 64   | 16                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Ν       | Υ             | 248                     | Υ                 |

| PIC24FJ256GB412 | 256K               | 16K             | 121  | 24                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Υ       | Υ             | 512                     | Υ                 |

| PIC24FJ256GB410 | 256K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 480                     | Y                 |

| PIC24FJ256GB406 | 256K               | 16K             | 64   | 16                 | 1          | 3           | Υ     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Υ       | Υ             | 240                     | Υ                 |

| PIC24FJ128GB412 | 128K               | 16K             | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 512                     | Υ                 |

| PIC24FJ128GB410 | 128K               | 16K             | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Υ       | Υ             | 480                     | Y                 |

| PIC24FJ128GB406 | 128K               | 16K             | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Υ       | Υ             | 240                     | Y                 |

| PIC24FJ64GB412  | 64K                | 8K              | 121  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 512                     | Y                 |

| PIC24FJ64GB410  | 64K                | 8K              | 100  | 24                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Υ         | 4   | Y       | Y             | 480                     | Y                 |

| PIC24FJ64GB406  | 64K                | 8K              | 64   | 16                 | 1          | 3           | Y     | 1/6       | 31/15            | 6/6       | 3                | 4     | 6   | Y         | 4   | Y       | Y             | 240                     | Y                 |

# **Peripheral Features**

- LCD Display Controller:

- Up to 64 Segments by 8 Commons

- Internal charge pump and low-power, internal resistor biasing

Operation in Sleep mode

- Up to Five External Interrupt Sources

- Peripheral Pin Select (PPS); allows Independent I/O Mapping of Many Peripherals

- Six-Channel DMA Supports All Peripheral modules:

Minimizes CPU overhead and increases data throughput

- Five 16-Bit Timers/Counters with Prescalers:

- Can be paired as 32-bit timers/counters

- Using a combination of Timer, CCP, IC and OC Timers, the Device can be Configured to use up to 31 16-Bit Timers, and up to 15 32-Bit Timers

- Six Input Capture modules, each with a Dedicated

16-Bit Timer

- Six Output Compare/PWM modules, each with a Dedicated 16-Bit Timer

- Six Single Output CCPs (SCCP) and One Multiple Output CCP (MCCP) modules:

- Independent 16/32-bit time base for each module

- Internal time base and Period registers

- Legacy PIC24F Capture and Compare modes (16 and 32-bit)

- Special variable frequency pulse and Brushless DC Motor (BDCM) Output modes

- Enhanced Parallel Master/Slave Port (EPMP/EPSP)

- Hardware Real-Time Clock/Calendar (RTCC) with Timestamping:

- Tamper detection with timestamping feature and tamper pin

- Runs in Deep Sleep and VBAT modes

- Four 3-Wire/4-Wire SPI modules (support 4 Frame modes) with 8-Level FIFO Buffer

- Three I<sup>2</sup>C modules support Multi-Master/Slave mode and 7-Bit/10-Bit Addressing

- Six UART modules:

- Support RS-485, RS-232 and LIN/J2602

- On-chip hardware encoder/decoder for IrDA<sup>®</sup>

- Auto-wake-up on Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Programmable 32-Bit Cyclic Redundancy Check (CRC) Generator

- Four Configurable Logic Cells (CLCs):

- Two inputs and one output, all mappable to peripherals or I/O pins

- AND/OR/XOR logic and D/JK flip-flop functions

- High-Current Sink/Source (18 mA/18 mA) on All I/O Pins

- Configurable Open-Drain Outputs on Digital I/O Pins

- 5.5V Tolerant Inputs on Multiple I/O Pins

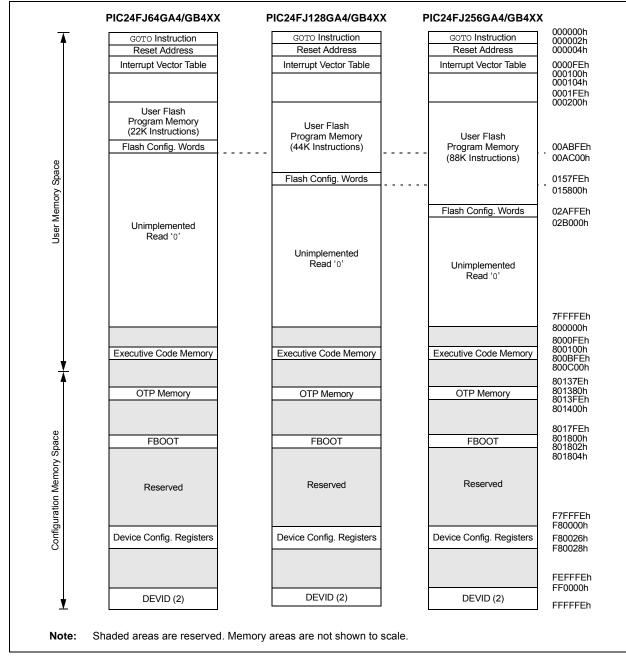

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space (DS) during code execution.

## 4.1 **Program Memory Space**

The program address memory space of the PIC24FJ256GA412/GB412 family devices is 4M instructions. The space is addressable by a 24-bit value

derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.4** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for PIC24FJ256GA412/GB412 family devices are shown in Figure 4-1.

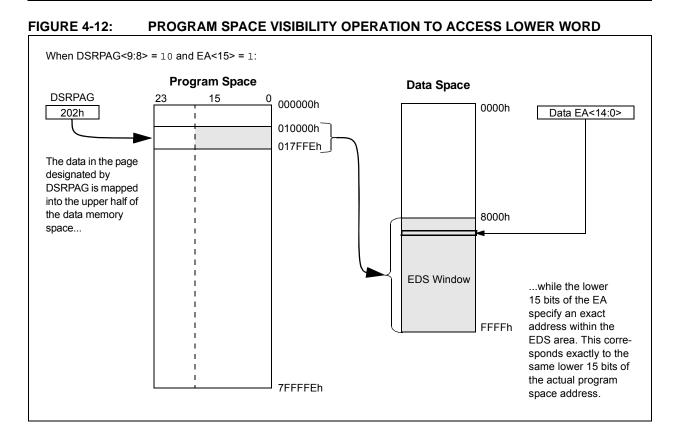

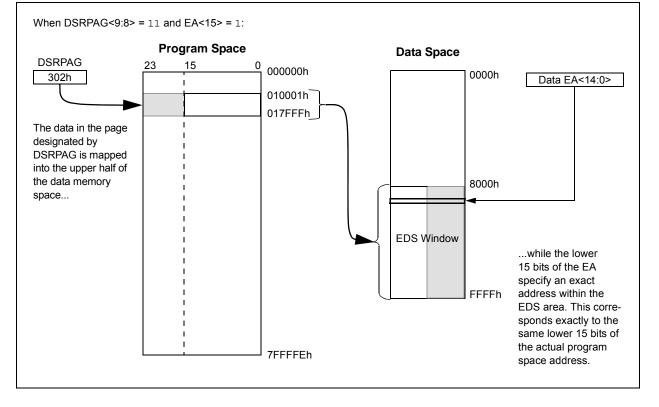

### FIGURE 4-13: PROGRAM SPACE VISIBILITY OPERATION TO ACCESS UPPER WORD

### REGISTER 8-5: INTCON4: INTERRUPT CONTROL REGISTER 4

|            | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit | _      | —   |     | —   | —   | —   | —   | —     |

|            | bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HSC |

|-------|-----|-----|-----|-----|-----|-----|------------|

| —     | —   | —   | —   | —   |     | _   | SGHT       |

| bit 7 |     |     |     |     |     |     | bit 0      |

| Legend:           | HSC = Hardware Settable/0 | Clearable bit              |                    |

|-------------------|---------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared       | x = Bit is unknown |

### bit 15-1 Unimplemented: Read as '0'

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = A software generated hard trap has occurred

0 = No software generated hard trap has occurred

### REGISTER 8-21: IEC7: INTERRUPT ENABLE CONTROL REGISTER 7

| U-0                                | U-0                              | U-0                                      | U-0               | U-0          | U-0                | U-0      | U-0    |  |  |  |  |

|------------------------------------|----------------------------------|------------------------------------------|-------------------|--------------|--------------------|----------|--------|--|--|--|--|

| —                                  | —                                | —                                        | —                 | _            |                    | —        | —      |  |  |  |  |

| bit 15                             |                                  |                                          |                   |              |                    |          | bit 8  |  |  |  |  |

|                                    |                                  |                                          |                   |              |                    |          |        |  |  |  |  |

| U-0                                | U-0                              | R/W-0                                    | R/W-0             | R/W-0        | R/W-0              | R/W-0    | R/W-0  |  |  |  |  |

|                                    |                                  | JTAGIE                                   | U6ERIE            | U6TXIE       | U6RXIE             | U5ERIE   | U5TXIE |  |  |  |  |

| bit 7                              |                                  |                                          |                   |              |                    |          | bit 0  |  |  |  |  |

|                                    |                                  |                                          |                   |              |                    |          |        |  |  |  |  |

| Legend:                            |                                  |                                          |                   |              |                    |          |        |  |  |  |  |

| R = Readal                         | ble bit                          | W = Writable                             | bit               | U = Unimplem | nented bit, read   | l as '0' |        |  |  |  |  |

| -n = Value at POR '1' = Bit is set |                                  |                                          | '0' = Bit is clea | ared         | x = Bit is unknown |          |        |  |  |  |  |

|                                    |                                  |                                          |                   |              |                    |          |        |  |  |  |  |

| bit 15-6                           | Unimplemen                       | ted: Read as '                           | כי                |              |                    |          |        |  |  |  |  |

| bit 5                              | JTAGIE: JAT                      | G Interrupt Ena                          | ble bit           |              |                    |          |        |  |  |  |  |

|                                    | 1 = Interrupt request is enabled |                                          |                   |              |                    |          |        |  |  |  |  |

|                                    | 0 = Interrupt                    | request is not e                         | enabled           |              |                    |          |        |  |  |  |  |

| bit 4                              | U6ERIE: UAF                      | U6ERIE: UART6 Error Interrupt Enable bit |                   |              |                    |          |        |  |  |  |  |

|                                    |                                  | request has oc                           |                   |              |                    |          |        |  |  |  |  |

|                                    | 0 = Interrupt                    | request has no                           | t occurred        |              |                    |          |        |  |  |  |  |

| bit 3                              |                                  | T6 Transmitter                           | •                 | ole bit      |                    |          |        |  |  |  |  |

|                                    |                                  | request has oc                           |                   |              |                    |          |        |  |  |  |  |

|                                    |                                  | request has no                           |                   |              |                    |          |        |  |  |  |  |

| bit 2                              |                                  | RT6 Receiver Ir                          | •                 | bit          |                    |          |        |  |  |  |  |

|                                    | 1 = Interrupt                    | request has oc                           | curred            |              |                    |          |        |  |  |  |  |

- 0 = Interrupt request has not occurred

- bit 1 U5ERIE: UART5 Error Interrupt Enable bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 U5TXIE: UART5 Transmitter Interrupt Enable bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER 8-35: IPC13: INTERRUPT PRIORITY CONTRO | L REGISTER 13 |

|-------------------------------------------------|---------------|

|-------------------------------------------------|---------------|

| U-0          | R/W-1                                                      | R/W-0                                                      | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|------------------------------------------------------------|------------------------------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| _            | CRYDNIP2                                                   | CRYDNIP21                                                  | CRYDNIP0         |                   | INT4IP2          | INT4IP1         | INT4IP0 |  |  |  |  |  |

| oit 15       |                                                            |                                                            |                  |                   |                  |                 | bit 8   |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                      | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

|              | INT3IP2                                                    | INT3IP1                                                    | INT3IP0          | —                 |                  | _               | _       |  |  |  |  |  |

| bit 7        |                                                            |                                                            |                  |                   |                  |                 | bit C   |  |  |  |  |  |

| Legend:      |                                                            |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable b                                             | bit              | U = Unimplen      | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                                           |                  | '0' = Bit is clea |                  | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                            |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 15       | Unimplemen                                                 | ted: Read as '0                                            | ,                |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12    | -                                                          | 0>: Cryptograph                                            |                  | one Interrupt F   | Priority bits    |                 |         |  |  |  |  |  |

|              |                                                            | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                              | pt is Priority 1<br>pt source is disa                      | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 11       |                                                            | ited: Read as '0                                           |                  |                   |                  |                 |         |  |  |  |  |  |

|              | -                                                          |                                                            |                  | ita               |                  |                 |         |  |  |  |  |  |

| bit 10-8     |                                                            | External Interro                                           |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          | pt is Priority 7 (I                                        | nignest priority | interrupt)        |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interru                                              |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 000 = Interru                                              | pt source is disa                                          | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | Unimplemen                                                 | ted: Read as '0                                            | ,                |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      | INT3IP<2:0>:                                               | External Interro                                           | upt 3 Priority b | its               |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt) |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                          |                                                            |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interru                                         | nt is Priority 1                                           |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                                                            | pt source is disa                                          | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 3-0      |                                                            | ted: Read as '0                                            |                  |                   |                  |                 |         |  |  |  |  |  |

| 510-0        | Sumblemen                                                  | icu. Neau as u                                             |                  |                   |                  |                 |         |  |  |  |  |  |

|  | REGISTER 8-43: | <b>IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21</b> |

|--|----------------|------------------------------------------------------|

|--|----------------|------------------------------------------------------|

| U-0     | R/W-1     | R/W-0     | R/W-0     | U-0 | R/W-1     | R/W-0     | R/W-0     |

|---------|-----------|-----------|-----------|-----|-----------|-----------|-----------|

| _       | U4ERIP2   | U4ERIP1   | U4ERIP0   | _   | USB1IP2   | USB1IP1   | USB1IP0   |

| bit 15  |           |           | •         |     | -         |           | bit 8     |

|         |           |           |           |     |           |           |           |

| U-0     | R/W-1     | R/W-0     | R/W-0     | U-0 | R/W-1     | R/W-0     | R/W-0     |

| _       | I2C2BCIP2 | I2C2BCIP1 | I2C2BCIP0 | _   | I2C1BCIP2 | I2C1BCIP1 | I2C1BCIP0 |

| bit 7   |           |           |           |     |           | •         | bit 0     |

|         |           |           |           |     |           |           |           |

| Legend: |           |           |           |     |           |           |           |

| Legena:      |                 |                                  |                       |                    |

|--------------|-----------------|----------------------------------|-----------------------|--------------------|

| R = Readab   | ole bit         | W = Writable bit                 | U = Unimplemented bit | , read as '0'      |

| -n = Value a | at POR          | '1' = Bit is set                 | '0' = Bit is cleared  | x = Bit is unknown |

|              |                 |                                  |                       |                    |

| bit 15       | Unimple         | mented: Read as '0'              |                       |                    |

| bit 14-12    | U4ERIP•         | <2:0>: UART4 Error Interrupt     | Priority bits         |                    |

|              | 111 <b>= In</b> | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              | 000 <b>= In</b> | terrupt source is disabled       |                       |                    |

| bit 11       | Unimple         | mented: Read as '0'              |                       |                    |

| bit 10-8     |                 | <2:0>: USB1 (USB OTG) Inte       |                       |                    |

|              | 111 <b>= In</b> | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              |                 | terrupt source is disabled       |                       |                    |

| bit 7        | -               | mented: Read as '0'              |                       |                    |

| bit 6-4      |                 | P<2:0>: I2C2 Bus Collision Ir    |                       |                    |

|              | 111 = In        | terrupt is Priority 7 (highest p | riority interrupt)    |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

| 1.1.0        |                 | terrupt source is disabled       |                       |                    |

| bit 3        | -               | mented: Read as '0'              |                       |                    |

| bit 2-0      |                 | P<2:0>: I2C1 Bus Collision In    |                       |                    |

|              | •               | terrupt is Priority 7 (highest p | nonty interrupt)      |                    |

|              | •               |                                  |                       |                    |

|              | •               |                                  |                       |                    |

|              |                 | terrupt is Priority 1            |                       |                    |

|              | $000 = \ln 3$   | terrupt source is disabled       |                       |                    |

|              |                 |                                  |                       |                    |

|              |                 |                                  |                       |                    |

| R/W-0         | R/W-0                                                                                                                                 | R/W-1                              | R/W-1           | R/W-0                | R/W-0           | R/W-0                       | R/W-1     |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|----------------------|-----------------|-----------------------------|-----------|--|--|--|--|

| ROI           | DOZE2                                                                                                                                 | DOZE1                              | DOZE0           | DOZEN <sup>(1)</sup> | RCDIV2          | RCDIV1                      | RCDIV0    |  |  |  |  |

| bit 15        |                                                                                                                                       |                                    |                 |                      |                 | •                           | bit       |  |  |  |  |

|               |                                                                                                                                       |                                    |                 |                      |                 |                             |           |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                 | R/W-0                              | U-0             | U-0                  | U-0             | U-0                         | U-0       |  |  |  |  |

| CPDIV1        | CPDIV0                                                                                                                                | PLLEN                              |                 | —                    |                 | _                           | —         |  |  |  |  |

| bit 7         |                                                                                                                                       |                                    |                 |                      |                 |                             | bit       |  |  |  |  |

| Legend:       |                                                                                                                                       |                                    |                 |                      |                 |                             |           |  |  |  |  |

| R = Readable  | e bit                                                                                                                                 | W = Writable                       | bit             | U = Unimplem         | ented bit, read | l as '0'                    |           |  |  |  |  |

| -n = Value at | POR                                                                                                                                   | '1' = Bit is set                   |                 | '0' = Bit is clea    | ired            | x = Bit is unkr             | nown      |  |  |  |  |

| bit 1E        |                                                                                                                                       | on Interrupt hi                    |                 |                      |                 |                             |           |  |  |  |  |

| bit 15        |                                                                                                                                       | on Interrupt bi                    |                 | et the CPU perip     | oheral clock ra | tio to 1·1                  |           |  |  |  |  |

|               |                                                                                                                                       | have no effect                     |                 |                      |                 |                             |           |  |  |  |  |

| bit 14-12     | DOZE<2:0>:                                                                                                                            | CPU Periphera                      | I Clock Ratio   | Select bits          |                 |                             |           |  |  |  |  |

|               | 111 = <b>1</b> : <b>128</b>                                                                                                           |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 110 = 1:64                                                                                                                            |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 101 = 1:32<br>100 = 1:16                                                                                                              |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 100 = 1.16<br>011 = 1.8 (default)                                                                                                     |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 010 = 1:4                                                                                                                             |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 001 = 1:2                                                                                                                             |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 000 = 1:1                                                                                                                             | (1)                                |                 |                      |                 |                             |           |  |  |  |  |

| bit 11        | DOZEN: Doze                                                                                                                           |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               |                                                                                                                                       | 0> bits specify<br>pheral clock ra |                 | oheral clock ratio   | )               |                             |           |  |  |  |  |

| bit 10-8      |                                                                                                                                       | FRC Postscal                       |                 |                      |                 |                             |           |  |  |  |  |

|               | 111 <b>= 31.25 k</b>                                                                                                                  | Hz (divide-by-2                    | 256)            |                      |                 |                             |           |  |  |  |  |

|               | 110 = 125  kHz (divide-by-64)                                                                                                         |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 101 = 250 kHz (divide-by-32)                                                                                                          |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 100 = 500 kHz (divide-by-16)                                                                                                          |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 011 = 1 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-4)                                                                                |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 010 = 2  MHz (divide-by-4)<br>001 = 4  MHz (divide-by-2) (default)                                                                    |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 000 <b>= 8 MHz</b>                                                                                                                    | • • • •                            | ,               |                      |                 |                             |           |  |  |  |  |

| bit 7-6       | CPDIV<1:0>:                                                                                                                           | System Clock                       | Select bits (po | ostscaler select f   | rom fast PLL b  | oranch)                     |           |  |  |  |  |

|               | <b>CPDIV&lt;1:0&gt;:</b> System Clock Select bits (postscaler select from fast PLL branch)<br>11 = 4 MHz (divide-by-8) <sup>(2)</sup> |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | $10 = 8 \text{ MHz} (divide-by-4)^{(2)}$                                                                                              |                                    |                 |                      |                 |                             |           |  |  |  |  |

|               | 01 = 16 MHz (divide-by-2)<br>00 = 32 MHz (divide-by-1)                                                                                |                                    |                 |                      |                 |                             |           |  |  |  |  |

| L:1 F         |                                                                                                                                       | • • •                              |                 |                      |                 |                             |           |  |  |  |  |

| bit 5         |                                                                                                                                       | PLL Enable bit                     | L               |                      |                 |                             |           |  |  |  |  |

|               | 1 = PLL is alw<br>0 = PLL is onl                                                                                                      |                                    | a PLL Oscillat  | or mode is seled     | ted (OSCCON     | <b> &lt;14:12&gt; =</b> 011 | L or 001) |  |  |  |  |

| bit 4-0       |                                                                                                                                       | ted: Read as '                     |                 |                      |                 |                             | ,         |  |  |  |  |

|               |                                                                                                                                       |                                    |                 |                      | interrupt occu  |                             |           |  |  |  |  |

2: This setting is not allowed while the USB module is enabled.

| U-0             | U-0           | R/W-0            | R/W-0          | R/W-0                                   | R/W-0            | R/W-0           | R/W-0          |

|-----------------|---------------|------------------|----------------|-----------------------------------------|------------------|-----------------|----------------|

| —               | —             | RP1R5            | RP1R4          | RP1R3                                   | RP1R2            | RP1R1           | RP1R0          |

| bit 15          |               |                  |                |                                         |                  |                 | bit 8          |

|                 |               |                  |                |                                         |                  |                 |                |

| U-0             | U-0           | R/W-0            | R/W-0          | R/W-0                                   | R/W-0            | R/W-0           | R/W-0          |

| —               | —             | RP0R5            | RP0R4          | RP0R3                                   | RP0R2            | RP0R1           | RP0R0          |

| bit 7           |               |                  |                |                                         |                  |                 | bit 0          |

|                 |               |                  |                |                                         |                  |                 |                |

| Legend:         |               |                  |                |                                         |                  |                 |                |

| R = Readable    | bit           | W = Writable     | bit            | U = Unimplem                            | nented bit, read | d as '0'        |                |

| -n = Value at F | POR           | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                  |                 |                |

|                 |               |                  |                |                                         |                  |                 |                |

| bit 15-14       | Unimplement   | ted: Read as 'd  | )'             |                                         |                  |                 |                |

| bit 13-8        | RP1R<5:0>: F  | RP1 Output Pir   | n Mapping bits |                                         |                  |                 |                |

|                 | Peripheral Ou | tput Number n    | is assigned to | pin, RP1 (see T                         | able 11-12 for   | peripheral func | tion numbers). |

### REGISTER 11-23: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| bit 5-0 | RP0R<5:0>: RP0 Output Pin Mapping bits                                                                |

|---------|-------------------------------------------------------------------------------------------------------|

|         | Peripheral Output Number n is assigned to pin, RP0 (see Table 11-12 for peripheral function numbers). |

# REGISTER 11-24: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cleared x =   |       | x = Bit is unki | = Bit is unknown |  |

|-------------------|-------|------------------|-------|----------------------------|-------|-----------------|------------------|--|

| R = Readable      | e bit | W = Writable bit |       | U = Unimplemented bit, rea |       | ead as '0'      |                  |  |

| Legend:           |       |                  |       |                            |       |                 |                  |  |

|                   |       |                  |       |                            |       |                 |                  |  |

| bit 7             |       |                  |       |                            | •     |                 | bit              |  |

| _                 | _     | RP2R5            | RP2R4 | RP2R3                      | RP2R2 | RP2R1           | RP2R0            |  |

| U-0               | U-0   | R/W-0            | R/W-0 | R/W-0                      | R/W-0 | R/W-0           | R/W-0            |  |

|                   |       |                  |       |                            |       |                 |                  |  |

| bit 15            |       |                  |       |                            |       |                 | bit              |  |

|                   | _     | RP3R5            | RP3R4 | RP3R3                      | RP3R2 | RP3R1           | RP3R0            |  |

| U-0               | U-0   | R/W-0            | R/W-0 | R/W-0                      | R/W-0 | R/W-0           | R/W-0            |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

Unimplemented: Read as '0'

Peripheral Output Number n is assigned to pin, RP3 (see Table 11-12 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP2R<5:0>:** RP2 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP2 (see Table 11-12 for peripheral function numbers).

bit 7-6

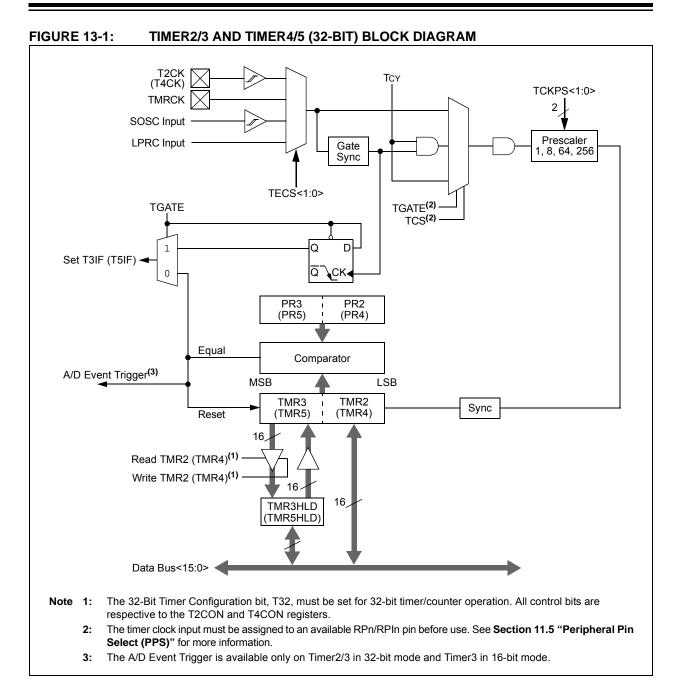

# **REGISTER 13-1:** TxCON: TIMER2 AND TIMER4 CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 3 **T32:** 32-Bit Timer Mode Select bit<sup>(3)</sup>

- 1 = Timerx and Timery form a single 32-bit timer

- 0 = Timerx and Timery act as two 16-bit timers

- In 32-bit mode, T3CON control bits do not affect 32-bit timer operation.

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timerx Clock Source Select bit<sup>(2)</sup>

- 1 = Timer source is selected by TECS<1:0>0 = Internal clock (Fosc/2)

- bit 0 Unimplemented: Read as '0'

- **Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

- 2: If TCS = 1 and TECS<1:0> = x1, the selected external timer input (TMRCK or TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- **3:** In T4CON, the T45 bit is implemented instead of T32 to select 32-bit mode. In 32-bit mode, the T3CON or T5CON control bits do not affect 32-bit timer operation.

#### 20.7.1 USB OTG MODULE CONTROL REGISTERS

# REGISTER 20-3: U1OTGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | _   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                            |

|          | <ul> <li>1 = No plug is attached or a Type B cable has been plugged into the USB receptacle</li> <li>0 = A Type A plug has been plugged into the USB receptacle</li> </ul>                |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                   |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has not been stable for the previous 1 ms</li> </ul> |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_SESS_VLD (as defined in the "USB 2.0 OTG Specification") on the<br>A or B-device                                                                         |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                            |

| bit 2    | SESEND: B Session End Indicator bit                                                                                                                                                       |

|          | <ul> <li>1 = The VBUS voltage is below VB_SESS_END (as defined in the "USB 2.0 OTG Specification") on the<br/>B-device</li> </ul>                                                         |

|          | 0 = The VBUS voltage is above VB_SESS_END on the B-device                                                                                                                                 |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 0    | VBUSVD: A VBUS Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the "USB 2.0 OTG Specification") on the<br>A-device                                                                              |

|          | 0 = The VBUS voltage is below VA_VBUS_VLD on the A-device                                                                                                                                 |

|          |                                                                                                                                                                                           |

### REGISTER 20-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0                    | U-0                                                                              | U-0               | U-0                                 | U-0                               | U-0            | U-0             | U-0   |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------|-------------------|-------------------------------------|-----------------------------------|----------------|-----------------|-------|--|--|--|--|

| _                      | —                                                                                | —                 | —                                   | —                                 | —              | —               | _     |  |  |  |  |

| bit 15                 |                                                                                  |                   |                                     |                                   |                |                 | bit 8 |  |  |  |  |

|                        |                                                                                  |                   |                                     |                                   |                |                 |       |  |  |  |  |

| R/W-0                  | R/W-0                                                                            | U-0               | R/W-0                               | U-0                               | U-0            | R/W-0           | R/W-0 |  |  |  |  |

| UTEYE                  | UOEMON <sup>(1)</sup>                                                            | —                 | USBSIDL                             | —                                 | —              | PPB1            | PPB0  |  |  |  |  |

| bit 7                  |                                                                                  |                   |                                     |                                   |                |                 | bit   |  |  |  |  |

|                        |                                                                                  |                   |                                     |                                   |                |                 |       |  |  |  |  |

| Legend:<br>R = Readabl | le hit                                                                           | W = Writable      | hit                                 | U = Unimplerr                     | onted hit rea  | ad as 'O'       |       |  |  |  |  |

| -n = Value at          |                                                                                  | '1' = Bit is set  |                                     | $0^{\circ} = \text{Bit is clear}$ |                | x = Bit is unkr | 0.000 |  |  |  |  |

|                        | IFUR                                                                             | I – DILISSE       |                                     |                                   | areu           |                 | IOWIT |  |  |  |  |

| bit 15-8               | Unimplemen                                                                       | ted: Read as      | 0'                                  |                                   |                |                 |       |  |  |  |  |

| bit 7                  | •                                                                                |                   |                                     |                                   |                |                 |       |  |  |  |  |

| SIC 1                  | <b>UTEYE:</b> USB Eye Pattern Test Enable bit<br>1 = Eye pattern test is enabled |                   |                                     |                                   |                |                 |       |  |  |  |  |

|                        | • •                                                                              | ern test is disal |                                     |                                   |                |                 |       |  |  |  |  |

| bit 6                  | UOEMON: U                                                                        | SB OE Monito      | r Enable bit <sup>(1)</sup>         |                                   |                |                 |       |  |  |  |  |

|                        | $1 = \overline{OE} \text{ signa}$<br>$0 = \overline{OE} \text{ signa}$           |                   | dicates interval                    | s during which                    | the D+/D- line | es are driving  |       |  |  |  |  |

| bit 5                  | Unimplemen                                                                       | ted: Read as '    | 0'                                  |                                   |                |                 |       |  |  |  |  |

| bit 4                  | USBSIDL: US                                                                      | SB OTG Stop i     | n Idle Mode bit                     |                                   |                |                 |       |  |  |  |  |

|                        |                                                                                  |                   | peration when t<br>ation in Idle mo | he device enter<br>de             | rs Idle mode   |                 |       |  |  |  |  |

| bit 3-2                | Unimplemen                                                                       | ted: Read as '    | 0'                                  |                                   |                |                 |       |  |  |  |  |

| bit 1-0                | PPB<1:0>: Ping-Pong Buffers Configuration bits                                   |                   |                                     |                                   |                |                 |       |  |  |  |  |

|                        | 11 = Even/Odd Ping-Pong Buffers are enabled for Endpoints 1 to 15                |                   |                                     |                                   |                |                 |       |  |  |  |  |

|                        |                                                                                  |                   |                                     | abled for all end                 |                |                 |       |  |  |  |  |

|                        |                                                                                  |                   | Buffers are ena<br>Buffers are dis  | abled for OUT E<br>abled          | inapoint u     |                 |       |  |  |  |  |

|                        |                                                                                  | a ing i ong       |                                     |                                   |                |                 |       |  |  |  |  |

Note 1: This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

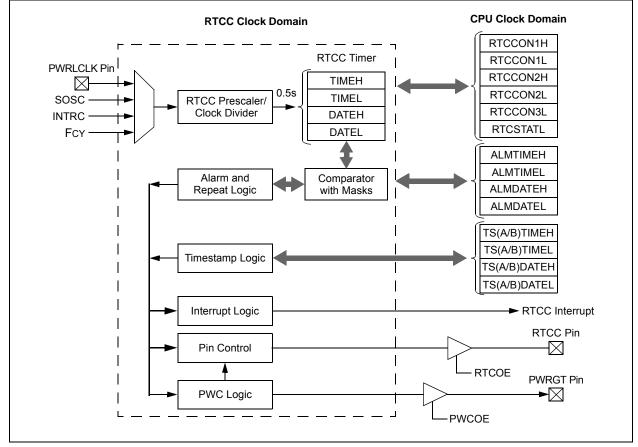

# 24.0 REAL-TIME CLOCK AND CALENDAR (RTCC) WITH TIMESTAMP

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "dsPIC33/PIC24 Family Reference Manual", "RTCC with Timestamp" (DS70005193). The information in this data sheet supersedes the information in the FRM.

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- Time (Hours, Minutes and Seconds) in 24-Hour (Military Time) Format

- Calendar (Weekday, Date, Month and Year)

- Year range from 2000 to 2099 with automatic Leap Year correction

- Alarm with Configurable Mask and Repeat

Options

- BCD Format for Compact Firmware

- Optimized for Low-Power Operation

- Multiple Clock Input Options, Including:

- 32.768 kHz crystal

- External Real-Time Clock (RTC)

- 50/60 Hz power line clock

- 31.25 kHz LPRC clock

- System clock, up to 32 MHz

- User Calibration with a Range of 2 ppm when using 32 kHz Source

- · Interrupt on Alarm and Timestamp Events

- Optional Timestamp Capture for Tamper Pin or Other Events

- User-Configurable Power Control with Dedicated Output Pin to Periodically Wake External Devices

# FIGURE 24-1: RTCC HIGH-LEVEL BLOCK DIAGRAM

### REGISTER 25-3: CRYSTAT: CRYPTOGRAPHIC STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-x, HSC <sup>(1)</sup> | R-0, HSC <sup>(1)</sup> | R/C-0, HS <sup>(2)</sup> | R/C-0, HS <sup>(2)</sup> | U-0 | R-0, HSC <sup>(1)</sup> | R-x, HSC <sup>(1)</sup>  | R-x, HSC <sup>(1)</sup>  |

|-------------------------|-------------------------|--------------------------|--------------------------|-----|-------------------------|--------------------------|--------------------------|

| CRYBSY <sup>(4)</sup>   | TXTABSY                 | CRYABRT <sup>(5)</sup>   | ROLLOVR                  | —   | MODFAIL <sup>(3)</sup>  | KEYFAIL <sup>(3,4)</sup> | PGMFAIL <sup>(3,4)</sup> |

| bit 7                   |                         |                          |                          |     |                         |                          | bit 0                    |

| Legend:           | C = Clearable bit          | HSC = Hardware Settable/C  | learable bit       |

|-------------------|----------------------------|----------------------------|--------------------|

| R = Readable bit  | HS = Hardware Settable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | <b>CRYBSY:</b> Cryptographic Engine Busy Status bit <sup>(1, 4)</sup>                                                                                                                                     |

|          | 1 = A cryptographic operation is in progress                                                                                                                                                              |

|          | 0 = No cryptographic operation is in progress                                                                                                                                                             |

| bit 6    | TXTABSY: CRYTXTA Busy Status bit <sup>(1)</sup>                                                                                                                                                           |

|          | 1 = The CRYTXTA register is busy and may not be written to                                                                                                                                                |

|          | 0 = The CRYTXTA is free and may be written to                                                                                                                                                             |

| bit 5    | CRYABRT: Cryptographic Operation Aborted Status bit <sup>(2,5)</sup>                                                                                                                                      |

|          | 1 = Last operation was aborted by clearing the CRYGO bit in software                                                                                                                                      |

|          | 0 = Last operation completed normally (CRYGO cleared in hardware)                                                                                                                                         |

| bit 4    | ROLLOVR: Counter Rollover Status bit <sup>(2)</sup>                                                                                                                                                       |

|          | 1 = The CRYTXTB counter rolled over on the last CTR mode operation; once set, this bit must be                                                                                                            |

|          | cleared by software before the CRYGO bit can be set again<br>0 = No rollover event has occurred                                                                                                           |

|          |                                                                                                                                                                                                           |

| bit 3    | Unimplemented: Read as '0'                                                                                                                                                                                |

| bit 2    | <b>MODFAIL:</b> Mode Configuration Fail Flag bit <sup>(1,3)</sup>                                                                                                                                         |

|          | 1 = Currently selected operating and Cipher mode configuration is invalid; the CRYWR bit cannot be                                                                                                        |

|          | set until a valid mode is selected (automatically cleared by hardware with any valid configuration)<br>0 = Currently selected operating and Cipher mode configurations are valid                          |

| bit 1    | <b>KEYFAIL:</b> Key Configuration Fail Status bit <sup>(1,3,4)</sup>                                                                                                                                      |

| DILI     | See Table 25-1 and Table 25-2 for invalid key configurations.                                                                                                                                             |

|          | 1 = Currently selected key and mode configurations are invalid; the CRYWR bit cannot be set until a                                                                                                       |

|          | valid mode is selected (automatically cleared by hardware with any valid configuration)                                                                                                                   |

|          | 0 = Currently selected configurations are valid                                                                                                                                                           |

| bit 0    | PGMFAIL: Key Storage/Configuration Program Fail Flag bit <sup>(1,3,4)</sup>                                                                                                                               |

|          | 1 = The page indicated by KEYPG<3:0> is reserved or locked; the CRYWR bit cannot be set and no                                                                                                            |

|          | programming operation can be started                                                                                                                                                                      |

|          | 0 = The page indicated by KEYPG<3:0> is available for programming                                                                                                                                         |

| Note 1:  | These bits are reset on system Resets or whenever the CRYMD bit (PMD8<0>) is set.                                                                                                                         |

| 2:       | These bits are reset on system Resets when the CRYMD bit is set or when CRYGO is cleared.                                                                                                                 |

| 3:       | These bits are functional even when the module is disabled (CRYON = 0); this allows mode configurations                                                                                                   |

|          | to be validated for compatibility before enabling the module.                                                                                                                                             |

| 4:       | These bits are automatically set during all OTP read operations, including the initial read at POR. Once the read is completed, the bit assumes the proper state that reflects the current configuration. |

5: If this bit is set, a cryptographic operation cannot be performed.

### REGISTER 27-8: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)

| -         -         -         CHH<25:24>(1)           bit 15         bit 8 | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0                |

|----------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-------|----------------------|

| bit 15 bit 8                                                               | _      | —   |     | —   | —   | —   | CHH<2 | 5:24> <sup>(1)</sup> |

|                                                                            | bit 15 |     |     |     |     |     |       | bit 8                |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|----------------------|-------|-------|-------|

|       |       |       | CHH<2 | 3:16> <sup>(1)</sup> |       |       |       |

| bit 7 |       |       |       |                      |       |       | bit 0 |

| Legend:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### Unimplemented: Read as '0' bit 15-10 bit 9-0 CHH<25:16>: A/D Compare Hit bits(1) If CM<1:0> = 11:

- 1 = A/D Result Buffer n has been written with data or a match has occurred

- 0 = A/D Result Buffer n has not been written with data

- For All Other Values of CM<1:0>:

1 = A match has occurred on A/D Result Channel n

0 = No match has occurred on A/D Result Channel n

### REGISTER 27-9: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|----------|-------|

|              |       |                  | CHF   | l<15:8>      |                  |          |       |

| bit 15       |       |                  |       |              |                  |          | bit 8 |

|              |       |                  |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|              |       |                  | CHI   | H<7:0>       |                  |          |       |

| bit 7        |       |                  |       |              |                  |          | bit 0 |

|              |       |                  |       |              |                  |          |       |

| Legend:      |       |                  |       |              |                  |          |       |

| R = Readable | bit   | W = Writable bit |       | U = Unimplen | nented bit, read | l as '0' |       |

'0' = Bit is cleared

| bit 15-0 | CHH<15:0>: A/D Compare Hit bits |  |

|----------|---------------------------------|--|

If CM<1:0> = 11:

-n = Value at POR

1 = A/D Result Buffer n has been written with data or a match has occurred

0 = A/D Result Buffer n has not been written with data

For All Other Values of CM<1:0>:

'1' = Bit is set

1 = A match has occurred on A/D Result Channel n