Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SPI, UART/USART, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, LVD, POR, PWM, WDT                           |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b; D/A 1x10b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb410t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR PIC24FJXXXGA412 (CONTINUED)

| Pin | Function                                              | Pin | Function                                          |

|-----|-------------------------------------------------------|-----|---------------------------------------------------|

| J1  | SEG4/AN3/C2INA/IOCB3/RB3                              | K7  | SEG8/AN14/RP14/CTED5/CTPLS/PMA1/PMALH/IOCB14/RB14 |

| J2  | SEG5/AN2/CTCMP/C2INB/RP13/CTED13/IOCB2/RB2            | K8  | VDD                                               |

| J3  | PGED2/SEG63/AN7/ <b>RP7</b> /U6TX/IOCB7/RB7           | K9  | SEG39/ <b>RP5</b> /IOCD15/RD15                    |

| J4  | AVdd                                                  | K10 | SEG12/RP16/IOCF3/RF3                              |

| J5  | IOCH7/RH7                                             | K11 | SEG40/ <b>RP30</b> /IOCF2/RF2                     |

| J6  | TCK/IOCA1/RA1                                         | L1  | PGEC2/LCDBIAS3/AN6/RP6/IOCB6/RB6                  |

| J7  | SEG18/AN12/U6RX/CTED2/PMA11/IOCB12/RB12               | L2  | SEG36/VREF-/CVREF-/PMA7/IOCA9/RA9                 |

| J8  | IOCH9/RH9                                             | L3  | AVss                                              |

| J9  | IOCH10/RH10                                           | L4  | SEG30/AN9/TMPR/RP9/T1CK/IOCB9/RB9                 |

| J10 | SEG41/ <b>RP15</b> /IOCF8/RF8                         | L5  | IOCH7/RH7                                         |

| J11 | SDA1/IOCG3/RG3                                        | L6  | SEG53/ <b>RP31</b> /IOCF13/RF13                   |

| K1  | PGEC1/SEG6/VREF-/CVREF-/AN1/AN1-/RP1/CTED12/IOCB1/RB1 | L7  | SEG19/AN13/SDI4/CTED1/PMA10/IOCB13/RB13           |

| K2  | PGED1/SEG7/VREF+/CVREF+/DVREF+/AN0/RP0/IOCB0/RB0      | L8  | SEG9/AN15/RP29/CTED6/PMA0/PMALL/IOCB15/RB15       |

| K3  | SEG37/VREF+/CVREF+/DVREF+/PMA6/IOCA10/RA10            | L9  | SEG38/ <b>RPI43</b> /IOCD14/RD14                  |

| K4  | SEG31/AN8/ <b>RP8</b> /PWRGT/IOCB8/RB8                | L10 | SEG10/ <b>RP10</b> /PMA9/IOCF4/RF4                |

| K5  | AN11/REFI1/SS4/FSYNC4/PMA12/IOCB11/RB11               | L11 | SEG11/RP17/PMA8/IOCF5/RF5                         |

| K6  | SEG54/RPI32/CTED7/PMA18/IOCF12/RF12                   |     |                                                   |

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select functions.

| Register         | Address | All Resets                              | Register         | Address | All Resets                              | Register | Address | All Resets                              |

|------------------|---------|-----------------------------------------|------------------|---------|-----------------------------------------|----------|---------|-----------------------------------------|

| SPI (Continued)  |         |                                         | CLC              | •       |                                         | I2C3ADD  | 4C0     | 000000000000000000000000000000000000000 |

| SPI1BUFL         | 400     | 000000000000000000                      | CLC1CONL         | 464     | 000000000000000000                      | I2C3MSK  | 4C2     | 000000000000000000000000000000000000000 |

| SPI1BUFH         | 402     | 000000000000000000                      | CLC1CONH         | 466     | 000000000000000000                      | DMA      |         |                                         |

| SPI1BRGL         | 404     | 000xxxxxxxxxxx                          | CLC1SEL          | 468     | 000000000000000000                      | DMACON   | 4C4     | 000000000000000000000000000000000000000 |

| <b>SPI1IMSKL</b> | 408     | 000000000000000000                      | CLC1GLSL         | 46C     | 000000000000000000                      | DMABUF   | 4C6     | 000000000000000000000000000000000000000 |

| SPI1IMSKH        | 40A     | 000000000000000000                      | CLC1GLSH         | 46E     | 000000000000000000                      | DMAL     | 4C8     | 0000000000000000000                     |

| SPI1URDTL        | 40C     | 000000000000000000                      | CLC2CONL         | 470     | 000000000000000000                      | DMAH     | 4CA     | 0000000000000000000                     |

| SPI1URDTH        | 40E     | 00000000000000000                       | CLC2CONH         | 472     | 00000000000000000                       | DMACH0   | 4CC     | 000000000000000000                      |

| SPI2CON1L        | 410     | 00000000000000000                       | CLC2SEL          | 474     | 00000000000000000                       | DMAINT0  | 4CE     | 000000000000000000                      |

| SPI2CON1H        | 412     | 000000000000000000                      | CLC2GLSL         | 478     | 000000000000000000                      | DMASRC0  | 4D0     | 000000000000000000                      |

| SPI2CON2L        | 414     | 000000000000000000                      | CLC2GLSH         | 47A     | 000000000000000000                      | DMADST0  | 4D2     | 0000000000000000000                     |

| SPI2STATL        | 418     | 000000000101000                         | CLC3CONL         | 47C     | 0101001100011000                        | DMACNT0  | 4D4     | 000000000000000000000000000000000000000 |

| SPI2STATH        | 41A     | 000000000000000000                      | CLC3CONH         | 47E     | 000000000000000000                      | DMACH1   | 4D6     | 000000000000000000                      |

| SPI2BUFL         | 41C     | 000000000000000000                      | CLC3SEL          | 480     | 000000000000000000                      | DMAINT1  | 4D8     | 000000000000000000                      |

| SPI2BUFH         | 41E     | 000000000000000000                      | CLC3GLSL         | 484     | 000000000000000000000000000000000000000 | DMASRC1  | 4DA     | 000000000000000000000000000000000000000 |

| SPI2BRGL         | 420     | 000xxxxxxxxxxx                          | CLC3GLSH         | 486     | 000000000000000000000000000000000000000 | DMADST1  | 4DC     | 000000000000000000000000000000000000000 |

| SPI2IMSKL        | 424     | 000000000000000000000000000000000000000 | CLC4CONL         | 488     | 000000000000000000000000000000000000000 | DMACNT1  | 4DE     | 000000000000000000000000000000000000000 |

| SPI2IMSKH        | 426     | 000000000000000000000000000000000000000 | CLC4CONH         | 48A     | 000000000000000000000000000000000000000 | DMACH2   | 4E0     | 000000000000000000000000000000000000000 |

| SPI2URDTL        | 428     | 000000000000000000000000000000000000000 | CLC4SEL          | 48C     | 000000000000000000000000000000000000000 | DMAINT2  | 4E2     | 000000000000000000000000000000000000000 |

| SPI2URDTH        | 42A     | 000000000000000000000000000000000000000 | CLC4GLSL         | 490     | 000000000000000000000000000000000000000 | DMASRC2  | 4E4     | 000000000000000000000000000000000000000 |

| SPI3CON1L        | 42C     | 000000000000000000                      | CLC4GLSH         | 492     | 000000000000000000000000000000000000000 | DMADST2  | 4E6     | 000000000000000000000000000000000000000 |

| SPI3CON1H        | 42E     | 000000000000000000                      | l <sup>2</sup> C |         |                                         | DMACNT2  | 4E8     | 000000000000000000000000000000000000000 |

| SPI3CON2L        | 430     | 000000000000000000                      | I2C1RCV          | 494     | 000000000000000000                      | DMACH3   | 4EA     | 000000000000000000000000000000000000000 |

| SPI3STATL        | 434     | 000000000101000                         | I2C1TRN          | 496     | 00000001111111                          | DMAINT3  | 4EC     | 000000000000000000000000000000000000000 |

| SPI3STATH        | 436     | 000000000000000000                      | I2C1BRG          | 498     | 000000000000000000                      | DMASRC3  | 4EE     | 000000000000000000000000000000000000000 |

| SPI3BUFL         | 438     | 000000000000000000                      | I2C1CONL         | 49A     | 00010000000000000                       | DMADST3  | 4F0     | 000000000000000000000000000000000000000 |

| SPI3BUFH         | 43A     | 000000000000000000                      | I2C1CONH         | 49C     | 000000000000000000                      | DMACNT3  | 4F2     | 000000000000000000000000000000000000000 |

| SPI3BRGL         | 43C     | 000xxxxxxxxxxx                          | I2C1STAT         | 49E     | 000000000000000000                      | DMACH4   | 4F4     | 000000000000000000                      |

| <b>SPI3IMSKL</b> | 440     | 000000000000000000                      | I2C1ADD          | 4A0     | 000000000000000000                      | DMAINT4  | 4F6     | 000000000000000000                      |

| <b>SPI3IMSKH</b> | 442     | 00000000000000000                       | I2C1MSK          | 4A2     | 00000000000000000                       | DMASRC4  | 4F8     | 000000000000000000                      |

| <b>SPI3URDTL</b> | 444     | 000000000000000000                      | I2C2RCV          | 4A4     | 000000000000000000                      | DMADST4  | 4FA     | 000000000000000000                      |

| SPI3URDTH        | 446     | 00000000000000000                       | I2C2TRN          | 4A6     | 000000011111111                         | DMACNT4  | 4FC     | 000000000000000000000000000000000000000 |

| SPI4CON1L        | 448     | 00000000000000000                       | I2C2BRG          | 4A8     | 00000000000000000                       | DMACH5   | 4FE     | 000000000000000000                      |

| SPI4CON1H        | 44A     | 00000000000000000                       | I2C2CONL         | 4AA     | 0001000000000000                        |          | •       |                                         |

| SPI4CON2L        | 44C     | 00000000000000000                       | I2C2CONH         | 4AC     | 00000000000000000                       |          |         |                                         |

| SPI4STATL        | 450     | 000000000101000                         | I2C2STAT         | 4AE     | 00000000000000000                       |          |         |                                         |

| SPI4STATH        | 452     | 000000000000000000                      | I2C2ADD          | 4B0     | 000000000000000000                      |          |         |                                         |

| SPI4BUFL         | 454     | 000000000000000000                      | I2C2MSK          | 4B2     | 000000000000000000000000000000000000000 |          |         |                                         |

| SPI4BUFH         | 456     | 000000000000000000                      | I2C3RCV          | 4B4     | 000000000000000000                      |          |         |                                         |

| SPI4BRGL         | 458     | 000xxxxxxxxxxx                          | I2C3TRN          | 4B6     | 00000001111111                          |          |         |                                         |

| SPI4IMSKL        | 45C     | 000000000000000000                      | I2C3BRG          | 4B8     | 000000000000000000                      |          |         |                                         |

| SPI4IMSKH        | 45E     | 000000000000000000                      | I2C3CONL         | 4BA     | 00010000000000000                       |          |         |                                         |

| SPI4URDTL        | 460     | 000000000000000000                      | I2C3CONH         | 4BC     | 000000000000000000                      |          |         |                                         |

| SPI4URDTH        | 462     | 000000000000000000                      | I2C3STAT         | 4BE     | 000000000000000000000000000000000000000 |          |         |                                         |

TABLE 4-9: SFR BLOCK 400h

Legend: x = unknown or indeterminate value. Reset and address values are in hexadecimal.

| REGISTER      | 5-2: DMAC                       | CHn: DMA Cł                           | HANNEL n C      | ONTROL RE         | GISTER            |                       |                        |

|---------------|---------------------------------|---------------------------------------|-----------------|-------------------|-------------------|-----------------------|------------------------|

| U-0           | U-0                             | U-0                                   | r-0             | U-0               | R/W-0             | R/W-0                 | R/W-0                  |

| _             | _                               | —                                     | —               | _                 | NULLW             | RELOAD <sup>(1)</sup> | CHREQ <sup>(3)</sup>   |

| bit 15        |                                 |                                       |                 |                   |                   |                       | bit                    |

| R/W-0         | R/W-0                           | R/W-0                                 | R/W-0           | R/W-0             | R/W-0             | R/W-0                 | R/W-0                  |

| SAMODE1       | SAMODE0                         | DAMODE1                               | DAMODE0         | TRMODE1           | TRMODE0           | SIZE                  | CHEN                   |

| bit 7         |                                 |                                       |                 |                   |                   |                       | bit                    |

| Legend:       |                                 | r = Reserved                          | bit             |                   |                   |                       |                        |

| R = Readable  | e bit                           | W = Writable                          | bit             | U = Unimplen      | nented bit, read  | d as '0'              |                        |

| -n = Value at | POR                             | '1' = Bit is set                      |                 | '0' = Bit is clea | ared              | x = Bit is unkn       | own                    |

|               |                                 |                                       | .1              |                   |                   |                       |                        |

| bit 15-13     | -                               | ted: Read as '(                       | ).              |                   |                   |                       |                        |

| bit 12        | Reserved: Ma                    |                                       | .,              |                   |                   |                       |                        |

| bit 11        | -                               | ted: Read as '(                       |                 |                   |                   |                       |                        |

| bit 10        |                                 | Write Mode bit<br>write is initiate   |                 | for over write    |                   |                       |                        |

|               |                                 | write is initiate                     |                 |                   | e to DIVIADS IT   | I                     |                        |

| bit 9         |                                 | dress and Cou                         |                 | )                 |                   |                       |                        |

|               |                                 |                                       |                 |                   | reloaded to th    | eir previous va       | lues upon th           |

|               |                                 | e next operation                      |                 | •                 |                   |                       | (0)                    |

|               |                                 |                                       |                 |                   | ded on the star   | t of the next ope     | eration <sup>(2)</sup> |

| bit 8         |                                 | A Channel Soft                        | •               |                   |                   |                       |                        |

|               |                                 | equest is initiate<br>request is pend |                 | automatically of  | cleared upon c    | ompletion of a [      | OMA transfer           |

| bit 7-6       | SAMODE<1:0                      | 0>: Source Add                        | lress Mode Se   | lection bits      |                   |                       |                        |

|               |                                 | Cn is used in P                       |                 |                   |                   |                       |                        |

|               |                                 | Cn is decremen<br>Cn is incremen      |                 |                   |                   |                       |                        |

|               |                                 | Cn remains un                         |                 |                   |                   | mpletion              |                        |

| bit 5-4       |                                 | 0>: Destination                       | -               | -                 |                   |                       |                        |

|               |                                 | Tn is used in P                       |                 |                   |                   | nchanged              |                        |

|               | 10 = DMADS                      | Tn is decremer                        | nted based on   | the SIZE bit aft  | ter a transfer co | ompletion             |                        |

|               |                                 | Tn is incremen                        |                 |                   |                   | mpletion              |                        |

| hit 2 2       |                                 | Tn remains und                        | -               | -                 | Dietion           |                       |                        |

| bit 3-2       |                                 | 0>: Transfer Mo                       |                 | nis               |                   |                       |                        |

|               | 10 = Continuo                   | ed Continuous r                       | noue            |                   |                   |                       |                        |

|               |                                 | ed One-Shot mo                        | ode             |                   |                   |                       |                        |

|               | 00 = One-Sho                    | ot mode                               |                 |                   |                   |                       |                        |

| bit 1         | SIZE: Data Si                   | ze Selection bi                       | t               |                   |                   |                       |                        |

|               | 1 = Byte (8-bi<br>0 = Word (16- |                                       |                 |                   |                   |                       |                        |

| bit 0         | CHEN: DMA                       | Channel Enable                        | e bit           |                   |                   |                       |                        |

|               | 1 = The corre                   | sponding chan                         | nel is enabled  |                   |                   |                       |                        |

|               |                                 | sponding chan                         |                 |                   |                   |                       |                        |

| Note 1: O     | nly the original D              | MACNTn is rec                         | uired to be sto | red to recover fl | he original DMA   | SRCn and DM           | ADSTn value            |

|               | MACNTn will alv                 |                                       | -               |                   | -                 |                       |                        |

|               | e number of tra                 | -                                     |                 |                   | -                 |                       |                        |

### REGISTER 5-2: DMACHn: DMA CHANNEL n CONTROL REGISTER

# 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24F Family Reference Manual", "Dual Partition Flash Program Memory" (DS70005156). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ256GA412/GB412 family of devices contains internal Flash program memory for storing and executing application code. The program memory is readable, writable and erasable. The Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ256GA412/GB412 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

# 6.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 6-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### 1 1 1 24 Bits $\sim$ Using Program Counter 0 Program 0 Counter Working Reg EA Usina Table TBLPAG Reg 1/0Instruction 8 Bits 16 Bits ▲. User/Configuration Byte 24-Bit EA Select Space Select 1

FIGURE 6-1: ADDRESSING FOR TABLE REGISTERS

# 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS39712). The information in this data sheet supersedes the information in the FRM.

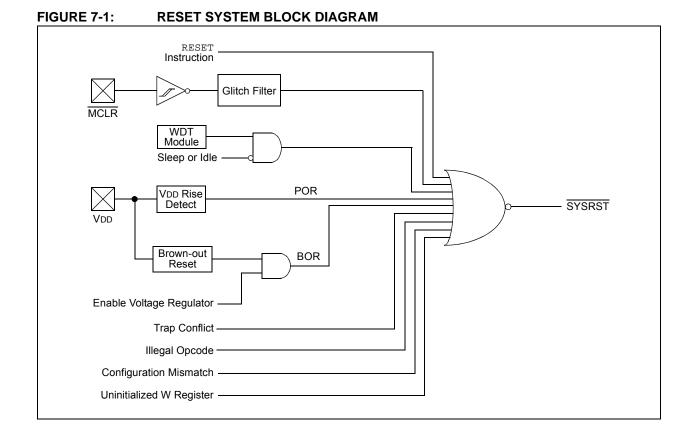

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). In addition, Reset events occurring while an extreme power-saving feature is in use (such as VBAT) will set one or more status bits in the RCON2 register (Register 7-2). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON registers should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

# 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS70000600). The information in this data sheet supersedes the information in the FRM.

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- Up to 8 Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with up to 118 Vectors

- Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Alternate Interrupt Vector Table (AIVT) for Debug Support

- Fixed Interrupt Entry and Return Latencies

### 8.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 8-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 source interrupts. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ256GA412/GB412 family devices implement non-maskable traps and unique interrupts. These are summarized in Table 8-1 and Table 8-2.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The ALTIVT (INTCON2<8>) control bit provides access to the AIVT. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application, and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the PC to zero. The micro-controller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0        | R-0, HSC                                                             | R/W-0                                                        | U-0            | U-0               | U-0              | U-0             | R/W-0  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------|--------------------------------------------------------------|----------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| GIE          | DISI                                                                 | SWTRAP                                                       | _              | _                 | _                | _               | ALTIVT |  |  |  |  |  |

| bit 15       |                                                                      |                                                              |                |                   |                  |                 | bit    |  |  |  |  |  |

|              |                                                                      |                                                              | DAMO           | DAVO              | DANA             | DAMA            | DANO   |  |  |  |  |  |

| U-0          | U-0                                                                  | U-0                                                          | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|              | _                                                                    | —                                                            | INT4EP         | INT3EP            | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |                                                                      |                                                              |                |                   |                  |                 | bit    |  |  |  |  |  |

| Legend:      |                                                                      | HSC = Hardwa                                                 | are Settable/C | learable bit      |                  |                 |        |  |  |  |  |  |

| R = Readab   | le bit                                                               | W = Writable b                                               | bit            | U = Unimplem      | nented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value a | t POR                                                                | '1' = Bit is set                                             |                | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |  |  |  |  |  |

|              |                                                                      |                                                              |                |                   |                  |                 |        |  |  |  |  |  |

| bit 15       |                                                                      | nterrupt Enable                                              |                |                   |                  |                 |        |  |  |  |  |  |

|              |                                                                      | and associated                                               | •              |                   | bled             |                 |        |  |  |  |  |  |

| L:L 4 4      |                                                                      | s are disabled; t                                            | •              | napled            |                  |                 |        |  |  |  |  |  |

| bit 14       |                                                                      | DISI: DISI Instruction Status bit                            |                |                   |                  |                 |        |  |  |  |  |  |

|              | 1 = DISI instruction is active<br>0 = DISI instruction is not active |                                                              |                |                   |                  |                 |        |  |  |  |  |  |

| bit 13       |                                                                      | oftware Trap Sta                                             |                |                   |                  |                 |        |  |  |  |  |  |

|              |                                                                      | = Generates a software trap                                  |                |                   |                  |                 |        |  |  |  |  |  |

|              | 0 = Software                                                         | trap is not requ                                             | ested          |                   |                  |                 |        |  |  |  |  |  |

| bit 12-9     | Unimplemen                                                           | ted: Read as '0                                              | ,              |                   |                  |                 |        |  |  |  |  |  |

| bit 8        | ALTIVT: Enable Alternate Interrupt Vector Table bit                  |                                                              |                |                   |                  |                 |        |  |  |  |  |  |

|              |                                                                      | ernate Interrupt<br>ndard (default)                          |                | or Table          |                  |                 |        |  |  |  |  |  |

| bit 7-5      | Unimplemen                                                           | ted: Read as '0                                              | 3              |                   |                  |                 |        |  |  |  |  |  |

| bit 4        | INT4EP: Exte                                                         | INT4EP: External Interrupt 4 Edge Detect Polarity Select bit |                |                   |                  |                 |        |  |  |  |  |  |

|              |                                                                      | on negative edg                                              |                |                   |                  |                 |        |  |  |  |  |  |

| bit 3        |                                                                      | INT3EP: External Interrupt 3 Edge Detect Polarity Select bit |                |                   |                  |                 |        |  |  |  |  |  |

|              | 1 = Interrupt                                                        | on negative edg                                              | ge             | 2                 |                  |                 |        |  |  |  |  |  |

| bit 2        | -                                                                    | ernal Interrupt 2                                            |                | Polarity Select h |                  |                 |        |  |  |  |  |  |

|              |                                                                      | on negative edg                                              | -              |                   |                  |                 |        |  |  |  |  |  |

|              |                                                                      | on positive edg                                              |                |                   |                  |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: Exte                                                         | ernal Interrupt 1                                            | Edge Detect I  | Polarity Select b | bit              |                 |        |  |  |  |  |  |

|              |                                                                      | on negative edg                                              |                |                   |                  |                 |        |  |  |  |  |  |

| bit 0        |                                                                      | ernal Interrupt 0                                            |                | Polarity Select b | bit              |                 |        |  |  |  |  |  |

|              |                                                                      | on negative edg                                              | -              |                   | -                |                 |        |  |  |  |  |  |

|              | 0 = Interrupt                                                        |                                                              |                |                   |                  |                 |        |  |  |  |  |  |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0          | U-0                                                                                                | U-0                                                                                                       | U-0           | U-0               | R/W-0            | U-0             | R/W-0 |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _            | _                                                                                                  | —                                                                                                         |               |                   | CMPMD            | —               | PMMD  |  |  |  |  |  |

| bit 15       |                                                                                                    |                                                                                                           |               |                   |                  |                 | bit 8 |  |  |  |  |  |

|              |                                                                                                    |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                              | U-0                                                                                                       | U-0           | R/W-0             | R/W-0            | R/W-0           | U-0   |  |  |  |  |  |

| CRCMD        | DACMD                                                                                              |                                                                                                           |               | U3MD              | I2C3MD           | I2C2MD          | _     |  |  |  |  |  |

| bit 7        |                                                                                                    |                                                                                                           |               |                   |                  |                 | bit ( |  |  |  |  |  |

| Legend:      |                                                                                                    |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                             | W = Writable b                                                                                            | it            | U = Unimplen      | nented bit, read | l as '0'        |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                                                                                          |               | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |  |  |  |

|              |                                                                                                    |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| bit 15-11    | Unimplemen                                                                                         | ted: Read as '0                                                                                           | 3             |                   |                  |                 |       |  |  |  |  |  |

| bit 10       | CMPMD: Trip                                                                                        | le Comparator N                                                                                           | Module Disabl | e bit             |                  |                 |       |  |  |  |  |  |

|              |                                                                                                    | = Module is disabled                                                                                      |               |                   |                  |                 |       |  |  |  |  |  |

| L:1 0        | •                                                                                                  | ower and clock                                                                                            |               | enabled           |                  |                 |       |  |  |  |  |  |

| bit 9        | -                                                                                                  | ted: Read as '0                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| bit 8        | -                                                                                                  | PMMD: Enhanced Parallel Master Port Disable bit<br>1 = Module is disabled                                 |               |                   |                  |                 |       |  |  |  |  |  |

|              |                                                                                                    |                                                                                                           | sources are e | nabled            |                  |                 |       |  |  |  |  |  |

| bit 7        | •                                                                                                  | <ul> <li>0 = Module power and clock sources are enabled</li> <li>CRCMD: CRC Module Disable bit</li> </ul> |               |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = Module is disabled                                                                             |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

|              | 0 = Module p                                                                                       | 0 = Module power and clock sources are enabled                                                            |               |                   |                  |                 |       |  |  |  |  |  |

| bit 6        | DACMD: DAG                                                                                         | C Module Disabl                                                                                           | le bit        |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = Module is disabled                                                                             |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

|              | •                                                                                                  | ower and clock                                                                                            |               | enabled           |                  |                 |       |  |  |  |  |  |

| bit 5-4      | -                                                                                                  | ted: Read as '0                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| bit 3        | U3MD: UART3 Module Disable bit                                                                     |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

|              | <ol> <li>1 = Module is disabled</li> <li>0 = Module power and clock sources are enabled</li> </ol> |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

| bit 2        | -                                                                                                  | 3 Module Disabl                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = Module is                                                                                      |                                                                                                           | C Dit         |                   |                  |                 |       |  |  |  |  |  |

|              |                                                                                                    | ower and clock                                                                                            | sources are e | enabled           |                  |                 |       |  |  |  |  |  |

| bit 1        | 12C2MD: 12C2                                                                                       | 2 Module Disabl                                                                                           | e bit         |                   |                  |                 |       |  |  |  |  |  |

|              | 1 = Module is                                                                                      |                                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

|              | -                                                                                                  | ower and clock                                                                                            |               | enabled           |                  |                 |       |  |  |  |  |  |

|              |                                                                                                    | ted: Read as '0                                                                                           |               |                   |                  |                 |       |  |  |  |  |  |

#### REGISTER 10-6: PMD3: PERIPHERAL MODULE DISABLE REGISTER 3

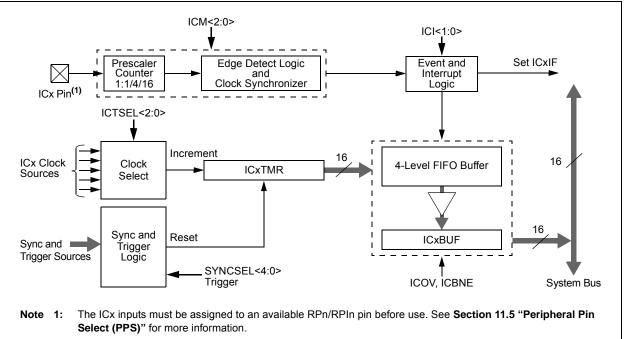

# 15.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture with Dedicated Timer" (DS70000352). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ256GA412/GB412 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-Configurable for 32-Bit Operation in All Modes by Cascading Two Adjacent Modules

- Synchronous and Trigger modes of Output compare Operation, with up to 30 User-Selectable Sync/Trigger Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- · Configurable Interrupt Generation

- Up to 6 Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

The module is controlled through two registers: ICxCON1 (Register 15-1) and ICxCON2 (Register 15-2). A general block diagram of the module is shown in Figure 15-1.

## 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSEL<4:0> bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

#### REGISTER 19-2: UxSTAL: UARTx STATUS LOW AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5   | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Receiver is Idle</li> <li>0 = Receiver is active</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receive buffer and the RSR to the empty state</li> </ul>                                                                                                                                                                               |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1: | The value of this bit only affects the transmit properties of the module when the IrDA encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                                      |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

#### REGISTER 19-3: UxSTAH: UARTx STATUS HIGH AND CONTROL REGISTER

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADMASK7 | ADMASK6 | ADMASK5 | ADMASK4 | ADMASK3 | ADMASK2 | ADMASK1 | ADMASK0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|----------|----------|----------|----------|----------|----------|----------|

| ADMADDF | ADMADDR6 | ADMADDR5 | ADMADDR4 | ADMADDR3 | ADMADDR2 | ADMADDR1 | ADMADDR0 |

| bit 7   |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-8 | ADMASK<7:0>: ADMADDR<7:0> Masking bits                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Corresponding ADMADDRx bit is used to detect the address match                                                                       |

|          | 0 = Corresponding ADMADDRx bit is not used to detect the address match                                                                   |

| bit 7-0  | ADMADDR<7:0>: Address Detect Task Off-Load bits                                                                                          |

|          | Used with the ADMASK<7:0> bits to off-load the task of detecting the address character from the<br>processor during Address Detect mode. |

### 20.1 Hardware Configuration

#### 20.1.1 DEVICE MODE

#### 20.1.1.1 D+ Pull-up Resistor

PIC24FJ256GA412/GB412 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller is operating in Device mode. This is used to signal an external host that the device is operating in Full-Speed Device mode. It is engaged by setting the USBEN bit (U1CON<0>) and powering up the USB module (USBPWR = 1). If the OTGEN bit (U1OTGCON<2>) is set, then the D+ pull-up is enabled through the DPPULUP bit (U1OTGCON<7>).

#### 20.1.1.2 The VBUS Pin

In order to meet the USB 2.0 specification requirement, relating to the back drive voltage on the D+/D- pins, the USB module incorporates VBUS-level sensing comparators. When the comparators detect the VBUS level below the VA\_SESS\_VLD level, the hardware will automatically disable the D+ pull-up resistor described in **Section 20.1.1.1** "D+ Pull-up Resistor". This allows the device to automatically meet the back drive requirement for D+ and D-, even if the application firmware does not explicitly monitor the VBUS level. Therefore, the VBUS microcontroller pin should not be left floating in USB Device mode application designs, and should normally be connected to the VBUS pin on the USB connector/cable (either directly or through a small resistance  $\leq$  100 ohms).

#### 20.1.1.3 Power Modes

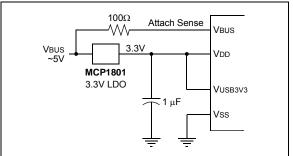

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- Bus Power Only mode

- · Self-Power Only mode

- Dual Power with Self-Power Dominance mode

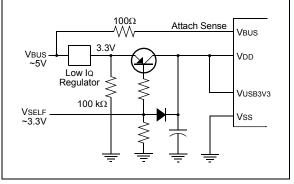

Bus Power Only mode (Figure 20-2) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the *"USB 2.0 OTG Specification"*, the total effective capacitance, appearing across VBUS and ground, must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or Dpull-up resistor must remain active, which will consume some of the allowed suspend current.

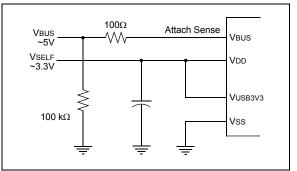

In Self-Power Only mode (Figure 20-3), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable when the USB module is operated in USB Device mode.

The Dual Power with Self-Power Dominance mode (Figure 20-4) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

#### FIGURE 20-2: BUS POWER ONLY INTERFACE EXAMPLE

FIGURE 20-3: SELF-POWER ONLY

FIGURE 20-4:

DUAL POWER EXAMPLE

| R/W-0           | R/W-0                                                                       | R/W-0                                                      | R/W-0                                     | U-0                  | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------|----------------------|------------------|-----------------|---------|--|--|--|--|

| CSDIS           | CSP                                                                         | CSPTEN                                                     | BEP                                       | —                    | WRSP             | RDSP            | SM      |  |  |  |  |

| bit 15          |                                                                             |                                                            |                                           |                      |                  |                 | bit 8   |  |  |  |  |

| R/W-0           | R/W-0                                                                       | R/W-0                                                      | U-0                                       | U-0                  | U-0              | U-0             | U-0     |  |  |  |  |

| ACKP            | PTSZ1                                                                       | PTSZ0                                                      | _                                         | _                    | _                | _               | _       |  |  |  |  |

| bit 7           | 11021                                                                       | 11020                                                      |                                           |                      |                  |                 | l bit ( |  |  |  |  |

|                 |                                                                             |                                                            |                                           |                      |                  |                 |         |  |  |  |  |

| Legend:         | 1.11                                                                        |                                                            | 1.11                                      |                      |                  | 1               |         |  |  |  |  |

| R = Readable    |                                                                             | W = Writable                                               |                                           | -                    | nented bit, read |                 |         |  |  |  |  |

| -n = Value at I | POR                                                                         | '1' = Bit is set                                           |                                           | '0' = Bit is clea    | ared             | x = Bit is unkn | iown    |  |  |  |  |

| bit 15          | 1 = Disables                                                                | Select x Disable<br>the Chip Select<br>the Chip Select     | t x functionalit                          |                      |                  |                 |         |  |  |  |  |

| bit 14          |                                                                             | elect x Polarity                                           | bit                                       |                      |                  |                 |         |  |  |  |  |

|                 | 1 = Active-hi<br>0 = Active-lo                                              |                                                            |                                           |                      |                  |                 |         |  |  |  |  |

| bit 13          |                                                                             | ICSx Port Enab                                             | ole bit                                   |                      |                  |                 |         |  |  |  |  |

|                 |                                                                             | port is enabled                                            |                                           |                      |                  |                 |         |  |  |  |  |

|                 |                                                                             | port is disabled                                           |                                           |                      |                  |                 |         |  |  |  |  |

| bit 12          | 1 = Nibble/b                                                                | elect x Nibble/B<br>yte enable is ac<br>yte enable is ac   | tive-high <u>(</u> PMI                    | BE0, PMBE1)          |                  |                 |         |  |  |  |  |

| bit 11          |                                                                             | -                                                          | •                                         |                      |                  |                 |         |  |  |  |  |

| bit 10          | Unimplemented: Read as '0'<br>WRSP: Chip Select x Write Strobe Polarity bit |                                                            |                                           |                      |                  |                 |         |  |  |  |  |

|                 | For Slave Mo<br>1 = Write str                                               | odes and Maste<br>obe is active-hig<br>obe is active-lo    | <u>r Mode when s</u><br>gh <u>(PMWR</u> ) |                      |                  |                 |         |  |  |  |  |

|                 | 1 = Enable s                                                                | lode when SM =<br>strobe is active-l<br>strobe is active-l | high (PMENB)                              | )                    |                  |                 |         |  |  |  |  |

| bit 9           | RDSP: Chip                                                                  | Select x Read S                                            | Strobe Polarity                           | bit                  |                  |                 |         |  |  |  |  |

|                 | 1 = Read str                                                                | odes and Maste<br>obe is active-hi<br>obe is active-lo     | gh <u>(PMRD</u> )                         | <u>SM = 0:</u>       |                  |                 |         |  |  |  |  |

|                 | 1 = Read/wr                                                                 | lode when SM =<br>ite strobe is act<br>rite strobe is act  | ive-high (PMR                             |                      |                  |                 |         |  |  |  |  |

| bit 8           | 1 = Read/wr                                                                 | lect x Strobe Mo<br>ite and enable s<br>d write strobes    | strobes (PMRI                             | D/PMWR and P<br>MWR) | MENB)            |                 |         |  |  |  |  |

| bit 7           |                                                                             | Select x Acknow                                            |                                           |                      |                  |                 |         |  |  |  |  |

|                 | 1 = ACK is a                                                                | nctive-high <u>(PM</u><br>nctive-low (PMA                  | ACK1)                                     |                      |                  |                 |         |  |  |  |  |

| bit 6-5         |                                                                             | Chip Select x P                                            |                                           |                      |                  |                 |         |  |  |  |  |

|                 | 11 = Reserve<br>10 = 16-bit p<br>01 = 4-bit po                              | -                                                          | 15:0>)<br>:0>)                            |                      |                  |                 |         |  |  |  |  |

|                 | 00 - 0 - 0100                                                               |                                                            | .0~1                                      |                      |                  |                 |         |  |  |  |  |

#### REGISTER 21-5: PMCSxCF: EPMP CHIP SELECT x CONFIGURATION REGISTER

#### REGISTER 23-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit              |

|-------|----------------------------------------------------------|

|       | 1 = Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit           |

|       | 1 = Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit              |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit           |

|       | 1 = Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = Data Source 1 inverted signal is disabled for Gate 3 |

#### 25.6 Encrypting a Session Key

| Note:                      | ECB and CBC modes are restricted to |  |  |

|----------------------------|-------------------------------------|--|--|

| 128-bit session keys only. |                                     |  |  |

- 1. If not already set, set the CRYON bit.

- 2. If not already programmed, program the SKEYEN bit to '1'.