Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                               |  |

|-------------------------|------------------------------------------------------------------------|--|

| Туре                    | SC140 Core                                                             |  |

| Interface               | Communications Processor Module (CPM)                                  |  |

| Clock Rate              | 275MHz                                                                 |  |

| Non-Volatile Memory     | External                                                               |  |

| On-Chip RAM             | 512kB                                                                  |  |

| Voltage - I/O           | 3.30V                                                                  |  |

| Voltage - Core          | 1.60V                                                                  |  |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                     |  |

| Mounting Type           | Surface Mount                                                          |  |

| Package / Case          | 332-BFBGA, FCBGA                                                       |  |

| Supplier Device Package | 332-FCBGA (17x17)                                                      |  |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8103vt1100f |  |

|                         |                                                                        |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Target Applications**

The MSC8103 targets applications requiring very high performance, very large amounts of internal memory, and such networking capabilities as:

- Third-generation wideband wireless infrastructure systems

- Packet Telephony systems

- Multi-channel modem banks

- Multi-channel xDSL

# **Product Documentation**

The documents listed in **Table 1** are required for a complete description of the MSC8103 and are necessary to design properly with the part. Documentation is available from the following sources (see back cover for details):

- A local Freescale distributor

- A Freescale Semiconductor sales office

- A Freescale Semiconductor Literature Distribution Center

- The world wide web (WWW)

|  | Table 1. | MSC8103 Documentation |

|--|----------|-----------------------|

|--|----------|-----------------------|

| Name                            | Description                                                                                                                                 | Order Number                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| MSC8103<br>Technical Data       | MSC8103 features list and physical, electrical, timing, and package specifications                                                          | MSC8103/D                       |

| MSC8101 User's Guide            | Detailed functional description of the MSC8101 memory configuration, operation, and register programming. All details apply to the MSC8103. | MSC8101UG/D                     |

| MSC8103 Reference Manual        | Detailed description of the MSC8103 processor core and instruction set                                                                      | MSC8103RM/D                     |

| SC140 DSP Core Reference Manual | Detailed description of the SC140 family processor core and instruction set                                                                 | MNSC140CORE/D                   |

| Application Notes               | Documents describing specific applications or optimized device<br>operation including code examples                                         | See the MSC8103 product website |

Although there are eight interrupt request ( $\overline{IRQ}$ ) connections to the core processor, there are multiple external lines that can connect to these internal signal lines. After reset, the default configuration includes two  $\overline{IRQ1}$  and two  $\overline{IRQ7}$  input lines. The designer must select one line for each required interrupt and reconfigure the other external signal line or lines for alternate functions.

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A[0-31]   | Input/Output | Address Bus<br>When the MSC8103 is in external master bus mode, these pins function as the address bus. The<br>MSC8103 drives the address of its internal bus masters and responds to addresses generated by<br>external bus masters. When the MSC8103 is in Internal Master Bus mode, these pins are used as<br>address lines connected to memory devices and are controlled by the MSC8103 memory controller. |  |

| TT[0-4]   | Input/Output | Bus Transfer Type<br>The bus master drives these pins during the address tenure to specify the type of transaction.                                                                                                                                                                                                                                                                                             |  |

| TSIZ[0-3] | Input/Output | Transfer Size<br>The bus master drives these pins with a value indicating the number of bytes transferred in the<br>current transaction.                                                                                                                                                                                                                                                                        |  |

| TBST      | Input/Output | Bus Transfer Burst<br>The bus master asserts this pin to indicate that the current transaction is a burst transaction<br>(transfers four quad words).                                                                                                                                                                                                                                                           |  |

| IRQ1      | Input        | Interrupt Request 1 <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                 |  |

| GBL       | Input/Output | <b>Global</b> <sup>1</sup><br>When a master within the chip initiates a bus transaction, it drives this pin. When an external master<br>initiates a bus transaction, it should drive this pin. Assertion of this pin indicates that the transfer is<br>global and it should be snooped by caches in the system.                                                                                                 |  |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                                          |  |

| BADDR29   | Output       | Burst Address 29 <sup>1</sup><br>One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8103 memory controller.                                                                                                                                                                                                                                       |  |

| IRQ2      | Input        | Interrupt Request 2 <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                 |  |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                                          |  |

| BADDR30   | Output       | Burst Address 30 <sup>1</sup><br>One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8103 memory controller.                                                                                                                                                                                                                                       |  |

| IRQ3      | Input        | <b>Interrupt Request 3</b> <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                          |  |

| Reserved  | Output       | The primary configuration is reserved.                                                                                                                                                                                                                                                                                                                                                                          |  |

| BADDR31   | Output       | Burst Address 31 <sup>1</sup><br>One of five outputs of the memory controller. These pins connect directly to memory devices controlled by the MSC8103 memory controller.                                                                                                                                                                                                                                       |  |

| IRQ5      | Input        | Interrupt Request 5 <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller,<br>from the SC140 core.                                                                                                                                                                                                                                              |  |

| Table 1-5. | System Bus. | HDI16, and | Interrupt Signals |

|------------|-------------|------------|-------------------|

|            | System Dus, | nono, anu  | interrupt Signals |

| Table 1-5.         System Bus, HDI16, and Interrupt Signals (Cont |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| Signal    | Data Flow    | Description                                                                                                                                                                                                                                                                                   |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[32–47]  | Input/Output | Data Bus Bits 32–47<br>In write transactions the bus master drives the valid data on this bus. In read transactions the slave<br>drives the valid data on this bus.                                                                                                                           |

| HD[0–15]  | Input/Output | Host Data <sup>2</sup><br>When the HDI16 interface is enabled, these signals are lines 0-15 of the bidirectional tri-state data bus.                                                                                                                                                          |

| D[48–51]  | Input/Output | Data Bus Bits 48–51<br>In write transactions the bus master drives the valid data on these pins. In read transactions the<br>slave drives the valid data on these pins.                                                                                                                       |

| HA[0–3]   | Input        | Host Address Line 0–3 <sup>3</sup><br>When the HDI16 interface bus is enabled, these lines address internal host registers.                                                                                                                                                                   |

| D52       | Input/Output | Data Bus Bit 52<br>In write transactions the bus master drives the valid data on this pin. In read transactions the slave<br>drives the valid data on this pin.                                                                                                                               |

| HCS1      | Input        | Host Chip Select <sup>3</sup><br>When the HDI16 interface is enabled, this is one of the two chip-select pins. The HDI16 chip select<br>is a logical OR of HCS1 and HCS2.                                                                                                                     |

| D53       | Input/Output | Data Bus Bit 53<br>In write transactions the bus master drives the valid data on this pin. In read transactions the slave<br>drives the valid data on this pin.                                                                                                                               |

| HRW       | Input        | Host Read Write Select <sup>3</sup><br>When the HDI16 interface is enabled in Single Strobe mode, this is the read/write input (HRW).                                                                                                                                                         |

| HRD/HRD   | Input        | Host Read Strobe <sup>3</sup><br>When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the read data strobe Schmitt trigger input (HRD/HRD). The polarity of the data strobe is programmable.                                                             |

| D54       | Input/Output | Data Bus Bit 54<br>In write transactions the bus master drives the valid data on this pin. In read transactions the slave<br>drives the valid data on this pin.                                                                                                                               |

| HDS/HDS   | Input        | Host Data Strobe <sup>3</sup><br>When the HDI16 is programmed to interface with a single data strobe host bus, this pin is the data<br>strobe Schmitt trigger input (HDS/HDS). The polarity of the data strobe is programmable.                                                               |

| HWR/HWR   | Input        | Host Write Data Strobe <sup>3</sup><br>When the HDI16 is programmed to interface with a double data strobe host bus, this pin is the write data strobe Schmitt trigger input (HWR/HWR). The polarity of the data strobe is programmable.                                                      |

| D55       | Input/Output | Data Bus Bit 55<br>In write transactions the bus master drives the valid data on this pin. In read transactions the slave<br>drives the valid data on this pin.                                                                                                                               |

| HREQ/HREQ | Output       | Host Request <sup>3</sup><br>When the HDI1 <u>6 is programmed to interface with a single host request host bus, this pin is the host request output (HREQ/HREQ). The polarity of the host request is programmable. The host request may be programmed as a driven or open-drain output.</u>   |

| HTRQ/HTRQ | Output       | <b>Transmit Host Request</b> <sup>3</sup><br>When the HDI16 is programmed to interface with a double host request host bus, this pin is the transmit host request output (HTRQ/HTRQ). The signal can be programmed as driven or open drain. The polarity of the host request is programmable. |

als/Connections

| T-11-4 C   | O             | IDIAO - LILIA       |            |             |

|------------|---------------|---------------------|------------|-------------|

| Table 1-5. | System Bus, F | HDI16, and Interrup | ot Signals | (Continued) |

| Signal   | Data Flow    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ĪRQ5     | Input        | Interrupt Request 5 <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| DP5      | Input/Output | <b>Data Parity 5</b> <sup>1</sup><br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity five pin should give odd parity (odd number of ones) on the group of signals that includes data parity 5 and D[40–47].                                                                                                                                                                                                                                                                                                                                            |  |

| DREQ4    | Input        | <b>DMA Request 4</b> <sup>1</sup><br>An external peripheral uses this pin to request DMA service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| EXT_DBG3 | Output       | <b>External Data Bus Grant 3</b> <sup>1,2</sup><br>The MSC8103 asserts this pin to grant data bus ownership to an external bus master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| IRQ6     | Input        | Interrupt Request 6 <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| DP6      | Input/Output | <b>Data Parity 6</b> <sup>1</sup><br>The agent that drives the data bus also drives the data parity signals. The value driven on the data parity six pin should give odd parity (odd number of ones) on the group of signals that includes data parity 6 and D[48–55].                                                                                                                                                                                                                                                                                                                                             |  |

| DACK3    | Output       | <b>DMA Acknowledge 3</b> <sup>1</sup><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| IRQ7     | Input        | <b>Interrupt Request 7</b> <sup>1</sup><br>One of eight external lines that can request a service routine, via the internal interrupt controller, from the SC140 core.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| DP7      | Input/Output | <b>Data Parity 7</b> <sup>1</sup><br>The master or slave that drives the data bus also drives the data parity signals. The value driven on the data parity seven pin should give odd parity (odd number of ones) on the group of signals that includes data parity 7 and D[56–63].                                                                                                                                                                                                                                                                                                                                 |  |

| DACK4    | Output       | <b>DMA Acknowledge</b> <sup>1</sup><br>The DMA controller drives this output to acknowledge the DMA transaction on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TA       | Input/Output | <b>Transfer Acknowledge</b><br>Indicates that a data beat is valid on the data bus. For single beat transfers, assertion of $\overline{TA}$ indicates the termination of the transfer. For burst transfers, $\overline{TA}$ is asserted four times to indicate the transfer of four data beats with the last assertion indicating the termination of the burst transfer.                                                                                                                                                                                                                                           |  |

| TEA      | Input/Output | Transfer Error Acknowledge<br>Indicates a bus error. masters within the MSC8103 monitor the state of this pin. The MSC8103<br>internal bus monitor can assert this pin if it identifies a bus transfer that is hung.                                                                                                                                                                                                                                                                                                                                                                                               |  |

| NMI      | Input        | Non-Maskable Interrupt<br>When an external device asserts this line, the MSC8103 NMI input is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| NMI_OUT  | Output       | Non-Maskable Interrupt<br>Driven from the MSC8103 internal interrupt controller. Assertion of this output indicates that a<br>non-maskable interrupt, pending in the MSC8103 internal interrupt controller, is waiting to be<br>handled by an external host.                                                                                                                                                                                                                                                                                                                                                       |  |

| PSDVAL   | Input/Output | Data Valid<br>Indicates that a data beat is valid on the data bus. The difference between the TA pin and PSDVAL<br>is that the TA pin is asserted to indicate data transfer terminations while the PSDVAL signal is<br>asserted with each data beat movement. Thus, when TA is asserted, PSDVAL is asserted, but when<br>PSDVAL is asserted, TA is not necessarily asserted. For example when the SDMA initiates a double<br>word (2x64 bits) transfer to a memory device that has a 32-bit port size, PSDVAL is asserted three<br>times without TA, and finally both pins are asserted to terminate the transfer. |  |

Table 1-7.

Port A Signals (Continued)

| Name                    |                                                        |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|--------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated Signal<br>Protocol | <ul> <li>Dedicated</li> <li>I/O Data</li> <li>Direction</li> </ul> | Description                                                                                                                                                                                                                                                                                                                                                                         |

| PA17                    | FCC1: RXD7<br>UTOPIA                                   | Input                                                              | <b>FCC1: UTOPIA Receive Data Bit 7.</b><br>The MSC8103 inputs ATM cell octets (UTOPIA interface data) on RXD[0–7]. RXD7 is the most significant bit. When no ATM data is available, idle cells are inserted. A cell is 53 bytes. To support Multi-PHY configurations, RXD[0–7] is tri-stated, enabled only when RXENB is asserted.                                                  |

|                         | FCC1: RXD0<br><i>MII</i> and <i>HDLC nibble</i>        | Input                                                              | FCC1: MII and HDLC Nibble Receive Data Bit 0<br>RXD[3–0] is supported by MII and HDLC nibble mode in FCC1. RXD0 is<br>the least significant bit.                                                                                                                                                                                                                                    |

|                         | FCC1: RXD<br>HDLC serial and transparent               | Input                                                              | FCC1: HDLC Serial and Transparent Receive Data Bit<br>This is the single receive data bit supported by HDLC and transparent<br>modes.                                                                                                                                                                                                                                               |

| PA16                    | FCC1: RXD6<br><i>UTOPIA</i>                            | Input                                                              | FCC1: UTOPIA Receive Data Bit 6.<br>The MSC8103 inputs ATM cell octets (UTOPIA interface data) on<br>RXD[0–7]. This is bit 6 of the receive data. RXD7 is the most significant<br>bit. When no ATM data is available, idle cells are inserted. A cell is 53<br>bytes. To support Multi-PHY configurations, RXD[0–7] is tri-stated,<br>enabled only when RXENB is asserted.          |

|                         | FCC1: RXD1<br><i>MII</i> and <i>HDLC nibble</i>        | Input                                                              | FCC1: MII and HDLC Nibble Receive Data Bit 1<br>This is bit 1 of the receive nibble data. RXD3 is the most significant bit.                                                                                                                                                                                                                                                         |

| PA15                    | FCC1: RXD5<br>UTOPIA                                   | Input                                                              | FCC1: UTOPIA Receive Data Bit 5<br>The MSC8103 inputs ATM cell octets (UTOPIA interface data) on<br>RXD[0–7]. This is bit 5 of the receive data. RXD7 is the most significant<br>bit. When no ATM data is available, idle cells are inserted. A cell is 53<br>bytes. To support Multi-PHY configurations, RXD[0–7] is tri-stated,<br>enabled only when RXENB is asserted.           |

|                         | RXD2<br>MII and HDLC nibble                            | Input                                                              | FCC1: MII and HDLC Nibble Receive Data Bit 2<br>This is bit 2 of the receive nibble data. RXD3 is the most significant bit.                                                                                                                                                                                                                                                         |

| PA14                    | FCC1: RXD4<br>UTOPIA                                   | Input                                                              | <b>FCC1: UTOPIA Receive Data Bit 4.</b><br>The MSC8103 inputs ATM cell octets (UTOPIA interface data) on<br>RXD[0–7]. RXD7 is the most significant bit. RXD0 is the least significant<br>bit. When no ATM data is available, idle cells are inserted. A cell is 53<br>bytes. To support Multi-PHY configurations, RXD[0–7] is tri-stated,<br>enabled only when RXENB is asserted.   |

|                         | FCC1: RXD3<br><i>MII</i> and <i>HDLC nibble</i>        | Input                                                              | FCC1: MII and HDLC Nibble Receive Data Bit 3<br>RXD3 is the most significant bit of the receive nibble bit.                                                                                                                                                                                                                                                                         |

| PA13                    | FCC1: RXD3<br>UTOPIA                                   | Input                                                              | <b>FCC1: UTOPIA Receive Data Bit 3</b><br>The MSC8103 inputs ATM cell octets (UTOPIA interface data) on<br>RXD[0–7]. RXD7 is the most significant bit. RXD0 is the least significant<br>bit. A cell is 53 bytes. To support Multi-PHY configurations, RXD[0–7] is<br>tri-stated, enabled only when RXENB is asserted.                                                               |

|                         | SDMA: MSNUM2                                           | Output                                                             | <b>Module Serial Number Bit 2</b><br>The MSNUM has 6 bits that identify devices using the serial DMA<br>(SDMA) modules. MSNUM[0–4] is the sub-block code of the current<br>peripheral controller using SDMA. MSNUM5 indicates the section,<br>transmit (0) or receive (1), that is active during the transfer. The<br>information is recorded in the SDMA transfer error registers. |

| Table 1-8. | Port B Signals | (Continued) |

|------------|----------------|-------------|

|------------|----------------|-------------|

| Name                    |                                                           | Dedicated                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated I/O<br>Protocol       | <ul> <li>Dedicated</li> <li>I/O Data</li> <li>Direction</li> </ul> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PB28                    | FCC2: RTS<br>HDLC serial, HDLC nibble, and<br>transparent | Output                                                             | <b>FCC2:</b> Request to Send<br>One of the standard modem interface signals supported by FCC2 ( $\overline{\text{RTS}}$ , $\overline{\text{CTS}}$ , and $\overline{\text{CD}}$ ). $\overline{\text{RTS}}$ is asynchronous with the data. $\overline{\text{RTS}}$ is typically used in conjunction with $\overline{\text{CD}}$ . The MSC8103 FCC2 transmitter requests the receiver to send data by asserting $\overline{\text{RTS}}$ low. The request is accepted when $\overline{\text{CTS}}$ is returned low. |

|                         | FCC2: RX_ER<br><i>MII</i>                                 | Input                                                              | FCC2: Media Independent Interface Receive Error<br>Asserted by an external fast Ethernet PHY to indicate a receive error,<br>which often indicates bad wiring.                                                                                                                                                                                                                                                                                                                                                  |

|                         | SCC2: RTS, TENA                                           | Output                                                             | <b>SCC2: Request to Send, Transmit Enable</b><br>Typically used in conjunction with CD supported by SCC2. The<br>MSC8103 SCC2 transmitter requests the receiver to send data by<br>asserting RTS low. The request is accepted when CTS is returned low.<br>TENA is the signal used in Ethernet mode.                                                                                                                                                                                                            |

|                         | SI2 TDMB2: L1TSYNC<br><i>TDM serial</i>                   | Input                                                              | <b>Time-Division Multiplexing B2: Layer 1 Transmit Synchronization</b><br>The synchronizing signal for the transmit channel. See the serial<br>interface with time-slot assigner chapter in the <i>MSC8103 Reference</i><br><i>Manual.</i>                                                                                                                                                                                                                                                                      |

| PB27                    | FCC2: COL<br>MII                                          | Input                                                              | FCC2: Media Independent Interface Collision Detect<br>Asserted by an external fast Ethernet PHY when a collision is detected.                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | SI2 TDMC2: L1TXD<br><i>TDM serial</i>                     | Output                                                             | Time-Division Multiplexing C2: Layer 1 Transmit Data<br>TDMC2 transmits serial data out of L1TXD.                                                                                                                                                                                                                                                                                                                                                                                                               |

| PB26                    | FCC2: CRS<br>MII                                          | Input                                                              | FCC2: Media Independent Interface Carrier Sense Input<br>Asserted by an external fast Ethernet PHY to indicate activity on the<br>cable.                                                                                                                                                                                                                                                                                                                                                                        |

|                         | SI2 TDMC2: L1RXD<br>TDM serial                            | Input                                                              | <b>Time-Division Multiplexing C2: Layer 1 Receive Data</b><br>TDMC2 receives serial data from L1RXD.                                                                                                                                                                                                                                                                                                                                                                                                            |

| PB25                    | FCC2: TXD3<br><i>MII</i> and <i>HDLC nibble</i>           | Output                                                             | FCC2: MII and HDLC Nibble Transmit Data Bit 3<br>TXD3 is bit 3 and the most significant bit of the transmit data nibble.                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | SI1 TDMA1: L1TXD3                                         | Output                                                             | <b>Time-Division Multiplexing A1: Nibble Layer 1 Transmit Data Bit 3</b><br>L1TXD3 is bit 3 and the most significant bit of the transmit data nibble.                                                                                                                                                                                                                                                                                                                                                           |

|                         | TDM nibble<br>SI2 TDMC2: L1TSYNC<br>TDM serial            | Input                                                              | <b>Time-Division Multiplexing C2: Layer 1 Transmit Synchronization</b><br>The synchronizing signal for the transmit channel. See the <i>Serial</i><br><i>Interface with Time-Slot Assigner</i> chapter in the <i>MSC8103 Reference</i><br><i>Manual.</i>                                                                                                                                                                                                                                                        |

| PB24                    | FCC2: TXD2<br><i>MII</i> and <i>HDLC nibble</i>           | Output                                                             | FCC2: MII and HDLC Nibble: Transmit Data Bit 2<br>TXD2 is bit 2 of the transmit data nibble.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | SI1 TDMA1: L1RXD3<br>nibble                               | Input                                                              | Time-Division Multiplexing A1: Nibble Layer 1 Receive Data Bit 3<br>L1RXD3 is bit 3 and the most significant bit of the receive data nibble.                                                                                                                                                                                                                                                                                                                                                                    |

|                         | SI2 TDMC2: L1RSYNC<br>serial                              | Input                                                              | <b>Time-Division Multiplexing C2: Layer 1 Receive Synchronization</b><br>The synchronizing signal for the receive channel.                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1-9.

Port C Signals (Continued)

| Name                    |                                                            | Dedicated                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------------------|------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated I/O<br><i>Protocol</i> | Dedicated<br>I/O Data<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| PC22                    | SI1: L1ST1                                                 | Output                             | Serial Interface 1: Layer 1 Strobe 1<br>The MSC8103 time-slot assigner supports up to four strobe outputs that<br>can be asserted on a bit or byte basis. The strobe outputs are useful for<br>interfacing to other devices that do not support the multiplexed interface or<br>for enabling/disabling three-state I/O buffers in a multiple-transmitter<br>architecture. These strobes can also generate output wave forms for such<br>applications as stepper-motor control.    |  |

|                         | CLK10                                                      | Input                              | <b>Clock 10</b><br>The CPM supports up to 10 clock input pins sent to the bank-of-clocks selection logic, where they can be routed to the controllers.                                                                                                                                                                                                                                                                                                                            |  |

|                         | DMA: DREQ1                                                 | Input/ Output                      | DMA: Request 1<br>DACK1, DREQ1, DRACK1, and DONE1 belong to the SIU DMA controller.<br>DONE1 and DRACK1 are signals on the same pin and therefore cannot be<br>used simultaneously. There are two sets of DMA pins associated with the<br>PIO ports.                                                                                                                                                                                                                              |  |

| PC15                    | SMC2: SMTXD                                                | Output                             | SMC2: Serial Management Transmit Data<br>The SMC interface consists of SMTXD, SMRXD, SMSYN, and a clock. Not<br>all signals are used for all applications. SMCs are full-duplex ports that<br>support three protocols or modes: UART, transparent, or general-circuit<br>interface (GCI). See also PA9.                                                                                                                                                                           |  |

|                         | SCC1: CTS/CLSN                                             | Input                              | SCC1: Clear To Send, Collision<br>Typically used in conjunction with RTS. The MSC8103 SCC1 transmitter<br>sends out a request to send data signal (RTS). The request is accepted<br>when CTS is returned low. CLSN is the signal used in Ethernet mode. See<br>also PC29.                                                                                                                                                                                                         |  |

|                         | FCC1: TXADDR0<br>UTOPIA master                             | Output                             | FCC1: UTOPIA Master Transmit Address Bit 0<br>This is master transmit address bit 0.                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                         | FCC1: TXADDR0<br><i>UTOPIA slave</i>                       | Input                              | FCC1: UTOPIA Slave Transmit Address Bit 0<br>This is slave transmit address bit 0.                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PC14                    | SI1: L1ST2                                                 | Output                             | Serial Interface 1: Layer 1 Strobe 2<br>The MSC8103 time-slot assigner supports up to four strobe outputs that<br>can be asserted on a bit or byte basis. The strobe outputs are useful for<br>interfacing to other devices that do not support the multiplexed interface or<br>for enabling/disabling three-state I/O buffers in a multiple-transmitter<br>architecture. These strobes can also be generate output wave forms for<br>such applications as stepper-motor control. |  |

|                         | SCC1: CD, RENA                                             | Input                              | <b>SCC1: Carrier Detect, Receive Enable</b><br>Typically used in conjunction with RTS supported by SCC1. The<br>MSC8103MSC8103 SCC1 transmitter requests the receiver to send data<br>by asserting RTS low. The request is accepted when CTS is returned low.                                                                                                                                                                                                                     |  |

|                         | FCC1: RXADDR0<br>UTOPIA master                             | Output                             | FCC1: UTOPIA Multi-PHY Master Receive Address Bit 0<br>This is master receive address bit 0.                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                         | FCC1: RXADDR0<br><i>UTOPIA slave</i>                       | Input                              | FCC1: UTOPIA Multi-PHY Slave Receive Address Bit 0<br>This is slave receive address bit 0.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Table 1-10. | Port D Signals | (Continued) |

|-------------|----------------|-------------|

|-------------|----------------|-------------|

|                         | Name                                                        | Dedicated                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------|-------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated I/O<br>Protocol         | Dedicated<br>I/O Data<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PD19                    | FCC1: TXADDR4<br>UTOPIA master                              | Output                             | FCC1: Multi-PHY Master Transmit Address Bit 4 Multiplexed Polling<br>This is master transmit address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                         | FCC1: TXADDR4<br><i>UTOPIA slave</i>                        | Input                              | FCC1: UTOPIA Slave Transmit Address Bit 4<br>This is slave transmit address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                         | FCC1: TXCLAV3<br>UTOPIA multi-PHY master, direct<br>polling | Input                              | FCC1: UTOPIA Multi-PHY master Transmit Cell Available 3 Direct<br>Polling<br>Asserted by an external UTOPIA slave PHY to indicate that it can accept<br>one complete ATM cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                         | BRG1O                                                       | Output                             | <b>Baud Rate Generator 1 Output</b><br>The CPM supports up to 8 BRGs for use internally by the bank-of-clocks<br>selection logic and/or to provide an output to one of the 8 BRG pins.<br>BRG10 can be the internal input to the SIU timers. When CLK5 is<br>selected (see PC27 above), it is the source for BRG10 which is the<br>default input for the SIU timers. See the system interface unit (SIU)<br>chapter in the <i>MSC8103 Reference Manual</i> for additional information. If<br>CLK5 is not enabled, BRG10 uses an internal input. If TMCLK is<br>enabled (see PC26 above), the BRG10 input to the SIU timers is<br>disabled. |  |

|                         | SPI: SPISEL                                                 | Input                              | SPI: Select<br>The SPI interface comprises four signals: master out slave in<br>(SPIMOSI), master in slave out (SPIMISO), clock (SPICLK) and select<br>(SPISEL). The SPI can be configured as a slave or master in single- or<br>multiple-master environments. SPISEL is the enable input to the SPI<br>slave. In a multimaster environment, SPISEL (always an input) detects<br>an error when more than one master is operating. SPI masters must<br>output a slave select signal to enable SPI slave devices by using a<br>separate general-purpose I/O signal. Assertion of an SPI SPISEL while<br>it is master causes an error.        |  |

| PD18                    | FCC1: RXADDR4<br>UTOPIA master                              | Output                             | FCC1: UTOPIA Master Receive Address Bit 4<br>This is master receive address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                         | FCC1: RXADDR4<br>UTOPIA slave                               | Input                              | FCC1: UTOPIA Slave Receive Address Bit 4<br>This is slave receive address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                         | FCC1: RXCLAV3<br>UTOPIA multi-PHY master, direct<br>polling | Input                              | FCC1: UTOPIA Multi-PHY Master Receive Cell Available 3 Direct<br>Polling<br>Asserted by an external PHY when one complete ATM cell is available<br>for transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                         | SPI: SPICLK                                                 | Input/ Output                      | SPI: Clock<br>The SPI interface comprises four signals: master out slave in<br>(SPIMOSI), master in slave out (SPIMISO), clock (SPICLK) and select<br>(SPISEL). The SPI can be configured as a slave or master in single- or<br>multiple-master environments. SPICLK is a gated clock, active only<br>during data transfers. Four combinations of SPICLK phase and polarity<br>can be configured. When the SPI is a master, SPICLK is the clock<br>output signal that shifts received data in from SPIMISO and transmitted<br>data out to SPIMOSI.                                                                                         |  |

# Physical and Electrical Specifications 2

This document contains detailed information on environmental limits, power considerations, DC/AC electrical characteristics, and AC timing specifications for the MSC8103 communications processor, mask set 2K87M. For additional information, see the *MSC8103 Reference Manual*.

## 2.1 Absolute Maximum Ratings

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist. **Table 2-1** describes the maximum electrical ratings for the MSC8103.

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | Symbol             | Value              | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------------|------|

| Core supply v                                                                                                                                                                                                                                                                                                                                                                                                                            | oltage <sup>3</sup> | V <sub>DD</sub>    | -0.2 to 1.7        | V    |

| PLL supply vo                                                                                                                                                                                                                                                                                                                                                                                                                            | ltage <sup>3</sup>  | V <sub>CCSYN</sub> | -0.2 to 1.7        | V    |

| I/O supply vol                                                                                                                                                                                                                                                                                                                                                                                                                           | tage <sup>3</sup>   | V <sub>DDH</sub>   | -0.2 to 3.6        | V    |

| Input voltage <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                               |                     | V <sub>IN</sub>    | (GND – 0.2) to 3.6 | V    |

| Maximum operating temperature range <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                         |                     | TJ                 | -40 to 120         | °C   |

| Storage temperature range                                                                                                                                                                                                                                                                                                                                                                                                                |                     | T <sub>STG</sub>   | -55 to +150        | °C   |

| <ol> <li>Functional operating conditions are given in Table 2-2.</li> <li>Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.</li> <li>The input voltage must not exceed the I/O supply V<sub>DDH</sub> by more than 2.5 V at any time, including during power-on reset. In</li> </ol> |                     |                    |                    |      |

| Table 2-1. Absolute Maximum Ratings | able 2-1. | Absolute Maximum Ratings <sup>2</sup> |

|-------------------------------------|-----------|---------------------------------------|

|-------------------------------------|-----------|---------------------------------------|

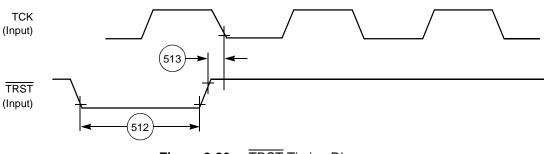

3. The input voltage must not exceed the I/O supply V<sub>DDH</sub> by more than 2.5 V at any time, including during power-on reset. In turn, V<sub>DDH</sub> can exceed V<sub>DD</sub>/V<sub>CCSYN</sub> by more than 3.3 V during power-on reset, but for no more than 100 ms. V<sub>DDH</sub> should not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> by more than 2.1 V during normal operation. V<sub>DD</sub>/V<sub>CCSYN</sub> must not exceed V<sub>DDH</sub> by more than 0.4 V at any time, including during power-on reset. See Section 4.2, *Electrical Design Considerations*, on page 4-1 for more information.

4. Section 4.1, *Thermal Design Considerations*, on page 4-1 includes a formula for computing the chip junction temperature (T<sub>.</sub>).

| _ | _ |        | _  |  |

|---|---|--------|----|--|

|   |   |        |    |  |

|   |   |        | 7  |  |

|   |   |        | Δ. |  |

|   |   | $\sim$ |    |  |

|                                                                                                                                                       |                | Maximum Rated Core Frequency             |                                                |                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------|------------------------------------------------|-------------------------------------------|--|

| Clock                                                                                                                                                 | Symbol         | All                                      | Max. Values for SC140 Clock Rating of:         |                                           |  |

|                                                                                                                                                       |                | Min                                      | 275 MHz                                        | 300 MHz                                   |  |

| Input Clock                                                                                                                                           | CLKIN          | 18 MHz                                   | 91.67 MHz                                      | 100 MHz                                   |  |

| SPLL MF Clock                                                                                                                                         | SPLLMFCLK      | 18 MHz                                   | 34.38 MHz                                      | 37.5 MHz                                  |  |

| Bus/Output                                                                                                                                            | BCLK<br>CLKOUT | 18 MHz                                   | 91.67 MHz                                      | 100 MHz                                   |  |

| Serial Communications Controller                                                                                                                      | SCLK           | 35 MHz                                   | 91.67 MHz                                      | 100 MHz                                   |  |

| Communications Processor Module                                                                                                                       | CPMCLK         | 70 MHz                                   | 183.3 MHz                                      | 200 MHz                                   |  |

| SC140 Core                                                                                                                                            | DSPCLK         | 72 MHz                                   | 275 MHz                                        | 300 MHz                                   |  |

| <ul> <li>Baud Rate Generator</li> <li>For BRG DF = 4</li> <li>For BRG DF = 16 (default)</li> <li>For BRG DF = 64</li> <li>For BRG DF = 256</li> </ul> | BRGCLK         | 36 MHz<br>9 MHz<br>2.25 MHz<br>562.5 KHz | 91.67 MHz<br>22.91 MHz<br>5.73 MHz<br>1.43 MHz | 100 MHz<br>25 MHz<br>6.25 MHz<br>1.56 MHz |  |

Table 2-11.Clock Ranges

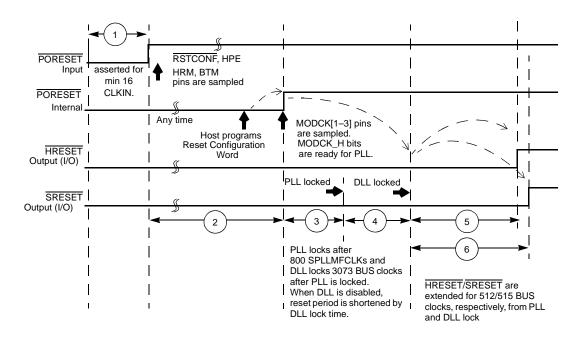

### 2.6.4 Reset Timing

The MSC8103 has several inputs to the reset logic:

- Power-on reset (PORESET)

- External hard reset (HRESET)

- External soft reset (SRESET)

Asserting an external PORESET causes concurrent assertion of an internal PORESET signal, HRESET, and SRESET. When the external PORESET signal is deasserted, the MSC8103 samples several configuration pins:

- RSTCONF—determines whether the MSC8103 is a master (0) or slave (1) device

- DBREQ—determines whether to operate in normal mode (0) or invoke the SC140 debug mode (1)

- HPE—disable (0) or enable (1) the host port (HDI16)

- BTM[0–1]—boot from external memory (00) or the HDI16 (01)

All these reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the last sources to cause a reset. **Table 2-12** describes reset causes.

Table 2-12. Reset Causes

| Name                        | Direction    | Description                                                                                                                                                                            |

|-----------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET) | Input        | PORESET initiates the power-on reset flow that resets all the MSC8103s and configures various attributes of the MSC8103, including its clock mode.                                     |

| Hard reset<br>(HRESET)      | Input/Output | The MSC8103 can detect an external assertion of HRESET only if it occurs while the MSC8103 is not asserting reset. During HRESET, SRESET is asserted. HRESET is an open-<br>drain pin. |

| Soft reset<br>(SRESET)      | Input/Output | The MSC8103 can detect an external assertion of SRESET only if it occurs while the MSC8103 is not asserting reset. SRESET is an open-drain pin.                                        |

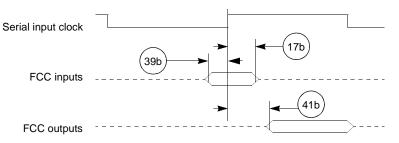

### ical and Electrical Specifications

Figure 2-7. Host Reset Configuration Timing

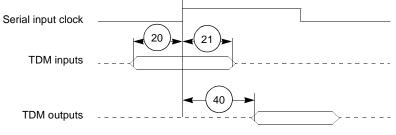

Figure 2-20. SCC/SMC/SPI/I<sup>2</sup>C Internal Clock Diagram

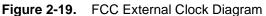

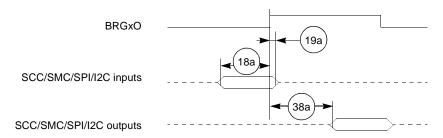

Figure 2-21. SCC/SMC/SPI/I<sup>2</sup>C External Clock Diagram

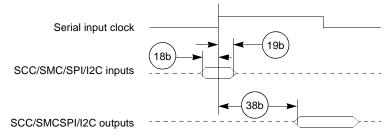

Figure 2-22. TDM Signal Diagram

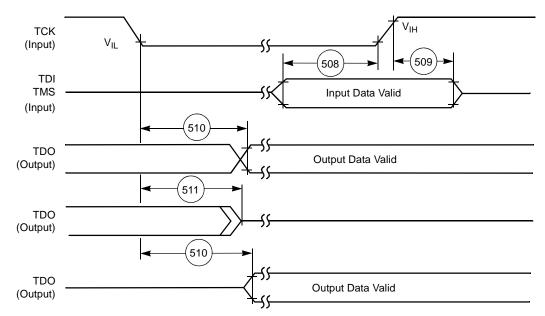

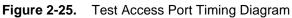

Figure 2-26. TRST Timing Diagram

| Signal Name | Number |

|-------------|--------|

| D42         | A12    |

| D43         | D13    |

| D44         | C13    |

| D45         | B13    |

| D46         | A13    |

| D47         | E14    |

| D48         | D14    |

| D49         | C14    |

| D50         | B14    |