Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                               |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | SC140 Core                                                             |

| Interface               | Communications Processor Module (CPM)                                  |

| Clock Rate              | 300MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 512kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.60V                                                                  |

| Operating Temperature   | -40°C ~ 75°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 332-BFBGA, FCBGA                                                       |

| Supplier Device Package | 332-FCBGA (17x17)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8103vt1200f |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **MSC8103 Features**

- SC140 core

- Architecture optimized for efficient C/C++ code compilation

- Four 16-bit ALUs and two 32-bit AGUs

- 1200 DSP MMACS running at 300 MHz

- Very low power dissipation

- Variable-length execution set (VLES) execution model

- JTAG/Enhanced OnCE debug port

- Communications processor module (CPM)

- Programmable protocol machine using a 32-bit RISC engine

- 155 Mbps ATM interface (including AAL 0/1/2/5)

- 10/100 Mbit Ethernet interface

- Up to four E1/T1 interfaces or one E3/T3 interface and one E1/T1 interface

- HDLC support up to T3 rates, or 256 channels

- 64- or 32-bit wide bus interface

- Support for bursts for high efficiency

- Glueless interface to 60x-compatible bus systems

- Multi-master support

- Programmable memory controller

- Control for up to eight banks of external memory

- User-programmable machines (UPM) allowing glueless interface to various memory types (SRAM, DRAM, EPROM, and Flash memory) and other user-definable peripherals

- Dedicated pipelined SDRAM memory interface

- Large internal SRAM

- 256K 16-bit words (512 KB)

- Unified program and data space configurable by the application

- Word and byte addressable

- DMA controller

- 16 DMA channels, FIFO based, with burst capabilities

- Sophisticated addressing capabilities

- Small foot print package

- 17 mm × 17 mm lidded FC-PBGA package with lead-bearing or lead-free spheres

- Very low power consumption

- Separate power supply for internal logic (1.6 V) and for I/O (3.3 V)

- Enhanced 16-bit parallel host interface (HDI16)

- Supports a variety of microcontroller, microprocessor, and DSP bus interfaces

- Phase-lock loops (PLLs)

- System PLL

- CPM DPLLs (SCC and SCM)

- Process technology

- 0.13 micron copper interconnect process technology

# Signals/Connections

The MSC8103 external signals are organized into functional groups, as shown in **Table 1-1**, **Figure 1-1**, and **Figure 1-2**. **Table 1-1** lists the functional groups, states the number of signal connections in each group, and references the table that gives details on multiplexed signals within each group. **Figure 1-1** shows MSC8103 external signals organized by function. **Figure 1-2** indicates how the parallel input/output (I/O) ports signals are multiplexed. Because the parallel I/O design supported by the MSC8103 communications processor module (CPM) is a subset of the parallel I/O signals supported by the MPC8260 device, port pins are not numbered sequentially.

| Functional Group                                        | Number of Signal<br>Connections | Detailed Description   |                         |  |

|---------------------------------------------------------|---------------------------------|------------------------|-------------------------|--|

| Power (V <sub>CC</sub> , V <sub>DD</sub> , and GND)     |                                 | 80                     | Table 1-2 on page 1-4   |  |

| Clock                                                   |                                 | 6                      | Table 1-3 on page 1-4   |  |

| Reset, configuration, and EOnCE                         |                                 | 11                     | Table 1-4 on page 1-5   |  |

| System bus, HDI16, and interrupts                       | 133                             | Table 1-5 on page 1-7  |                         |  |

| Memory controller                                       | 27                              | Table 1-6 on page 1-13 |                         |  |

| CPM input/output parallel ports                         | Port A                          | 26                     | Table 1-7 on page 1-16  |  |

|                                                         | Port B                          | 14                     | Table 1-8 on page 1-21  |  |

|                                                         | Port C                          | 18                     | Table 1-9 on page 1-24  |  |

|                                                         | Port D                          | 8                      | Table 1-10 on page 1-33 |  |

| JTAG test access port (TAP)                             |                                 | 5                      | Table 1-11 on page 1-36 |  |

| Reserved (denotes connections that are always reserved) |                                 | 5                      | Table 1-12 on page 1-36 |  |

| Table 1-1. | MSC8103 Functional | Signal Groupings |

|------------|--------------------|------------------|

|------------|--------------------|------------------|

## 1.1 Power Signals

| Power Name          | Description                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>     | Internal Logic Power<br>$V_{DD}$ dedicated for use with the device core. The voltage should be well-regulated and the input should be provided with<br>an extremely low impedance path to the $V_{DD}$ power rail.                                                   |

| V <sub>DDH</sub>    | Input/Output Power<br>This source supplies power for the I/O buffers. The user must provide adequate external decoupling capacitors.                                                                                                                                 |

| V <sub>CCSYN</sub>  | System PLL Power<br>V <sub>CC</sub> dedicated for use with the system Phase Lock Loop (PLL). The voltage should be well-regulated and the input<br>should be provided with an extremely low impedance path to the V <sub>CC</sub> power rail.                        |

| V <sub>CCSYN1</sub> | SC140 PLL Power<br>$V_{CC}$ dedicated for use with the SC140 core PLL. The voltage should be well-regulated and the input should be provided<br>with an extremely low impedance path to the V <sub>CC</sub> power rail.                                              |

| GND                 | System Ground<br>An isolated ground for the internal processing logic. This connection must be tied externally to all chip ground<br>connections, except GND <sub>SYN</sub> and GND <sub>SYN1</sub> . The user must provide adequate external decoupling capacitors. |

| GND <sub>SYN</sub>  | System PLL Ground<br>Ground dedicated for system PLL use. The connection should be provided with an extremely low-impedance path to<br>ground.                                                                                                                       |

| GND <sub>SYN1</sub> | SC140 PLL Ground 1<br>Ground dedicated for SC140 core PLL use. The connection should be provided with an extremely low-impedance path<br>to ground.                                                                                                                  |

#### Table 1-2. Power and Ground Signal Inputs

## 1.2 Clock Signals

| Signal Name | Туре   | Signal Description                                                                                                         |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| CLKIN       | Input  | Clock In<br>Primary clock input to the MSC8103 PLL.                                                                        |

| MODCK1      | Input  | Clock Mode Input 1<br>Defines the operating mode of internal clock circuits.                                               |

| тсо         | Output | <b>Transfer Code 0</b><br>Supplies information that can be useful for debugging bus transactions initiated by the MSC8103. |

| BNKSEL0     | Output | Bank Select 0<br>Selects the SDRAM bank when the MSC8103 is in 60x-compatible bus mode.                                    |

| MODCK2      | Input  | Clock Mode Input 2<br>Defines the operating mode of internal clock circuits.                                               |

| TC1         | Output | <b>Transfer Code 1</b><br>Supplies information that can be useful for debugging bus transactions initiated by the MSC8103. |

| BNKSEL1     | Output | Bank Select 1<br>Selects the SDRAM bank when the MSC8103 is in 60x-compatible bus mode.                                    |

| MODCK3      | Input  | Clock Mode Input 3<br>Defines the operating mode of internal clock circuits.                                               |

| TC2         | Output | <b>Transfer Code 2</b><br>Supplies information that can be useful for debugging bus transactions initiated by the MSC8103. |

| BNKSEL2     | Output | Bank Select 2<br>Selects the SDRAM bank when the MSC8103 is in 60x-compatible bus mode.                                    |

#### Table 1-3. Clock Signals

als/Connections

| Signal Name      | Туре             | Signal Description                                                                                                                                                                                                                              |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTM[0-1]         | Input            | <b>Boot Mode 0–1</b><br>Determines the MSC8103 boot mode when PORESET is deasserted. See the emulation and debug chapter in the <i>SC140 DSP Core Reference Manual</i> for details on how to set these pins.                                    |

| EE4 <sup>1</sup> |                  | <b>EOnCE Event 4</b><br>After PORESET is deasserted, you can configure EE4 as an input (default) or an output. See the emulation and debug chapter in the <i>SC140 DSP Core Reference Manual</i> for details on the ETRSMT Register.            |

|                  | Input            | Enable Address Event Detection Channel 4 or generate an EOnCE event.                                                                                                                                                                            |

|                  | Output           | The DSP wrote the EOnCE Transmit Register (ETRSMT). Triggers external debugging equipment.                                                                                                                                                      |

| EE5 <sup>1</sup> |                  | EOnCE Event 5<br>After PORESET is deasserted, you can configure EE5 as an input (default) or an output.                                                                                                                                         |

|                  | Input            | Enable Address Event Detection Channel 5.                                                                                                                                                                                                       |

|                  | Output           | Detection by Address Event Detection Channel 5. Triggers external debugging equipment.                                                                                                                                                          |

| EED <sup>1</sup> |                  | Enhanced OnCE (EOnCE) Event Detection<br>After PORESET is deasserted, you can configure EED as an input (default) or output:                                                                                                                    |

|                  | Input            | Enable the Data Event Detection Channel.                                                                                                                                                                                                        |

|                  | Output           | Detection by the Data Event Detection Channel. Triggers external debugging equipment.                                                                                                                                                           |

| PORESET          | Input            | Power-On Reset<br>When asserted, this line causes the MSC8103 to enter power-on reset state.                                                                                                                                                    |

| RSTCONF          | Input            | Reset Configuration<br>Used during reset configuration sequence of the chip. A detailed explanation of its function is<br>provided in the "Power-On Reset Flow" and "Hardware Reset Configuration" sections of the<br>MSC8103 Reference Manual. |

| HRESET           | Input            | Hard Reset<br>When asserted, this open-drain line causes the MSC8103 to enter the hard reset state.                                                                                                                                             |

| SRESET           | Input            | Soft Reset<br>When asserted, this open-drain line causes the MSC8103 to enter the soft reset state.                                                                                                                                             |

| Note: See the e  | mulation and deb | ug chapter in the SC140 DSP Core Reference Manual for details on how to configure these pins.                                                                                                                                                   |

Table 1-4.

Reset, Configuration, and EOnCE Event Signals (Continued)

### 1.4 System Bus, HDI16, and Interrupt Signals

The system bus, HDI16, and interrupt signals are grouped together because they use a common set of signal lines. Individual assignment of a signal to a specific signal line is configured through registers in the System Interface Unit (SIU) and the Host Interface (HDI16). 1-5 describes the signals in this group.

Note: To boot from the host interface, the HDI16 must be enabled by pulling up the HPE signal line during PORESET. The configuration word must then be loaded from the host. The configuration word must set the Internal Space Port Size bit in the Bus Control Register (BCR[ISPS]) to change the system data bus width from 64 bits to 32 bits and reassign the upper 32 bits to their HDI16 functions. Never set the Host Port Enable (HEN) bit in the Host Port Control Register (HPCR) to enable the HDI16, unless the bus size is first changed from 64 bits to 32 bits. Otherwise, unpredictable operation may occur.

Table 1-7.

Port A Signals (Continued)

| Name                    |                                                        | Dedicated                          |                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------|--------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated Signal<br>Protocol | Dedicated<br>I/O Data<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PA27                    | FCC1: RXSOC<br>UTOPIA slave                            | Output                             | <b>FCC1: UTOPIA Receive Start of Cell</b><br>Asserted by the MSC8103 (UTOPIA slave) for an external PHY when<br>RXD[0–7] contains the first valid byte of the cell.                                                                                                                                                                                                          |  |  |

|                         | FCC1: RX_DV<br>MII                                     | Input                              | <b>FCC1: Media Independent Interface Receive Data Valid</b><br>Asserted by an external fast Ethernet PHY to indicate that valid data is<br>being sent. The presence of carrier sense but not RX_DV indicates<br>reception of broken packet headers, probably due to bad wiring or a bad<br>circuit.                                                                          |  |  |

| PA26                    | FCC1: RXCLAV<br>UTOPIA slave                           | Output                             | <b>FCC1: UTOPIA Slave Receive Cell Available</b><br>Asserted by the MSC8103 (UTOPIA slave PHY) when one complete<br>ATM cell is available for transfer.                                                                                                                                                                                                                      |  |  |

|                         | FCC1: RXCLAV<br>UTOPIA master, or                      | Input                              | FCC1: UTOPIA Master Receive Cell Available<br>Asserted by an external PHY when one complete ATM cell is available<br>for transfer.                                                                                                                                                                                                                                           |  |  |

|                         | RXCLAV0<br>UTOPIA master, Multi-PHY, direct<br>polling | Input                              | FCC1: UTOPIA Master Receive Cell Available 0 Direct Polling<br>Asserted by an external PHY when one complete ATM cell is available<br>for transfer.                                                                                                                                                                                                                          |  |  |

|                         | FCC1: RX_ER<br>MII                                     | Input                              | FCC1: Media Independent Interface Receive Error<br>Asserted by an external fast Ethernet PHY to indicate a receive error,<br>which often indicates bad wiring.                                                                                                                                                                                                               |  |  |

| PA25                    | FCC1: TXD0<br><i>UTOPIA</i>                            | Output                             | <b>FCC1: UTOPIA Transmit Data Bit 0</b><br>The MSC8103 outputs ATM cell octets (UTOPIA interface data) on TXD[0–7]. TXD0 is the least significant bit. When no ATM data is available, idle cells are inserted. A cell is 53 bytes.                                                                                                                                           |  |  |

|                         | SDMA: MSNUM0                                           | Output                             | Module Serial Number Bit 0<br>The MSNUM has 6 bits that identify devices using the serial DMA<br>(SDMA) modules. MSNUM[0–4] is the sub-block code of the current<br>peripheral controller using SDMA. MSNUM5 indicates the section,<br>transmit (0) or receive (1), that is active during the transfer. The<br>information is recorded in the SDMA transfer error registers. |  |  |

| PA24                    | FCC1: TXD1<br>UTOPIA                                   | Output                             | <b>FCC1: UTOPIA Transmit Data Bit 1</b><br>The MSC8103 outputs ATM cell octets (UTOPIA interface data) on TXD[0–7]. This is bit 1 of the transmit data. TXD7 is the most significant bit. When no ATM data is available, idle cells are inserted. A cell is 53 bytes.                                                                                                        |  |  |

|                         | SDMA: MSNUM1                                           | Output                             | Module Serial Number Bit 1<br>The MSNUM has 6 bits that identify devices using the serial DMA<br>(SDMA) modules. MSNUM[0–4] is the sub-block code of the current<br>peripheral controller using SDMA. MSNUM5 indicates the section,<br>transmit (0) or receive (1), that is active during the transfer. The<br>information is recorded in the SDMA transfer error registers. |  |  |

| PA23                    | FCC1: TXD2<br>UTOPIA                                   | Output                             | <b>FCC1: UTOPIA Transmit Data Bit 2</b><br>The MSC8103 outputs ATM cell octets (UTOPIA interface data) on TXD[0–7]. This is bit 2 of the transmit data. TXD7 is the most significant bit. When no ATM data is available, idle cells are inserted. A cell is 53 bytes.                                                                                                        |  |  |

als/Connections

| Table 1-9. | Port C Signals | (Continued) |

|------------|----------------|-------------|

|------------|----------------|-------------|

| Name                    |                                                            | Dedicated             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------------------|------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated I/O<br><i>Protocol</i> | I/O Data<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PC5                     | SMC1: SMTXD                                                | Output                | SMC1: Transmit Data<br>The SMC interface consists of SMTXD, SMRXD, SMSYN, and a clock. Not<br>all signals are used for all applications. SMCs are full-duplex ports that<br>supports three protocols or modes: UART, transparent, or general-circuit<br>interface (GCI).                                                                                                                                                                                                       |  |  |

|                         | SI2: L1ST3                                                 | Output                | Serial Interface 2: Layer 1 Strobe 3<br>The MSC8103 time-slot assigner supports up to four strobe outputs that<br>can be asserted on a bit or byte basis. The strobe outputs are useful for<br>interfacing to other devices that do not support the multiplexed interface or<br>for enabling/disabling three-state I/O buffers in a multiple-transmitter<br>architecture. These strobes can also generate output wave forms for such<br>applications as stepper-motor control. |  |  |

|                         | FCC2: CTS<br>HDLC serial, HDLC nibble,<br>and transparent  | Input                 | FCC2: Clear To Send<br>In th <u>e</u> standard modem interface signals supported by FCC2 (RTS, CTS,<br>and CD). CTS is asynchronous with the data.                                                                                                                                                                                                                                                                                                                             |  |  |

| PC4                     | SMC1: SMRXD                                                | Input                 | SMC1: Receive Data<br>The SMC interface consists of SMTXD, SMRXD, SMSYN, and a clock. Not<br>all signals are used for all applications. SMCs are full-duplex ports that<br>supports three protocols or modes: UART, transparent, or general-circuit<br>interface (GCI).                                                                                                                                                                                                        |  |  |

|                         | SI2: L1ST4                                                 | Output                | Serial Interface 2: Layer 1 Strobe 4<br>The MSC8103 time-slot assigner supports up to four strobe outputs that<br>can be asserted on a bit or byte basis. The strobe outputs are useful for<br>interfacing to other devices that do not support the multiplexed interface or<br>for enabling/disabling three-state I/O buffers in a multiple-transmitter<br>architecture. These strobes can also generate output wave forms for such<br>applications as stepper-motor control. |  |  |

|                         | FCC2: CD<br>HDLC serial, HDLC nibble,<br>and transparent   | Input                 | FCC2: Carrier Detect<br>In the standard modem interface signals supported by FCC2 ( $\overline{\text{RTS}}$ , $\overline{\text{CTS}}$<br>and $\overline{\text{CD}}$ ). $\overline{\text{CD}}$ is asynchronous with the data.                                                                                                                                                                                                                                                   |  |  |

| Table 1-10. | Port D Signals | (Continued) |

|-------------|----------------|-------------|

|-------------|----------------|-------------|

| Name                    |                                                             | Dedicated                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------|-------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General-<br>Purpose I/O | Peripheral Controller:<br>Dedicated I/O<br>Protocol         | Dedicated<br>I/O Data<br>Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PD19                    | FCC1: TXADDR4<br>UTOPIA master                              | Output                             | FCC1: Multi-PHY Master Transmit Address Bit 4 Multiplexed Polling<br>This is master transmit address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                         | FCC1: TXADDR4<br><i>UTOPIA slave</i>                        | Input                              | FCC1: UTOPIA Slave Transmit Address Bit 4<br>This is slave transmit address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                         | FCC1: TXCLAV3<br>UTOPIA multi-PHY master, direct<br>polling | Input                              | FCC1: UTOPIA Multi-PHY master Transmit Cell Available 3 Direct<br>Polling<br>Asserted by an external UTOPIA slave PHY to indicate that it can accept<br>one complete ATM cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                         | BRG1O                                                       | Output                             | <b>Baud Rate Generator 1 Output</b><br>The CPM supports up to 8 BRGs for use internally by the bank-of-clocks<br>selection logic and/or to provide an output to one of the 8 BRG pins.<br>BRG10 can be the internal input to the SIU timers. When CLK5 is<br>selected (see PC27 above), it is the source for BRG10 which is the<br>default input for the SIU timers. See the system interface unit (SIU)<br>chapter in the <i>MSC8103 Reference Manual</i> for additional information. If<br>CLK5 is not enabled, BRG10 uses an internal input. If TMCLK is<br>enabled (see PC26 above), the BRG10 input to the SIU timers is<br>disabled. |  |  |

|                         | SPI: SPISEL                                                 | Input                              | SPI: Select<br>The SPI interface comprises four signals: master out slave in<br>(SPIMOSI), master in slave out (SPIMISO), clock (SPICLK) and select<br>(SPISEL). The SPI can be configured as a slave or master in single- or<br>multiple-master environments. SPISEL is the enable input to the SPI<br>slave. In a multimaster environment, SPISEL (always an input) detects<br>an error when more than one master is operating. SPI masters must<br>output a slave select signal to enable SPI slave devices by using a<br>separate general-purpose I/O signal. Assertion of an SPI SPISEL while<br>it is master causes an error.        |  |  |

| PD18                    | FCC1: RXADDR4<br>UTOPIA master                              | Output                             | FCC1: UTOPIA Master Receive Address Bit 4<br>This is master receive address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                         | FCC1: RXADDR4<br>UTOPIA slave                               | Input                              | FCC1: UTOPIA Slave Receive Address Bit 4<br>This is slave receive address bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                         | FCC1: RXCLAV3<br>UTOPIA multi-PHY master, direct<br>polling | Input                              | FCC1: UTOPIA Multi-PHY Master Receive Cell Available 3 Direct<br>Polling<br>Asserted by an external PHY when one complete ATM cell is available<br>for transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                         | SPI: SPICLK                                                 | Input/ Output                      | SPI: Clock<br>The SPI interface comprises four signals: master out slave in<br>(SPIMOSI), master in slave out (SPIMISO), clock (SPICLK) and select<br>(SPISEL). The SPI can be configured as a slave or master in single- or<br>multiple-master environments. SPICLK is a gated clock, active only<br>during data transfers. Four combinations of SPICLK phase and polarity<br>can be configured. When the SPI is a master, SPICLK is the clock<br>output signal that shifts received data in from SPIMISO and transmitted<br>data out to SPIMOSI.                                                                                         |  |  |

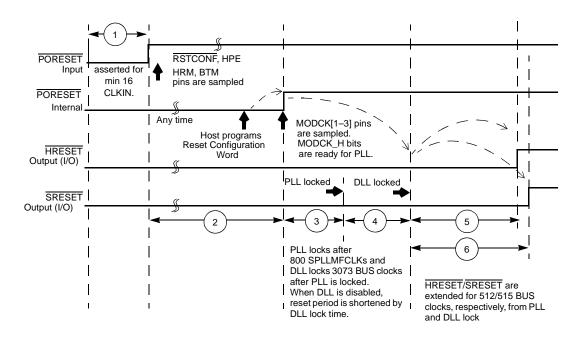

| No.                                                                                                                                                                                                                                       | Characteristics                                                                                                                                                                                                               | Expression                | Min      | Max                      | Unit                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|--------------------------|----------------------|

| 4                                                                                                                                                                                                                                         | Delay from SPLL lock to DLL lock <ul> <li>DLL enabled</li> <li>BCLK = 18 MHz</li> <li>BCLK = 75 MHz</li> <li>DLL disabled</li> </ul>                                                                                          | 3073 / BLCK<br>—          | 40       | ).72<br>.97<br>.0        | μs<br>μs<br>ns       |

| 5                                                                                                                                                                                                                                         | <ul> <li>Delay from SPLL lock to HRESET deassertion</li> <li>DLL enabled <ul> <li>BCLK = 18 MHz</li> <li>BCLK = 75 MHz</li> </ul> </li> <li>DLL disabled <ul> <li>BCLK = 18 MHz</li> <li>BCLK = 75 MHz</li> </ul> </li> </ul> | 3585 / BLCK<br>512 / BLCK | 47       | 0.17<br>7.5<br>8.4<br>83 | μs<br>μs<br>μs<br>μs |

| 6                                                                                                                                                                                                                                         | <ul> <li>Delay from SPLL lock to SRESET deassertion</li> <li>DLL enabled <ul> <li>BCLK = 18 MHz</li> <li>BCLK = 75 MHz</li> </ul> </li> <li>DLL disabled <ul> <li>BCLK = 18 MHz</li> <li>BCLK = 75 MHz</li> </ul> </li> </ul> | 3588 / BLCK<br>515 / BLCK | 47<br>28 | ).33<br>.84<br>.61<br>87 | μs<br>μs<br>μs<br>μs |

| Note:         Value given for lowest possible CLKIN frequency 18 MHz to ensure proper initialization of reset sequence.         Value given for lowest possible CLKIN frequency 18 MHz to ensure proper initialization of reset sequence. |                                                                                                                                                                                                                               |                           |          |                          |                      |

| Table 2-14. | Reset Timing | (Continued) |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

### 2.6.4.3 Host Reset Configuration

Host reset configuration allows the host to program the reset configuration word via the Host port after PORESET is deasserted, as described in the *MSC8103 Reference Manual*. The MSC8103 samples the signals described in **Table 2-13** one the rising edge of PORESET when the signal is deasserted.

If HPE is sampled high, the host port is enabled. In this mode the RSTCONF pin *must* be pulled up. The device extends the internal PORESET until the host programs the reset configuration word register. The host must write four 8-bit half-words to the Host Reset Configuration Register address to program the reset configuration word, which is 32 bits wide. For more information, see the *MSC8103 Reference Manual*. The reset configuration word is programmed before the internal PLL and DLL in the MSC8103 are locked. The host must program it after the rising edge of the PORESET input. In this mode, the host must have its own clock that does not depend on the MSC8103 clock. After the PLL and DLL are locked, HRESET remains asserted for another 512 bus clocks and is then released. The SRESET is released three bus clocks later (see Figure 2-7).

#### ical and Electrical Specifications

Figure 2-7. Host Reset Configuration Timing

#### AC Timings

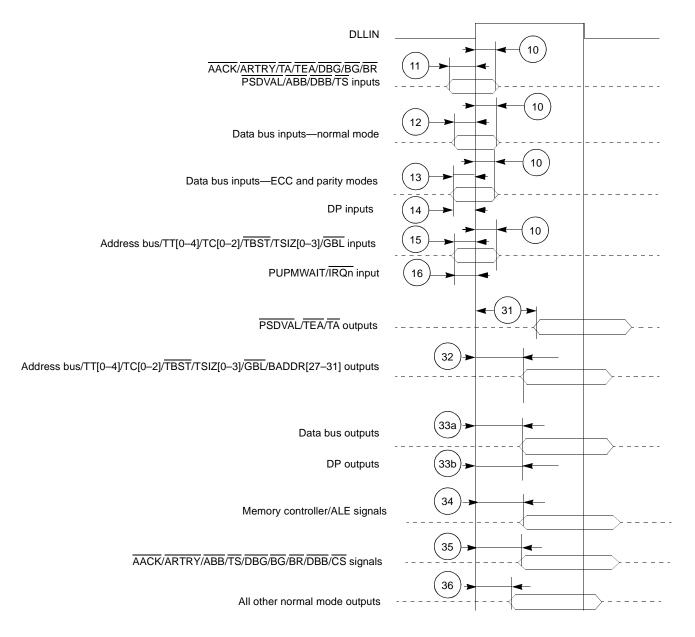

Figure 2-10. Bus Signal Timing

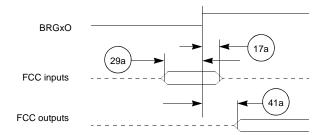

### 2.6.7 CPM Timings

| No.   | Characteristic                                                                                                                                            | Typical | Unit     |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|--|--|

| 39    | FCC input set-up time before low-to-high clock transition<br>a. internal clock (BRGxO)<br>b. external clock (serial clock input)                          | 10<br>5 | ns<br>ns |  |  |

| 17    |                                                                                                                                                           |         |          |  |  |

| 18    | SCC/SMC/SPI/I <sup>2</sup> C input set-up time before low-to-high clock transition<br>a. internal clock (BRGxO)<br>b. external clock (serial clock input) | 20<br>5 | ns<br>ns |  |  |

| 19    | SCC/SMC/SPI/I <sup>2</sup> C input hold time after low-to-high clock transition<br>a. internal clock (BRGxO)<br>b. external clock (serial clock input)    | 0<br>5  | ns<br>ns |  |  |

| 20    | TDM input set-up time before low-to-high serial clock transition                                                                                          | 5       | ns       |  |  |

| 21    | TDM input hold time after low-to-high serial transition                                                                                                   | 5       | ns       |  |  |

| 22    | PIO/TIMER/DMA input set-up time before low-to-high serial clock transition                                                                                | 10      | ns       |  |  |

| 23    | PIO/TIMER/DMA input hold time after low-to-high serial clock transition                                                                                   | 3       | ns       |  |  |

| Note: | FCC, SCC, SMC, SPI, I <sup>2</sup> C are non-multiplexed serial interface signals.                                                                        |         |          |  |  |

| Table 2-20. | CPM Input Characteristics |

|-------------|---------------------------|

|-------------|---------------------------|

Table 2-21. CPM Output Characteristics

| No.   | Characteristic                                                                                                                                      | Min    | Max      | Unit     |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|----------|--|--|

| 41    | FCC output delay after low-to-high clock transition<br>a. internal clock (BRGxO)<br>b. external clock (serial input clock)                          | 0<br>2 | 6<br>18  | ns<br>ns |  |  |

| 38    | SCC/SMC/SPI/I <sup>2</sup> C output delay after low-to-high clock transition<br>a. internal clock (BRGxO)<br>b. external clock (serial input clock) | 0<br>0 | 20<br>30 | ns<br>ns |  |  |

| 40    | 40 TDM output delay after low-to-high serial clock transition                                                                                       |        |          | ns       |  |  |

| 42    | PIO/TIMER/DMA output delay after low-to-high serial clock transition                                                                                | 1      | 14       | ns       |  |  |

| Note: | Note: FCC, SCC, SMC, SPI, I <sup>2</sup> C are Non-Multiplexed Serial Interface signals.                                                            |        |          |          |  |  |

Figure 2-18. FCC Internal Clock Diagram

# Packaging

This chapter provides information about the MSC8103 package, including diagrams of the package pinouts and tables showing how the signals discussed in **Chapter 1** are allocated. The MSC8103 is available in a 332-pin lidded flip chip-plastic ball grid array (FC-PBGA).

### 3.1 FC-PBGA Package Description

**Figure 3-1** and **Figure 3-2** show top and bottom views of the FC-PBGA package, including pinouts. **Table 3-1** lists the MSC8103 signals alphabetically by signal name. Connections with multiple names are listed individually by each name. Signals with programmable polarity are shown both as signals which are asserted low (default) and high (that is, NAME/NAME). **Table 3-2** lists the signals numerically by pin number. Each pin number is listed once with the various signals that are multiplexed to it. For simplicity, signals with programmable polarity are shown in this table only with their default name (asserted low).

Note: The package description in this chapter applies to packages with lead-bearing and lead-free spheres.

| Signal Name | Number |

|-------------|--------|

| D8          | D6     |

| D9          | C6     |

| D10         | B6     |

| D11         | A6     |

| D12         | G7     |

| D13         | E7     |

| D14         | D7     |

| D15         | C7     |

| D16         | B7     |

| D17         | A7     |

| D18         | F8     |

| D19         | D8     |

| D20         | C8     |

| D21         | B8     |

| D22         | A8     |

| D23         | G9     |

| D24         | D9     |

| D25         | C9     |

| D26         | В9     |

| D27         | A9     |

| D28         | F10    |

| D29         | D10    |

| D30         | C10    |

| D31         | B10    |

| D32         | A10    |

| D33         | G11    |

| D34         | D11    |

| D35         | C11    |

| D36         | B11    |

| D37         | A11    |

| D38         | F12    |

| D39         | D12    |

| D40         | C12    |

| D41         | B12    |

Table 3-1.

MSC8103 Signal Listing By Name (Continued)

| Signal Name                   | Number |

|-------------------------------|--------|

| RXD3 for FCC2 MII/HDLC nibble | R4     |

| RXD4 for FCC1 UTOPIA 8        | W8     |

| RXD5 for FCC1 UTOPIA 8        | W3     |

| RXD6 for FCC1 UTOPIA 8        | M7     |

| RXD7 for FCC1 UTOPIA 8        | T4     |

| RXENB for FCC1                | K1     |

| RXPRTY for FCC1 UTOPIA 8      | N7     |

| RXSOC for FCC1                | L1     |

| SCL                           | R4     |

| SDA                           | U2     |

| SMRXD for SMC1                | P10    |

| SMRXD for SMC2                | U10    |

| SMSYN for SMC1                | V9     |

| SMSYN for SMC2                | V10    |

| SMTXD for SMC1                | W10    |

| SMTXD for SMC2                | W9     |

| SMTXD for SMC2                | V3     |

| SPARE1                        | R2     |

| SPARE5                        | U11    |

| SPICLK                        | U3     |

| SPIMISO                       | U4     |

| SPIMOSI                       | N7     |

| SPISEL                        | V2     |

| SRESET                        | W4     |

| TA                            | J13    |

| TBST                          | U13    |

| TC0                           | E18    |

| TC1                           | F18    |

| TC2                           | G18    |

| ТСК                           | G4     |

| TDI                           | H6     |

| TDO                           | F1     |

| TEA                           | G17    |

| TEST                          | W6     |

Table 3-1.

MSC8103 Signal Listing By Name (Continued)

| Signal Name      | Number |

|------------------|--------|

| V <sub>DD</sub>  | H16    |

| V <sub>DD</sub>  | J4     |

| V <sub>DD</sub>  | L16    |

| V <sub>DD</sub>  | L4     |

| V <sub>DD</sub>  | N4     |

| V <sub>DD</sub>  | P16    |

| V <sub>DD</sub>  | R11    |

| V <sub>DD</sub>  | R13    |

| V <sub>DD</sub>  | R8     |

| V <sub>DDH</sub> | E10    |

| V <sub>DDH</sub> | E11    |

| V <sub>DDH</sub> | E13    |

| V <sub>DDH</sub> | E15    |

| V <sub>DDH</sub> | E4     |

| V <sub>DDH</sub> | E6     |

| V <sub>DDH</sub> | E8     |

| V <sub>DDH</sub> | G15    |

| V <sub>DDH</sub> | G16    |

| V <sub>DDH</sub> | G5     |

| V <sub>DDH</sub> | J15    |

| V <sub>DDH</sub> | J16    |

| V <sub>DDH</sub> | K16    |

| V <sub>DDH</sub> | K5     |

| V <sub>DDH</sub> | M4     |

| V <sub>DDH</sub> | N15    |

| V <sub>DDH</sub> | N16    |

| V <sub>DDH</sub> | R10    |

| V <sub>DDH</sub> | R12    |

| V <sub>DDH</sub> | R14    |

| V <sub>DDH</sub> | R15    |

| V <sub>DDH</sub> | R6     |

| V <sub>DDH</sub> | R7     |

| V <sub>DDH</sub> | R9     |

| V <sub>DDH</sub> | T15    |

Table 3-1.

MSC8103 Signal Listing By Name (Continued)

| Number | Signal Name                              |  |  |  |  |

|--------|------------------------------------------|--|--|--|--|

| E5     | V <sub>DD</sub>                          |  |  |  |  |

| E6     | V <sub>DDH</sub>                         |  |  |  |  |

| E7     | D13                                      |  |  |  |  |

| E8     | V <sub>DDH</sub>                         |  |  |  |  |

| E9     | V <sub>DD</sub>                          |  |  |  |  |

| E10    | V <sub>DDH</sub>                         |  |  |  |  |

| E11    | V <sub>DDH</sub>                         |  |  |  |  |

| E12    | V <sub>DD</sub>                          |  |  |  |  |

| E13    | V <sub>DDH</sub>                         |  |  |  |  |

| E14    | D47 / HD15                               |  |  |  |  |

| E15    | V <sub>DDH</sub>                         |  |  |  |  |

| E16    | D56 / HACK / HRRQ                        |  |  |  |  |

| E17    | PSDA10 / PGPL0                           |  |  |  |  |

| E18    | MODCK1 / TC0 / BNKSEL0                   |  |  |  |  |

| E19    | PSDCAS / PGPL3                           |  |  |  |  |

| F1     | TDO                                      |  |  |  |  |

| F2     | EED                                      |  |  |  |  |

| F3     | BTM1 / EE5                               |  |  |  |  |

| F4     | V <sub>DD</sub>                          |  |  |  |  |

| F5     | GND                                      |  |  |  |  |

| F6     | IRQ7 / DP7 / DACK4                       |  |  |  |  |

| F7     | GND                                      |  |  |  |  |

| F8     | D18                                      |  |  |  |  |

| F9     | GND                                      |  |  |  |  |

| F10    | D28                                      |  |  |  |  |

| F11    | GND                                      |  |  |  |  |

| F12    | D38 / HD6                                |  |  |  |  |

| F13    | GND                                      |  |  |  |  |

| F14    | PSDWE / PGPL1                            |  |  |  |  |

| F15    | GND                                      |  |  |  |  |

| F16    | V <sub>DD</sub>                          |  |  |  |  |

| F17    | PWE7 / PSDDQM7 / PBS7                    |  |  |  |  |

| F18    | MODCK2 / TC1 / BNKSEL1                   |  |  |  |  |

| F19    | BCTL0                                    |  |  |  |  |

| G1     | PA31 / FCC1:UTOPIA8:TXENB / FCC1:MII:COL |  |  |  |  |

| G2     | TMS                                      |  |  |  |  |

| G3     | TRST                                     |  |  |  |  |

| G4     | ТСК                                      |  |  |  |  |

| G5     | V <sub>DDH</sub>                         |  |  |  |  |

Table 3-2.

MSC8103 Signal Listing by Pin Designator (Continued)

| Number | Signal Name                                                                      |  |  |  |

|--------|----------------------------------------------------------------------------------|--|--|--|

| M7     | PA16 / FCC1:UTOPIA8:RXD6 / FCC1:MII and HDLC nibble:RXD1                         |  |  |  |

| M13    | A21                                                                              |  |  |  |

| M14    | A26                                                                              |  |  |  |

| M15    | GND                                                                              |  |  |  |

| M16    | CS0                                                                              |  |  |  |

| M17    | CS5                                                                              |  |  |  |

| M18    | CS7                                                                              |  |  |  |

| M19    | CS4                                                                              |  |  |  |

| N1     | PC25 / DMA: DACK2 / BRG7O / CLK7 / TIN4                                          |  |  |  |

| N2     | PA25 / FCC1:UTOPIA8:TXD0 / SDMA:MSNUM0                                           |  |  |  |

| N3     | PB25 / FCC2:MII and HDLC nibble:TXD3 / TDMA1:nibble:L1TXD3 / TDMC2:L1TSYNC       |  |  |  |

| N4     | V <sub>DD</sub>                                                                  |  |  |  |

| N5     | PC23 / EXT2 / DMA:DACK1 / CLK9                                                   |  |  |  |

| N6     | GND                                                                              |  |  |  |

| N7     | PD17 / FCC1:UTOPIA8:RXPRTY / SPI:SPIMOSI / BRG2O                                 |  |  |  |

| N8     | CLKIN                                                                            |  |  |  |

| N9     | GND                                                                              |  |  |  |

| N10    | PC6 / FCC1:UTOPIA8:RXADDR2 / FCC1:UTOPIA8:RXADDR2/RXCLAV1<br>FCC1:CD / SI2:LIST2 |  |  |  |

| N11    | TSIZ3                                                                            |  |  |  |

| N12    | TT1                                                                              |  |  |  |

| N13    | тто                                                                              |  |  |  |

| N14    | A1                                                                               |  |  |  |

| N15    | V <sub>DDH</sub>                                                                 |  |  |  |

| N16    | V <sub>DDH</sub>                                                                 |  |  |  |

| N17    | A28                                                                              |  |  |  |

| N18    | A30                                                                              |  |  |  |

| N19    | A31                                                                              |  |  |  |

| P1     | PC24 / DMA:DREQ2 / BRG8O / CLK8 / TIN3/TOUT4                                     |  |  |  |

| P2     | PA24 / FCC1:UTOPIA8:TXD1 / SDMA:MSNUM1                                           |  |  |  |

| P3     | PB24 / FCC2:MII and HDLC nibble:TXD2 / TDMA1:nibble:L1RXD3 / TDMC2:L1RSYNC       |  |  |  |

| P4     | PA23 / FCC1:UTOPIA8:TXD2                                                         |  |  |  |

| P5     | PB20 / FCC2:MII and HDLC nibble:RXD1 / TDMA1:nibble:L1TXD1 / TDMD2:L1RSYNC       |  |  |  |

| P6     | GND                                                                              |  |  |  |

| P7     | GND                                                                              |  |  |  |

| P8     | DLLIN                                                                            |  |  |  |

| P9     | GND                                                                              |  |  |  |

Table 3-2.

MSC8103 Signal Listing by Pin Designator (Continued)

### 3.2 Lidded FC-PBGA Package Mechanical Drawing

Notes: 1. Dimensioning and tolerancing per ASME Y14.5M–1994.

2. Dimensions in millimeters.

A Maximum solder ball diameter measured parallel to Datum A.

A Primary Datum A and the seating plane are defined by the spherical crowns of the solder balls.

#### CASE 1473-01

Figure 3-3. Case 1473-01 Mechanical Information, 332-pin Lidded FC-PBGA Package

### **Ordering Information**

For product availability, consult a Freescale Semiconductor sales office or authorized distributor.

| Part    | Supply<br>Voltage | Package Type                  | Pin<br>Count | Mask<br>Set | Sphere Type | Core<br>Frequency<br>(MHz) | Order Number   |

|---------|-------------------|-------------------------------|--------------|-------------|-------------|----------------------------|----------------|

| MSC8103 | 1.6 V core        | Lidded Flip Chip Plastic Ball | 332          | 2K87M       | Pb-bearing  | 275                        | MSC8103M1100F  |

|         | 3.3 V I/O         | Grid Array (FC-PBGA)          |              |             | Pb-free     | 275                        | MSC8103VT1100F |

|         |                   |                               |              |             | Pb-bearing  | 300                        | MSC8103M1200F  |

|         |                   |                               |              |             | Pb-free     | 300                        | MSC8103VT1200F |

#### How to Reach Us:

Home Page:

www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

MSC8103 Rev. 12 8/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup>, the Freescale logo, and StarCore are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2001, 2008.