#### Zilog - EZ80L92AZ020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processore280Core Size8-BitSpeed20MHzConnectivityEBI/EMI, I°C, IrDA, SPI, UART/USARTPeripheralsDMA, WDTNumber of I/O24Program Memory Size-Program Memory TypeROMIessEEPROM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case10-LQFPPurchase URLhttps://www.e-xfl.com/product-detail/zilog/ez80/92a2020sg |                            |                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivityEBI/EMI, I²C, IrDA, SPI, UART/USARTPeripheralsDMA, WDTNumber of I/O24Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSuppler Device Package-                                                                           | Product Status             | Active                                                    |

| Speed20MHzConnectivityEBI/EMI, I²C, IrDA, SPI, UART/USARTPeripheralsDMA, WDTNumber of I/O24Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                        | Core Processor             | eZ80                                                      |

| ConnectivityEBI/EMI, I²C, IrDA, SPI, UART/USARTPeripheralsDMA, WDTNumber of I/O24Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                  | Core Size                  | 8-Bit                                                     |

| PeripheralsDMA, WDTNumber of I/O24Program Memory Size-Program Memory TypeROMlessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                 | Speed                      | 20MHz                                                     |

| Number of I/O24Program Memory Size-Program Memory TypeROMlessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                    | Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART          |

| Program Memory Size-Program Memory TypeROMlessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                   | Peripherals                | DMA, WDT                                                  |

| Program Memory TypeROMlessEEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                       | Number of I/O              | 24                                                        |

| EEPROM Size-RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                 | Program Memory Size        | -                                                         |

| RAM Size-Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                             | Program Memory Type        | ROMIess                                                   |

| Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                                      | EEPROM Size                | -                                                         |

| Data Converters-Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                                                                         | RAM Size                   | · .                                                       |

| Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                                                                                         | Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Operating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package-                                                                                                                                                                                                                                                                                                                                | Data Converters            | -                                                         |

| Mounting Type     Surface Mount       Package / Case     100-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                  |

| Package / Case     100-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                   | Mounting Type              | Surface Mount                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | Package / Case             | 100-LQFP                                                  |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/ez80l92az020sg                                                                                                                                                                                                                                                                                                                                                                      | Supplier Device Package    | •                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80l92az020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Four other block transfer instructions are modified to improve performance related to the eZ80190 device. These modified instructions are:

- IND2R (input from I/O, decrement the memory address, decrement the I/O address, and repeat).

- INI2R (input from I/O, increment the memory address, increment the I/O address, and repeat).

- OTD2R (output to I/O, decrement the memory address, decrement the I/O address, and repeat).

- OTI2R (output to I/O, increment the memory address, increment the I/O address, and repeat).

For more information on the eZ80 CPU, its instruction set, and eZ80 programming, refer to the  $eZ80^{\ensuremath{\mathbb{R}}}$  CPU User Manual. For more information on the eZ80190, refer to the eZ80190 Product Specification.

## **Low-Power Modes**

The eZ80L92 MCU provides a range of power-saving features. The highest level of power reduction is provided by SLEEP mode. The next level of power reduction is provided by the HALT instruction. The lowest level of power reduction is provided by the clock peripheral power-down registers.

## SLEEP Mode

Execution of the eZ80 CPU's SLP instruction places the eZ80L92 MCU into SLEEP mode. In SLEEP mode, the operating characteristics are:

- Primary crystal oscillator is disabled.

- System clock is disabled.

- eZ80 CPU is idle.

- Program counter (PC) stops incrementing.

- 32 kHz crystal oscillator continues to operate and drives the Real-Time Clock and the Watchdog Timer (if WDT is configured to operate from the 32 kHz oscillator.)

The eZ80 CPU can be brought out of SLEEP mode by any of the following operations:

- RESET through the external RESET pin driven Low.

- RESET through a Real-Time Clock alarm.

- RESET through a Watchdog Timer time-out (if running off of the 32 kHz oscillator and configured to generate a RESET upon time-out).

- RESET through execution of a Debug RESET command.

After exiting SLEEP mode, the standard RESET delay occurs to allow the primary crystal oscillator to stabilize. See Reset on page 33.

#### HALT Mode

Execution of the eZ80 CPU's HALT instruction places the eZ80L92 MCU into HALT mode. In HALT mode, the operating characteristics are:

- Primary crystal oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ80 CPU is idle.

- Program counter stops incrementing.

# **Chip Selects and Wait States**

The eZ80L92 MCU generates four Chip Selects for external devices. Each Chip Select is programmed to access either memory space or I/O space. The Memory Chip Selects can be individually programmed on a 64 KB boundary. Each I/O Chip Select can choose a 256-byte section of I/O space. In addition, each Chip Select can be programmed for up to 7 wait states.

## Memory and I/O Chip Selects

Each of the Chip Selects is enabled for either the memory address space or the I/O address space, but not both. To select the memory address space for a particular Chip Select,  $CSx\_IO$  ( $CSx\_CTL[4]$ ) must be reset to 0. To select the I/O address space for a particular Chip Select,  $CSx\_IO$  must be set to 1. After RESET, the default is for all Chip Selects to be configured for the memory address space. For either the memory address space or the I/O address space, the individual Chip Selects must be enabled by setting  $CSx\_EN$  ( $CSx\_CTL[3]$ ) to 1.

## **Memory Chip Select Operation**

Operation of each Memory Chip Selects is controlled by three control registers. To enable a particular Memory Chip Select, following conditions must be fulfilled:

- The Chip Select is enabled by setting CSx\_EN to 1.

- The Chip Select is configured for Memory by clearing CSx\_IO to 0.

- The address is in the associated Chip Select range:

$CSx\_LBR[7:0] \le ADDR[23:16] \le CSx\_UBR[7:0]$

- No higher priority (lower number) Chip Select meets the above conditions.

- A memory access instruction must be executing.

If all the above conditions are met to generate a Memory Chip Select, then the following actions occur:

- The appropriate Chip Select— $\overline{CS0}$ ,  $\overline{CS1}$ ,  $\overline{CS2}$ , or  $\overline{CS3}$ —is asserted (driven Low).

- MREQ is asserted (driven Low).

- Depending upon the instruction, either  $\overline{RD}$  or  $\overline{WR}$  is asserted (driven Low).

If the upper and lower bounds are set to the same value ( $CSx\_UBR = CSx\_LBR$ ), then a particular Chip Select is valid for a single 64 KB page.

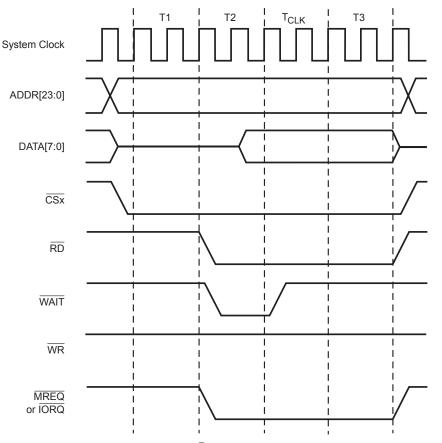

Figure 7. Z80<sup>®</sup> Bus Mode Read Timing Example

determine the source of the NMI event, provided that the last RESET was not caused by the WDT.

## Watchdog Timer Registers

#### Watchdog Timer Control Register

The Watchdog Timer Control register, described in Table 27, is an 8-bit Read/Write register used to enable the Watchdog Timer, set the time-out period, indicate the source of the most recent RESET, and select the required operation upon WDT time-out.

Table 27. Watchdog Timer Control Register (WDT\_CTL = 0093h)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2 | 1   | 0   |  |

|------------|-----|-----|-----|-----|-----|---|-----|-----|--|

| Reset      | 0   | 0   | 0/1 | 0   | 0   | 0 | 0   | 0   |  |

| CPU Access | R/W | R/W | R   | R/W | R/W | R | R/W | R/W |  |

|            |     |     |     |     |     |   |     |     |  |

Note: R = Read only; R/W = Read/Write.

| Bit<br>Position       | Value | Description                                                                                                                                                                      |

|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                     | 0     | WDT is disabled.                                                                                                                                                                 |

| WDT_EN                | 1     | WDT is enabled. When enabled, the WDT cannot be disabled without a full RESET.                                                                                                   |

| 6                     | 0     | WDT time-out resets the CPU.                                                                                                                                                     |

| NMI_OUT               | 1     | WDT time-out generates a nonmaskable interrupt (NMI) to the CPU.                                                                                                                 |

| 5                     | 0     | RESET caused by external full-chip reset or ZDI reset.                                                                                                                           |

| RST_FLAG <sup>*</sup> | 1     | RESET caused by WDT time-out. This flag is set by the WDT time-out, even if the NMI_OUT flag is set to 1. The CPU can poll this bit to determine the source of the RESET or NMI. |

| [4:3]                 | 00    | WDT clock source is system clock.                                                                                                                                                |

| WDT_CLK               | 01    | WDT clock source is Real-Time Clock source (32 kHz on-chip oscillator or 50/60Hz input as set by RTC_CTRL[4]).                                                                   |

| -                     | 10    | Reserved.                                                                                                                                                                        |

| -                     | 11    | Reserved.                                                                                                                                                                        |

| 2<br>RESERVED         | 0     | Reserved.                                                                                                                                                                        |

Note: \*RST\_FLAG is only cleared by a non-WDT RESET.

of the timer is achieved by loading 0001h. Maximum duration is achieved by loading 0000h, because the timer first rolls over to FFFFh and then continues counting down to 0000h.

The time-out period of the PRT is returned by the following equation:

PRT Time-Out Period = Clock Divider Ratio x Reload Value System Clock Frequency

To calculate the time-out period with the above equation when using an initial value of 0000h, enter a reload value of 65536 (FFFFh + 1).

Minimum time-out duration is 4 times longer than the input clock period and is generated by setting the clock divider ratio to 1:4 and the reload value to 0001h. Maximum time-out duration is  $2^{24}$  (16,777,216) times longer than the input clock period and is generated by setting the clock divider ratio to 1:256 and the reload value to 0000h.

#### SINGLE PASS Mode

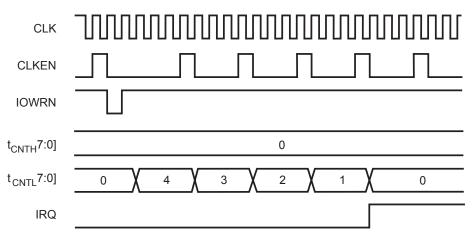

In SINGLE PASS mode, when the end-of-count value, 0000h, is reached, counting halts, the timer is disabled, and the PRT\_EN bit resets to 0. To restart the timer, the CPU must reenable the timer by setting the PRT\_EN bit to 1. An example of a PRT operating in SINGLE PASS mode is illustrated in Figure 19. Timer register information is indicated in Table 29.

Figure 19. PRT SINGLE PASS Mode Operation Example

| Parameter                  | Control Register(s)    | Value |

|----------------------------|------------------------|-------|

| PRT Enabled                | TMRx_CTL[0]            | 1     |

| Reload and Restart Enabled | TMRx_CTL[1]            | 1     |

| PRT Clock Divider = 4      | TMRx_CTL[3:2]          | 00b   |

| SINGLE PASS Mode           | TMRx_CTL[4]            | 0     |

| PRT Interrupt Enabled      | TMRx_CTL[6]            | 1     |

| PRT Reload Value           | {TMRx_RR_H, TMRx_RR_L} | 0004h |

#### Table 29. PRT SINGLE PASS Mode Operation Example

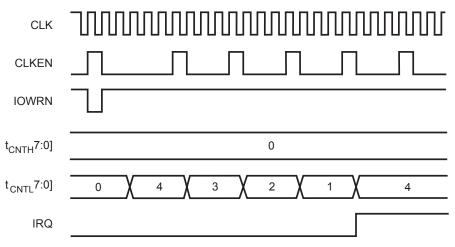

#### **CONTINUOUS Mode**

In CONTINUOUS mode, when the end-of-count value, 0000h, is reached, the timer automatically reloads the 16-bit start value from the Timer Reload registers, TMRx\_RR\_H and TMRx\_RR\_L. Downcounting continues on the next clock edge. In CONTINUOUS mode, the PRT continues to count until disabled. An example of a PRT operating in CONTINUOUS mode is illustrated in Figure 20. Timer register information is indicated in Table 30.

Figure 20. PRT CONTINUOUS Mode Operation Example

| Bit<br>Position    | Value   | Description                                                                                                                                                                                               |

|--------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_DR_H | 00h–FFh | These bits represent the High byte of the 2-byte timer data value, {TMRx_DR_H[7:0], TMRx_DR_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer data value. Bit 0 is bit 8 of the 16-bit timer data value. |

#### Timer Reload Registers—Low Byte

The Timer Reload Register—Low Byte, described in Table 35, stores the least significant byte (LSB) of the 2-byte timer reload value. In CONTINUOUS mode, the timer reload value is reloaded into the timer upon end-of-count. When RST\_EN (TMRx\_CTL[1]) is set to 1 to enable the automatic reload and restart function, the timer reload value is written to the timer on the next rising edge of the clock.

**Note:** The Timer Data registers and Timer Reload registers share the same address space.

Table 35. Timer Reload Registers—Low Byte (TMR0\_RR\_L = 0081h, TMR1\_RR\_L = 0084h, TMR2\_RR\_L = 0087h, TMR3\_RR\_L = 008Ah, TMR4\_RR\_L = 008Dh, or TMR5\_RR\_L = 0090h)

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write only. |   |   |   |   |   |   |   |   |

| Bit<br>Position    | Value   | Description                                                                                                                                                                                                   |

|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_RR_L | 00h–FFh | These bits represent the Low byte of the 2-byte timer reload value, {TMRx_RR_H[7:0], TMRx_RR_L[7:0]}. Bit 7 is bit 7 of the 16-bit timer reload value. Bit 0 is bit 0 (lsb) of the 16-bit timer reload value. |

## **Real Time Clock Month Register**

This register contains the current month count. See Table 43.

#### Table 43. Real Time Clock Month Register (RTC\_MON = 00E5h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read-only if RTC locked, Read/Write if RTC unlocked.

| Bit               |          |                                            |

|-------------------|----------|--------------------------------------------|

| Position          | Value    | Description                                |

| [7:4]<br>TENS_MON | 0–1      | The tens digit of the current month count. |

| [3:0]<br>MON      | 0–9      | The ones digit of the current month count. |

| Binary Operati    | on (BCD_ | EN = 0)                                    |

| Bit               |          |                                            |

| Position          | Value    | Description                                |

| [7:0]<br>MON      | 01h-0Ch  | The current month count.                   |

## **Real Time Clock Century Register**

This register contains the current century count. See Table 45.

#### Table 45. Real Time Clock Century Register (RTC\_CEN = 00E7h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read-only if RTC locked, Read/Write if RTC unlocked.

| Bit<br>Position   | Value    | Description                                  |

|-------------------|----------|----------------------------------------------|

| [7:4]<br>TENS_CEN | 0–9      | The tens digit of the current century count. |

| [3:0]<br>CEN      | 0–9      | The ones digit of the current century count. |

| Binary Operation  | on (BCD_ | _EN = 0)                                     |

| Bit<br>Position   | Value    | Description                                  |

| [7:0]<br>CEN      | 00h–63   | Che current century count.                   |

### Real Time Clock Alarm Hours Register

This register contains the alarm hours value. See Table 48.

#### Table 48. Real Time Clock Alarm Hours Register (RTC\_AHRS = 00EAh)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Reset      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |  |

| CPU Access | R/W |  |

|            |     |     |     |     |     |     |     |     |  |

**Note:** X = Unchanged by RESET; R/W = Read/Write.

| Bit<br>Position   | Value [    | Description                              |  |  |  |

|-------------------|------------|------------------------------------------|--|--|--|

| [7:4]<br>ATEN_HRS | 0–2 1      | The tens digit of the alarm hours value. |  |  |  |

| [3:0]<br>AHRS     | 0–9 1      | The ones digit of the alarm hours value. |  |  |  |

| Binary Operat     | ion (BCD_E | EN = 0)                                  |  |  |  |

| Bit<br>Position   | Value      | Description                              |  |  |  |

| [7:0]<br>AHRS     | 00h–17h    | The alarm hours value.                   |  |  |  |

### Real Time Clock Alarm Day-of-the-Week Register

This register contains the alarm day-of-the-week value. See Table 49.

# Table 49. Real Time Clock Alarm Day-of-the-Week Register (RTC\_ADOW = 00EBh)

| Bit                                                                                        | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|--------------------------------------------------------------------------------------------|---|---|---|---|------|------|------|------|

| Reset                                                                                      | 0 | 0 | 0 | 0 | Х    | Х    | Х    | Х    |

| CPU Access                                                                                 | R | R | R | R | R/W* | R/W* | R/W* | R/W* |

| Note: X = Unchanged by RESET; R = Read Only; R/W* = Read-only if RTC locked, Read/Write if |   |   |   |   |      |      |      |      |

RTC unlocked.

| Bit           |            |                                  |

|---------------|------------|----------------------------------|

| Position      | Value      | Description                      |

| [7:4]         | 0000       | Reserved.                        |

| [3:0]<br>ADOW | 1-7        | The alarm day-of-the-week.value. |

| Binary Oper   | ation (BCD | _EN = 0)                         |

| Bit           |            |                                  |

| Position      | Value      | Description                      |

|               |            |                                  |

| [7:4]         | 0000    | Reserved.                        |

|---------------|---------|----------------------------------|

| [3:0]<br>ADOW | 01h–07h | The alarm day-of-the-week value. |

CLK\_SEL and FREQ\_SEL select the RTC clock source. If the 32 kHz crystal option is selected the oscillator is enabled and the internal prescaler is set to divide by 32768. If the power-line frequency option is selected, the prescale value is set by FREQ\_SEL, and the 32 kHz oscillator is disabled. See Table 51.

| Bit               |                                  | 7                                                                                                    | 6         | 5                      | 4         | 3          | 2       | 1         | 0   |  |

|-------------------|----------------------------------|------------------------------------------------------------------------------------------------------|-----------|------------------------|-----------|------------|---------|-----------|-----|--|

| Reset             |                                  | X 0 X X X 0                                                                                          |           |                        |           |            |         | 0/1       | 0   |  |

| CPU Access        |                                  | R                                                                                                    | R/W       | R/W                    | R/W       | R/W        | R       | R         | R/W |  |

| Note: X = Unchang | ged by RE                        | SET; F                                                                                               | R = Read  | -only; R/\             | N = Read  | l/Write.   | 1       | 1         |     |  |

| Bit               |                                  |                                                                                                      |           |                        |           |            |         |           |     |  |

| Position          | Value                            | Des                                                                                                  | cription  | 1                      |           |            |         |           |     |  |

| 7                 | 0                                | Alar                                                                                                 | m interru | upt is ina             | active.   |            |         |           |     |  |

| ALARM             | 1                                | Alar                                                                                                 | m interru | upt is ac              | tive.     |            |         |           |     |  |

| 6                 | 0                                | Inte                                                                                                 | rupt on   | alarm co               | ondition  | is disable | ed.     |           |     |  |

| INT_EN            | 1                                | Inte                                                                                                 | rupt on   | alarm co               | ondition  | is enable  | ed.     |           |     |  |

| 5                 | 0                                | RTC count and alarm value registers are binary.                                                      |           |                        |           |            |         |           |     |  |

| BCD_EN            | 1                                | RTC count and alarm value registers are binary-coded decimal (BCD).                                  |           |                        |           |            |         |           |     |  |

| 4<br>CLK_SEL      | 0                                | RTC clock source is crystal oscillator output (32768 Hz).<br>On-chip 32768 Hz oscillator is enabled. |           |                        |           |            |         |           |     |  |

|                   | 1                                | RTC clock source is power-line frequency input.<br>On-chip 32768 Hz oscillator is disabled.          |           |                        |           |            |         |           |     |  |

| 3                 | 0                                | Pow                                                                                                  | er-line f | requenc                | y is 60H  | Z.         |         |           |     |  |

| FREQ_SEL          | 1 Power-line frequency is 50 Hz. |                                                                                                      |           |                        |           |            |         |           |     |  |

| 2                 | 0                                | Res                                                                                                  | erved.    |                        |           |            |         |           |     |  |

| 1                 | 0                                | RTC does not generate a Sleep-Mode Recovery reset.                                                   |           |                        |           |            |         |           |     |  |

| SLP_WAKE          | 1                                | RTC                                                                                                  | CAlarm    | generate               | es a Slee | ep-Mode    | Recove  | ery reset |     |  |

| 0<br>RTC_UNLOCK   | 0                                | RTC count registers are locked to prevent write access.<br>RTC counter is enabled.                   |           |                        |           |            |         | SS.       |     |  |

|                   | 1                                |                                                                                                      |           | egisters<br>r is disal |           | ocked to   | allow w | rite acce | SS. |  |

## **SPI Signals**

The four basic SPI signals are:

- MISO (Master-In/Slave-Out)

- MOSI (Master-Out/Slave-In)

- SCK (SPI Serial Clock)

- $\overline{SS}$  (Slave Select)

The following section describes the SPI signals. Each signal is described in both MASTER and SLAVE modes.

#### Master-In, Slave-Out

The Master-In/Slave-Out (MISO) pin is configured as an input in a master device and as an output in a slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. The MISO pin of a slave device is placed in a high-impedance state if the slave is not selected. When the SPI is not enabled, this signal is in a highimpedance state.

#### Master-Out, Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a master device and as an input in a slave device. It is one of the two lines that transfer serial data, with the most significant bit sent first. When the SPI is not enabled, this signal is in a high-impedance state.

#### **Slave Select**

The active Low Slave Select ( $\overline{SS}$ ) input signal is used to select the SPI as a slave device. It must be Low prior to all data communication and must stay Low for the duration of the data transfer.

The  $\overline{SS}$  input signal must be High for the SPI to operate as a master device. If the  $\overline{SS}$  signal goes Low, a Mode Fault error flag (MODF) is set in the SPI\_SR register. See the SPI Status Register (SPI\_SR) on page 136 for more information.

When the clock phase (CPHA) is set to 0, the shift clock is the logical OR of  $\overline{SS}$  with SCK. In this clock phase mode,  $\overline{SS}$  must go High between successive characters in an SPI message. When CPHA is set to 1,  $\overline{SS}$  can remain Low for several SPI characters. In cases where there is only one SPI slave, its  $\overline{SS}$  line could be tied Low as long as CPHA is set to 1. See the SPI Control Register (SPI\_CTL) on page 135 for more information about CPHA.

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Value   | Description                                                                                 |

|-----------------|---------|---------------------------------------------------------------------------------------------|

| [7:1]<br>SLA    | 00h–7Fh | 7-bit slave address or upper 2 bits,I2C_SAR[2:1], of address when operating in 10-bit mode. |

| 0               | 0       | I <sup>2</sup> C not enabled to recognize the General Call Address.                         |

| GCE             | 1       | I <sup>2</sup> C enabled to recognize the General Call Address.                             |

#### I<sup>2</sup>C Extended Slave Address Register

The I2C\_XSAR register is used in conjunction with the I2C\_SAR register to provide 10bit addressing of the I<sup>2</sup>C when in SLAVE mode. The I2C\_SAR value forms the lower 8 bits of the 10-bit slave address. The full 10-bit address is supplied by  $\{I2C\_SAR[2:1], I2C\_XSAR[7:0]\}$ .

When the register receives an address starting with F7h to F0h (I2C\_SAR[7:3] = 11110b), the I<sup>2</sup>C recognizes that a 10-bit slave addressing mode is being selected. The I<sup>2</sup>C sends an ACK after receiving the I2C\_XSAR byte (the device does not generate an interrupt at this point). After the next byte of the address (I2C\_XSAR) is received, the I<sup>2</sup>C generates an interrupt and goes into SLAVE mode. Then I2C\_SAR[2:1] are used as the upper 2 bits for the 10-bit extended address. The full 10-bit address is supplied by {I2C\_SAR[2:1], I2C\_XSAR[7:0]}. See Table 82.

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Value   | Description                                                    |

|-----------------|---------|----------------------------------------------------------------|

| [7:0]<br>SLAX   | 00h–FFh | Least significant 8 bits of the 10-bit extended slave address. |

## I<sup>2</sup>C Data Register

This register contains the data byte/slave address to be transmitted or the data byte just received. In transmit mode, the most significant bit of the byte is transmitted first. In receive mode, the first bit received is placed in the most significant bit of the register. After each byte is transmitted, the I2C\_DR register contains the byte that is present on the bus in case a lost arbitration event occurs. See Table 83.

### Table 83. I<sup>2</sup>C Data Register (I2C\_DR = 00CAh)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Value   | Description                 |

|-----------------|---------|-----------------------------|

| [7:0]<br>DATA   | 00h–FFh | I <sup>2</sup> C data byte. |

### I<sup>2</sup>C Control Register

The I2C\_CTL register is a control register that is used to control the interrupts and the master slave relationships on the I<sup>2</sup>C bus.

When the Interrupt Enable bit (IEN) is set to 1, the interrupt line goes High when the IFLG is set to 1. When IEN is cleared to 0, the interrupt line always remains Low.

When the Bus Enable bit (ENAB) is set to 0, the  $I^2C$  bus inputs SCLx and SDAx are ignored and the  $I^2C$  module does not respond to any address on the bus. When ENAB is set to 1, the  $I^2C$  responds to calls to its slave address and to the general call address if the GCE bit (I2C\_SAR[0]) is set to 1.

When the Master Mode Start bit (STA) is set to 1, the  $I^2C$  enters MASTER mode and sends a START condition on the bus when the bus is free. If the STA bit is set to 1 when the  $I^2C$  module is already in MASTER mode and one or more bytes are transmitted, then a repeated START condition is sent. If the STA bit is set to 1 when the  $I^2C$  block is being

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BRK_NEXT   | 0     | The ZDI BREAK on the next CPU instruction is disabled.<br>Clearing this bit releases the CPU from its current BREAK<br>condition.                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 1     | The ZDI BREAK on the next CPU instruction is enabled.<br>The CPU can use multibyte Op Codes and multibyte<br>operands. break points only occur on the first Op Code in a<br>multibyte Op Code instruction. If the ZCL pin is High and<br>the ZDA pin is Low at the end of RESET, this bit is set to 1<br>and a BREAK occurs on the first instruction following the<br>RESET. This bit is set automatically during ZDI BREAK on<br>address match. A BREAK can also be forced by writing a 1<br>to this bit. |

| 6<br>brk_addr3  | 0     | The ZDI BREAK, upon matching break address 3, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 3, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5<br>brk_addr2  | 0     | The ZDI BREAK, upon matching break address 2, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 2, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4<br>brk_addr1  | 0     | The ZDI BREAK, upon matching break address 1, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 1, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3<br>brk_addr0  | 0     | The ZDI BREAK, upon matching break address 0, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 0, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2<br>ign_low_1  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If BRK_ADDR1 is set to 1, ZDI<br>initiates a BREAK when the entire 24-bit address,<br>ADDR[23:0], matches the 3-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H, ZDI_ADDR1_L}.                                                                                                                                                                                                                                        |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If BRK_ADDR1 is set to 1, ZDI<br>initiates a BREAK when only the upper 2 bytes of the 24-bit<br>address, ADDR[23:8], match the 2-byte value<br>{ZDI_ADDR1_U, ZDI_ADDR1_H}. As a result, a BREAK<br>can occur anywhere within a 256-byte page.                                                                                                                                                                  |

## **OCI Information Requests**

For additional information regarding On-Chip Instrumentation, or to order OCI debug tools, please contact:

First Silicon Solutions, Inc. 5440 SW Westgate Drive, Suite 240 Portland, OR 97221 Phone: (503) 292-6730 Fax: (503) 292-5840 www.fs2.com

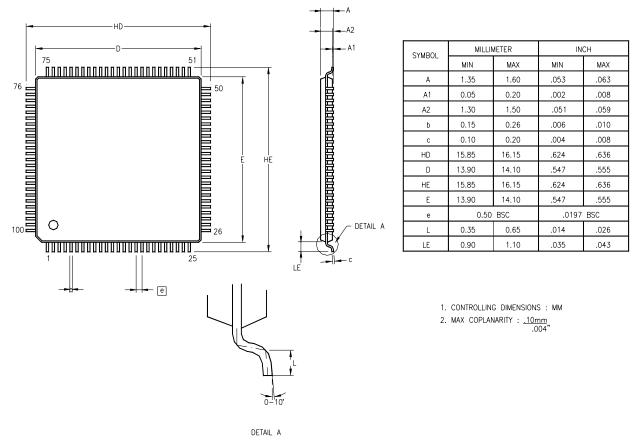

# Packaging

Figure 56 illustrates the 100-pin low-profile quad flat pack (LQFP) package for the eZ80L92 devices.

Figure 56. 100-Lead Plastic Low-Profile Quad Flat Package (LQFP)

## Index

## **Numerics**

100-pin LQFP package 4, 2120 MHz Primary Crystal Oscillator Operation 19832 KHz Real-Time Clock Crystal Oscillator Operation 199

## Α

Absolute Maximum Ratings 201 Absolute maximum ratings 201 AC Characteristics 203 ACK 141, 145, 146, 147, 148, 149, 151, 156 Acknowledge 141 ADDR0 5, 21 ADDR1 5, 21 ADDR10 6, 21 ADDR11 7, 21 ADDR12 7, 21 ADDR13 7, 21 ADDR14 7, 21 ADDR15 7, 21 ADDR16 8, 21 ADDR17 8, 21 ADDR18 8, 21 ADDR19 8, 21 ADDR2 5, 21 ADDR20 8, 22 ADDR21 9, 22 ADDR22 9, 22 ADDR23 9, 22 ADDR3 5, 21 ADDR4 5, 21 ADDR5 5, 21 ADDR6 6, 21 ADDR7 6, 21 ADDR8 6, 21 ADDR9 6, 21

Address Bus 5, 6, 7, 8, 9 address bus 45, 50, 53, 54, 56, 57, 58, 61, 64, 65, 68, 69, 90, 167, 176, 181 address bus, 24-bit 25 Addressing 151 Arbitration 143 Architectural Overview 1 asynchronous serial data 13, 15, 16

## В

Baud Rate Generator 104, 108 Baud Rate Generator Functional Description 133 Block Diagram 3 BRG Control Registers 109 Bus Arbitration Overview 139 Bus Mode Controller 53 Bus Requests During ZDI Debug Mode 167 BUSACK 12, 23, 53, 167, 175, 181, 214 BUSREQ 12, 23, 53, 167, 176, 181 Byte Format 141

## С

Characteristics, electrical Absolute maximum ratings 201 Chip Select Registers 67 Chip Select x Bus Mode Control Register 71 Chip Select x Control Register 70 Chip Select x Lower Bound Register 67 Chip Select x Upper Bound Register 69 Chip Select/Wait State Generator block 5, 6, 7, 8, 9 Chip Selects and Wait States 48 Chip Selects During Bus Request/Bus Acknowledge Cycles 53 Clear to Send 14, 16, 121 Clock Peripheral Power-Down Registers 35