# E·XFL

#### Zilog - EZ80L92AZ050EC00TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ80                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 50MHz                                                         |

| Connectivity               | EBI/EMI, I²C, Irda, SPI, UART/USART                           |

| Peripherals                | DMA, WDT                                                      |

| Number of I/O              | 24                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | -                                                             |

| RAM Size                   | -                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 100-LQFP                                                      |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80l92az050ec00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 1. 100-Pin LQFP Pin Identification of eZ80L92 MCU (Continued)

| Pin No | Symbol              | Function                             | Signal Direction                     | Description                                                                                                                                                                                                                                                                                 |

|--------|---------------------|--------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52     | NMI                 | Nonmaskable<br>Interrupt             | Schmitt Trigger Input,<br>Active Low | The $\overline{\text{NMI}}$ input is a higher priority input<br>than the maskable interrupts. It is always<br>recognized at the end of an instruction,<br>regardless of the state of the interrupt<br>enable control bits. This input includes a<br>Schmitt trigger to allow RC rise times. |

| 53     | BUSREQ              | Bus Request                          | Input, Active Low                    | External devices can request the eZ80L92<br>MCU to release the memory interface bus<br>for their use, by driving this pin Low.                                                                                                                                                              |

| 54     | BUSACK              | Bus<br>Acknowledge                   | Output, Active Low                   | The eZ80L92 MCU responds to a Low on BUSREQ, by tristating the address, data, and control signals, and by driving the BUSACK line Low. During bus acknowledge cycles ADDR[23:0], IORQ, and MREQ are inputs.                                                                                 |

| 55     | HALT_SLP            | HALT and<br>SLEEP<br>Indicator       | Output, Active Low                   | A Low on this pin indicates that the CPU<br>has entered either HALT or SLEEP mode<br>because of execution of either a HALT or<br>SLP instruction.                                                                                                                                           |

| 56     | V <sub>DD</sub>     | Power Supply                         |                                      | Power Supply.                                                                                                                                                                                                                                                                               |

| 57     | V <sub>SS</sub>     | Ground                               |                                      | Ground.                                                                                                                                                                                                                                                                                     |

| 58     | RTC_XIN             | Real-Time<br>Clock Crystal<br>Input  | Input                                | This pin is the input to the low-power<br>32 kHz crystal oscillator for the Real-Time<br>Clock.                                                                                                                                                                                             |

| 59     | RTC_XOUT            | Real-Time<br>Clock Crystal<br>Output | Bidirectional                        | This pin is the output from the low-power 32 kHz crystal oscillator for the Real-Time Clock. This pin is an input when the RTC is configured to operate from 50/60 Hz input clock signals and the 32 kHz crystal oscillator is disabled.                                                    |

| 60     | RTC_V <sub>DD</sub> | Real-Time<br>Clock Power<br>Supply   |                                      | Power supply for the Real-Time Clock and<br>associated 32 kHz oscillator. Isolated from<br>the power supply to the remainder of the<br>chip. A battery can be connected to this<br>pin to supply constant power to the<br>Real-Time Clock and 32 kHz oscillator.                            |

| 61     | V <sub>SS</sub>     | Ground                               |                                      | Ground.                                                                                                                                                                                                                                                                                     |

| 62     | TMS                 | JTAG Test<br>Mode Select             | Input                                | JTAG Mode Select Input.                                                                                                                                                                                                                                                                     |

## Table 1. 100-Pin LQFP Pin Identification of eZ80L92 MCU (Continued)

| Pin No | Symbol | Function               | Signal Direction   | Description                                                                                                                                                                                                                                                                                                    |

|--------|--------|------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70     | PD2    | GPIO Port D            | Bidirectional      | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port D pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. Port D is multiplexed with<br>one UART. |

|        | RTS0   | Request to<br>Send     | Output, Active Low | Modem control signal from UART.<br>This signal is multiplexed with PD2.                                                                                                                                                                                                                                        |

| 71     | PD3    | GPIO Port D            | Bidirectional      | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port D pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. Port D is multiplexed with<br>one UART. |

|        | CTS0   | Clear to Send          | Input, Active Low  | Modem status signal to the UART.<br>This signal is multiplexed with PD3.                                                                                                                                                                                                                                       |

| 72     | PD4    | GPIO Port D            | Bidirectional      | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port D pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. Port D is multiplexed with<br>one UART. |

|        | DTR0   | Data Terminal<br>Ready | Output, Active Low | Modem control signal to the UART.<br>This signal is multiplexed with PD4.                                                                                                                                                                                                                                      |

| 73     | PD5    | GPIO Port D            | Bidirectional      | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port D pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. Port D is multiplexed with<br>one UART. |

|        | DSR0   | Data Set<br>Ready      | Input, Active Low  | Modem status signal to the UART.<br>This signal is multiplexed with PD5.                                                                                                                                                                                                                                       |

## Table 1. 100-Pin LQFP Pin Identification of eZ80L92 MCU (Continued)

| Pin No | Symbol | Function            | Signal Direction  | Description                                                                                                                                                                                                                                                            |

|--------|--------|---------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90     | PB2    | GPIO Port B         | Bidirectional     | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port B pin,<br>when programmed as output, can be<br>selected to be an open-drain or<br>open-source output.  |

|        | SS     | Slave Select        | Input, Active Low | The slave select input line is used to select a slave device in SPI mode. This signal is multiplexed with PB2.                                                                                                                                                         |

| 91     | PB3    | GPIO Port B         | Bidirectional     | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port B pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. |

|        | SCK    | SPI Serial<br>Clock | Bidirectional     | SPI serial clock. This signal is multiplexed with PB3.                                                                                                                                                                                                                 |

| 92     | PB4    | GPIO Port B         | Bidirectional     | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port B pin,<br>when programmed as output, can be<br>selected to be an open-drain or open-<br>source output. |

|        | T4_OUT | Timer 4 Out         | Output            | Programmable Reload Timer 4 timer-out signal. This signal is multiplexed with PB4.                                                                                                                                                                                     |

| 93     | PB5    | GPIO Port B         | Bidirectional     | This pin can be used for GPIO. It can be<br>individually programmed as input or<br>output and can also be used individually<br>as an interrupt input. Each Port B pin,<br>when programmed as output, can be<br>selected to be an open-drain or<br>open-source output.  |

|        | T5_OUT | Timer 5 Out         | Output            | Programmable Reload Timer 5 timer-out signal. This signal is multiplexed with PB5.                                                                                                                                                                                     |

| Pin<br>No. | Symbol          | Direction | Reset<br>Direction | Active<br>Low/High | Tristate<br>Output | Pull<br>Up/Down | Schmitt<br>Trigger<br>Input | Open<br>Drain/Source |

|------------|-----------------|-----------|--------------------|--------------------|--------------------|-----------------|-----------------------------|----------------------|

| 25         | ADDR20          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                   |

| 26         | ADDR21          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                   |

| 27         | ADDR22          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                   |

| 28         | ADDR23          | I/O       | 0                  | N/A                | Yes                | No              | No                          | No                   |

| 29         | CS0             | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 30         | CS1             | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 31         | CS2             | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 32         | CS3             | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 33         | V <sub>DD</sub> |           |                    |                    |                    |                 |                             |                      |

| 34         | V <sub>SS</sub> |           |                    |                    |                    |                 |                             |                      |

| 35         | DATA0           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 36         | DATA1           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 37         | DATA2           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 38         | DATA3           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 39         | DATA4           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 40         | DATA5           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 41         | DATA6           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 42         | DATA7           | I/O       | I                  | N/A                | Yes                | No              | No                          | No                   |

| 43         | V <sub>DD</sub> |           |                    |                    |                    |                 |                             |                      |

| 44         | V <sub>SS</sub> |           |                    |                    |                    |                 |                             |                      |

| 45         | IORQ            | I/O       | 0                  | Low                | Yes                | No              | No                          | No                   |

| 46         | MREQ            | I/O       | 0                  | Low                | Yes                | No              | No                          | No                   |

| 47         | RD              | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 48         | WR              | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 49         | INSTRD          | 0         | 0                  | Low                | No                 | No              | No                          | No                   |

| 50         | WAIT            | I         | I                  | Low                | N/A                | No              | No                          | N/A                  |

| 51         | RESET           | I         | I                  | Low                | N/A                | Up              | Yes                         | N/A                  |

| 52         | NMI             | I         | I                  | Low                | N/A                | No              | Yes                         | N/A                  |

## Table 2. Pin Characteristics of eZ80L92 MCU (Continued)

{MBASE[7:0], I[7:0], 1Eh} and {MBASE, I[7:0], 1Fh}. The least significant byte is stored at the lower address.

When any one or more of the interrupt requests (IRQs) become active, an interrupt request is generated by the interrupt controller and sent to the CPU. The corresponding 8-bit interrupt vector for the highest priority interrupt is placed on the 8-bit interrupt vector bus, IVECT[7:0]. The interrupt vector bus is internal to the eZ80L92 and is therefore not visible externally. The response time of the eZ80 CPU to an interrupt request is a function of the current instruction being executed as well as the number of WAIT states being asserted.

The interrupt vector, {I[7:0], IVECT[7:0]}, is visible on the address bus, ADDR[15:0], when the interrupt service routine begins. The response of the eZ80 CPU to a vectored interrupt on the eZ80L92 is explained in Table 12. Interrupt sources are required to be active until the Interrupt Service Routine (ISR) starts. We recommend you to change the Interrupt Page Address Register (I) value from its default value of 00h as this address can create conflicts between the non-maskable interrupt vector, the RST instruction addresses, and the maskable interrupt vectors.

| Memory<br>Mode | ADL<br>Bit | MADL<br>Bit | Operation                                                                                                                        |

|----------------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Z80 Mode       | 0          | 0           | Read the LSB of the interrupt vector placed on the internal vectored interrupt bus, IVECT [7:0], by the interrupting peripheral. |

|                |            |             | • IEF1 $\leftarrow$ 0                                                                                                            |

|                |            |             | • IEF2 $\leftarrow$ 0                                                                                                            |

|                |            |             | <ul> <li>The starting Program Counter is effectively {MBASE, PC[15:0]}.</li> </ul>                                               |

|                |            |             | • Push the 2-byte return address PC[15:0] on the ({MBASE,SPS}) stack.                                                            |

|                |            |             | <ul> <li>The ADL mode bit remains cleared to 0.</li> </ul>                                                                       |

|                |            |             | • The interrupt vector address is located at { MBASE, I[7:0], IVECT[7:0] }                                                       |

|                |            |             | ● PC[15:0] ← ( { MBASE, I[7:0], IVECT[7:0] } ).                                                                                  |

|                |            |             | <ul> <li>The ending Program Counter is effectively {MBASE, PC[15:0]}</li> </ul>                                                  |

|                |            |             | <ul> <li>The interrupt service routine must end with RETI.</li> </ul>                                                            |

#### Table 12. Vectored Interrupt Operation

| Table 12. Vectored Interrupt | Operation | (Continued) |

|------------------------------|-----------|-------------|

|------------------------------|-----------|-------------|

| Memory<br>Mode | ADL<br>Bit | MADL<br>Bit | Operation                                                                                                                           |

|----------------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| ADL Mode       | 1          | 0           | Read the LSB of the interrupt vector placed on the internal vectored interrupt bus, IVECT [7:0], by the interrupting peripheral.    |

|                |            |             | • IEF1 $\leftarrow$ 0                                                                                                               |

|                |            |             | • IEF2 $\leftarrow$ 0                                                                                                               |

|                |            |             | <ul> <li>The starting Program Counter is PC[23:0].</li> </ul>                                                                       |

|                |            |             | <ul> <li>Push the 3-byte return address, PC[23:0], onto the SPL stack.</li> </ul>                                                   |

|                |            |             | <ul> <li>The ADL mode bit remains set to 1.</li> </ul>                                                                              |

|                |            |             | <ul> <li>The interrupt vector address is located at { 00h, I[7:0], IVECT[7:0] }.</li> </ul>                                         |

|                |            |             | ● PC[15:0] ← ( { 00h, I[7:0], IVECT[7:0] } ).                                                                                       |

|                |            |             | <ul> <li>The ending Program Counter is { 00h, PC[15:0] }.</li> </ul>                                                                |

|                |            |             | <ul> <li>The interrupt service routine must end with RETI.</li> </ul>                                                               |

| Z80 Mode       | 0          | 1           | Read the LSB of the interrupt vector placed on the internal vectored interrupt bus, IVECT[7:0], bus by the interrupting peripheral. |

|                |            |             | • IEF1 $\leftarrow$ 0                                                                                                               |

|                |            |             | • IEF2 $\leftarrow$ 0                                                                                                               |

|                |            |             | <ul> <li>The starting Program Counter is effectively {MBASE, PC[15:0]}.</li> </ul>                                                  |

|                |            |             | <ul> <li>Push the 2-byte return address, PC[15:0], onto the SPL stack.</li> </ul>                                                   |

|                |            |             | <ul> <li>Push a 00h byte onto the SPL stack to indicate an interrupt from Z80<sup>®</sup> mode (because ADL = 0).</li> </ul>        |

|                |            |             | <ul> <li>Set the ADL mode bit to 1.</li> </ul>                                                                                      |

|                |            |             | <ul> <li>The interrupt vector address is located at { 00h, I[7:0], IVECT[7:0] }.</li> </ul>                                         |

|                |            |             | ● PC[15:0] ← ( { 00h, I[7:0], IVECT[7:0] } ).                                                                                       |

|                |            |             | <ul> <li>The ending Program Counter is { 00h, PC[15:0] }.</li> </ul>                                                                |

|                |            |             | <ul> <li>The interrupt service routine must end with RETI.L</li> </ul>                                                              |

## Watchdog Timer Operation

#### **Enabling and Disabling the WDT**

The Watchdog Timer is disabled upon a system reset (RESET). To enable the WDT, the application program must set the WDT\_EN bit (bit 7) of the WDT\_CTL register. When enabled, the WDT cannot be disabled without a RESET.

#### **Time-Out Period Selection**

There are four choices of time-out periods for the WDT $-2^{18}$ ,  $2^{22}$ ,  $2^{25}$ , and  $2^{27}$  system clock cycles. The WDT time-out period is defined by the WDT\_PERIOD field of the WDT\_CTL register (WDT\_CTL[1:0]). The approximate time-out periods for two different WDT clock sources is listed in Table 26.

| Clock Source                  | Divider Value   | Time Out Delay |

|-------------------------------|-----------------|----------------|

| 32.768 kHz Crystal Oscillator | 2 <sup>18</sup> | 8.00 s         |

| 32.768 kHz Crystal Oscillator | 2 <sup>22</sup> | 128 s          |

| 32.768 kHz Crystal Oscillator | 2 <sup>25</sup> | 1024 s         |

| 32.768 kHz Crystal Oscillator | 2 <sup>27</sup> | 4096 s         |

| 20 MHz System Clock           | 2 <sup>18</sup> | 13.1 ms        |

| 20 MHz System Clock           | 2 <sup>22</sup> | 209.7 ms       |

| 20 MHz System Clock           | 2 <sup>25</sup> | 1.68s          |

| 20 MHz System Clock           | 2 <sup>27</sup> | 6.71s          |

| 50 MHz System Clock           | 2 <sup>18</sup> | 5.2 ms*        |

| 50 MHz System Clock           | 2 <sup>22</sup> | 83.9 ms*       |

| 50 MHz System Clock           | 2 <sup>25</sup> | 0.67 s         |

| 50 MHz System Clock           | 2 <sup>27</sup> | 2.68 s         |

#### Table 26. Watchdog Timer Approximate Time-Out Delays

#### **RESET Or NMI Generation**

Upon a WDT time-out, the RST\_FLAG in the WDT\_CTL register is set to 1. In addition, the WDT can cause a RESET or send a nonmaskable interrupt (NMI) signal to the CPU. The default operation is for the WDT to cause a RESET. It asserts/deasserts on the rising edge of the clock. The RST\_FLAG bit can be polled by the CPU to determine the source of the RESET event.

If the NMI\_OUT bit in the WDT\_CTL register is set to 1, then upon time-out, the WDT asserts an NMI for CPU processing. The RST\_FLAG bit can be polled by the CPU to

## **Real Time Clock Year Register**

This register contains the current year count. See Table 44.

#### Table 44. Real Time Clock Year Register (RTC\_YR = 00E6h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read-only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit<br>Position  | Value   | Description                               |

|------------------|---------|-------------------------------------------|

| [7:4]<br>TENS YR | 0–9     | The tens digit of the current year count. |

| [3:0]<br>YR      | 0–9     | The ones digit of the current year count. |

| Binary Operation | on (BCD | _EN = 0)                                  |

| Bit<br>Position  | Value   | Description                               |

| [7:0]<br>YR      | 00h–63  | The current year count.                   |

## Real Time Clock Alarm Minutes Register

This register contains the alarm minutes value. See Table 47.

#### Table 47. Real Time Clock Alarm Minutes Register (RTC\_AMIN = 00E9h)

| Bit        | 7   | 6   | 5      | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|--------|-----|-----|-----|-----|-----|

| Reset      | Х   | Х   | Х      | Х   | Х   | Х   | Х   | Х   |

| CPU Access | R/W | R/W | R/W    | R/W | R/W | R/W | R/W | R/W |

|            |     |     | 104/14 |     |     |     |     |     |

**Note:** X = Unchanged by RESET; R/W = Read/Write.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| -                 |             |                                            |  |  |  |  |

|-------------------|-------------|--------------------------------------------|--|--|--|--|

| Bit<br>Position   | Value D     | Description                                |  |  |  |  |

| [7:4]<br>ATEN_MIN | 0–5 T       | he tens digit of the alarm minutes value.  |  |  |  |  |

| [3:0]<br>AMIN     | 0–9 T       | The ones digit of the alarm minutes value. |  |  |  |  |

| Binary Opera      | tion (BCD_E | EN = 0)                                    |  |  |  |  |

| Bit               |             |                                            |  |  |  |  |

| Position          | Value       | Description                                |  |  |  |  |

| [7:0]<br>AMIN     | 00h–3Bh     | The alarm minutes value.                   |  |  |  |  |

## Real Time Clock Alarm Day-of-the-Week Register

This register contains the alarm day-of-the-week value. See Table 49.

## Table 49. Real Time Clock Alarm Day-of-the-Week Register (RTC\_ADOW = 00EBh)

| Bit                                                                                        | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|--------------------------------------------------------------------------------------------|---|---|---|---|------|------|------|------|

| Reset                                                                                      | 0 | 0 | 0 | 0 | Х    | Х    | Х    | Х    |

| CPU Access                                                                                 | R | R | R | R | R/W* | R/W* | R/W* | R/W* |

| Note: X = Unchanged by RESET; R = Read Only; R/W* = Read-only if RTC locked, Read/Write if |   |   |   |   |      |      |      |      |

RTC unlocked.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit              |            |                                  |  |

|------------------|------------|----------------------------------|--|

| Position         | Value      | Description                      |  |

| [7:4]            | 0000       | Reserved.                        |  |

| [3:0]<br>ADOW    | 1-7        | The alarm day-of-the-week.value. |  |

| Binary Operation | ation (BCD | _EN = 0)                         |  |

| Bit              |            |                                  |  |

| Position         | Value      | Description                      |  |

| roontion         | value      | Description                      |  |

| [7:4]         | 0000    | Reserved.                        |

|---------------|---------|----------------------------------|

| [3:0]<br>ADOW | 01h–07h | The alarm day-of-the-week value. |

## Universal Asynchronous Receiver/ Transmitter

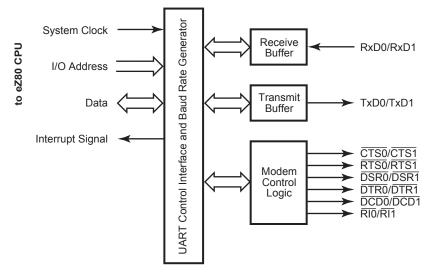

The UART module implements the logic required to support various asynchronous communications protocols. The module also implements two separate 16-byte-deep FIFOs for both transmission and reception. A block diagram of the UART is illustrated in Figure 23.

Figure 23. UART Block Diagram

The UART module provides the following asynchronous communication protocol-related features and functions:

- 5-bit, 6-bit, 7-bit, or 8-bit data transmission

- Even parity/odd parity or no parity bit generation and detection

- Start and stop bit generation and detection (supports up to two stop bits)

- Line break detection and generation

- Receiver overrun and framing errors detection

- Logic and associated I/O to provide modem handshake capability

is reset only when the processor reads all of the received data bytes. If the number of bits received is less than eight, the unused most significant bits of the data byte Read are 0.

The receiver uses the clock from the BRG for receiving the data. This clock must be 16 times the appropriate baud rate. The receiver synchronizes the shift clock on the falling edge of the RxD input start bit. It then receives a complete byte according to the set parameters. The receiver also implements logic to detect framing errors, parity errors, overrun errors, and break signals.

#### **UART Modem Control**

The modem control logic provides two outputs and four inputs for handshaking with the modem. Any change in the modem status inputs, except  $\overline{RI}$ , is detected and an interrupt can be generated. For  $\overline{RI}$ , an interrupt is generated only when the trailing edge of the  $\overline{RI}$  is detected. The module also provides LOOP mode for self-diagnostics.

## **UART Interrupts**

There are five different sources of interrupts from the UART are:

- Transmitter.

- Receiver (three different interrupts).

- Modem status.

#### **UART Transmitter Interrupt**

The transmitter interrupt is generated if there is no data available for transmission. This interrupt can be disabled using the individual interrupt enable bit or cleared by writing data into the UARTx\_THR register.

#### **UART Receiver Interrupts**

A receiver interrupt can be generated by three possible sources. The first source, a receiver data ready, indicates that one or more data bytes are received and are ready to be read. This interrupt is generated if the number of bytes in the receiver FIFO is greater than or equal to the trigger level. If the FIFO is not enabled, the interrupt is generated if the receive buffer contains a data byte. This interrupt is cleared by reading the UARTx RBR.

The second interrupt source is the receiver time-out. A receiver time-out interrupt is generated when there are fewer data bytes in the receiver FIFO than the trigger level and there are no Reads and Writes to or from the receiver FIFO for four consecutive byte times. When the receiver time-out interrupt is generated, it is cleared only after emptying the entire receive FIFO.

The first two interrupt sources from the receiver (data ready and time-out) share an interrupt enable bit.

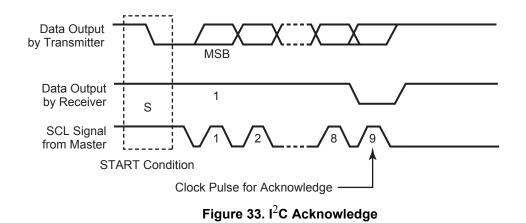

slave-transmitter must release the data line to allow the master to generate a STOP or a repeated START condition.

## **Clock Synchronization**

All masters generate their own clocks on the SCL line to transfer messages on the  $I^2C$  bus. Data is only valid during the High period of each clock.

Clock synchronization is performed using the wired AND connection of the I<sup>2</sup>C interfaces to the SCL line, meaning that a High-to-Low transition on the SCL line causes the relevant devices to start counting from their Low period. When a device clock goes Low, it holds the SCL line in that state until the clock High state is reached. See Figure 34. The Low-to-High transition of this clock, however, may not change the state of the SCL line if another clock is still within its Low period. The SCL line is held Low by the device with the long-est Low period. Devices with shorter Low periods enter a High wait-state during this time.

When all devices concerned count off their Low period, the clock line is released and goes High. There is no difference between the device clocks and the state of the SCL line, and all of the devices start counting their High periods. The first device to complete its High period again pulls the SCL line Low. In this way, a synchronized SCL clock is generated with its Low period determined by the device with the longest clock Low period, and its High period determined by the one with the shortest clock High period.

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Value   | Description                                                                                 |

|-----------------|---------|---------------------------------------------------------------------------------------------|

| [7:1]<br>SLA    | 00h–7Fh | 7-bit slave address or upper 2 bits,I2C_SAR[2:1], of address when operating in 10-bit mode. |

| 0               | 0       | I <sup>2</sup> C not enabled to recognize the General Call Address.                         |

| GCE             | 1       | I <sup>2</sup> C enabled to recognize the General Call Address.                             |

#### I<sup>2</sup>C Extended Slave Address Register

The I2C\_XSAR register is used in conjunction with the I2C\_SAR register to provide 10bit addressing of the I<sup>2</sup>C when in SLAVE mode. The I2C\_SAR value forms the lower 8 bits of the 10-bit slave address. The full 10-bit address is supplied by  $\{I2C\_SAR[2:1], I2C\_XSAR[7:0]\}$ .

When the register receives an address starting with F7h to F0h (I2C\_SAR[7:3] = 11110b), the I<sup>2</sup>C recognizes that a 10-bit slave addressing mode is being selected. The I<sup>2</sup>C sends an ACK after receiving the I2C\_XSAR byte (the device does not generate an interrupt at this point). After the next byte of the address (I2C\_XSAR) is received, the I<sup>2</sup>C generates an interrupt and goes into SLAVE mode. Then I2C\_SAR[2:1] are used as the upper 2 bits for the 10-bit extended address. The full 10-bit address is supplied by {I2C\_SAR[2:1], I2C\_XSAR[7:0]}. See Table 82.

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Code | Status                                                                                      |

|------|---------------------------------------------------------------------------------------------|

| B0h  | Arbitration lost in address as master, slave address and Read bit received, ACK transmitted |

| B8h  | Data byte transmitted in SLAVE mode, ACK received                                           |

| C0h  | Data byte transmitted in SLAVE mode, ACK not received                                       |

| C8h  | Last byte transmitted in SLAVE mode, ACK received                                           |

| D0h  | Second Address byte and Write bit transmitted, ACK received                                 |

| D8h  | Second Address byte and Write bit transmitted, ACK not received                             |

| F8h  | No relevant status information, IFLG = 0                                                    |

If an illegal condition occurs on the  $I^2C$  bus, the bus error state is entered (status code 00h). To recover from this state, the STP bit in the I2C\_CTL register must be set and the IFLG bit cleared. The  $I^2C$  then returns to the idle state. No STOP condition is transmitted on the  $I^2C$  bus.

**Note:** The STP and STA bits may be set to 1 at the same time to recover from the bus error. The  $I^2C$  then sends a START.

#### I<sup>2</sup>C Clock Control Register

The I2C\_CCR register is a Write-Only register. The seven LSBs control the frequency at which the I<sup>2</sup>C bus is sampled and the frequency of the I<sup>2</sup>C clock line (SCL) when the I<sup>2</sup>C is in MASTER mode. The Write-Only I2C\_CCR registers share the same I/O addresses as the Read-Only I2C\_SR registers. See Table 87.

| Bit                  | 7     | 6         | 5        | 4 | 3 | 2 | 1 | 0 |

|----------------------|-------|-----------|----------|---|---|---|---|---|

| Reset                | 0     | 0         | 0        | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | W     | W         | W        | W | W | W | W | W |

| Note: W = Read only. | ·     |           |          |   |   |   |   |   |

| Bit<br>Position      | Value | Des       | cription |   |   |   |   |   |

| 7                    | 0     | Reserved. |          |   |   |   |   |   |

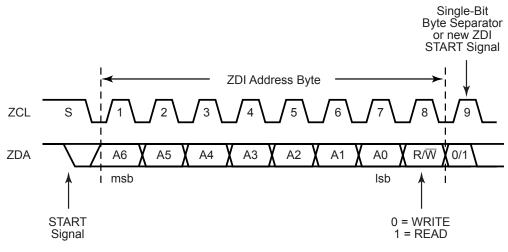

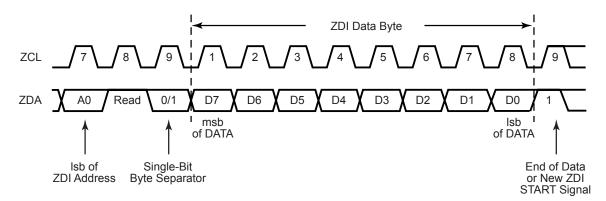

can be repeated. This allows repeated Read or Write operations without having to resend the ZDI command. A START signal must follow to initiate a new ZDI command. Figure 39 illustrates the timing for address Writes to ZDI registers.

Figure 39. ZDI Address Write Timing

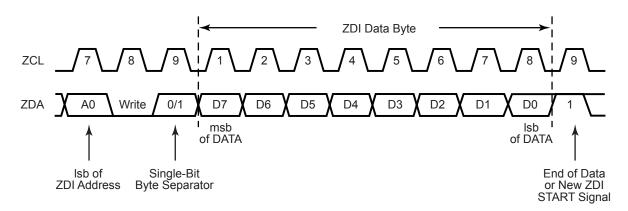

### **ZDI Write Operations**

#### **ZDI Single-Byte Write**

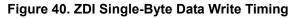

For single-byte Write operations, the address and write control bit are first written to the ZDI block. Following the single-bit byte separator, the data is shifted into the ZDI block on the next 8 rising edges of ZCL. The master terminates activity after 8 clock cycles. Figure 40 illustrates the timing for ZDI single-byte Write operations.

Figure 42. ZDI Single-Byte Data Read Timing

#### **ZDI Block Read**

A Block Read operation is initiated the same as a single-byte Read; however, the ZDI master continues to clock in the next byte from the ZDI slave as the ZDI slave continues to output data. The ZDI register address counter increments with each Read. If the ZDI register address reaches the end of the Read-Only ZDI register address space (20h), the address stops incrementing. Figure 43 illustrates the ZDI's Block Read timing.

Figure 43. ZDI Block Data Read Timing

## **Operation of the eZ80L92 During ZDI Break Points**

If the ZDI forces the CPU to break, only the CPU suspends operation. The system clock continues to operate and drive other peripherals. Those peripherals that can operate autonomously from the CPU may continue to operate, if so enabled. For example, the Watchdog Timer and Programmable Reload Timers continue to count during a ZDI break point.

## **Opcode Map**

Table 109 through Table 115 indicate the hex values for the eZ80 instructions.

#### Table 109. Opcode Map—First Opcode

Legend Lower opcode Nibble Upper opċode 4 Nibble AND Mnemonic A,H First Operand Second Operand Lower Nibble (Hex) 0 2 3 4 5 6 7 8 9 А В С D Е F LD DEC LD INC INC DEC LD ΕX ADD LD DEC INC LD 0 NOP RLCA RRCA BC, (BC),A BC В В B,n AF,AF HL,BC A,(BC) BC С С C,n Mmn LD INC DEC INC DJNZ LD INC LD ADD LD DEC DEC LD JR 1 DE, RLA RRA d (DE),A DE D D D,n d HL,DE A,(DE) DE Е Е E,n Mmn LD LD LD JR INC INC DEC LD JR ADD DEC INC DEC LD 2 (Mmn), DAA HL, CPL HL. NZ,d HL H,n Z,d HL,HL L,n н Н HL L L Mmn HL (Mmn) LD LD LD JR INC INC DEC LD JR ADD DEC INC DEC LD 3 SCF CCF SP. (Mmn), A. NC,d (HL) (HL) (HL),n CF,d HL,SP SP SP А А A,n (Mmn) Mmn Α .SIS LD LD LD LD LD LD LD LD .LIS LD LD LD LD LD LD 4 suffix B,C B.D B.E B.H B,L B,(HL) B,A C,B suffix C,D C.E C,H C,L C,(HL) C,A LD .SIL LD LD LD LD LD LD LD LD .LIL LD LD LD LD LD 5 E,B E,D D,B D,C suffix D,E D,H D,L D,(HL) D,A E,C suffix E,H E,L E,(HL) E,A LD 6 Upper Nibble (Hex) H,B H,C H,D H,E H,H H,L H,(HL) L,B L,C L,D L,H L,(HL) H,A L,E L,L L,A LD ID 7 HALT (HL),C (HL),B (HL),D (HL),E (HL),H (HL),L (HL),A A,B A,C A,D A,(HL) A,E A,H A,L A,A ADD ADD ADD ADD ADD ADD ADD ADC ADC ADC ADC ADC ADC ADC ADC ADD 8 A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A SUB SUB SUB SUB SUB SUB SUB SUB SBC SBC SBC SBC SBC SBC SBC SBC 9 A,B A,C A,D A.E A,H A,L A,(HL) A,A A.B A,C A,D A.E A,H A,L A,(HL) A.A AND AND AND XOR AND AND AND AND AND XOR XOR XOR XOR XOR XOR XOR A A,(HL) A,(HL) A,D A,E A,A A,B A,C A,D A,E A,L A.B A.C A.H A.L A.H A.A OR OR OR OR OR OR OR OR CP CP CP CP CP CP CP CP В A,H A,B A,D A,E A,(HL) A,B A,C A,D A,E A,(HL) A,A A,C A,H A,L A,A A,L JP CALL JP CALL Table RET POP JP PUSH ADD RST RET CALL ADC RST С NZ, NZ, RET Ζ, Ζ, N7 BC Mmn BC A,n 00h Ζ 110 Mmn A,n 08h Mmn Mmn Mmn Mmn JP CALL JP CALL Table RET POP OUT PUSH SUB RST RET IN SBC RST D NC, EXX CF, CF, NC. NC DE (n),A DE 10h CF A,(n) 18h A,n 111 A,n Mmn Mmn Mmn Mmn CALL JP CALL JP Table RET POP ΕX PUSH AND RST RET ΕX XOR RST JP Е PO, PE, PE, PO. PO HL (SP),HL HL A.n 20h ΡE (HL) DE,HL 112 A.n 28h Mmn Mmn Mmn Mmn JP CALL JP CALL POP PUSH Table RET OR RST RET LD CP RST F P. M. Μ, DI Ρ. ΕI SP,HL 38h F AF AF A.n 30h Μ A,n 113 Mmn Mmn Mmn Mmn

Notes: n = 8-bit data; Mmn = 16- or 24-bit addr or data; d = 8-bit two's-complement displacement.

## **AC Characteristics**

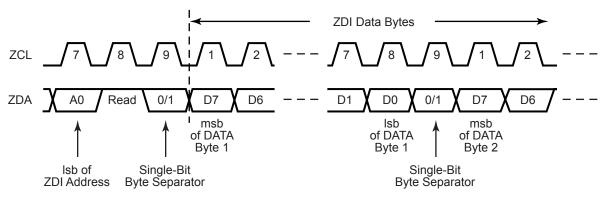

The section provides information on the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs. See Table 120.

SPI 1, 36, 44, 128, 129, 132 SPI Baud Rate Generator 133 SPI Baud Rate Generator Register 27 SPI Baud Rate Generator Registers-Low Byte and High Byte 134 SPI Block 27 SPI Control Register 27, 135 SPI Data Rate 133 SPI Flags 132 SPI Functional Description 131 SPI interrupt service routine 44 SPI Master device 134 SPI master device 20 SPI MASTER mode 132 SPI mode 19 SPI Receive Buffer Register 27, 137 SPI Registers 134 SPI serial bus 137 SPI Serial Clock 19 SPI Signals 129 SPI slave device 20 SPI SLAVE mode 132 SPI Status Register 27, 136 SPI Status register 132 SPI Transmit Shift Register 27, 134, 137 SPI Transmit Shift register 133 **SPIF 131** spiF 136 SPIF bit 137 SPIF flag 132 SPIF status bit 137 SRA 190 SRA, Op Code Map 192, 196 SS 19, 129, 131, 132, 133, 136 **STA 153** standard mode 139 START and STOP Conditions 140 Supply Voltage 202 supply voltage 1, 39, 139, 201 Switching Between Bus Modes 67 system clock cycles 11, 51, 53, 54, 58, 62, 74, 183 System Clock Oscillator Input 18 System Clock Oscillator Output 18

## Т

TERI 121 Test Mode 184 Time-Out Period Selection 74 Timer Control Register 82 Timer Data Register—High Byte 84 Timer Data Register—Low Byte 83 Timer Input Source Select Register 86 Timer Input Source Selection 80 Timer Output 81 Timer Reload Register—High Byte 86 Transferring Data 141 Transmit, Infrared Encoder/Decoder 124 TxD0 13 TxD1 15

## U

UART Baud Rate Generator Register -Low and High Bytes 109 **UART FIFO Control Register 114 UART Functional Description 105** UART Interrupt Enable Register 112 **UART Interrupt Identification Register 113 UART Interrupts 106** UART Line Control Register 115 **UART Line Status Register 118** UART Modem Control 106 UART Modem Control Register 117 UART Modem Status Interrupt 107 UART Modem Status Register 120 UART Receive Buffer Register 111 **UART Receiver 105 UART Receiver Interrupts 106** UART Recommended Usage 107 **UART Registers 110** UART Scratch Pad Register 122 UART Transmit Holding Register 111 **UART Transmitter 105 UART Transmitter Interrupt 106** Universal Asynchronous Receiver/Transmitter 104