#### Zilog - EZ80L92AZ050SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 50MHz                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART          |

| Peripherals                | DMA, WDT                                                  |

| Number of I/O              | 24                                                        |

| Program Memory Size        | -                                                         |

| Program Memory Type        | ROMIess                                                   |

| EEPROM Size                | -                                                         |

| RAM Size                   | -                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 100-LQFP                                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80l92az050sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 1. 100-Pin LQFP Pin Identification of eZ80L92 MCU (Continued)

| an be used for GPIO. It can be<br>y programmed as input or<br>d can also be used individually<br>rrupt input. Each Port B pin,<br>grammed as output, can be<br>o be an open-drain or                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rce output.                                                                                                                                                                                         |

| ) line is configured as an input<br>eZ80L92 MCU is an SPI master<br>d as an output when eZ80L92<br>n SPI slave device. This signal is<br>ed with PB6.                                               |

| an be used for GPIO. It can be<br>y programmed as input or<br>d can also be used individually<br>rrupt input. Each Port B pin,<br>grammed as output, can be<br>o be an open-drain or<br>rce output. |

| I line is configured as an output<br>eZ80L92 MCU is an SPI master<br>d as an input when the eZ80L92<br>n SPI slave device. This signal is<br>ed with PB7.                                           |

| pply.                                                                                                                                                                                               |

|                                                                                                                                                                                                     |

| arries the I <sup>2</sup> C data signal.                                                                                                                                                            |

| used to receive and transmit ock.                                                                                                                                                                   |

| an output driven by the internal ock.                                                                                                                                                               |

|                                                                                                                                                                                                     |

# Table 16. Intel<sup>®</sup> Bus Mode Read States (Separate Address and Data Buses) (Continued)

STATE T3 During State T3, no bus signals are altered. If the external ReadY (WAIT) pin is driven Low at least one eZ80 system clock cycle prior to the beginning of State T3, additional WAIT states (T<sub>WAIT</sub>) are asserted until the ReadY pin is driven High.

STATE T4 The CPU latches the Read data at the beginning of State T4. The CPU deasserts the RD signal and completes the Intel Bus Mode cycle.

During Write operations with separate address and data buses, the Intel Bus Mode employs 4 states (T1, T2, T3, and T4) as described in Table 17.

#### Table 17. Intel<sup>®</sup> Bus Mode Write States (Separate Address and Data Buses)

| STATE T1 | The Write cycle begins in State T1. The CPU drives the address onto the address bus, the associated Chip Select signal is asserted, and the data is driven onto the data bus. The CPU drives the ALE signal High at the beginning of T1. During the middle of T1, the CPU drives ALE Low to facilitate the latching of the address. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATE T2 | During State T2, the CPU asserts the $\overline{\text{WR}}$ signal. Depending on the instruction, either the $\overline{\text{MREQ}}$ or $\overline{\text{IORQ}}$ signal is asserted.                                                                                                                                               |

| STATE T3 | During State T3, no bus signals are altered. If the external ReadY ( $\overline{WAIT}$ ) pin is driven Low at least one eZ80 system clock cycle prior to the beginning of State T3, additional WAIT states ( $T_{WAIT}$ ) are asserted until the ReadY pin is driven High.                                                          |

| STATE T4 | The CPU deasserts the $\overline{\rm WR}$ signal at the beginning of State T4. The CPU holds the data and address buses through the end of T4. The bus cycle is completed at the end of T4.                                                                                                                                         |

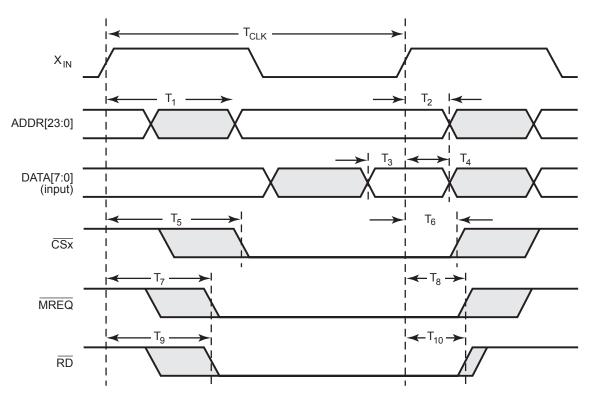

Intel Bus Mode timing is illustrated for a Read operation in Figure 10 and for a Write operation in Figure 11. If the ReadY signal (external WAIT pin) is driven Low prior to the beginning of State T3, additional WAIT states ( $T_{WAIT}$ ) are asserted until the ReadY signal is driven High. The Intel Bus Mode states can be configured for 2 to 15 eZ80 system clock cycles. In the figures, each Intel<sup>®</sup> Bus Mode state is 2 eZ80 system clock cycles in duration. Figure 10 and Figure 11 also illustrate the assertion of one WAIT state ( $T_{WAIT}$ ) by the selected peripheral.

| Bit        |       |                                                      |

|------------|-------|------------------------------------------------------|

| Position   | Value | Description                                          |

| [1:0]      | 00    | WDT time-out period is 2 <sup>27</sup> clock cycles. |

| WDT_PERIOD | 01    | WDT time-out period is 2 <sup>25</sup> clock cycles. |

|            | 10    | WDT time-out period is 2 <sup>22</sup> clock cycles. |

|            | 11    | WDT time-out period is 2 <sup>18</sup> clock cycles. |

Note: \*RST\_FLAG is only cleared by a non-WDT RESET.

#### Watchdog Timer Reset Register

The Watchdog Timer Reset register, described in Table 28, is an 8-bit Write-Only register. The Watchdog Timer is reset when an A5h value followed by 5Ah is written to this register. Any amount of time can occur between the writing of the A5h value and the 5Ah value, so long as the WDT time-out does not occur prior to completion.

#### Table 28. Watchdog Timer Reset Register (WDT\_RR = 0094h)

| Bit        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|---|

| Reset      | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access | W | W | W | W | W | W | W | W |

|            |   |   |   |   |   |   |   |   |

**Note:** X = Undefined; W = Write only.

| Bit             |       |                                                                                                                                                                                              |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position        | Value | Description                                                                                                                                                                                  |

| [7:0]<br>WDT_RR | A5h   | The first Write value required to reset the WDT prior to a time-out.                                                                                                                         |

|                 | 5Ah   | The second Write value required to reset the WDT prior to a time-out. If an A5h, 5Ah sequence is written to WDT_RR, the WDT timer is reset to its initial count value, and counting resumes. |

# **Programmable Reload Timers**

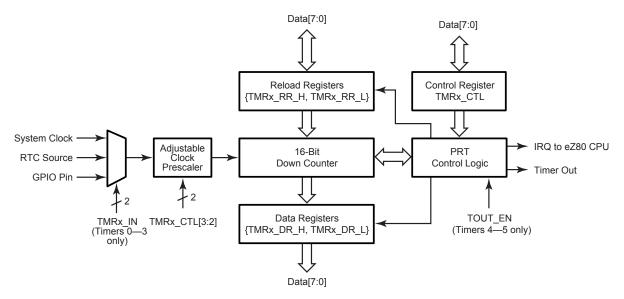

The eZ80L92 MCU features six Programmable Reload Timers (PRT). Each PRT contains a 16-bit downcounter and a 16-bit reload register. In addition, each PRT features a clock prescaler with four selectable taps for CLK  $\div$  4, CLK  $\div$  16, CLK  $\div$  64, and CLK  $\div$  256. Each timer can be individually enabled to operate in either SINGLE PASS or CONTINUOUS mode. The timer can be programmed to start, stop, restart from the current value, or restart from the initial value, and generate interrupts to the CPU.

Four of the Programmable Reload Timers (timers 0–3) feature a selectable clock source input. The input for these timers can be either the system clock or the Real-Time Clock (RTC) source. Timers 0–3 can also be used for event counting, with their inputs received from a GPIO port pin. Output from timers 4 and 5 can be directed to a GPIO port pin.

Each of the six PRTs available on the eZ80L92 can be controlled individually. They do not share the same counters, reload registers, control registers, or interrupt signals. A simplified block diagram of a programmable reload timer is illustrated in Figure 18.

Figure 18. Programmable Reload Timer Block Diagram

#### **Programmable Reload Timer Operation**

#### **Setting Timer Duration**

There are three factors to consider when determining Programmable Reload Timer duration—clock frequency, clock divider ratio, and initial count value. Minimum duration

| Parameter                  | Control Register(s)    | Value |

|----------------------------|------------------------|-------|

| PRT Enabled                | TMRx_CTL[0]            | 1     |

| Reload and Restart Enabled | TMRx_CTL[1]            | 1     |

| PRT Clock Divider = 4      | TMRx_CTL[3:2]          | 00b   |

| SINGLE PASS Mode           | TMRx_CTL[4]            | 0     |

| PRT Interrupt Enabled      | TMRx_CTL[6]            | 1     |

| PRT Reload Value           | {TMRx_RR_H, TMRx_RR_L} | 0004h |

#### Table 29. PRT SINGLE PASS Mode Operation Example

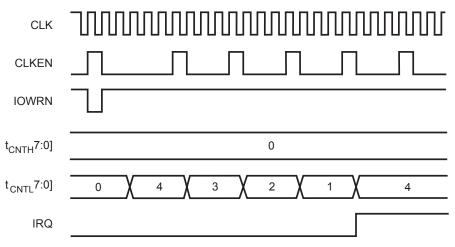

#### **CONTINUOUS Mode**

In CONTINUOUS mode, when the end-of-count value, 0000h, is reached, the timer automatically reloads the 16-bit start value from the Timer Reload registers, TMRx\_RR\_H and TMRx\_RR\_L. Downcounting continues on the next clock edge. In CONTINUOUS mode, the PRT continues to count until disabled. An example of a PRT operating in CONTINUOUS mode is illustrated in Figure 20. Timer register information is indicated in Table 30.

Figure 20. PRT CONTINUOUS Mode Operation Example

The third source of a receiver interrupt is a line status error, indicating an error in byte reception. This error may result from:

- Incorrect received parity.

- Incorrect framing; that is, the stop bit is not detected by receiver at the end of the byte.

- Receiver over run condition.

- A BREAK condition being detected on the receive data input.

An interrupt due to one of the above conditions is cleared when the UARTx\_LSR register is read. In FIFO mode, a line status interrupt is generated only after the received byte with an error reaches the top of the FIFO and is ready to be read.

A line status interrupt is activated (provided this interrupt is enabled) as long as the Read pointer of the receiver FIFO points to the location of the FIFO that contains a byte with the error. The interrupt is immediately cleared when the UARTx\_LSR register is read. The ERR bit of the UARTx\_LSR register is active as long as an erroneous byte is present in the receiver FIFO.

#### **UART Modem Status Interrupt**

The modem status interrupt is generated if there is any change in state of the modem status inputs to the UART. This interrupt is cleared when the processor reads the UARTx\_MSR register.

#### UART Recommended Usage

The following is the standard sequence of events that occur in the eZ80L92 MCU using the UART. A description of each follows.

- 1. Module reset.

- 2. Control transfers to configure UART operation.

- 3. Data transfers.

**Module Reset.** Upon reset, all internal registers are set to their default values. All command status registers are programmed with their default values, and the FIFOs are flushed.

**Control Transfers.** Based on the requirements of the application, the data transfer baud rate is determined and the BRG is configured to generate a 16X clock frequency. Interrupts are disabled and the communication control parameters are programmed in the UARTx\_LCTL register. The FIFO configuration is determined and the receive trigger levels are set in the UARTx\_FCTL register. The status registers, UARTx\_LSR and UARTx\_MSR, are read, and ensure that none of the interrupt sources are active. The inter-

**Note:** The UARTx\_BRG\_L registers share the same address space with the UARTx\_RBR and UARTx\_THR registers. The UARTx\_BRG\_H registers share the same address space with the UARTx\_IER registers. Bit 7 of the associated UART Line Control register (UARTx\_LCTL) must be set to 1 to enable access to the BRG registers.

## Table 52. UART Baud Rate Generator Registers—Low Byte (UART0\_BRG\_L = 00C0h, UART1\_BRG\_L = 00D0h)

| Bit                                    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                                  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| CPU Access                             | R/W |

| Note: R = Read only; R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position      | Value   | Description                                                                                                                                                        |

|----------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>UARTx_BRG_L | 00h–FFh | These bits represent the Low byte of the 16-bit Baud Rate<br>Generator divider value. The complete BRG divisor value<br>is returned by {UARTx_BRG_H, UARTx_BRG_L}. |

# Table 53. UART Baud Rate Generator Registers—High Byte (UART0\_BRG\_H = 00C1h, UART1\_BRG\_H = 00D1h)

| Bit                                    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access                             | R/W |

| Note: P = Pead only: P(M = Pead(M/rite |     |     |     |     |     |     |     |     |

**Note:** R = Read only; R/W = Read/Write.

| Position             | Value   | Description                                                                                                                                                   |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>UARTx_BRG_H | 00h–FFh | These bits represent the High byte of the 16-bit Baud Rate Generator divider value. The complete BRG divisor value is returned by {UARTx_BRG_H, UARTx_BRG_L}. |

## **UART Registers**

After a RESET, all UART registers are set to their default values. Any Writes to unused registers or register bits are ignored and Reads return a value of 0. For compatibility with future revisions, unused bits within a register must be written with a value of 0. Read/

# Table 55. UART Receive Buffer Registers (UART0\_RBR = 00C0h, UART1\_RBR = 00D0h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   |   |   |   |   |   |   |   |

| Bit<br>Position | Value   | Description        |

|-----------------|---------|--------------------|

| [7:0]<br>RxD    | 00h–FFh | Receive data byte. |

#### **UART Interrupt Enable Registers**

The UARTx\_IER register is used to enable and disable the UART interrupts. The UARTx\_IER registers share the same I/O addresses as the UARTx\_BRG\_H registers. See Table 56.

# Table 56. UART Interrupt Enable Registers (UART0\_IER = 00C1h, UART1\_IER = 00D1h)

| Bit                                    | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|----------------------------------------|---|---|---|---|-----|-----|-----|-----|

| Reset                                  | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |

| CPU Access                             | R | R | R | R | R/W | R/W | R/W | R/W |

| Note: R = Read only : R/W = Read/Write |   |   |   |   |     |     |     |     |

**Note:** R = Read only.; R/W = Read/Write.

| Bit      |       |                                                                                                                                                  |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Position | Value | Description                                                                                                                                      |

| [7:4]    | 0000  | Reserved                                                                                                                                         |

| 3        | 0     | Modem interrupt on edge detect of status inputs is disabled.                                                                                     |

| MIIE     | 1     | Modem interrupt on edge detect of status inputs is enabled.                                                                                      |

| 2        | 0     | Line status interrupt is disabled.                                                                                                               |

| LSIE     | 1     | Line status interrupt is enabled for receive data errors:<br>incorrect parity bit received, framing error, overrun error, or<br>break detection. |

6. When the SPI data transfer is complete, de-assert the ENABLE pin of the slave device.

#### Data Transfer Procedure with SPI Configured as a Slave

Follow the steps below for data transfer with SPI configured as the slave:

- 1. Load the SPI Baud Rate Generator Registers, SPI\_BRG\_H and SPI\_BRG\_L.

- 2. Load the SPI Transmit Shift Register, SPI\_TSR. This load cannot occur while the SPI slave is currently receiving data.

- 3. Wait for the external SPI Master device to initiate the data transfer by asserting  $\overline{SS}$ .

#### **SPI Registers**

There are six registers in the Serial Peripheral Interface which provide control, status, and data storage functions. The SPI registers are described in the following section.

#### SPI Baud Rate Generator Registers—Low Byte and High Byte

These registers hold the Low and High bytes of the 16-bit divisor count loaded by the processor for baud rate generation. The 16-bit clock divisor value is returned by {SPI\_BRG\_H, SPI\_BRG\_L}. Upon RESET, the 16-bit BRG divisor value resets to 0002h. When configured as a Master, the 16-bit divisor value must be between 0003h and FFFFh, inclusive. When configured as a Slave, the 16-bit divisor value must be between 0004h and FFFFh, inclusive.

A Write to either the Low or High byte registers for the BRG Divisor Latch causes both bytes to be loaded into the BRG counter and the count restarted. See Table 69 and Table 70.

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

#### Table 69. SPI Baud Rate Generator Register—Low Byte (SPI\_BRG\_L = 00B8h)

| Bit<br>Position    | Value   | Description                                                                                                                                              |

|--------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>SPI_BRG_L | 00h–FFh | These bits represent the Low byte of the 16-bit Baud Rate Generator divider value. The complete BRG divisor value is returned by {SPI_BRG_H, SPI_BRG_L}. |

is transmitted, the IFLG is set and the I2C\_SR register contains C8h and the  $I^2C$  returns to the idle state. The AAK bit must be set to 1 before reentering SLAVE mode.

If no acknowledge is received after transmitting a byte, the IFLG is set and the I2C\_SR register contains C0h. The  $I^2C$  then returns to the idle state.

If a STOP condition is detected after an acknowledge bit, the I<sup>2</sup>C returns to the idle state.

#### **Slave Receive**

In SLAVE RECEIVE mode, a number of data bytes are received from a master transmitter.

The I<sup>2</sup>C enters SLAVE RECEIVE mode when it receives its own slave address and a Write bit (lsb = 0) after a START condition. The I<sup>2</sup>C transmits an acknowledge bit and sets the IFLG bit in the I2C\_CTL register and the I2C\_SR register contains the status code 60h. The I<sup>2</sup>C also enters SLAVE RECEIVE mode when it receives the general call address 00h (if the GCE bit in the I2C\_SAR register is set). The status code is then 70h.

**Note:** When the I<sup>2</sup>C contains a 10-bit slave address (signified by F0h-F7h in the I2C\_SAR register), it transmits an acknowledge after the first address byte is received but no interrupt is generated. IFLG is not set and the status does not change. The I<sup>2</sup>C generates an interrupt only after the second address byte is received. The I<sup>2</sup>C sets the IFLG bit and loads the status code as described above.

I<sup>2</sup>C goes from MASTER mode to SLAVE RECEIVE mode when arbitration is lost during the transmission of an address, and the slave address and Write bit (or the general call address if the CGE bit in the I2C\_SAR register is set to 1) are received. The status code in the I2C\_SR register is 68h if the slave address is received or 78h if the general call address is received. The IFLG bit must be cleared to 0 to allow data transfer to continue.

If the AAK bit in the I2C\_CTL register is set to 1 then an acknowledge bit (Low level on SDA) is transmitted and the IFLG bit is set after each byte is received. The I2C\_SR register contains the status code 80h or 90h if SLAVE RECEIVE mode is entered with the general call address. The received data byte can be read from the I2C\_DR register and the IFLG bit must be cleared to allow the transfer to continue. If a STOP condition or a repeated START condition is detected after the acknowledge bit, the IFLG bit is set and the I2C\_SR register contains status code A0h.

If the AAK bit is cleared to 0 during a transfer, the  $I^2C$  transmits a not-acknowledge bit (High level on SDA) after the next byte is received, and set the IFLG bit. The I2C\_SR register contains the status code 88h or 98h if SLAVE RECEIVE mode is entered with the general call address. The  $I^2C$  returns to the idle state when the IFLG bit is cleared to 0.

| Code | Status                                                                                      |

|------|---------------------------------------------------------------------------------------------|

| B0h  | Arbitration lost in address as master, slave address and Read bit received, ACK transmitted |

| B8h  | Data byte transmitted in SLAVE mode, ACK received                                           |

| C0h  | Data byte transmitted in SLAVE mode, ACK not received                                       |

| C8h  | Last byte transmitted in SLAVE mode, ACK received                                           |

| D0h  | Second Address byte and Write bit transmitted, ACK received                                 |

| D8h  | Second Address byte and Write bit transmitted, ACK not received                             |

| F8h  | No relevant status information, IFLG = 0                                                    |

If an illegal condition occurs on the  $I^2C$  bus, the bus error state is entered (status code 00h). To recover from this state, the STP bit in the I2C\_CTL register must be set and the IFLG bit cleared. The  $I^2C$  then returns to the idle state. No STOP condition is transmitted on the  $I^2C$  bus.

**Note:** The STP and STA bits may be set to 1 at the same time to recover from the bus error. The  $I^2C$  then sends a START.

#### I<sup>2</sup>C Clock Control Register

The I2C\_CCR register is a Write-Only register. The seven LSBs control the frequency at which the I<sup>2</sup>C bus is sampled and the frequency of the I<sup>2</sup>C clock line (SCL) when the I<sup>2</sup>C is in MASTER mode. The Write-Only I2C\_CCR registers share the same I/O addresses as the Read-Only I2C\_SR registers. See Table 87.

| Bit                  | 7     | 6         | 5        | 4 | 3 | 2 | 1 | 0 |

|----------------------|-------|-----------|----------|---|---|---|---|---|

| Reset                | 0     | 0         | 0        | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | W     | W         | W        | W | W | W | W | W |

| Note: W = Read only. |       |           |          |   |   |   |   |   |

| Bit<br>Position      | Value | Des       | cription |   |   |   |   |   |

| 7                    | 0     | Reserved. |          |   |   |   |   |   |

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BRK_NEXT   | 0     | The ZDI BREAK on the next CPU instruction is disabled.<br>Clearing this bit releases the CPU from its current BREAK<br>condition.                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 1     | The ZDI BREAK on the next CPU instruction is enabled.<br>The CPU can use multibyte Op Codes and multibyte<br>operands. break points only occur on the first Op Code in a<br>multibyte Op Code instruction. If the ZCL pin is High and<br>the ZDA pin is Low at the end of RESET, this bit is set to 1<br>and a BREAK occurs on the first instruction following the<br>RESET. This bit is set automatically during ZDI BREAK on<br>address match. A BREAK can also be forced by writing a 1<br>to this bit. |

| 6<br>brk_addr3  | 0     | The ZDI BREAK, upon matching break address 3, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 3, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5<br>brk_addr2  | 0     | The ZDI BREAK, upon matching break address 2, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 2, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4<br>brk_addr1  | 0     | The ZDI BREAK, upon matching break address 1, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 1, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3<br>brk_addr0  | 0     | The ZDI BREAK, upon matching break address 0, is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 1     | The ZDI BREAK, upon matching break address 0, is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2<br>ign_low_1  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If BRK_ADDR1 is set to 1, ZDI<br>initiates a BREAK when the entire 24-bit address,<br>ADDR[23:0], matches the 3-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H, ZDI_ADDR1_L}.                                                                                                                                                                                                                                        |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If BRK_ADDR1 is set to 1, ZDI<br>initiates a BREAK when only the upper 2 bytes of the 24-bit<br>address, ADDR[23:8], match the 2-byte value<br>{ZDI_ADDR1_U, ZDI_ADDR1_H}. As a result, a BREAK<br>can occur anywhere within a 256-byte page.                                                                                                                                                                  |

#### **ZDI Write Data Registers**

These three registers are used in the ZDI Write-Only register address space to store the data that is written when a Write instruction is sent to the ZDI Read/Write Control register (ZDI\_RW\_CTL). The ZDI Read/Write Control register is located at ZDI address 16h immediately following the ZDI Write Data registers. As a result, the ZDI Master is allowed to write the data to {ZDI\_WR\_U, ZDI\_WR\_H, ZDI\_WR\_L} and the Write command in one data transfer operation. See Table 95.

# Table 95. ZDI Write Data Registers (ZDI\_WR\_U = 13h, ZDI\_WR\_H = 14h, and ZDI\_WR\_L = 15h in the ZDI Register Write-Only Address Space)

| Bit                             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------------------------|---|---|---|---|---|---|---|---|

| Reset                           | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access                      | W | W | W | W | W | W | W | W |

| Note: X = Undefined; W = Write. |   |   |   |   |   |   |   |   |

| Bit<br>Position                                   | Value   | Description                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>ZDI_WR_L,<br>ZDI_WR_H,<br>or<br>ZDI_WR_L | 00h–FFh | These registers contain the data that is written during execution of a Write operation defined by the ZDI_RW_CTL register. The 24-bit data value is stored as {ZDI_WR_U, ZDI_WR_H, ZDI_WR_L}. If less than 24 bits of data are required to complete the required operation, the data is taken from the least significant byte(s). |

#### **ZDI Read/Write Control Register**

The ZDI Read/Write Control register is used in the ZDI Write-Only Register address to read data from, write data to, and manipulate the CPU's registers or memory locations. When this register is written, the eZ80L92 immediately performs the operation corresponding to the data value written as described in Table 96.

When a Read operation is executed via this register, the requested data values are placed in the ZDI Read Data registers {ZDI\_RD\_U, ZDI\_RD\_H, ZDI\_RD\_L}. When a Write operation is executed via this register, the Write data is taken from the ZDI Write Data registers {ZDI\_WR\_U, ZDI\_WR\_H, ZDI\_WR\_L}. See Table 96. For more information on the CPU registers, refer to the *eZ80*<sup>®</sup> CPU User Manual (UM0077).

| Bit<br>Position     | Value   | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>zdi_wr_mem | 00h–FFh | The 8-bit data that is transferred to the ZDI slave<br>following a Write to this address is written to the address<br>indicated by the current program counter. The program<br>counter is incremented following each 8 bits of data. In<br>Z80 MEMORY mode, ({MBASE, PC[15:0]}) $\leftarrow$ 8 bits of<br>transferred data. In ADL MEMORY mode, (PC[23:0]) $\leftarrow$<br>8 bits of transferred data. |

#### eZ80<sup>®</sup> Product ID Low and High Byte Registers

The eZ80 Product ID Low and High Byte registers combine to provide a means for an external device to determine the particular eZ80 product being addressed. For the eZ80L92, these two bytes, {ZDI\_ID\_H, ZDI\_ID\_L} return the value {00h, 06h}. See Tables 100 and 101.

# Table 100. eZ80<sup>®</sup> Product ID Low Byte Register (ZDI\_ID\_L = 00h in the ZDI Register Read-Only Address Space)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read-only. |   |   |   |   |   |   |   |   |

| Bit<br>Position   | Value | Description                                                      |

|-------------------|-------|------------------------------------------------------------------|

| [7:0]<br>zdi_id_l | 06h   | {ZDI_ID_H, ZDI_ID_L} = {00h, 06h} indicates the eZ80L92 product. |

# Table 101. eZ80<sup>®</sup> Product ID High Byte Register (ZDI\_ID\_H = 01h in the ZDI Register Read-Only Address Space)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read-only. |   |   |   |   |   |   |   |   |

#### Table 108. Input/Output Instructions

| Mnemonic      | Instruction                               |

|---------------|-------------------------------------------|

| OUT0          | Output to I/O on Page 0                   |

| OUTD (OTDR)   | Output to I/O and Decrement (with Repeat) |

| OUTD2 (OTD2R) | Output to I/O and Decrement (with Repeat) |

| OUTI (OTIR)   | Output to I/O and Increment (with Repeat) |

| OUTI2 (OTI2R) | Output to I/O and Increment (with Repeat) |

| TSTIO         | Test I/O                                  |

#### Table 108. Load Instructions

| Mnemonic | Instruction            |

|----------|------------------------|

| LD       | Load                   |

| LEA      | Load Effective Address |

| PEA      | Push Effective Address |

| POP      | Рор                    |

| PUSH     | Push                   |

#### Table 108. Logical Instructions

| Mnemonic | Instruction            |

|----------|------------------------|

| AND      | Logical AND            |

| CPL      | Complement Accumulator |

| OR       | Logical OR             |

| TST      | Test Accumulator       |

| XOR      | Logical Exclusive OR   |

#### Table 108. Processor Control Instructions

| Mnemonic | Instruction           |

|----------|-----------------------|

| CCF      | Complement Carry Flag |

| DI       | Disable Interrupts    |

## **External Memory Read Timing**

Figure 48 and Table 121 illustrate the timing for external Reads.

Figure 48. External Memory Read Timing

#### Table 121. External Read Timing

|                |                                           | 20 MHz (ns) |      | 50 MHz (ns) |      |

|----------------|-------------------------------------------|-------------|------|-------------|------|

| Parameter      | Description                               | Min         | Max  | Min         | Max  |

| T <sub>1</sub> | Clock Rise to ADDR Valid Delay            | —           | 10.2 | —           | 10.2 |

| T <sub>2</sub> | Clock Rise to ADDR Hold Time              | 2.4         | _    | 2.4         | _    |

| T <sub>3</sub> | Input DATA Valid to Clock Rise Setup Time | 1.0         | _    | 1.0         | _    |

| T <sub>4</sub> | DATA Hold Time from Clock Rise            | 2.4         | _    | 2.4         | _    |

| T <sub>5</sub> | Clock Rise to CSx Assertion Delay         | 3.2         | 10.3 | 3.2         | 10.3 |

| T <sub>6</sub> | Clock Rise to CSx Deassertion Delay       | 2.9         | 9.7  | 2.9         | 9.7  |

| T <sub>7</sub> | Clock Rise to MREQ Assertion Delay        | 2.8         | 9.6  | 2.8         | 9.6  |

# Index

### **Numerics**

100-pin LQFP package 4, 2120 MHz Primary Crystal Oscillator Operation 19832 KHz Real-Time Clock Crystal Oscillator Operation 199

## Α

Absolute Maximum Ratings 201 Absolute maximum ratings 201 AC Characteristics 203 ACK 141, 145, 146, 147, 148, 149, 151, 156 Acknowledge 141 ADDR0 5, 21 ADDR1 5, 21 ADDR10 6, 21 ADDR117,21 ADDR12 7, 21 ADDR13 7, 21 ADDR14 7, 21 ADDR15 7, 21 ADDR16 8, 21 ADDR17 8, 21 ADDR18 8, 21 ADDR19 8, 21 ADDR2 5, 21 ADDR20 8, 22 ADDR21 9, 22 ADDR22 9, 22 ADDR23 9, 22 ADDR3 5, 21 ADDR4 5, 21 ADDR5 5, 21 ADDR6 6, 21 ADDR7 6, 21 ADDR8 6, 21 ADDR9 6, 21

Address Bus 5, 6, 7, 8, 9 address bus 45, 50, 53, 54, 56, 57, 58, 61, 64, 65, 68, 69, 90, 167, 176, 181 address bus, 24-bit 25 Addressing 151 Arbitration 143 Architectural Overview 1 asynchronous serial data 13, 15, 16

## В

Baud Rate Generator 104, 108 Baud Rate Generator Functional Description 133 Block Diagram 3 BRG Control Registers 109 Bus Arbitration Overview 139 Bus Mode Controller 53 Bus Requests During ZDI Debug Mode 167 BUSACK 12, 23, 53, 167, 175, 181, 214 BUSREQ 12, 23, 53, 167, 176, 181 Byte Format 141

## С

Characteristics, electrical Absolute maximum ratings 201 Chip Select Registers 67 Chip Select x Bus Mode Control Register 71 Chip Select x Control Register 70 Chip Select x Lower Bound Register 67 Chip Select x Upper Bound Register 69 Chip Select/Wait State Generator block 5, 6, 7, 8, 9 Chip Selects and Wait States 48 Chip Selects During Bus Request/Bus Acknowledge Cycles 53 Clear to Send 14, 16, 121 Clock Peripheral Power-Down Registers 35

Clock Synchronization 142 Clocking Overview 139 Continuous Mode 79 CPHA 129, 135 CPHA bit 132 CPOL 130, 135 CPOL bit 132 CSO 9, 22, 48, 49, 50, 51 CS1 9, 22, 48, 49, 50, 51 CS2 9, 22, 48, 50, 51 CS3 9, 22, 48, 50, 51 CTS 118, 121 CTS0 14, 125 CTS1 16 Customer Feedback Form 225

## D

DATA bus 61 Data Bus 10 data bus 53, 56, 57, 58, 65, 71, 90, 167, 176, 181 Data Carrier Detect 15, 17, 121 Data Set Ready 14, 17, 121 Data Terminal Ready 14, 17, 118 Data Transfer Procedure with SPI configured as a Slave 134 Data Transfer Procedure with SPI Configured as the Master 133 data transfer, SPI 136 Data Validity 140 DATA0 10, 22 DATA1 10, 22 DATA2 10, 22 DATA3 10, 22 DATA4 10, 22 DATA5 10, 22 DATA6 10, 22 DATA7 10, 22 DC Characteristics 201 DCD 118, 121 DCD0 15, 125 DCD1 17 DCTS 121 **DDCD 121**

DDSR 121 DSR 118, 121 DSR0 14, 125 DSR1 17 DTACK 64, 65 DTR 118, 121 DTR0 14, 125 DTR1 17

## Ε

**Edge-Triggered Interrupts 41** EI, Op Code Map 191 **Electrical Characteristics 201** Enabling and Disabling the WDT 74 Event Counter 81 External Bus Acknowledge Timing 214 External I/O Read Timing 208 External I/O Write Timing 209 **External Memory Read Timing 205** External Memory Write Timing 206 External System Clock Driver (PHI) Timing 214 eZ80 CPU 33, 34, 51, 53, 57, 58, 64, 65, 123, 169, 183 eZ80 CPU Core 31 eZ80 Product ID Low and High Byte Registers 178 eZ80 Product ID Revision Register 179 eZ80 Webserver-i 1, 4, 5, 10, 11, 12, 20, 25, 33, 34, 38, 44, 45, 48, 50, 73, 77, 80, 107, 109, 151, 158, 161, 162, 163, 165, 166, 169, 172, 173, 176, 177, 178, 179, 182, 186, 201, 203, 214, 216 eZ80 Webserver-i Block Diagram 3 eZ80L92 MCU 3

## F

f 21, 22, 54, 57 FAST mode 139, 158 Features 1 Features, eZ80 CPU Core 31 full-duplex transmission 131 Functional Description, Infrared Encoder/Decoder 123

Master Mode Stop bit 154 MASTER mode, SPI 132 Master Receive 139, 147 Master Transmit 144 MASTER TRANSMIT mode 139 master en bit 132 Master-In, Slave-Out 129 Master-Out, Slave-In 129 Memory and I/O Chip Selects 48 Memory Chip Select Example 49 Memory Chip Select Operation 48 Memory Chip Select Priority 49 Memory Request 11 memory space 48, 50 MISO 20, 129, 130, 131, 132 Mode Fault 132 mode fault 136 Mode Fault error flag 129 Mode Fault flag 132 Modem status signal 14, 15, 16, 17 MODF 129, 132, 136 MOSI 129, 130, 131, 132 Motorola Bus Mode 63 Motorola-compatible 53 MREQ 11, 12, 22, 48, 53, 54, 57, 58, 61 multimaster conflict 132, 136

## Ν

NACK 141, 145, 146, 147, 148, 149, 154, 156 New and Improved Instructions, eZ80 CPU Core 31 NMI 12, 22, 31, 35, 47, 73, 74, 75 Nonmaskable Interrupts 47 Not Acknowledge 141

## 0

OCI Activation 183 OCI Information Requests 185 OCI Interface 184 On-Chip Instrumentation 183 On-Chip Oscillators 198 Op Code maps 191 Open-Drain output 39 open-drain output 139 open-source output 13, 14, 15, 16, 17, 18, 19, 20 Operating Modes 144 Operation of the eZ80 Webserver-i during ZDI BREAKpoints 166 Ordering Information 216

## Ρ

Packaging 215 Part Number Description 216 PB0 18, 24, 80 PB1 18, 24, 81 PB2 19, 24 PB3 19, 24 PB4 19, 24, 40, 81 PB5 19, 24, 81 PB6 20, 24 PB7 20, 24, 38 PC0 15, 23 PC1 16, 23 PC2 16, 23 PC3 16, 23 PC4 17, 24 PC5 17, 24 PC6 17. 24 PC7 17, 24, 40 PD0 13, 126 PD1 13, 23, 126 PD2 14, 23, 126 PD3 14, 23 PD4 14, 23 PD5 14, 23 PD6 15, 23 PD7 15, 23, 126 Pin Characteristics 21 Pin Description 4 POP, Op Code Map 191, 193, 195 Port x Alternate Register 1 43 Port x Alternate Register 2 43 Port x Data Direction Registers 43 Port x Data Registers 42 Power connections 2 Programmable Reload Timer Operation 77

#### V

VCC 2

## W

WAIT 1, 11, 22, 58, 61, 64, 65 WAIT Input Signal 51 WAIT pin, external 53, 54 WAIT state 54, 62, 211, 212 Wait State Timing for Read Operations 211 Wait State Timing for Write Operations 212 WAIT states 45, 58, 61, 70, 167 Wait States 51 Watch-Dog Timer 73 Watch-Dog Timer Control Register 75 Watch-Dog Timer Operation 74 Watch-Dog Timer Registers 75 Watch-Dog Timer Reset Register 76 WCOL 132, 133 wcOl 136 WR 11, 22, 48, 51, 54, 58, 61, 210 Write Collision 133 write collision 132 write collision, SPI 136

## Ζ

Z80-53 Z80 Bus Mode 53 ZCL 162, 164, 171 ZDA 162, 171, 184 ZDI Address Match Registers 169 ZDI Block Read 166 **ZDI BLOCK WRITE 165** ZDI BREAK Control Register 170 ZDI Bus Control Register 175 ZDI Bus Status Register 181 ZDI Clock and Data Conventions 162 ZDI Master Control Register 172 ZDI Read Memory Register 182 **ZDI Read Operations 165** ZDI Read Register Low, High, and Upper 180 ZDI Read/Write Control Register 173

ZDI Read-Only Registers 169 ZDI Register Addressing 163 **ZDI Register Definitions 169** ZDI Single-Byte Read 165 ZDI SINGLE-BYTE WRITE 164 ZDI Start Condition 162 **ZDI Status Register 179** ZDI Write Data Registers 173 ZDI Write Memory Register 177 **ZDI Write Operations 164** ZDI Write-Only Registers 168 ZDI BUS STAT 167, 169, 181 ZDI BUSACK EN 167 ZDI BUSAcK En 181 ZDI-Supported Protocol 161 ZiLOG Debug Interface 160