Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 76                                                                               |

| Program Memory Size        | 192KB (192K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe164hm-24f80l-aa |

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1 | Summary of Features  Basic Device Types           | 10 |

|-----------------|---------------------------------------------------|----|

| 1.2             | Definition of Feature Variants                    | 11 |

| 2               | General Device Information                        |    |

| 2.1             | Pin Configuration and Definition                  |    |

| 2.2             | Identification Registers                          | 39 |

| 3               | Functional Description                            |    |

| 3.1             | Memory Subsystem and Organization                 |    |

| 3.2             | External Bus Controller                           |    |

| 3.3             | Central Processing Unit (CPU)                     |    |

| 3.4             | Memory Protection Unit (MPU)                      |    |

| 3.5             | Memory Checker Module (MCHK)                      |    |

| 3.6             | Interrupt System                                  |    |

| 3.7             | On-Chip Debug Support (OCDS)                      |    |

| 3.8             | Capture/Compare Unit (CAPCOM2)                    |    |

| 3.9             | Capture/Compare Units CCU6x                       |    |

| 3.10            | General Purpose Timer (GPT12E) Unit               |    |

| 3.11            | Real Time Clock                                   |    |

| 3.12            | A/D Converters                                    |    |

| 3.13            | Universal Serial Interface Channel Modules (USIC) |    |

| 3.14            | MultiCAN Module                                   |    |

| 3.15            | System Timer                                      |    |

| 3.16            | Watchdog Timer                                    |    |

| 3.17            | Clock Generation                                  |    |

| 3.18            | Parallel Ports                                    |    |

| 3.19            | Instruction Set Summary                           | 68 |

| 4               | Electrical Parameters                             |    |

| 4.1             | General Parameters                                |    |

| 4.1.1           | Absolut Maximum Rating Conditions                 |    |

| 4.1.2           | Operating Conditions                              |    |

| 4.1.3           | Pad Timing Definition                             |    |

| 4.1.4           | Parameter Interpretation                          |    |

| 4.2             | DC Parameters                                     |    |

| 4.2.1           | DC Parameters                                     |    |

| 4.2.2           | DC Parameters for Lower Voltage Area              |    |

| 4.2.3           | Power Consumption                                 |    |

| 4.3             | Analog/Digital Converter Parameters               |    |

| 4.4             | System Parameters                                 |    |

| 4.5             | Flash Memory Parameters                           | 93 |

**Summary of Features**

16-Bit Single-Chip Real Time Signal Controller XE164xM (XE166 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XE164xM are summarized here.

- · High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- Interrupt system with 16 priority levels for up to 96 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- · On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 32 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 576 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                    |

|-----|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | P7.4              | O0 / I | St/B | Bit 4 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                               |

|     | EMUX2             | O1     | St/B | External Analog MUX Control Output 2 (ADC1)                                                                                                                                                                                                                                 |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                           |

|     | U0C1_SCLK<br>OUT  | О3     | St/B | USIC0 Channel 1 Shift Clock Output                                                                                                                                                                                                                                          |

|     | CCU62_CCP<br>OS2A | I      | St/B | CCU62 Position Input 2                                                                                                                                                                                                                                                      |

|     | TCK_C             | IH     | St/B | DAPO/JTAG Clock Input If JTAG pos. C is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it. If DAP pos. 2 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |

|     | U0C0_DX0D         | I      | St/B | USIC0 Channel 0 Shift Data Input                                                                                                                                                                                                                                            |

|     | U0C1_DX1E         | I      | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                                                                                                                           |

| 11  | P6.0              | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output                                                                                                                                                                                                                               |

|     | EMUX0             | O1     | DA/A | External Analog MUX Control Output 0 (ADC0)                                                                                                                                                                                                                                 |

|     | TxDC2             | O2     | DA/A | CAN Node 2 Transmit Data Output                                                                                                                                                                                                                                             |

|     | BRKOUT            | О3     | DA/A | OCDS Break Signal Output                                                                                                                                                                                                                                                    |

|     | ADCx_REQG<br>TyG  | I      | DA/A | External Request Gate Input for ADC0/1                                                                                                                                                                                                                                      |

|     | U1C1_DX0E         | I      | DA/A | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                            |

| 12  | P6.1              | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output                                                                                                                                                                                                                               |

|     | EMUX1             | 01     | DA/A | External Analog MUX Control Output 1 (ADC0)                                                                                                                                                                                                                                 |

|     | T3OUT             | O2     | DA/A | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                         |

|     | U1C1_DOUT         | О3     | DA/A | USIC1 Channel 1 Shift Data Output                                                                                                                                                                                                                                           |

|     | ADCx_REQT<br>RyE  | I      | DA/A | External Request Trigger Input for ADC0/1                                                                                                                                                                                                                                   |

|     | RxDC2E            | I      | DA/A | CAN Node 2 Receive Data Input                                                                                                                                                                                                                                               |

|     | ESR1_6            | I      | DA/A | ESR1 Trigger Input 6                                                                                                                                                                                                                                                        |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 48  | P2.6              | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output  |

|     | U0C0_SELO<br>0    | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output        |

|     | U0C1_SELO<br>1    | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output        |

|     | CC2_CC19          | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.      |

|     | A19               | ОН     | St/B | External Bus Interface Address Line 19         |

|     | U0C0_DX2D         | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|     | RxDC0D            | I      | St/B | CAN Node 0 Receive Data Input                  |

|     | ESR2_6            | I      | St/B | ESR2 Trigger Input 6                           |

| 49  | P4.3              | O0 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CC2_CC27          | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.      |

|     | CS3               | ОН     | St/B | External Bus Interface Chip Select 3 Output    |

|     | RxDC2A            | I      | St/B | CAN Node 2 Receive Data Input                  |

|     | T2EUDA            | I      | St/B | GPT12E Timer T2 External Up/Down Control Input |

|     | CCU62_CCP<br>OS2B | I      | St/B | CCU62 Position Input 2                         |

| 53  | P0.0              | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output  |

|     | U1C0_DOUT         | 01     | St/B | USIC1 Channel 0 Shift Data Output              |

|     | CCU61_CC6<br>0    | О3     | St/B | CCU61 Channel 0 IOutput                        |

|     | A0                | ОН     | St/B | External Bus Interface Address Line 0          |

|     | U1C0_DX0A         | I      | St/B | USIC1 Channel 0 Shift Data Input               |

|     | CCU61_CC6<br>0INA | I      | St/B | CCU61 Channel 0 Input                          |

|     | ESR1_11           | I      | St/B | ESR1 Trigger Input 11                          |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 62  | P10.2             | O0 / I     | St/B | Bit 2 of Port 10, General Purpose Input/Output |

|     | U0C0_SCLK<br>OUT  | O1         | St/B | USIC0 Channel 0 Shift Clock Output             |

|     | CCU60_CC6<br>2    | O2         | St/B | CCU60 Channel 2 Output                         |

|     | AD2               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2     |

|     | CCU60_CC6<br>2INA | I          | St/B | CCU60 Channel 2 Input                          |

|     | U0C0_DX1B         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

| 63  | P0.4              | O0 / I     | St/B | Bit 4 of Port 0, General Purpose Input/Output  |

|     | U1C1_SELO<br>0    | O1         | St/B | USIC1 Channel 1 Select/Control 0 Output        |

|     | U1C0_SELO<br>1    | O2         | St/B | USIC1 Channel 0 Select/Control 1 Output        |

|     | CCU61_COU<br>T61  | О3         | St/B | CCU61 Channel 1 Output                         |

|     | A4                | ОН         | St/B | External Bus Interface Address Line 4          |

|     | U1C1_DX2A         | I          | St/B | USIC1 Channel 1 Shift Control Input            |

|     | RxDC1B            | I          | St/B | CAN Node 1 Receive Data Input                  |

|     | ESR2_8            | I          | St/B | ESR2 Trigger Input 8                           |

| 65  | P2.13             | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |

|     | U2C1_SELO<br>2    | O1         | St/B | USIC2 Channel 1 Select/Control 2 Output        |

|     | RxDC2D            | I          | St/B | CAN Node 2 Receive Data Input                  |

| 66  | P2.10             | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT         | O1         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | U0C0_SELO<br>3    | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CC2_CC23          | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|     | A23               | ОН         | St/B | External Bus Interface Address Line 23         |

|     | U0C1_DX0E         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CAPINA            | I          | St/B | GPT12E Register CAPREL Capture Input           |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                |

|-----|-------------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93  | P1.6              | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output                                                                                                                                                           |

|     | CCU62_CC6         | O1 / I | St/B | CCU62 Channel 1 Output                                                                                                                                                                                  |

|     | U1C1_SELO<br>2    | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output                                                                                                                                                                 |

|     | U2C0_DOUT         | О3     | St/B | USIC2 Channel 0 Shift Data Output                                                                                                                                                                       |

|     | A14               | ОН     | St/B | External Bus Interface Address Line 14                                                                                                                                                                  |

|     | U2C0_DX0D         | I      | St/B | USIC2 Channel 0 Shift Data Input                                                                                                                                                                        |

|     | CCU62_CC6<br>1INA | I      | St/B | CCU62 Channel 1 Input                                                                                                                                                                                   |

| 94  | P1.7              | O0 / I | St/B | Bit 7 of Port 1, General Purpose Input/Output                                                                                                                                                           |

|     | CCU62_CC6         | O1     | St/B | CCU62 Channel 0 Output                                                                                                                                                                                  |

|     | U1C1_MCLK<br>OUT  | O2     | St/B | USIC1 Channel 1 Master Clock Output                                                                                                                                                                     |

|     | U2C0_SCLK<br>OUT  | О3     | St/B | USIC2 Channel 0 Shift Clock Output                                                                                                                                                                      |

|     | A15               | ОН     | St/B | External Bus Interface Address Line 15                                                                                                                                                                  |

|     | U2C0_DX1C         | I      | St/B | USIC2 Channel 0 Shift Clock Input                                                                                                                                                                       |

|     | CCU62_CC6<br>0INA | I      | St/B | CCU62 Channel 0 Input                                                                                                                                                                                   |

| 95  | XTAL2             | 0      | Sp/M | Crystal Oscillator Amplifier Output                                                                                                                                                                     |

| 96  | XTAL1             | I      | Sp/M | Crystal Oscillator Amplifier Input To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\rm DDIM}$ . |

|     | ESR2_9            | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                    |

### **Functional Description**

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD<sup>1</sup>). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XE164xM to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

Data Sheet 57 V2.1, 2011-07

<sup>1)</sup> Exception: T5EUD is not connected to a pin.

### **Functional Description**

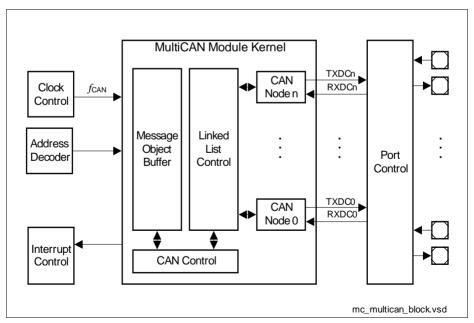

#### 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

**Electrical Parameters**

### 4 Electrical Parameters

The operating range for the XE164xM is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

### 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions  $(V_{\rm IN} > V_{\rm DDP} \text{ or } V_{\rm IN} < V_{\rm SS})$  the voltage on  $V_{\rm DDP}$  pins with respect to ground  $(V_{\rm SS})$  must not exceed the values defined by the absolute maximum ratings.

Table 11 Absolute Maximum Rating Parameters

| Parameter                                                 | Symbol                                      |      | Values | ;                      | Unit | Note /                     |

|-----------------------------------------------------------|---------------------------------------------|------|--------|------------------------|------|----------------------------|

|                                                           |                                             | Min. | Тур.   | Max.                   |      | Test Condition             |

| Output current on a pin when high value is driven         | $I_{OH}SR$                                  | -30  | -      | -                      | mA   |                            |

| Output current on a pin when low value is driven          | $I_{\rm OL}{\rm SR}$                        | _    | -      | 30                     | mA   |                            |

| Overload current                                          | $I_{OV}SR$                                  | -10  | _      | 10                     | mA   | 1)                         |

| Absolute sum of overload currents                         | $\Sigma  I_{ m OV} $ SR                     | _    | -      | 100                    | mA   | 1)                         |

| Junction Temperature                                      | $T_{J}SR$                                   | -40  | _      | 150                    | °C   |                            |

| Storage Temperature                                       | $T_{\rm ST}{ m SR}$                         | -65  | _      | 150                    | °C   |                            |

| Digital supply voltage for IO pads and voltage regulators | $V_{\rm DDPA}, \\ V_{\rm DDPB} \\ {\rm SR}$ | -0.5 | -      | 6.0                    | V    |                            |

| Voltage on any pin with respect to ground (Vss)           | $V_{IN}SR$                                  | -0.5 | _      | V <sub>DDP</sub> + 0.5 | V    | $V_{IN} \leq V_{DDP(max)}$ |

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

#### **Electrical Parameters**

## 4.2.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

Table 14 is valid under the following conditions:

$V_{\rm DDP} \ge 3.0 \text{ V}; \ V_{\rm DDPtvp} = 3.3 \text{ V}; \ V_{\rm DDP} \le 4.5 \text{ V}$

Table 14 DC Characteristics for Lower Voltage Range

| Parameter                                                                                   | Symbol                   |                                                                | Values |                                   | Unit | Note /                                                                                             |

|---------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------|--------|-----------------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                                                           | Тур.   | Max.                              |      | Test Condition                                                                                     |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                                                              | _      | 10                                | pF   | not subject to production test                                                                     |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | $\begin{array}{c} \text{0.07 x} \\ V_{\text{DDP}} \end{array}$ | -      | -                                 | V    | $R_{\rm S} = 0 \; {\rm Ohm}$                                                                       |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>OZ1</sub>  <br>CC | _                                                              | 10     | 200                               | nA   | $\begin{aligned} V_{\text{IN}} &> V_{\text{SS}}; \\ V_{\text{IN}} &< V_{\text{DDP}} \end{aligned}$ |

| Absolute input leakage current for all other pins. To be doubled for double                 | I <sub>OZ2</sub>  <br>CC | -                                                              | 0.2    | 2.5                               | μА   | $T_{\rm J} \leq 110~{\rm ^{\circ}C};$ $V_{\rm IN} < V_{\rm DDP};$ $V_{\rm IN} > V_{\rm SS}$        |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                                                              | 0.2    | 8                                 | μА   | $T_{\rm J} \leq 150~{\rm ^{\circ}C};$ $V_{\rm IN} < V_{\rm DDP};$ $V_{\rm IN} > V_{\rm SS}$        |

| Pull Level Force Current <sup>5)</sup>                                                      | $ I_{\rm PLF} $ SR       | 150                                                            | _      | _                                 |      | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                       | $ I_{\rm PLK} $ SR       | -                                                              | _      | 10                                | μА   | 6)                                                                                                 |

| Input high voltage (all except XTAL1)                                                       | $V_{IH}SR$               | $0.7~\mathrm{x}$ $V_\mathrm{DDP}$                              | -      | <i>V</i> <sub>DDP</sub> + 0.3     | V    |                                                                                                    |

| Input low voltage (all except XTAL1)                                                        | $V_{IL}SR$               | -0.3                                                           | -      | $0.3~\mathrm{x}$ $V_\mathrm{DDP}$ | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                           | $V_{OH}CC$               | V <sub>DDP</sub> - 1.0                                         | -      | _                                 | V    | $I_{OH} \geq I_{OHmax}$                                                                            |

|                                                                                             |                          | V <sub>DDP</sub> - 0.4                                         | -      | _                                 | V    | $I_{OH} \geq I_{OHnom}^{9)}$                                                                       |

#### **Electrical Parameters**

## 4.2.3 Power Consumption

The power consumed by the XE164xM depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current I<sub>S</sub> depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}$$

.

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

#### Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

### Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

Table 15 Switching Power Consumption

| Parameter                                                              | Symbol                  | Values |                                            |                      | Unit | Note /         |

|------------------------------------------------------------------------|-------------------------|--------|--------------------------------------------|----------------------|------|----------------|

|                                                                        |                         | Min.   | Тур.                                       | Max.                 |      | Test Condition |

| Power supply current (active) with all peripherals active and EVVRs on | I <sub>SACT</sub><br>CC | _      | 10 + $0.6 \text{ x}$ $f_{\text{SYS}}^{1)}$ | 10 + $f_{SYS}^{(1)}$ | mA   | 2)3)           |

| Power supply current in stopover mode, EVVRs on                        | I <sub>SSO</sub> CC     | _      | 0.7                                        | 2.0                  | mA   |                |

<sup>1)</sup>  $f_{SYS}$  in MHz.

#### **Electrical Parameters**

Table 16 Leakage Power Consumption

| Parameter                     | Symbol              |      | Values | ı    | Unit | Note /                                  |

|-------------------------------|---------------------|------|--------|------|------|-----------------------------------------|

|                               |                     | Min. | Тур.   | Max. |      | Test Condition                          |

| Leakage supply current        | I <sub>LK1</sub> CC | -    | 0.03   | 0.05 | mA   | $T_{\rm J} = 25  {\rm ^{\circ}C^{1)}}$  |

| (DMP_1 powered) <sup>1)</sup> |                     | _    | 0.5    | 1.3  | mA   | $T_{\rm J} = 85  ^{\circ}{\rm C}^{1)}$  |

|                               |                     | _    | 2.1    | 6.2  | mA   | $T_{\rm J} = 125  ^{\circ}{\rm C}^{1)}$ |

|                               |                     | _    | 4.4    | 13.7 | mA   | $T_{\rm J} = 150~{\rm ^{\circ}C^{1)}}$  |

All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at V<sub>DDP</sub> - 0.1 V to V<sub>DDP</sub> and all outputs (including pins configured as outputs) are disconnected.

Note: A fraction of the leakage current flows through domain DMP\_A (pin  $V_{DDPA}$ ). This current can be calculated as 7 000  $\times$  e<sup>- $\alpha$ </sup>, with  $\alpha$  = 5 000 / (273 + 1.3 $\times$ T<sub>J</sub>). For  $T_J$  = 150°C, this results in a current of 160  $\mu$ A.

The leakage power consumption can be calculated according to the following formulas:

$$I_{LK0} = 500\ 000 \times e^{-\alpha}$$

, with  $\alpha = 3\ 000\ /\ (273 + B \times T_{J})$

Parameter B must be replaced by

- 1.0 for typical values

- 1.6 for maximum values

$I_{\rm LK1} = 600~000 \times {\rm e}^{-\alpha}$ , with  $\alpha = 5~000 / (273 + {\rm B} \times T_{\rm J})$

Parameter B must be replaced by

- 1.0 for typical values

- 1.3 for maximum values

#### **Electrical Parameters**

- 3)  $f_{WU}$  in MHz

- 4) This value includes a hysteresis of approximately 50 mV for rising voltage.

- 5)  $V_{1V}$  = selected SWD voltage level

- 6) The limit  $V_{LV}$  0.10 V is valid for the OK1 level. The limit for the OK2 level is  $V_{LV}$  0.15 V.

### Conditions for $t_{SPO}$ Timing Measurement

The time required for the transition from **Power-On** to **Base** mode is called  $t_{SPO}$ . It is measured under the following conditions:

Precondition: The pad supply is valid, i.e.  $V_{\rm DDPB}$  is above 3.0 V and remains above 3.0 V even though the XE164xM is starting up. No debugger is attached.

Start condition: Power-on reset is removed ( $\overline{PORST} = 1$ ).

End condition: External pin toggle caused by first user instruction executed from FLASH after startup.

### Conditions for $t_{SSO}$ Timing Measurement

The time required for the transition from **Stopover** to **Stopover Waked-Up** mode is called  $t_{SSO}$ . It is measured under the following conditions:

Precondition: The **Stopover** mode has been entered using the procedure defined in the Programmer's Guide.

Start condition: Pin toggle on ESR pin triggering the startup sequence.

End condition: External pin toggle caused by first user instruction executed from PSRAM after startup.

## Coding of bit fields LEVxV in SWD and PVC Configuration Registers

Table 20 Coding of bit fields LEVxV in Register SWDCON0

| Code              | Default Voltage Level | Notes <sup>1)</sup>  |

|-------------------|-----------------------|----------------------|

| 0000 <sub>B</sub> | 2.9 V                 |                      |

| 0001 <sub>B</sub> | 3.0 V                 | LEV1V: reset request |

| 0010 <sub>B</sub> | 3.1 V                 |                      |

| 0011 <sub>B</sub> | 3.2 V                 |                      |

| 0100 <sub>B</sub> | 3.3 V                 |                      |

| 0101 <sub>B</sub> | 3.4 V                 |                      |

| 0110 <sub>B</sub> | 3.6 V                 |                      |

| 0111 <sub>B</sub> | 4.0 V                 |                      |

| 1000 <sub>B</sub> | 4.2 V                 |                      |

#### **Electrical Parameters**

### 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE164xM. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2

- By supplying an external clock signal

- This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain)

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . If connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Note: Operating Conditions apply.

Table 24 External Clock Input Characteristics

| Parameter                                      | Symbol                |                                    | Values | 5    | Unit | Note /                               |  |

|------------------------------------------------|-----------------------|------------------------------------|--------|------|------|--------------------------------------|--|

|                                                |                       | Min.                               | Тур.   | Max. |      | <b>Test Condition</b>                |  |

| Oscillator frequency                           | $f_{\rm OSC}{\rm SR}$ | 4                                  | _      | 40   | MHz  | Input = clock<br>signal              |  |

|                                                |                       | 4                                  | _      | 16   | MHz  | Input = crystal or ceramic resonator |  |

| XTAL1 input current absolute value             | I <sub>IL</sub>   CC  | _                                  | _      | 20   | μА   |                                      |  |

| Input clock high time                          | t <sub>1</sub> SR     | 6                                  | -      | _    | ns   |                                      |  |

| Input clock low time                           | t <sub>2</sub> SR     | 6                                  | -      | _    | ns   |                                      |  |

| Input clock rise time                          | t <sub>3</sub> SR     | _                                  | -      | 8    | ns   |                                      |  |

| Input clock fall time                          | $t_4$ SR              | _                                  | -      | 8    | ns   |                                      |  |

| Input voltage amplitude on XTAL11)             | $V_{AX1}SR$           | $0.3 \text{ x}$ $V_{\text{DDIM}}$  | _      | -    | V    | 4 to 16 MHz                          |  |

|                                                |                       | $0.4~\mathrm{x}$ $V_\mathrm{DDIM}$ | _      | -    | V    | 16 to 25 MHz                         |  |

|                                                |                       | $0.5~\mathrm{x}$ $V_\mathrm{DDIM}$ | _      | -    | V    | 25 to 40 MHz                         |  |

| Input voltage range limits for signal on XTAL1 | $V_{IX1}SR$           | $-1.7 + V_{\text{DDIM}}$           | _      | 1.7  | V    | 2)                                   |  |

### **Electrical Parameters**

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{\rm SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

### **Variable Memory Cycles**

External bus cycles of the XE164xM are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

Table 28 Programmable Bus Cycle Phases (see timing diagrams)

| <del>-</del>                                                                                                                   | -         | -            |      |

|--------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Bus Cycle Phase                                                                                                                | Parameter | Valid Values | Unit |

| Address setup phase, the standard duration of this phase (1 2 TCS) can be extended by 0 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                            | tpC       | 0 3          | TCS  |

| Write Data setup/MUX Tristate phase                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

#### **Electrical Parameters**

Table 30 EBC External Bus Timing for Lower Voltage Range

| Parameter                                                                                   | Symbol                    | Values |      |      | Unit | Note /                |

|---------------------------------------------------------------------------------------------|---------------------------|--------|------|------|------|-----------------------|

|                                                                                             |                           | Min.   | Тур. | Max. |      | <b>Test Condition</b> |

| Output valid delay for RD, WR(L/H)                                                          | t <sub>10</sub> CC        | _      | 11   | 20   | ns   |                       |

| Output valid delay for BHE, ALE                                                             | <i>t</i> <sub>11</sub> CC | _      | 10   | 21   | ns   |                       |

| Address output valid delay for A23 A0                                                       | t <sub>12</sub> CC        | _      | 11   | 22   | ns   |                       |

| Address output valid delay for AD15 AD0 (MUX mode)                                          | t <sub>13</sub> CC        | _      | 10   | 22   | ns   |                       |

| Output valid delay for CS                                                                   | t <sub>14</sub> CC        | -      | 10   | 13   | ns   |                       |

| Data output valid delay for AD15 AD0 (write data, MUX mode)                                 | t <sub>15</sub> CC        | -      | 10   | 22   | ns   |                       |

| Data output valid delay for D15 D0 (write data, DEMUX mode)                                 | t <sub>16</sub> CC        | -      | 10   | 22   | ns   |                       |

| Output hold time for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>20</sub> CC        | -2     | 8    | 10   | ns   |                       |

| Output hold time for BHE, ALE                                                               | t <sub>21</sub> CC        | -2     | 8    | 10   | ns   |                       |

| Address output hold time for AD15 AD0                                                       | t <sub>23</sub> CC        | -3     | 8    | 10   | ns   |                       |

| Output hold time for CS                                                                     | t <sub>24</sub> CC        | -3     | 8    | 11   | ns   |                       |

| Data output hold time for D15 D0 and AD15 AD0                                               | t <sub>25</sub> CC        | -3     | 8    | 10   | ns   |                       |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                          | t <sub>30</sub> SR        | 29     | 17   | -    | ns   |                       |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                                    | <i>t</i> <sub>31</sub> SR | 0      | -9   | -    | ns   |                       |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge

of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can

change after the rising edge of RD.

#### **Electrical Parameters**

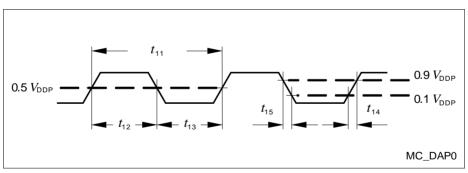

### 4.6.7 Debug Interface Timing

The debugger can communicate with the XE164xM either via the 2-pin DAP interface or via the standard JTAG interface.

### Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

Table 35 DAP Interface Timing for Upper Voltage Range

| Parameter                                      | Symbol             | Values           |      |      | Unit | Note /                 |

|------------------------------------------------|--------------------|------------------|------|------|------|------------------------|

|                                                |                    | Min.             | Тур. | Max. |      | Test Condition         |

| DAP0 clock period                              | t <sub>11</sub> SR | 25 <sup>1)</sup> | _    | _    | ns   |                        |

| DAP0 high time                                 | t <sub>12</sub> SR | 8                | _    | _    | ns   |                        |

| DAP0 low time                                  | t <sub>13</sub> SR | 8                | _    | _    | ns   |                        |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -                | _    | 4    | ns   |                        |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -                | _    | 4    | ns   |                        |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6                | -    | _    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6                | -    | _    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 17               | 20   | _    | ns   | pad_type= stan dard    |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

Data Sheet 118 V2.1, 2011-07

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

#### **Electrical Parameters**

Table 36 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol                    | Values           |      |      | Unit | Note /                |

|------------------------------------------------|---------------------------|------------------|------|------|------|-----------------------|

|                                                |                           | Min.             | Тур. | Max. |      | <b>Test Condition</b> |

| DAP0 clock period                              | t <sub>11</sub> SR        | 25 <sup>1)</sup> | _    | _    | ns   |                       |

| DAP0 high time                                 | t <sub>12</sub> SR        | 8                | _    | _    | ns   |                       |

| DAP0 low time                                  | t <sub>13</sub> SR        | 8                | _    | _    | ns   |                       |

| DAP0 clock rise time                           | t <sub>14</sub> SR        | -                | _    | 4    | ns   |                       |

| DAP0 clock fall time                           | t <sub>15</sub> SR        | -                | _    | 4    | ns   |                       |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR        | 6                | _    | _    | ns   | pad_type= stan dard   |

| DAP1 hold after DAP0 rising edge               | <i>t</i> <sub>17</sub> SR | 6                | _    | _    | ns   | pad_type= stan dard   |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC        | 12               | 17   | _    | ns   | pad_type= stan dard   |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 27 Test Clock Timing (DAP0)

Data Sheet 119 V2.1, 2011-07

#### **Electrical Parameters**

### **Debug via JTAG**

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_i$  = 20 pF.

Table 37 JTAG Interface Timing for Upper Voltage Range

| Parameter                                                                | Symbol             | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|--------------------|------------------|------|------|------|----------------|

|                                                                          |                    | Min.             | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR  | 50 <sup>1)</sup> | _    | _    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR  | 16               | _    | _    | ns   |                |

| TCK low time                                                             | $t_3$ SR           | 16               | _    | _    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR  | _                | _    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR  | _                | _    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR  | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR  | 6                | _    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC  | _                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC  | _                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | t <sub>10</sub> CC | _                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | t <sub>18</sub> CC | 5                | _    | _    | ns   |                |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

<sup>2)</sup> Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

<sup>3)</sup> The falling edge on TCK is used to generate the TDO timing.

<sup>4)</sup> The setup time for TDO is given implicitly by the TCK cycle time.

Package and Reliability

# 5 Package and Reliability

The XE166 Family devices use the package type PG-LQFP (Plastic Green - Low Profile Quad Flat Package). The following specifications must be regarded to ensure proper integration of the XE164xM in its target environment.

## 5.1 Packaging

These parameters specify the packaging rather than the silicon.

Table 39 Package Parameters (PG-LQFP-100-8)

| Parameter             | Symbol              | l Limit Values |           | Unit | Notes                         |  |

|-----------------------|---------------------|----------------|-----------|------|-------------------------------|--|

|                       |                     | Min.           | Max.      |      |                               |  |

| Exposed Pad Dimension | Ex × Ey             | _              | 6.2 × 6.2 | mm   | _                             |  |

| Power Dissipation     | $P_{DISS}$          | _              | 1.0       | W    | _                             |  |

| Thermal resistance    | $R_{\Theta \sf JA}$ | _              | 47        | K/W  | No thermal via <sup>1)</sup>  |  |

| Junction-Ambient      |                     |                | 29        | K/W  | 4-layer, no pad <sup>2)</sup> |  |

|                       |                     |                | 23        | K/W  | 4-layer, pad3)                |  |

Device mounted on a 2-layer JEDEC board (according to JESD 51-3) or a 4-layer board without thermal vias; exposed pad not soldered.

Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements.

Board layout examples are given in an application note.

### Package Compatibility Considerations

The XE164xM is a member of the XE166 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Pad (if present) may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.