Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 76                                                                               |

| Program Memory Size        | 384KB (384K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe164hm-48f80l-aa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Summary of Features**

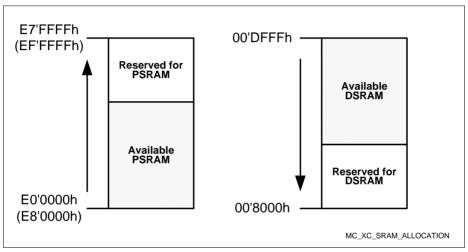

The XE164xM types are offered with several SRAM memory sizes. Figure 1 shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

#### **General Device Information**

#### **Key to Pin Definitions**

- Ctrl.: The output signal for a port pin is selected by bit field PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc.

- Output signal OH is controlled by hardware.

- Type: Indicates the pad type and its power supply domain (A, B, M, 1).

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DP: Double pad can be used as standard or high speed pad

- In: Input only pad

- PS: Power supply pad

Table 5 Pin Definitions and Functions

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                               |

|-----|-------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM             | I      | In/B | $\begin{tabular}{ll} \textbf{Testmode Enable} \\ \textbf{Enables factory test modes, must be held HIGH for} \\ \textbf{normal operation (connect to $V_{\rm DDPB}$).} \\ \textbf{An internal pull-up device will hold this pin high} \\ \textbf{when nothing is driving it.} \\ \end{tabular}$                                         |

| 4   | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                          |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                            |

|     | CCU62_CCP<br>OS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                 |

|     | TDI_C             | IH     | St/B | JTAG Test Data Input If JTAG pos. C is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.                                                                                                                                                                                        |

| 5   | TRST              | I      | In/B | Test-System Reset Input For normal system operation, pin TRST should be held low. A high level at this pin at the rising edge of PORST activates the XE164xM's debug system. In this case, pin TRST must be driven low once to reset the debug system. An internal pull-down device will hold this pin low when nothing is driving it. |

#### **General Device Information**

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Type | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 13  | P6.2             | O0 / I | DA/A | Bit 2 of Port 6, General Purpose Input/Output  |

|     | EMUX2            | 01     | DA/A | External Analog MUX Control Output 2 (ADC0)    |

|     | T6OUT            | O2     | DA/A | GPT12E Timer T6 Toggle Latch Output            |

|     | U1C1_SCLK<br>OUT | О3     | DA/A | USIC1 Channel 1 Shift Clock Output             |

|     | U1C1_DX1C        | I      | DA/A | USIC1 Channel 1 Shift Clock Input              |

| 15  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input        |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1                |

| 16  | P15.2            | I      | In/A | Bit 2 of Port 15, General Purpose Input        |

|     | ADC1_CH2         | I      | In/A | Analog Input Channel 2 for ADC1                |

|     | T5INA            | I      | In/A | GPT12E Timer T5 Count/Gate Input               |

| 17  | P15.4            | I      | In/A | Bit 4 of Port 15, General Purpose Input        |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1                |

|     | T6INA            | I      | In/A | GPT12E Timer T6 Count/Gate Input               |

| 18  | P15.5            | I      | In/A | Bit 5 of Port 15, General Purpose Input        |

|     | ADC1_CH5         | I      | In/A | Analog Input Channel 5 for ADC1                |

|     | T6EUDA           | I      | In/A | GPT12E Timer T6 External Up/Down Control Input |

| 19  | P15.6            | I      | In/A | Bit 6 of Port 15, General Purpose Input        |

|     | ADC1_CH6         | I      | In/A | Analog Input Channel 6 for ADC1                |

| 20  | $V_{AREF}$       | -      | PS/A | Reference Voltage for A/D Converters ADC0/1    |

| 21  | $V_{AGND}$       | -      | PS/A | Reference Ground for A/D Converters ADC0/1     |

| 22  | P5.0             | I      | In/A | Bit 0 of Port 5, General Purpose Input         |

|     | ADC0_CH0         | I      | In/A | Analog Input Channel 0 for ADC0                |

| 23  | P5.2             | I      | In/A | Bit 2 of Port 5, General Purpose Input         |

|     | ADC0_CH2         | I      | In/A | Analog Input Channel 2 for ADC0                |

|     | TDI_A            | I      | In/A | JTAG Test Data Input                           |

### **General Device Information**

Table 5 Pin Definitions and Functions (cont'd)

|     | 1                 | 1      |      |                                                                                                                                                                                                                                                                               |

|-----|-------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                      |

| 57  | P2.9              | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                 |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                             |

|     | TxDC1             | O2     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                               |

|     | CC2_CC22          | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                     |

|     | A22               | ОН     | St/B | External Bus Interface Address Line 22                                                                                                                                                                                                                                        |

|     | CLKIN1            | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                          |

|     | TCK_A             | IH     | St/B | DAPO/JTAG Clock Input  If JTAG pos. A is selected during start-up, an internal pull-up device will hold this pin high when nothing is driving it.  If DAP pos. 0 is selected during start-up, an internal pull-down device will hold this pin low when nothing is driving it. |

| 58  | P0.2              | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output                                                                                                                                                                                                                                 |

|     | U1C0_SCLK<br>OUT  | O1     | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                                                                                                                            |

|     | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                               |

|     | CCU61_CC6         | О3     | St/B | CCU61 Channel 2 Output                                                                                                                                                                                                                                                        |

|     | A2                | ОН     | St/B | External Bus Interface Address Line 2                                                                                                                                                                                                                                         |

|     | U1C0_DX1B         | I      | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                             |

|     | CCU61_CC6<br>2INA | I      | St/B | CCU61 Channel 2 Input                                                                                                                                                                                                                                                         |

## **Functional Description**

# 3.1 Memory Subsystem and Organization

The memory space of the XE164xM is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

Table 7 XE164xM Memory Map 1)

| Tubic 7 AETO-AIII                    | moniory ma           | Υ                    |                         |                     |

|--------------------------------------|----------------------|----------------------|-------------------------|---------------------|

| Address Area                         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes               |

| IMB register space                   | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes               | -                   |

| Reserved (Access trap)               | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | <1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM                  | E8'8000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors EPSRAM      |

| Emulated PSRAM                       | E8'0000 <sub>H</sub> | E8'7FFF <sub>H</sub> | 32 Kbytes               | With Flash timing   |

| Reserved for PSRAM                   | E0'8000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors PSRAM       |

| Program SRAM                         | E0'0000 <sub>H</sub> | E0'7FFF <sub>H</sub> | 32 Kbytes               | Maximum speed       |

| Reserved for Flash                   | CD'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | <1.25 Mbytes            | -                   |

| Program Flash 3                      | CC'0000 <sub>H</sub> | CC'FFFF <sub>H</sub> | 64 Kbytes               | -                   |

| Program Flash 2                      | C8'0000 <sub>H</sub> | CB'FFFF <sub>H</sub> | 256 Kbytes              | _                   |

| Program Flash 1                      | C4'0000 <sub>H</sub> | C7'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 0                      | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes              | 3)                  |

| External memory area                 | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                | -                   |

| Available Ext. IO area <sup>4)</sup> | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus USIC/CAN      |

| Reserved                             | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes               | -                   |

| USIC alternate regs.                 | 20'B000 <sub>H</sub> | 20'BFFF <sub>H</sub> | 4 Kbytes                | Accessed via EBC    |

| MultiCAN alternate regs.             | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes               | Accessed via EBC    |

| Reserved                             | 20'6000 <sub>H</sub> | 20'7FFF <sub>H</sub> | 8 Kbytes                | _                   |

| USIC registers                       | 20'4000 <sub>H</sub> | 20'5FFF <sub>H</sub> | 8 Kbytes                | Accessed via EBC    |

| MultiCAN registers                   | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes               | Accessed via EBC    |

| External memory area                 | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0     |

| SFR area                             | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbyte               | -                   |

| Dual-Port RAM                        | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                | _                   |

| Reserved for DPRAM                   | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbyte                 | _                   |

| ESFR area                            | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbyte               | -                   |

| XSFR area                            | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                | _                   |

|                                      |                      |                      |                         |                     |

### **Functional Description**

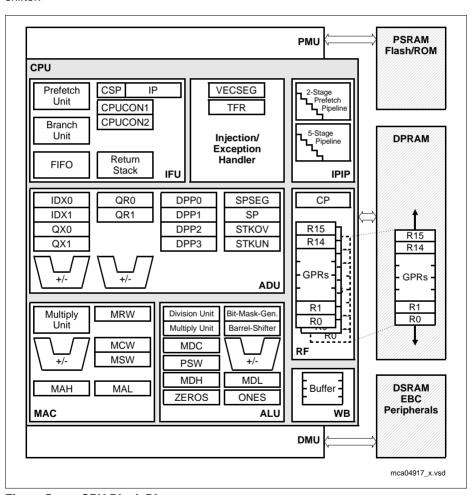

## 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

Figure 5 CPU Block Diagram

### **Functional Description**

to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

## 3.7 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XE164xM provides a broad range of debug and emulation features. User software running on the XE164xM can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This either consists of the 2-pin Device Access Port (DAP) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XE166 Family emulation device.

The DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

Data Sheet 49 V2.1, 2011-07

### **Functional Description**

## 3.8 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range or variation for the timer period and resolution and allows precise adjustments to the application-specific requirements. In addition, an external count input allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

Table 8 Compare Modes

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

### **Functional Description**

#### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

### **Functional Description**

# 3.19 Instruction Set Summary

Table 10 lists the instructions of the XE164xM.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 10 Instruction Set Summary

| Mnemonic      | Description                                                                                       | Bytes |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-------|--|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                     |       |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |  |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- × 16-bit)                                       | 2     |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |  |  |

| ВСМР          | Compare direct bit to direct bit                                                                  | 4     |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |  |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |  |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |  |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |  |  |

## **Functional Description**

Table 10 Instruction Set Summary (cont'd)

| Mnemonic     | Description                                                                           | Bytes |

|--------------|---------------------------------------------------------------------------------------|-------|

| ROL/ROR      | Rotate left/right direct word GPR                                                     | 2     |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                     | 2     |

| MOV(B)       | Move word (byte) data                                                                 | 2/4   |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                | 2/4   |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                   | 4     |

| JMPS         | Jump absolute to a code segment                                                       | 4     |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                    | 4     |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                  | 4     |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                        | 4     |

| CALLS        | Call absolute subroutine in any code segment                                          | 4     |

| PCALL        | Push direct word register onto system stack and call absolute subroutine              | 4     |

| TRAP         | Call interrupt service routine via immediate trap number                              | 2     |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                  | 2     |

| SCXT         | Push direct word register onto system stack and update register with word operand     | 4     |

| RET(P)       | Return from intra-segment subroutine (and pop direct word register from system stack) | 2     |

| RETS         | Return from inter-segment subroutine                                                  | 2     |

| RETI         | Return from interrupt service subroutine                                              | 2     |

| SBRK         | Software Break                                                                        | 2     |

| SRST         | Software Reset                                                                        | 4     |

| IDLE         | Enter Idle Mode                                                                       | 4     |

| PWRDN        | Unused instruction <sup>1)</sup>                                                      | 4     |

| SRVWDT       | Service Watchdog Timer                                                                | 4     |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                         | 4     |

| EINIT        | End-of-Initialization Register Lock                                                   | 4     |

| ATOMIC       | Begin ATOMIC sequence                                                                 | 2     |

| EXTR         | Begin EXTended Register sequence                                                      | 2     |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                           | 2/4   |

| EXTS(R)      | Begin EXTended Segment (and Register) sequence                                        | 2/4   |

## **Functional Description**

Table 10 Instruction Set Summary (cont'd)

| Mnemonic     | Description                         | Bytes |

|--------------|-------------------------------------|-------|

| NOP          | Null operation                      | 2     |

| CoMUL/CoMAC  | Multiply (and accumulate)           | 4     |

| CoADD/CoSUB  | Add/Subtract                        | 4     |

| Co(A)SHR     | (Arithmetic) Shift right            | 4     |

| CoSHL        | Shift left                          | 4     |

| CoLOAD/STORE | Load accumulator/Store MAC register | 4     |

| CoCMP        | Compare                             | 4     |

| CoMAX/MIN    | Maximum/Minimum                     | 4     |

| CoABS/CoRND  | Absolute value/Round accumulator    | 4     |

| CoMOV        | Data move                           | 4     |

| CoNEG/NOP    | Negate accumulator/Null operation   | 4     |

The Enter Power Down Mode instruction is not used in the XE164xM, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

#### **Electrical Parameters**

Table 12 Operating Conditions (cont'd)

| Parameter                                                 | Symbol               | Values |      |      | Unit | Note /                         |

|-----------------------------------------------------------|----------------------|--------|------|------|------|--------------------------------|

|                                                           |                      | Min.   | Тур. | Max. |      | Test Condition                 |

| Absolute sum of overload currents                         | $\Sigma  I_{OV} $ SR | _      | _    | 50   | mA   | not subject to production test |

| Digital core supply voltage for domain M <sup>8)</sup>    | $V_{DDIM}$           | -      | 1.5  | -    |      |                                |

| Digital core supply voltage for domain 18)                | $V_{ m DDI1}$ CC     | _      | 1.5  | _    |      |                                |

| Digital supply voltage for IO pads and voltage regulators | $V_{DDP}SR$          | 4.5    | -    | 5.5  | V    |                                |

| Digital ground voltage                                    | $V_{\rm SS}$ SR      | _      | 0    | _    | V    |                                |

- 1) To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each  $V_{\rm DDIM}$  and  $V_{\rm DDIM}$  pin to keep the resistance of the board tracks below 2 Ohm. Connect all  $V_{\rm DDIM}$  pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the PAD properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>1</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 80 MHz devices are marked ...F80L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by V<sub>DDIM</sub>).

- 7) An overload current  $(I_{\text{OV}})$  through a pin injects a certain error current  $(I_{\text{IN,I}})$  into the adjacent pins. This error current adds to the respective pins leakage current  $(I_{\text{OZ}})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{\text{OV}}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{\text{TOT}}| = |I_{\text{OZ}}| + (|I_{\text{OV}}| K_{\text{OV}})$ . The additional error current may distort the input voltage on analog inputs.

- 8) Value is controlled by on-chip regulator

#### **Electrical Parameters**

## 4.5 Flash Memory Parameters

The XE164xM is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XE164xM's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been

erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or

characterization.

Note: Operating Conditions apply.

Table 22 Flash Parameters

| Parameter                                 | Symbol                       |      | Values          | 5               | Unit       | Note /                                     |

|-------------------------------------------|------------------------------|------|-----------------|-----------------|------------|--------------------------------------------|

|                                           |                              | Min. | Тур.            | Max.            |            | Test Condition                             |

| Parallel Flash module program/erase limit | $N_{PP}SR$                   | _    | _               | 41)             |            | $N_{FL\_RD} \leq 1, \ f_{SYS} \leq 80~MHz$ |

| depending on Flash read activity          |                              | -    | _               | 1 <sup>2)</sup> |            | $N_{\text{FL\_RD}} > 1$                    |

| Flash erase endurance for security pages  | N <sub>SEC</sub> SR          | 10   | -               | _               | cycle<br>s | t <sub>RET</sub> ≥ 20 years                |

| Flash wait states <sup>3)</sup>           | $N_{\mathrm{WSFLAS}}$        | 1    | _               | _               |            | $f_{\rm SYS} \le 8 \; \rm MHz$             |

|                                           | <sub>H</sub> SR              | 2    | _               | _               |            | $f_{\rm SYS} \le$ 13 MHz                   |

|                                           |                              | 3    | _               | _               |            | $f_{\rm SYS} \leq$ 17 MHz                  |

|                                           |                              | 4    | _               | _               |            | $f_{\rm SYS}$ > 17 MHz                     |

| Erase time per sector/page                | $t_{\sf ER}$ CC              | _    | 7 <sup>4)</sup> | 8.0             | ms         |                                            |

| Programming time per page                 | t <sub>PR</sub> CC           | _    | 3 <sup>4)</sup> | 3.5             | ms         |                                            |

| Data retention time                       | $t_{RET}CC$                  | 20   | _               | _               | year<br>s  | $N_{\rm Er} \le 1~000$ cycles              |

| Drain disturb limit                       | $N_{\mathrm{DD}}\mathrm{SR}$ | 32   | -               | -               | cycle<br>s |                                            |

#### **Electrical Parameters**

Table 22 Flash Parameters (cont'd)

| Parameter              | Symbol             |      | Values |        | Unit       | Note /                                                                                         |  |

|------------------------|--------------------|------|--------|--------|------------|------------------------------------------------------------------------------------------------|--|

|                        |                    | Min. | Тур.   | Max.   |            | Test Condition                                                                                 |  |

| Number of erase cycles | N <sub>Er</sub> SR | _    | _      | 15 000 | cycle<br>s | $t_{RET} \ge 5$ years;<br>Valid for up to<br>64 user-<br>selected<br>sectors (data<br>storage) |  |

|                        |                    | _    | -      | 1 000  | cycle<br>s | t <sub>RET</sub> ≥ 20 years                                                                    |  |

- All Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

- Flash module 3 can be erased/programmed while code is executed and/or data is read from any other Flash module.

- 3) Value of IMB\_IMBCTRL.WSFLASH.

- 4) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This increases the stated durations noticably only at extremely low system clock frequencies.

Access to the XE164xM Flash modules is controlled by the IMB. Built-in prefetch mechanisms optimize the performance for sequential access.

Flash access waitstates only affect non-sequential access. Due to prefetch mechanisms, the performance for sequential access (depending on the software structure) is only partially influenced by waitstates.

#### **Electrical Parameters**

#### **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$$f_{SYS} = f_{IN}$$

.

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

#### **Prescaler Operation**

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$$f_{SYS} = f_{OSC} / 1024$$

.

# 4.6.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor  $\mathbf{F}$  ( $f_{\rm SYS} = f_{\rm IN} \times \mathbf{F}$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$$(F = N / (P \times K2)).$$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{\rm SYS}$  so that it is locked to  $f_{\rm IN}$ . The slight variation causes a jitter of  $f_{\rm SYS}$  which in turn affects the duration of individual TCSs.

Data Sheet 97 V2.1, 2011-07

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\rm DDIM}$

**Electrical Parameters**

## 4.6.4 Pad Properties

The output pad drivers of the XE164xM can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\rm DDP}$ . The following table lists the pad parameters.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

#### **Electrical Parameters**

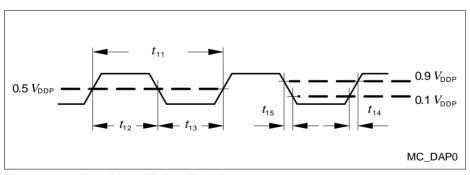

### 4.6.7 Debug Interface Timing

The debugger can communicate with the XE164xM either via the 2-pin DAP interface or via the standard JTAG interface.

## Debug via DAP

The following parameters are applicable for communication through the DAP debug interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_1$  = 20 pF.

Table 35 DAP Interface Timing for Upper Voltage Range

| Parameter                                      | Symbol             | Values           |      |      | Unit | Note /              |

|------------------------------------------------|--------------------|------------------|------|------|------|---------------------|

|                                                |                    | Min.             | Тур. | Max. |      | Test Condition      |

| DAP0 clock period                              | t <sub>11</sub> SR | 25 <sup>1)</sup> | _    | _    | ns   |                     |

| DAP0 high time                                 | t <sub>12</sub> SR | 8                | _    | _    | ns   |                     |

| DAP0 low time                                  | t <sub>13</sub> SR | 8                | _    | _    | ns   |                     |

| DAP0 clock rise time                           | t <sub>14</sub> SR | -                | _    | 4    | ns   |                     |

| DAP0 clock fall time                           | t <sub>15</sub> SR | -                | _    | 4    | ns   |                     |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR | 6                | _    | _    | ns   | pad_type= stan dard |

| DAP1 hold after DAP0 rising edge               | t <sub>17</sub> SR | 6                | -    | _    | ns   | pad_type= stan dard |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC | 17               | 20   | _    | ns   | pad_type= stan dard |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

#### **Electrical Parameters**

Table 36 DAP Interface Timing for Lower Voltage Range

| Parameter                                      | Symbol                    | Values           |      |      | Unit | Note /                |

|------------------------------------------------|---------------------------|------------------|------|------|------|-----------------------|

|                                                |                           | Min.             | Тур. | Max. |      | <b>Test Condition</b> |

| DAP0 clock period                              | t <sub>11</sub> SR        | 25 <sup>1)</sup> | _    | _    | ns   |                       |

| DAP0 high time                                 | t <sub>12</sub> SR        | 8                | _    | _    | ns   |                       |

| DAP0 low time                                  | t <sub>13</sub> SR        | 8                | _    | _    | ns   |                       |

| DAP0 clock rise time                           | t <sub>14</sub> SR        | -                | _    | 4    | ns   |                       |

| DAP0 clock fall time                           | t <sub>15</sub> SR        | -                | _    | 4    | ns   |                       |

| DAP1 setup to DAP0 rising edge                 | t <sub>16</sub> SR        | 6                | _    | _    | ns   | pad_type= stan dard   |

| DAP1 hold after DAP0 rising edge               | <i>t</i> <sub>17</sub> SR | 6                | _    | _    | ns   | pad_type= stan dard   |

| DAP1 valid per DAP0 clock period <sup>2)</sup> | t <sub>19</sub> CC        | 12               | 17   | _    | ns   | pad_type= stan dard   |

<sup>1)</sup> The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

<sup>2)</sup> The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 27 Test Clock Timing (DAP0)

www.infineon.com

Published by Infineon Technologies AG