Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 76                                                                               |

| Program Memory Size        | 576KB (576K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe164fm72f80laakxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Device Information**

# 2 General Device Information

### The XE164xM series (16-Bit Single-Chip

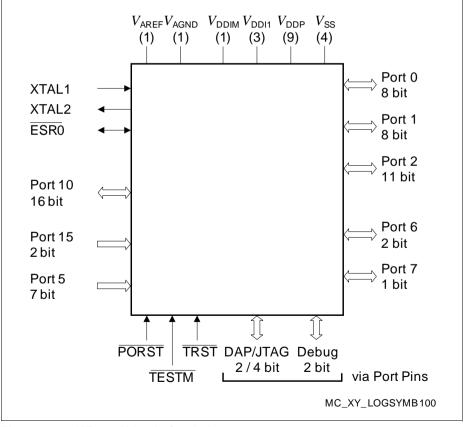

Real Time Signal Controller) is a part of the Infineon XE166 Family of full-feature singlechip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

Figure 2 XE164xM Logic Symbol

| Table 5         Pin Definitions and Functions (cont'd) |                   |        |      |                                                   |

|--------------------------------------------------------|-------------------|--------|------|---------------------------------------------------|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                          |

| 13                                                     | P6.2              | O0 / I | DA/A | Bit 2 of Port 6, General Purpose Input/Output     |

|                                                        | EMUX2             | 01     | DA/A | External Analog MUX Control Output 2 (ADC0)       |

|                                                        | T6OUT             | 02     | DA/A | GPT12E Timer T6 Toggle Latch Output               |

|                                                        | U1C1_SCLK<br>OUT  | O3     | DA/A | USIC1 Channel 1 Shift Clock Output                |

|                                                        | U1C1_DX1C         | I      | DA/A | USIC1 Channel 1 Shift Clock Input                 |

| 15                                                     | P15.0             | I      | In/A | Bit 0 of Port 15, General Purpose Input           |

|                                                        | ADC1_CH0          | I      | In/A | Analog Input Channel 0 for ADC1                   |

| 16                                                     | P15.2             | I      | In/A | Bit 2 of Port 15, General Purpose Input           |

|                                                        | ADC1_CH2          | I      | In/A | Analog Input Channel 2 for ADC1                   |

|                                                        | T5INA             | I      | In/A | GPT12E Timer T5 Count/Gate Input                  |

| 17                                                     | P15.4             | I      | In/A | Bit 4 of Port 15, General Purpose Input           |

| -                                                      | ADC1_CH4          | I      | In/A | Analog Input Channel 4 for ADC1                   |

|                                                        | T6INA             | I      | In/A | GPT12E Timer T6 Count/Gate Input                  |

| 18                                                     | P15.5             | I      | In/A | Bit 5 of Port 15, General Purpose Input           |

|                                                        | ADC1_CH5          | I      | In/A | Analog Input Channel 5 for ADC1                   |

|                                                        | T6EUDA            | I      | In/A | GPT12E Timer T6 External Up/Down Control<br>Input |

| 19                                                     | P15.6             | I      | In/A | Bit 6 of Port 15, General Purpose Input           |

|                                                        | ADC1_CH6          | I      | In/A | Analog Input Channel 6 for ADC1                   |

| 20                                                     | V <sub>AREF</sub> | -      | PS/A | Reference Voltage for A/D Converters ADC0/1       |

| 21                                                     | V <sub>AGND</sub> | -      | PS/A | Reference Ground for A/D Converters ADC0/1        |

| 22                                                     | P5.0              | I      | In/A | Bit 0 of Port 5, General Purpose Input            |

|                                                        | ADC0_CH0          | I      | In/A | Analog Input Channel 0 for ADC0                   |

| 23                                                     | P5.2              | I      | In/A | Bit 2 of Port 5, General Purpose Input            |

|                                                        | ADC0_CH2          | I      | In/A | Analog Input Channel 2 for ADC0                   |

|                                                        | TDI_A             | 1      | In/A | JTAG Test Data Input                              |

| Table 5Pin Definitions and Functions (cont'd) |                   |        |      |                                               |

|-----------------------------------------------|-------------------|--------|------|-----------------------------------------------|

| Pin                                           | Symbol            | Ctrl.  | Туре | Function                                      |

| 45                                            | P2.4              | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output |

|                                               | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output             |

|                                               | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output               |

|                                               | CC2_CC17          | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.     |

|                                               | A17               | ОН     | St/B | External Bus Interface Address Line 17        |

|                                               | ESR1_0            | I      | St/B | ESR1 Trigger Input 0                          |

|                                               | U0C0_DX0F         | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|                                               | RxDC1A            | I      | St/B | CAN Node 1 Receive Data Input                 |

| 46                                            | P2.5              | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output |

| -                                             | U0C0_SCLK<br>OUT  | O1     | St/B | USIC0 Channel 0 Shift Clock Output            |

|                                               | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output               |

|                                               | CC2_CC18          | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.     |

|                                               | A18               | OH     | St/B | External Bus Interface Address Line 18        |

|                                               | U0C0_DX1D         | I      | St/B | USIC0 Channel 0 Shift Clock Input             |

|                                               | ESR1_10           | I      | St/B | ESR1 Trigger Input 10                         |

| 47                                            | P4.2              | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output |

|                                               | TxDC2             | 02     | St/B | CAN Node 2 Transmit Data Output               |

|                                               | CC2_CC26          | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.     |

|                                               | CS2               | ОН     | St/B | External Bus Interface Chip Select 2 Output   |

|                                               | T2INA             | I      | St/B | GPT12E Timer T2 Count/Gate Input              |

|                                               | CCU62_CCP<br>OS1B | 1      | St/B | CCU62 Position Input 1                        |

## XE164FM, XE164GM, XE164HM, XE164KM XE166 Family / Base Line

| Table | Pin Definitions and Functions (cont'd) |            |      |                                                |  |

|-------|----------------------------------------|------------|------|------------------------------------------------|--|

| Pin   | Symbol                                 | Ctrl.      | Туре | Function                                       |  |

| 73    | P10.7                                  | O0 / I     | St/B | Bit 7 of Port 10, General Purpose Input/Output |  |

|       | U0C1_DOUT                              | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |

|       | CCU60_COU<br>T63                       | O2         | St/B | CCU60 Channel 3 Output                         |  |

|       | AD7                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 7     |  |

|       | U0C1_DX0B                              | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |

|       | CCU60_CCP<br>OS0A                      | I          | St/B | CCU60 Position Input 0                         |  |

|       | T4INB                                  | I          | St/B | GPT12E Timer T4 Count/Gate Input               |  |

| 74    | P0.7                                   | O0 / I     | St/B | Bit 7 of Port 0, General Purpose Input/Output  |  |

|       | U1C1_DOUT                              | 01         | St/B | USIC1 Channel 1 Shift Data Output              |  |

| _     | U1C0_SELO<br>3                         | O2         | St/B | USIC1 Channel 0 Select/Control 3 Output        |  |

|       | TxDC3                                  | O3         | St/B | CAN Node 3 Transmit Data Output                |  |

|       | A7                                     | ОН         | St/B | External Bus Interface Address Line 7          |  |

|       | U1C1_DX0B                              | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |

|       | CCU61_CTR<br>APB                       | 1          | St/B | CCU61 Emergency Trap Input                     |  |

| 78    | P1.0                                   | O0 / I     | St/B | Bit 0 of Port 1, General Purpose Input/Output  |  |

|       | U1C0_MCLK<br>OUT                       | O1         | St/B | USIC1 Channel 0 Master Clock Output            |  |

|       | U1C0_SELO<br>4                         | O2         | St/B | USIC1 Channel 0 Select/Control 4 Output        |  |

|       | A8                                     | ОН         | St/B | External Bus Interface Address Line 8          |  |

|       | ESR1_3                                 | I          | St/B | ESR1 Trigger Input 3                           |  |

|       | CCU62_CTR<br>APB                       | I          | St/B | CCU62 Emergency Trap Input                     |  |

|       | T6INB                                  | I          | St/B | GPT12E Timer T6 Count/Gate Input               |  |

## XE164FM, XE164GM, XE164HM, XE164KM XE166 Family / Base Line

### **General Device Information**

| Pin | Symbol           | Ctrl.      | Туре | Function                                                                                                                                                           |

|-----|------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81  | P1.1             | O0 / I     |      | Bit 1 of Port 1, General Purpose Input/Output                                                                                                                      |

|     | CCU62_COU<br>T62 | O1         | St/B | CCU62 Channel 2 Output                                                                                                                                             |

|     | U1C0_SELO<br>5   | 02         | St/B | USIC1 Channel 0 Select/Control 5 Output                                                                                                                            |

|     | U2C1_DOUT        | O3         | St/B | USIC2 Channel 1 Shift Data Output                                                                                                                                  |

|     | A9               | ОН         | St/B | External Bus Interface Address Line 9                                                                                                                              |

|     | ESR2_3           | I          | St/B | ESR2 Trigger Input 3                                                                                                                                               |

|     | U2C1_DX0C        | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                   |

| 82  | P10.10           | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                    |

|     | U0C0_SELO<br>0   | 01         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                            |

| -   | CCU60_COU<br>T63 | 02         | St/B | CCU60 Channel 3 Output                                                                                                                                             |

|     | AD10             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                                        |

|     | U0C0_DX2C        | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                |

|     | U0C1_DX1A        | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                  |

|     | TDI_B            | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.           |

| 83  | P10.11           | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                    |

|     | U1C0_SCLK<br>OUT | 01         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                 |

|     | BRKOUT           | O2         | St/B | OCDS Break Signal Output                                                                                                                                           |

|     | AD11             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                                        |

|     | U1C0_DX1D        | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                  |

|     | RxDC2B           | I          | St/B | CAN Node 2 Receive Data Input                                                                                                                                      |

|     | TMS_B            | IH         | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |

| Table 5         Pin Definitions and Functions (cont'd) |                   |            |      |                                                                                                                                                                               |  |

|--------------------------------------------------------|-------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                    | Symbol            | Ctrl.      | Туре | Function                                                                                                                                                                      |  |

| 84                                                     | P1.2              | O0 / I     | St/B | Bit 2 of Port 1, General Purpose Input/Output                                                                                                                                 |  |

|                                                        | CCU62_CC6<br>2    | O1         | St/B | CCU62 Channel 2 Output                                                                                                                                                        |  |

|                                                        | U1C0_SELO<br>6    | O2         | St/B | USIC1 Channel 0 Select/Control 6 Output                                                                                                                                       |  |

|                                                        | U2C1_SCLK<br>OUT  | O3         | St/B | USIC2 Channel 1 Shift Clock Output                                                                                                                                            |  |

|                                                        | A10               | ОН         | St/B | External Bus Interface Address Line 10                                                                                                                                        |  |

|                                                        | ESR1_4            | I          | St/B | ESR1 Trigger Input 4                                                                                                                                                          |  |

|                                                        | CCU61_T12<br>HRB  | I          | St/B | External Run Control Input for T12 of CCU61                                                                                                                                   |  |

|                                                        | CCU62_CC6<br>2INA | I          | St/B | CCU62 Channel 2 Input                                                                                                                                                         |  |

|                                                        | U2C1_DX0D         | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                              |  |

|                                                        | U2C1_DX1C         | I          | St/B | USIC2 Channel 1 Shift Clock Input                                                                                                                                             |  |

| 85                                                     | P10.12            | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                               |  |

|                                                        | U1C0_DOUT         | 01         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |

|                                                        | TxDC2             | 02         | St/B | CAN Node 2 Transmit Data Output                                                                                                                                               |  |

|                                                        | TDO_B             | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |

|                                                        | AD12              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 12                                                                                                                                   |  |

|                                                        | U1C0_DX0C         | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |

|                                                        | U1C0_DX1E         | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |

## 3.1 Memory Subsystem and Organization

The memory space of the XE164xM is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

|                                      |                      | P                    |                         |                     |

|--------------------------------------|----------------------|----------------------|-------------------------|---------------------|

| Address Area                         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes               |

| IMB register space                   | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes               | -                   |

| Reserved (Access trap)               | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | <1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM                  | E8'8000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors EPSRAM      |

| Emulated PSRAM                       | E8'0000 <sub>H</sub> | E8'7FFF <sub>H</sub> | 32 Kbytes               | With Flash timing   |

| Reserved for PSRAM                   | E0'8000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors PSRAM       |

| Program SRAM                         | E0'0000 <sub>H</sub> | E0'7FFF <sub>H</sub> | 32 Kbytes               | Maximum speed       |

| Reserved for Flash                   | CD'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | <1.25 Mbytes            | -                   |

| Program Flash 3                      | CC'0000 <sub>H</sub> | CC'FFFF <sub>H</sub> | 64 Kbytes               | -                   |

| Program Flash 2                      | C8'0000 <sub>H</sub> | CB'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 1                      | C4'0000 <sub>H</sub> | C7'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 0                      | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes              | 3)                  |

| External memory area                 | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                | -                   |

| Available Ext. IO area <sup>4)</sup> | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus USIC/CAN      |

| Reserved                             | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes               | -                   |

| USIC alternate regs.                 | 20'B000 <sub>H</sub> | 20'BFFF <sub>H</sub> | 4 Kbytes                | Accessed via EBC    |

| MultiCAN alternate regs.             | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes               | Accessed via EBC    |

| Reserved                             | 20'6000 <sub>H</sub> | 20'7FFF <sub>H</sub> | 8 Kbytes                | -                   |

| USIC registers                       | 20'4000 <sub>H</sub> | 20'5FFF <sub>H</sub> | 8 Kbytes                | Accessed via EBC    |

| MultiCAN registers                   | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes               | Accessed via EBC    |

| External memory area                 | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0     |

| SFR area                             | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbyte               | -                   |

| Dual-Port RAM                        | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                | -                   |

| Reserved for DPRAM                   | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbyte                 | -                   |

| ESFR area                            | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbyte               | -                   |

| XSFR area                            | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                | -                   |

### Table 7 XE164xM Memory Map <sup>1)</sup>

## 3.9 Capture/Compare Units CCU6x

The XE164xM types feature the CCU60, CCU61, CCU62 unit(s).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

### **Additional Features**

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD<sup>1</sup>). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XE164xM to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

<sup>1)</sup> Exception: T5EUD is not connected to a pin.

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

### **Functional Description**

| Table 10         Instruction Set Summary (cont'd) |                                     |       |  |  |  |

|---------------------------------------------------|-------------------------------------|-------|--|--|--|

| Mnemonic                                          | Description                         | Bytes |  |  |  |

| NOP                                               | Null operation                      | 2     |  |  |  |

| CoMUL/CoMAC                                       | Multiply (and accumulate)           | 4     |  |  |  |

| CoADD/CoSUB                                       | Add/Subtract                        | 4     |  |  |  |

| Co(A)SHR                                          | (Arithmetic) Shift right            | 4     |  |  |  |

| CoSHL                                             | Shift left                          | 4     |  |  |  |

| CoLOAD/STORE                                      | Load accumulator/Store MAC register | 4     |  |  |  |

| CoCMP                                             | Compare                             |       |  |  |  |

| CoMAX/MIN                                         | Maximum/Minimum                     | 4     |  |  |  |

| CoABS/CoRND                                       | Absolute value/Round accumulator    | 4     |  |  |  |

| CoMOV                                             | Data move                           | 4     |  |  |  |

| CoNEG/NOP                                         | Negate accumulator/Null operation   | 4     |  |  |  |

1) The Enter Power Down Mode instruction is not used in the XE164xM, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

# 4 Electrical Parameters

The operating range for the XE164xM is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

## 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

## 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                                                       | Symbol Values              |      |      | 5                         | Unit | Note /                             |

|-----------------------------------------------------------------|----------------------------|------|------|---------------------------|------|------------------------------------|

|                                                                 |                            | Min. | Тур. | Max.                      |      | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR         | -30  | -    | -                         | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR         | -    | -    | 30                        | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$       | -10  | -    | 10                        | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR    | -    | -    | 100                       | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\rm J}{\rm SR}$        | -40  | -    | 150                       | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$        | -65  | -    | 150                       | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{ m DDPA}, V_{ m DDPB}$ | -0.5 | -    | 6.0                       | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}$ SR            | -0.5 | -    | V <sub>DDP</sub><br>+ 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

### Table 11 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Sample time and conversion time of the XE164xM's A/D converters are programmable. The timing above can be calculated using **Table 18**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{\text{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |

|-----------------------|-------------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                                | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                            | 01 <sub>H</sub>     | $t_{\sf ADCI} 	imes {f 3}$                  |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                            | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                        | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                           | FE <sub>H</sub>     | $t_{\rm ADCI} 	imes 256$                    |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                           | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                    |

Table 18

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

### **Converter Timing Example A:**

| Assumptions:          | $f_{\rm SYS}$    | = 80 MHz (i.e. $t_{SYS}$ = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>             |

|-----------------------|------------------|-------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$   | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                              |

| Sample time           | t <sub>S</sub>   | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                          |

| Conversion 10-        | bit:             |                                                                                                 |

|                       | t <sub>C10</sub> | = $13 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $13 \times 50$ ns + $2 \times 12.5$ ns = 0.675 µs |

| <b>Conversion 8-b</b> | it:              |                                                                                                 |

|                       | t <sub>C8</sub>  | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 50$ ns + $2 \times 12.5$ ns = 0.575 µs |

#### **Converter Timing Example B:**

| Assumptions:          | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub>                   |

|-----------------------|-------------------------|-----------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$                                |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                                              |

| Conversion 10-        | bit:                    |                                                                                                     |

|                       | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $16 \times 75$ ns + $2 \times 25$ ns = $1.25 \ \mu s$ |

| <b>Conversion 8-b</b> | it:                     |                                                                                                     |

|                       | t <sub>C8</sub>         | = $14 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $14 \times 75$ ns + $2 \times 25$ ns = 1.10 µs        |

|                       |                         |                                                                                                     |

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and Figure 20).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$D_{\text{Tmax}}$  [ns] = ±(220 / (K2 ×  $f_{\text{SYS}}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$D_{T}$  [ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max}$  =  $\pm(220$  / (4  $\times$  33) + 4.3) = 5.97 ns (Not applicable directly in this case!)

$D_3 = 5.97 \times [(1 - 0.058 \times 4) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 4]$

= 5.97 × [0.768 × 2 / 26.39 + 0.232]

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max} = \pm (220 / (2 \times 33) + 4.3) = 7.63$  ns (Not applicable directly in this case!)

$\begin{array}{l} \mathsf{D}_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) \ / \ (0.83 \times 33 - 1) + 0.058 \times 2] \\ = 7.63 \times [0.884 \times 2 \ / \ 26.39 + 0.116] \end{array}$

## 4.6.4 Pad Properties

The output pad drivers of the XE164xM can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . The following table lists the pad parameters.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

**Electrical Parameters**

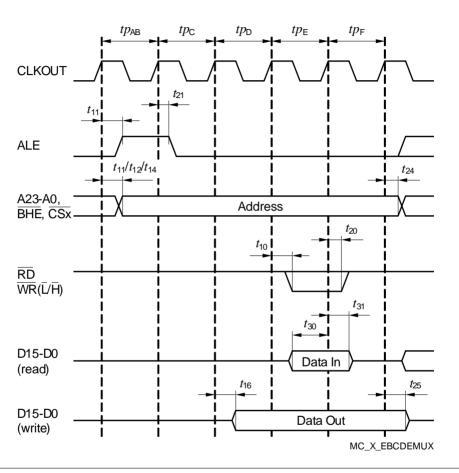

## 4.6.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

### **Electrical Parameters**

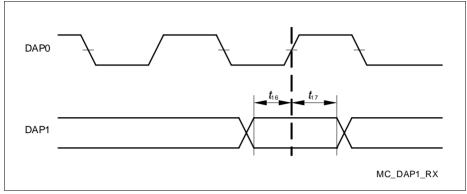

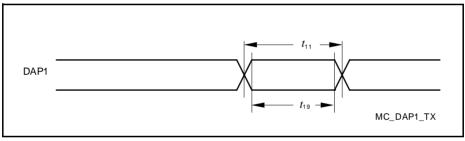

Figure 28 DAP Timing Host to Device

Figure 29 DAP Timing Device to Host

Note: The transmission timing is determined by the receiving debugger by evaluating the sync-request synchronization pattern telegram.

### Package and Reliability

## Package Outlines

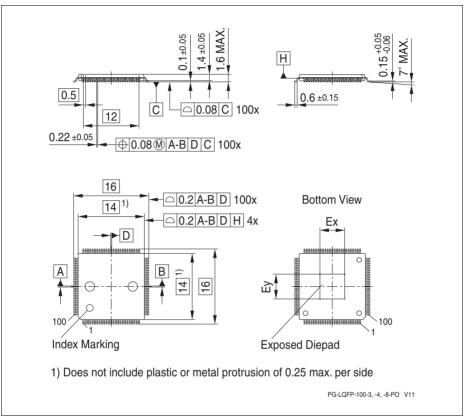

Figure 32 PG-LQFP-100-8 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

### Package and Reliability

## 5.2 Thermal Considerations

When operating the XE164xM in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 125 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} \cdot V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- · Reduce the number of output pins

- Reduce the load on active output drivers