Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-UQFN (4x4)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga702-i-mv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>D</b> '      | F                           | in Number/G         | rid Locator    |                    |     |                 |                                                                               |

|-----------------|-----------------------------|---------------------|----------------|--------------------|-----|-----------------|-------------------------------------------------------------------------------|

| Pin<br>Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                                   |

| IOCB0           | 4                           | 1                   | 21             | 23                 | I   | ST              | PORTB Interrupt-on-Change                                                     |

| IOCB1           | 5                           | 2                   | 22             | 24                 | Ι   | ST              |                                                                               |

| IOCB2           | 6                           | 3                   | 23             | 25                 | Ι   | ST              |                                                                               |

| IOCB3           | 7                           | 4                   | 24             | 26                 | Ι   | ST              |                                                                               |

| IOCB4           | 11                          | 8                   | 33             | 36                 | Ι   | ST              |                                                                               |

| IOCB5           | 14                          | 11                  | 41             | 45                 | Ι   | ST              |                                                                               |

| IOCB6           | 15                          | 12                  | 42             | 46                 | Ι   | ST              |                                                                               |

| IOCB7           | 16                          | 13                  | 43             | 47                 | Ι   | ST              |                                                                               |

| IOCB8           | 17                          | 14                  | 44             | 48                 | Ι   | ST              |                                                                               |

| IOCB9           | 18                          | 15                  | 1              | 1                  | Ι   | ST              |                                                                               |

| IOCB10          | 21                          | 18                  | 8              | 9                  | Ι   | ST              |                                                                               |

| IOCB11          | 22                          | 19                  | 9              | 10                 | I   | ST              |                                                                               |

| IOCB12          | 23                          | 20                  | 10             | 11                 | I   | ST              |                                                                               |

| IOCB13          | 24                          | 21                  | 11             | 12                 | I   | ST              |                                                                               |

| IOCB14          | 25                          | 22                  | 14             | 15                 | Ι   | ST              |                                                                               |

| IOCB15          | 26                          | 23                  | 15             | 16                 | I   | ST              |                                                                               |

| IOCC1           | _                           | _                   | 26             | 28                 | I   | ST              | PORTC Interrupt-on-Change                                                     |

| IOCC2           | _                           | _                   | 27             | 29                 | I   | ST              |                                                                               |

| IOCC3           | _                           | _                   | 36             | 39                 | I   | ST              |                                                                               |

| IOCC4           | _                           | _                   | 37             | 40                 | I   | ST              |                                                                               |

| IOCC5           | _                           | _                   | 38             | 41                 | I   | ST              |                                                                               |

| IOCC6           |                             | _                   | 2              | 2                  | I   | ST              |                                                                               |

| IOCC7           | _                           | _                   | 3              | 3                  | I   | ST              |                                                                               |

| IOCC8           | _                           | _                   | 4              | 4                  | I   | ST              |                                                                               |

| IOCC9           | —                           | _                   | 5              | 5                  | Ι   | ST              |                                                                               |

| MCLR            | 1                           | 26                  | 18             | 19                 | l   | ST              | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OCM1A           | 16                          | 13                  | 43             | 47                 | 0   | DIG             | MCCP1 Outputs                                                                 |

| OCM1B           | 17                          | 14                  | 44             | 48                 | 0   | DIG             |                                                                               |

| OCM1C           | 21                          | 18                  | 8              | 9                  | 0   | DIG             | 1                                                                             |

| OCM1D           | 24                          | 21                  | 11             | 12                 | 0   | DIG             | ]                                                                             |

| OCM1E           | 14                          | 11                  | 41             | 45                 | 0   | DIG             | 1                                                                             |

| OCM1F           | 15                          | 12                  | 42             | 46                 | 0   | DIG             | 1                                                                             |

| OSCI            | 9                           | 6                   | 30             | 33                 | Ι   | ANA/ST          | Main Oscillator Input Connection                                              |

| OSCO            | 10                          | 7                   | 31             | 34                 | 0   | ANA             | Main Oscillator Output Connection                                             |

#### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Legend:** TTL = TTL input buffer ANA = Analog level inp ST = Schmitt Trigger input buffer

ANA = Analog level input/output DIG = Digital input/output  $I^2C = I^2C/SMBus input buffer$

XCVR = Dedicated Transceiver

## 2.4 Voltage Regulator Pin (VCAP)

Note: This section applies only to PIC24FJ devices with an on-chip voltage regulator.

Refer to **Section 29.3** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

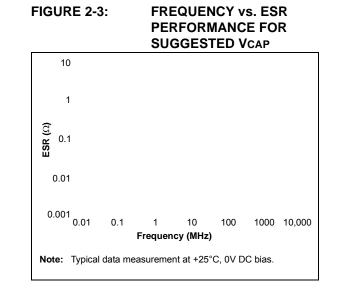

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate the ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 32.0** "**Electrical Characteristics**" for additional information.

## TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS (0805 CASE SIZE)

| Make   | Part #              | Nominal<br>Capacitance | Base Tolerance | Rated Voltage |

|--------|---------------------|------------------------|----------------|---------------|

| TDK    | C2012X5R1E106K085AC | 10 µF                  | ±10%           | 25V           |

| TDK    | C2012X5R1C106K085AC | 10 µF                  | ±10%           | 16V           |

| Kemet  | C0805C106M4PACTU    | 10 µF                  | ±10%           | 16V           |

| Murata | GRM21BR61E106KA3L   | 10 µF                  | ±10%           | 25V           |

| Murata | GRM21BR61C106KE15   | 10 µF                  | ±10%           | 16V           |

## 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. This is done by clearing all bits in the ANSx registers. Refer to **Section 11.2** "**Configuring Analog Port Pins (ANSx)**" for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the A/D module, as follows:

Set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGCx/PGDx pair, at any time. When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ANSx registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### 4.2.5 EXTENDED DATA SPACE (EDS)

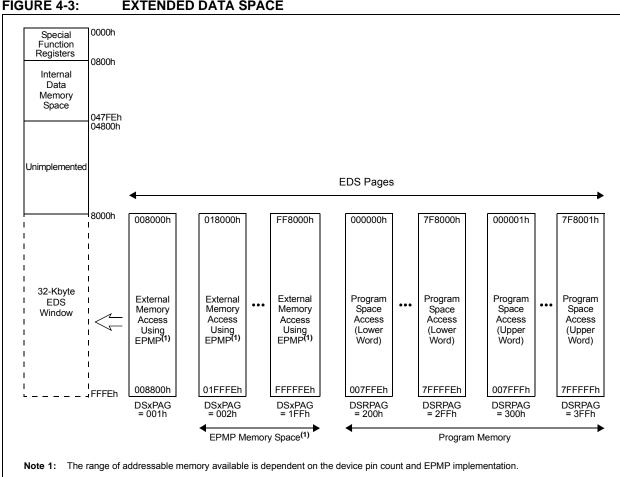

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space and any external memory through EPMP.

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.3.3 "Reading Data from Program Memory Using EDS".

Figure 4-3 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to the size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read Page register (DSRPAG) or the Data Space Write Page register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA).

The data addressing range of the PIC24FJ256GA705 family devices depends on the version of the Enhanced Parallel Master Port implemented on a particular device; this is, in turn, a function of device pin count. Table 4-12 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to the "dsPIC33/PIC24 Family Reference Manual', "Enhanced Parallel Master Port (EPMP)" (DS39730).

| TABLE 4-12: | TOTAL ACCESSIBLE DATA |

|-------------|-----------------------|

|             | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGA70X | 16K             | 1K                                   |

Note: Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

#### FIGURE 4-3: **EXTENDED DATA SPACE**

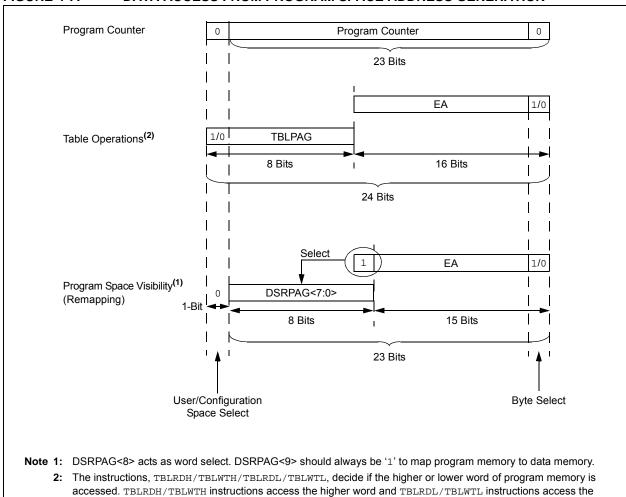

lower word. Table Read operations are permitted in the configuration memory space.

#### FIGURE 4-7: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

© 2016 Microchip Technology Inc.

| Reset Type      | Clock Source | SYSRST Delay           | System Clock<br>Delay | Notes         |

|-----------------|--------------|------------------------|-----------------------|---------------|

| POR             | EC           | TPOR + TSTARTUP + TRST |                       | 1, 2, 3       |

|                 | ECPLL        | TPOR + TSTARTUP + TRST | Тьоск                 | 1, 2, 3, 5    |

|                 | XT, HS, SOSC | TPOR + TSTARTUP + TRST | Тоѕт                  | 1, 2, 3, 4    |

|                 | XTPLL, HSPLL | TPOR + TSTARTUP + TRST | Tost + Tlock          | 1, 2, 3, 4, 5 |

|                 | FRC, OSCFDIV | TPOR + TSTARTUP + TRST | TFRC                  | 1, 2, 3, 6, 7 |

|                 | FRCPLL       | TPOR + TSTARTUP + TRST | TFRC + TLOCK          | 1, 2, 3, 5, 6 |

|                 | LPRC         | TPOR + TSTARTUP + TRST | Tlprc                 | 1, 2, 3, 6    |

| BOR             | EC           | TSTARTUP + TRST        | —                     | 2, 3          |

|                 | ECPLL        | TSTARTUP + TRST        | Тьоск                 | 2, 3, 5       |

|                 | XT, HS, SOSC | TSTARTUP + TRST        | Тоѕт                  | 2, 3, 4       |

|                 | XTPLL, HSPLL | TSTARTUP + TRST        | Tost + Tlock          | 2, 3, 4, 5    |

|                 | FRC, OSCFDIV | TSTARTUP + TRST        | TFRC                  | 2, 3, 6, 7    |

|                 | FRCPLL       | TSTARTUP + TRST        | TFRC + TLOCK          | 2, 3, 5, 6    |

|                 | LPRC         | TSTARTUP + TRST        | Tlprc                 | 2, 3, 6       |

| MCLR            | Any Clock    | TRST                   | _                     | 3             |

| WDT             | Any Clock    | Trst                   |                       | 3             |

| Software        | Any clock    | TRST                   |                       | 3             |

| Illegal Opcode  | Any Clock    | Trst                   |                       | 3             |

| Uninitialized W | Any Clock    | TRST                   |                       | 3             |

| Trap Conflict   | Any Clock    | Trst                   |                       | 3             |

**Note 1:** TPOR = Power-on Reset delay (10  $\mu$ s nominal).

- **2:** TSTARTUP = TVREG.

- **3:** TRST = Internal State Reset Time (2 μs nominal).

- **4:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL Lock Time.

- **6:** TFRC and TLPRC = RC Oscillator Start-up Times.

- 7: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC so the system clock delay is just TFRC, and in such cases, FRC start-up time is valid; it switches to the Primary Oscillator after its respective clock delay.

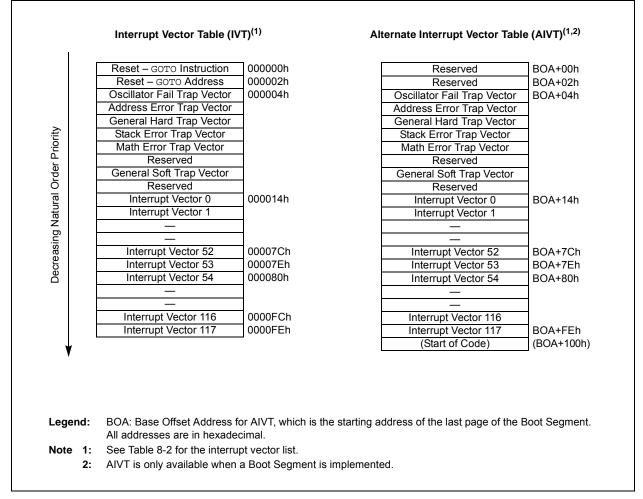

## FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLES

## TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source            |

|---------------|-------------|--------------|------------------------|

| 0             | 000004h     | BOA+04h      | Oscillator Failure     |

| 1             | 000006h     | BOA+06h      | Address Error          |

| 2             | 000008h     | BOA+08h      | General Hardware Error |

| 3             | 00000Ah     | BOA+0Ah      | Stack Error            |

| 4             | 00000Ch     | BOA+0Ch      | Math Error             |

| 5             | 00000Eh     | BOA+0Eh      | Reserved               |

| 6             | 000010h     | BOA+10h      | General Software Error |

| 7             | 000012h     | BOA+12h      | Reserved               |

**Legend:** BOA = Base Offset Address for AIVT segment, which is the starting address of the last page of the Boot Segment.

| REGISTER 8-1: | SR: ALU STATUS REGISTER <sup>(1)</sup> |

|---------------|----------------------------------------|

|---------------|----------------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | —   | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| 011        | = CPU Interrupt Priority Level is 6 (14)<br>= CPU Interrupt Priority Level is 5 (13)<br>= CPU Interrupt Priority Level is 4 (12)<br>= CPU Interrupt Priority Level is 3 (11)                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 010<br>001 | <ul> <li>CPU Interrupt Priority Level is 3 (11)</li> <li>CPU Interrupt Priority Level is 2 (10)</li> <li>CPU Interrupt Priority Level is 1 (9)</li> <li>CPU Interrupt Priority Level is 0 (8)</li> </ul> |

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> Status bits are concatenated with the IPL3 Status bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Power-Saving Features" (DS39698), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ256GA705 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the  ${\tt PWRSAV}$  instruction is shown in Example 10-1.

The MPLAB<sup>®</sup> XC16 C compiler offers "built-in" functions for the power-saving modes as follows:

Idle(); // places part in Idle

Sleep(); // places part in Sleep

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

#### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | SLEEP mode |

|--------|-------------|---|-----|-----|--------|------|------------|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | IDLE mode  |

## 11.5.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 11-32 through Register 11-46). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-7).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| <b>TABLE 11-7:</b> | SELECTABLE OUTPUT SOURCES | (MAPS FUNCTION TO OUTPUT) |

|--------------------|---------------------------|---------------------------|

|                    |                           |                           |

| Output Function Number | Function            | Output Name              |

|------------------------|---------------------|--------------------------|

| 0                      | None (Pin Disabled) | —                        |

| 1                      | C1OUT               | Comparator 1 Output      |

| 2                      | C2OUT               | Comparator 2 Output      |

| 3                      | U1TX                | UART1 Transmit           |

| 4                      | U1RTS               | UART1 Request-to-Send    |

| 5                      | U2TX                | UART2 Transmit           |

| 6                      | U2RTS               | UART2 Request-to-Send    |

| 7                      | SDO1                | SPI1 Data Output         |

| 8                      | SCK1OUT             | SPI1 Clock Output        |

| 9                      | SS1OUT              | SPI1 Slave Select Output |

| 10                     | SDO2                | SPI2 Data Output         |

| 11                     | SCK2OUT             | SPI2 Clock Output        |

| 12                     | SS2OUT              | SPI2 Slave Select Output |

| 13                     | OC1                 | Output Compare 1         |

| 14                     | OC2                 | Output Compare 2         |

| 15                     | OC3                 | Output Compare 3         |

| 16                     | OCM2A               | CCP2A Output Compare     |

| 17                     | OCM2B               | CCP2B Output Compare     |

| 18                     | OCM3A               | CCP3A Output Compare     |

| 19                     | OCM3B               | CCP3B Output Compare     |

| 20                     | OCM4A               | CCP4A Output Compare     |

| 21                     | OCM4B               | CCP4B Output Compare     |

| 22                     | Reserved            | —                        |

| 23                     | SDO3                | SPI3 Data Output         |

| 24                     | SCK3OUT             | SPI3 Clock Output        |

| 25                     | SS3OUT              | SPI3 Slave Select Output |

| 26                     | C3OUT               | Comparator 3 Output      |

| 27                     | PWRGT               | RTCC Power Control       |

| 28                     | REFO                | Reference Clock Output   |

| 29                     | CLC10UT             | CLC1 Output              |

| 30                     | CLC2OUT             | CLC2 Output              |

| 31                     | RTCC                | RTCC Clock Output        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| · ·    |     |        |        |        |        |        |        |

## REGISTER 11-40: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP17R<5:0>: RP17 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP17 (see Table 11-7 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP16R<5:0>: RP16 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP16 (see Table 11-7 for peripheral function numbers). |

### REGISTER 11-41: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 | •   |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP19R<5:0>:** RP19 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP19 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP18R<5:0>:** RP18 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP18 (see Table 11-7 for peripheral function numbers).

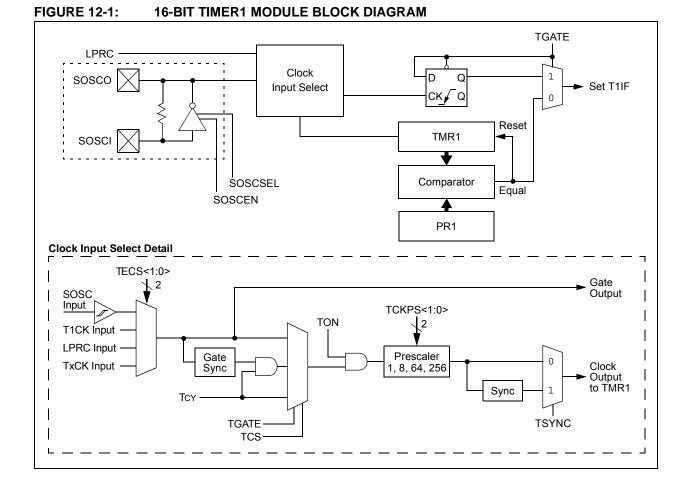

# 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"Timers"* (DS39704), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS, TECS<1:0> and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

© 2016 Microchip Technology Inc.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 11111 = Not used

- 11110 = Not used 11101 = Not used 11100 = CTMU trigger<sup>(1)</sup> 11011 = A/D interrupt<sup>(1)</sup>

- 11010 = CMP3 trigger<sup>(1)</sup>

- 11001 = CMP2 trigger<sup>(1)</sup>

- 11000 = CMP1 trigger<sup>(1)</sup>

- 10111 = Not used

- 10110 = MCCP4 IC/OC interrupt

- 10101 = MCCP3 IC/OC interrupt

- 10100 = MCCP2 IC/OC interrupt

- 10011 = MCCP1 IC/OC interrupt

- 10010 = IC3 interrupt<sup>(2)</sup>

- 10001 = IC2 interrupt<sup>(2)</sup>

- 10000 = IC1 interrupt<sup>(2)</sup>

- 01111 = Not used

- 01110 = Not used

- 01101 = Timer3 match event

- 01100 = Timer2 match event

- 01011 = Timer1 match event

- 01010 = Not used

- 01001 = Not used

- 01000 = Not used

- 00111 = MCCP4 Sync/Trigger out

- 00110 = MCCP3 Sync/Trigger out

- 00101 = MCCP2 Sync/Trigger out

- 00100 = MCCP1 Sync/Trigger out

- 00011 = OC3 Sync/Trigger out

- 00010 = OC2 Sync/Trigger out

- 00001 = OC1 Sync/Trigger out

- 00000 **=** Off

- Note 1: Use these inputs as Trigger sources only and never as Sync sources.

- 2: Never use an Input Capture x module as its own Trigger source by selecting this mode.

NOTES:

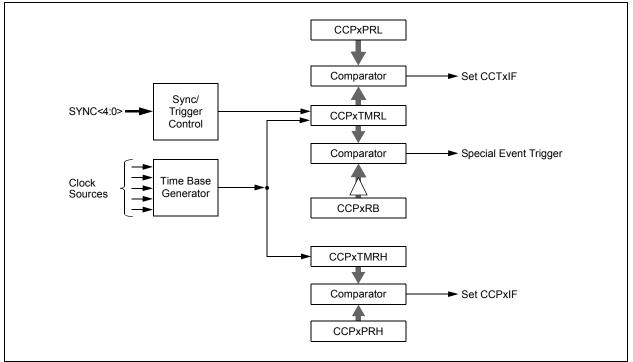

## 16.2 General Purpose Timer

Timer mode is selected when CCSEL = 0 and MOD<3:0> = 0000. The timer can function as a 32-bit timer or a dual 16-bit timer, depending on the setting of the T32 bit (Table 16-1).

| T32<br>(CCPxCON1L<5>) | Operating Mode           |  |  |  |

|-----------------------|--------------------------|--|--|--|

| 0                     | Dual Timer Mode (16-bit) |  |  |  |

| 1                     | Timer Mode (32-bit)      |  |  |  |

TABLE 16-1: TIMER OPERATION MODE

Dual 16-Bit Timer mode provides a simple timer function with two independent 16-bit timer/counters. The primary timer uses the CCPxTMRL and CCPxPRL registers. Only the primary timer can interact with other modules on the device. It generates the MCCPx Sync out signals for use by other MCCPx modules. It can also use the SYNC<4:0> bits signal generated by other modules.

The secondary timer uses the CCPxTMRH and CCPxPRH registers. It is intended to be used only as a periodic interrupt source for scheduling CPU events. It does not generate an output Sync/Trigger signal like the primary time base. In Dual Timer mode, the Timer Period High register, CCPxPRH, generates the MCCPx compare event (CCPxIF) used by many other modules on the device.

The 32-Bit Timer mode uses the CCPxTMRL and CCPxTMRH registers, together, as a single 32-bit timer. When CCPxTMRL overflows, CCPxTMRH increments

FIGURE 16-3: DUAL 16-BIT TIMER MODE

by one. This mode provides a simple timer function when it is important to track long time periods. Note that the T32 bit (CCPxCON1L<5>) should be set before the CCPxTMRL or CCPxPRH registers are written to initialize the 32-bit timer.

#### 16.2.1 SYNC AND TRIGGER OPERATION

In both 16-bit and 32-bit modes, the timer can also function in either Synchronization ("Sync") or Trigger mode operation. Both use the SYNC<4:0> bits (CCPxCON1H<4:0>) to determine the input signal source. The difference is how that signal affects the timer.

In Sync operation, the Timer Reset or clear occurs when the input selected by SYNC<4:0> is asserted. The timer immediately begins to count again from zero unless it is held for some other reason. Sync operation is used whenever the TRIGEN bit (CCPxCON1H<7>) is cleared. The SYNC<4:0> bits can have any value except '11111'.

In Trigger mode operation, the timer is held in Reset until the input selected by SYNC<4:0> is asserted; when it occurs, the timer starts counting. Trigger operation is used whenever the TRIGEN bit is set. In Trigger mode, the timer will continue running after a trigger event as long as the CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG, the TRCLR bit (CCPxSTATL<5>) must be set to clear the trigger event, reset the timer and hold it at zero until another trigger event occurs. On PIC24FJ256GA705 family devices, Trigger mode operation can only be used when the system clock is the time base source (CLKSEL<2:0> = 000).

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | —   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

|        |     |                       |                       |                       |          |          |          |

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

| —      | —   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2   | TXELM1   | TXELM0   |

| bit 7  |     |                       |                       |                       |          |          | bit 0    |

| REGISTER 17-5: SPIXSTATH: SPIX STATUS REGISTER HIGH | REGISTER 17-5: | SPIxSTATH: SPIx STATUS REGISTER HIGH |

|-----------------------------------------------------|----------------|--------------------------------------|

|-----------------------------------------------------|----------------|--------------------------------------|

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

**3:** RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

| Bit Field Value |     | Input Source |             |  |  |

|-----------------|-----|--------------|-------------|--|--|

|                 |     | CLC1         | CLC2        |  |  |

| DS4<2:0>        | 011 | SDI1         | SDI2        |  |  |

|                 | 001 | CLC2 Output  | CLC1 Output |  |  |

| DS3<2:0>        | 100 | U1RX         | U2RX        |  |  |

|                 | 011 | SDO1         | SDO2        |  |  |

|                 | 001 | CLC1 Output  | CLC2 Output |  |  |

| DS2<2:0>        | 011 | U1TX         | U2TX        |  |  |

|                 | 001 | CLC2 Output  | CLC1 Output |  |  |

#### TABLE 23-1: MODULE-SPECIFIC INPUT DATA SOURCES

## REGISTER 23-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| G2D4T  | G2D4N | G2D3T | G2D3N | G2D2T | G2D2N | G2D1T | G2D1N |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N |

| bit 7 |       |       |       |       | •     |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15 | <b>G2D4T:</b> Gate 2 Data Source 4 True Enable bit<br>1 = The Data Source 4 signal is enabled for Gate 2                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 0 = The Data Source 4 signal is disabled for Gate 2                                                                                                   |

| bit 14 | G2D4N: Gate 2 Data Source 4 Negated Enable bit                                                                                                        |

|        | <ul> <li>1 = The Data Source 4 inverted signal is enabled for Gate 2</li> <li>0 = The Data Source 4 inverted signal is disabled for Gate 2</li> </ul> |

| bit 13 | G2D3T: Gate 2 Data Source 3 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 3 signal is enabled for Gate 2</li><li>0 = The Data Source 3 signal is disabled for Gate 2</li></ul>                      |

| bit 12 | G2D3N: Gate 2 Data Source 3 Negated Enable bit                                                                                                        |

|        | <ul> <li>1 = The Data Source 3 inverted signal is enabled for Gate 2</li> <li>0 = The Data Source 3 inverted signal is disabled for Gate 2</li> </ul> |

| bit 11 | G2D2T: Gate 2 Data Source 2 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 2 signal is enabled for Gate 2</li><li>0 = The Data Source 2 signal is disabled for Gate 2</li></ul>                      |

| bit 10 | G2D2N: Gate 2 Data Source 2 Negated Enable bit                                                                                                        |

|        | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 2</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 2</li> </ul> |

| bit 9  | G2D1T: Gate 2 Data Source 1 True Enable bit                                                                                                           |

|        | <ul><li>1 = The Data Source 1 signal is enabled for Gate 2</li><li>0 = The Data Source 1 signal is disabled for Gate 2</li></ul>                      |

|        |                                                                                                                                                       |

# 24.3 Registers

The 12-bit A/D Converter is controlled through a total of 13 registers:

- AD1CON1 through AD1CON5 (Register 24-1 through Register 24-5)

- AD1CHS (Register 24-6)

- ANCFG (Register 24-7)

- AD1CHITL (Register 24-8)

- AD1CSSH and AD1CSSL (Register 24-9 and Register 24-10)

- AD1CTMENH and AD1CTMENL (Register 24-11 and Register 24-12)

- AD1DMBUF (not shown) The 16-bit conversion buffer for Extended Buffer mode

| TABLE 24-1: | INDIRECT ADDRI | ESS GENERATION IN PI | A MODE |  |

|-------------|----------------|----------------------|--------|--|

|             |                |                      |        |  |

| DMABL<2:0> | Buffer Size per<br>Channel (words) | Generated Offset<br>Address (lower 11 bits) | Available<br>Input<br>Channels | Allowable DMADSTn<br>Addresses |

|------------|------------------------------------|---------------------------------------------|--------------------------------|--------------------------------|

| 000        | 1                                  | 000 00cc ccc0                               | 32                             | xxxx xxxx xx00 0000            |

| 001        | 2                                  | 000 0ccc ccn0                               | 32                             | xxxx xxxx x000 0000            |

| 010        | 4                                  | 000 cccc cnn0                               | 32                             | xxxx xxxx 0000 0000            |

| 011        | 8                                  | 00c cccc nnn0                               | 32                             | xxxx xxx0 0000 0000            |

| 100        | 16                                 | 0cc cccn nnn0                               | 32                             | xxxx xx00 0000 0000            |

| 101        | 32                                 | ccc ccnn nnn0                               | 32                             | xxxx x000 0000 0000            |

| 110        | 64                                 | ccc cnnn nnn0                               | 16                             | xxxx x000 0000 0000            |

| 111        | 128                                | ccc nnnn nnn0                               | 8                              | xxxx x000 0000 0000            |

**Legend:** CCC = Channel number (three to five bits), n = Base buffer address (zero to seven bits), x = User-definable range of DMADSTn for base address, 0 = Masked bits of DMADSTn for IA

| R/W-0         | U-0                                                                      | R/W-0                                                  | U-0             | R/W-0            | HS, HC, R-0      | HS, HC, R-0      |                       |  |  |

|---------------|--------------------------------------------------------------------------|--------------------------------------------------------|-----------------|------------------|------------------|------------------|-----------------------|--|--|

| HLVDEN        | —                                                                        | LSIDL                                                  | _               | VDIR             | BGVST            | IRVST            | LVDEVT <sup>(2)</sup> |  |  |

| bit 15        |                                                                          |                                                        |                 |                  |                  |                  | bit 8                 |  |  |

|               |                                                                          |                                                        |                 |                  |                  |                  |                       |  |  |

| U-0           | U-0                                                                      | U-0                                                    | U-0             | R/W-0            | R/W-0            | R/W-0            | R/W-0                 |  |  |

|               |                                                                          | <u> </u>                                               |                 | HLVDL3           | HLVDL2           | HLVDL1           | HLVDL0                |  |  |

| bit 7         |                                                                          |                                                        |                 |                  |                  |                  | bit (                 |  |  |

| Legend:       |                                                                          | HS = Hardware                                          | e Settable bit  | HC = Hardwa      | re Clearable bit |                  |                       |  |  |

| R = Readabl   | e bit                                                                    | W = Writable b                                         |                 |                  | nented bit, read | l as '0'         |                       |  |  |

| -n = Value at | POR                                                                      | '1' = Bit is set                                       |                 | '0' = Bit is cle |                  | x = Bit is unkr  | nown                  |  |  |

|               |                                                                          |                                                        |                 |                  |                  |                  |                       |  |  |

| bit 15        | -                                                                        | h/Low-Voltage                                          | Detect Power E  | Enable bit       |                  |                  |                       |  |  |

|               | 1 = HLVD is<br>0 = HLVD is                                               |                                                        |                 |                  |                  |                  |                       |  |  |

| bit 14        |                                                                          | ted: Read as '0                                        | ,               |                  |                  |                  |                       |  |  |

| bit 13        | -                                                                        | Stop in Idle Mc                                        |                 |                  |                  |                  |                       |  |  |

|               |                                                                          | ues module ope                                         |                 | evice enters Id  | le mode          |                  |                       |  |  |

|               |                                                                          | s module opera                                         |                 |                  |                  |                  |                       |  |  |

| bit 12        | Unimplemen                                                               | ted: Read as '0                                        | ,               |                  |                  |                  |                       |  |  |

| bit 11        | VDIR: Voltage                                                            | e Change Direct                                        | tion Select bit |                  |                  |                  |                       |  |  |

|               |                                                                          | curs when voltag                                       |                 |                  |                  |                  |                       |  |  |

| bit 10        |                                                                          | d Gap Voltage S                                        |                 |                  | -                |                  |                       |  |  |

|               |                                                                          | that the band ga                                       |                 |                  |                  |                  |                       |  |  |

| <b>h</b> # 0  |                                                                          | that the band ga                                       |                 |                  |                  |                  |                       |  |  |

| bit 9         | 1 = Internal r                                                           | al Reference Vo                                        | •               | •                | etect logic gene | rates the interr | upt flag at the       |  |  |

|               | 0 = Internal r                                                           | voltage range<br>eference voltage<br>e specified volta |                 |                  |                  |                  | e the interrup        |  |  |

| bit 8         | •                                                                        | -Voltage Event                                         | • •             |                  |                  | be chabled       |                       |  |  |

|               |                                                                          | it is true during of                                   |                 | ion cycle        |                  |                  |                       |  |  |

|               |                                                                          | it is not true duri                                    |                 |                  |                  |                  |                       |  |  |

| bit 7-4       | Unimplemen                                                               | ted: Read as '0                                        | ,               |                  |                  |                  |                       |  |  |

| bit 3-0       | HLVDL<3:0>                                                               | : High/Low-Volta                                       | age Detection L | _imit bits       |                  |                  |                       |  |  |

|               |                                                                          | nal analog input                                       | is used (input  | comes from th    | e HLVDIN pin)    |                  |                       |  |  |

|               | 1110 = Trip Point 1 <sup>(1)</sup>                                       |                                                        |                 |                  |                  |                  |                       |  |  |

|               | 1101 = Trip Point 2 <sup>(1)</sup><br>1100 = Trip Point 3 <sup>(1)</sup> |                                                        |                 |                  |                  |                  |                       |  |  |

|               | •                                                                        | Sint O                                                 |                 |                  |                  |                  |                       |  |  |

|               | •                                                                        |                                                        |                 |                  |                  |                  |                       |  |  |

|               | •                                                                        | $P_{oint 14}(1)$                                       |                 |                  |                  |                  |                       |  |  |

|               | 0100 = Trip F<br>00xx = Unus                                             |                                                        |                 |                  |                  |                  |                       |  |  |

|               |                                                                          |                                                        |                 |                  |                  |                  |                       |  |  |

### REGISTER 28-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

2: The LVDIF flag cannot be cleared by software unless LVDEVT = 0. The voltage must be monitored so that the HLVD condition (as set by VDIR and HLVDL<3:0>) is not asserted.

x = Bit is unknown

| U-1          | U-1    | U-1          | U-1        | U-1                                | U-1         | U-1    | U-1    |

|--------------|--------|--------------|------------|------------------------------------|-------------|--------|--------|

| —            | —      | —            | _          | —                                  | —           | —      | —      |

| bit 23       |        |              |            |                                    |             |        | bit 16 |

|              |        |              |            |                                    |             |        |        |

| U-1          | U-1    | U-1          | R/PO-1     | R/PO-1                             | R/PO-1      | R/PO-1 | R/PO-1 |

| —            | —      | —            |            |                                    | BSLIM<12:8> |        |        |

| bit 15       |        |              |            |                                    |             |        | bit 8  |

|              |        |              |            |                                    |             |        |        |

| R/PO-1       | R/PO-1 | R/PO-1       | R/PO-1     | R/PO-1                             | R/PO-1      | R/PO-1 | R/PO-1 |

|              |        |              | BSLIN      | <b>/</b> <7:0>                     |             |        |        |

| bit 7        |        |              |            |                                    |             |        | bit 0  |

|              |        |              |            |                                    |             |        |        |

| Legend:      |        | PO = Prograr | n Once bit |                                    |             |        |        |

| R = Readable | e bit  | W = Writable | bit        | U = Unimplemented bit, read as '0' |             |        |        |

#### **REGISTER 29-2: FBSLIM CONFIGURATION REGISTER**

'1' = Bit is set

bit 23-13 Unimplemented: Read as '1'

-n = Value at POR

bit 12-0 **BSLIM<12:0>:** Active Boot Segment Code Flash Page Address Limit (Inverted) bits This bit field contains the last active Boot Segment Page + 1 (i.e., first page address of GS). The value is stored as an inverted page address, such that programming additional '0's can only increase the size of BS. If BSLIM<12:0> is set to all '1's (unprogrammed default), the active Boot Segment size is zero.

'0' = Bit is cleared