Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

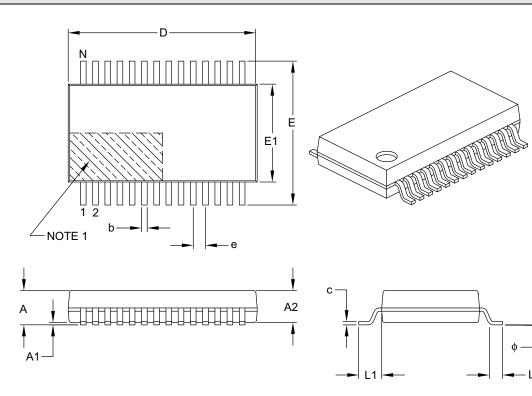

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga702-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Features                                                               | PIC24FJ64GA702 | PIC24FJ128GA702                                                                                                  | PIC24FJ256GA702 |

|------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------|-----------------|

| Operating Frequency                                                    |                | DC – 32 MHz                                                                                                      |                 |

| Program Memory (bytes)                                                 | 64K            | 128K                                                                                                             | 256K            |

| Program Memory<br>(instruction words, 24 bits)                         | 22,528         | 45,056                                                                                                           | 88,064          |

| Data Memory (bytes)                                                    |                | 16K                                                                                                              |                 |

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                | 124                                                                                                              |                 |

| I/O Ports                                                              |                | Ports A, B                                                                                                       |                 |

| Total I/O Pins                                                         |                | 22                                                                                                               |                 |

| Remappable Pins                                                        |                | 18 (18 I/Os, 0 input only)                                                                                       |                 |

| DMA                                                                    |                | 1 6-channel                                                                                                      |                 |

| 16-Bit Timers                                                          |                | 3(1)                                                                                                             |                 |

| Real-Time Clock and Calendar<br>(RTCC)                                 |                | Yes                                                                                                              |                 |

| Cyclic Redundancy Check (CRC)                                          |                | Yes                                                                                                              |                 |

| Input Capture Channels                                                 |                | 3 <sup>(1)</sup>                                                                                                 |                 |

| Output Compare/PWM Channels                                            |                | 3(1)                                                                                                             |                 |

| Input Change Notification Interrupt                                    |                | 21 (remappable pins)                                                                                             |                 |

| Serial Communications:                                                 |                |                                                                                                                  |                 |

| UART                                                                   |                | 2(1)                                                                                                             |                 |

| SPI (3-wire/4-wire)                                                    |                | 3(1)                                                                                                             |                 |

| I <sup>2</sup> C                                                       |                | 2                                                                                                                |                 |

| Configurable Logic Cell (CLC)                                          |                | 2(1)                                                                                                             |                 |

| Parallel Communications<br>(EPMP/PSP)                                  |                | No                                                                                                               |                 |

| Capture/Compare/PWM/Timer                                              |                | 4 Multiple CCPs                                                                                                  |                 |

| Modules                                                                |                | 1 (6-output), 3 (2-output)                                                                                       |                 |

| JTAG Boundary Scan                                                     |                | Yes                                                                                                              |                 |

| 10/12-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) |                | 10                                                                                                               |                 |

| Analog Comparators                                                     |                | 3                                                                                                                |                 |

| CTMU Interface                                                         |                | Yes                                                                                                              |                 |

| Universal Serial Bus Controller                                        |                | No                                                                                                               |                 |

| Resets (and Delays)                                                    | MCLR, W        | OR, VDD POR, BOR, RESET IN<br>/DT, Illegal Opcode, REPEAT I<br>re Traps, Configuration Word I<br>(OST, PLL Lock) | nstruction,     |

| Instruction Set                                                        | 76 Base Instru | uctions, Multiple Addressing M                                                                                   | lode Variations |

| Packages                                                               | 28-Pin (       | QFN, UQFN, SOIC, SSOP an                                                                                         | d SPDIP         |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJXXXGA702: 28-PIN DEVICES

**Note 1:** Some peripherals are accessible through remappable pins.

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/ +80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

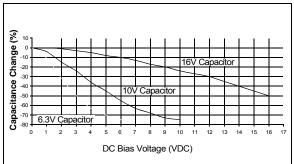

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at a minimum of 16V for the 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGCx and PGDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGCx and PGDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" pins (i.e., PGCx/PGDx) programmed into the device match the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "PIC24F Flash Program Memory" (DS30009715), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space during code execution.

#### 4.1 Program Memory Space

The program address memory space of the PIC24FJ256GA705 family devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and customer OTP sections of the configuration memory space.

The memory map for the PIC24FJ256GA705 family of devices is shown in Figure 4-1.

| File Name     | Address | All Resets | File Name                        | Address | All Resets |  |  |

|---------------|---------|------------|----------------------------------|---------|------------|--|--|

| CPU CORE      |         |            | INTERRUPT CONTROLLER (CONTINUED) |         |            |  |  |

| WREG0         | 0000    | 0000       | IEC1                             | 009A    | 0000       |  |  |

| WREG1         | 0002    | 0000       | IEC2                             | 009C    | 0000       |  |  |

| WREG2         | 0004    | 0000       | IEC3                             | 009E    | 0000       |  |  |

| WREG3         | 0006    | 0000       | IEC4                             | 00A0    | 0000       |  |  |

| WREG4         | 0008    | 0000       | IEC5                             | 00A2    | 0000       |  |  |

| WREG5         | 000A    | 0000       | IEC6                             | 00A4    | 0000       |  |  |

| WREG6         | 000C    | 0000       | IEC7                             | 00A6    | 0000       |  |  |

| WREG7         | 000E    | 0000       | IPC0                             | 00A8    | 4444       |  |  |

| WREG8         | 0010    | 0000       | IPC1                             | 00AA    | 4444       |  |  |

| WREG9         | 0012    | 0000       | IPC2                             | 00AC    | 4444       |  |  |

| WREG10        | 0014    | 0000       | IPC3                             | 00AE    | 4444       |  |  |

| WREG11        | 0016    | 0000       | IPC4                             | 00B0    | 4444       |  |  |

| WREG12        | 0018    | 0000       | IPC5                             | 00B2    | 4404       |  |  |

| WREG13        | 001A    | 0000       | IPC6                             | 00B4    | 4444       |  |  |

| WREG14        | 001C    | 0000       | IPC7                             | 00B6    | 4444       |  |  |

| WREG15        | 001E    | 0800       | IPC8                             | 00B8    | 0044       |  |  |

| SPLIM         | 0020    | xxxx       | IPC9                             | 00BA    | 4444       |  |  |

| PCL           | 002E    | 0000       | IPC10                            | 00BC    | 4444       |  |  |

| PCH           | 0030    | 0000       | IPC11                            | 00BE    | 4444       |  |  |

| DSRPAG        | 0032    | 0000       | IPC12                            | 00C0    | 4444       |  |  |

| DSWPAG        | 0034    | 0000       | IPC13                            | 00C2    | 0440       |  |  |

| RCOUNT        | 0036    | xxxx       | IPC14                            | 00C4    | 4400       |  |  |

| SR            | 0042    | 0000       | IPC15                            | 00C6    | 4444       |  |  |

| CORCON        | 0044    | 0004       | IPC16                            | 00C8    | 4444       |  |  |

| DISICNT       | 0052    | xxxx       | IPC17                            | 00CA    | 4444       |  |  |

| TBLPAG        | 0054    | 0000       | IPC18                            | 00CC    | 0044       |  |  |

| INTERRUPT CON | TROLLER | •          | IPC19                            | 00CE    | 0040       |  |  |

| INTCON1       | 0080    | 0000       | IPC20                            | 00D0    | 4440       |  |  |

| INTCON2       | 0082    | 8000       | IPC21                            | 00D2    | 4444       |  |  |

| INTCON4       | 0086    | 0000       | IPC22                            | 00D4    | 4444       |  |  |

| IFS0          | 0088    | 0000       | IPC23                            | 00D6    | 4400       |  |  |

| IFS1          | 008A    | 0000       | IPC24                            | 00D8    | 4444       |  |  |

| IFS2          | 008C    | 0000       | IPC25                            | 00DA    | 0440       |  |  |

| IFS3          | 008E    | 0000       | IPC26                            | 00DC    | 0400       |  |  |

| IFS4          | 0090    | 0000       | IPC27                            | 00DE    | 4440       |  |  |

| IFS5          | 0092    | 0000       | IPC28                            | 00E0    | 4444       |  |  |

| IFS6          | 0094    | 0000       | IPC29                            | 00E2    | 0044       |  |  |

| IFS7          | 0096    | 0000       | INTTREG                          | 00E4    | 0000       |  |  |

| IEC0          | 0098    | 0000       |                                  |         |            |  |  |

TABLE 4-4: SFR MAP: 0000h BLOCK

Legend: x = undefined. Reset values are shown in hexadecimal.

## REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE REGISTER 3

| U-0                               | U-0                                                                                                | U-0                                         | U-0           | U-0               | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

| _                                 |                                                                                                    |                                             | _             | _                 | CMPMD           | RTCCMD          | PMPMD |  |  |  |  |

| bit 15                            |                                                                                                    |                                             |               |                   |                 |                 | bit 8 |  |  |  |  |

|                                   |                                                                                                    |                                             |               |                   |                 |                 |       |  |  |  |  |

| R/W-0                             | U-0                                                                                                | U-0                                         | U-0           | U-0               | U-0             | R/W-0           | U-0   |  |  |  |  |

| CRCMD                             | _                                                                                                  | —                                           |               | —                 | —               | I2C2MD          |       |  |  |  |  |

| bit 7                             |                                                                                                    |                                             |               |                   |                 |                 | bit C |  |  |  |  |

|                                   |                                                                                                    |                                             |               |                   |                 |                 |       |  |  |  |  |

| Legend:                           |                                                                                                    |                                             |               |                   |                 |                 |       |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                    |                                             |               | •                 | nented bit, rea |                 |       |  |  |  |  |

| -n = Value a                      | at POR                                                                                             | '1' = Bit is set                            |               | '0' = Bit is clea | ared            | x = Bit is unkn | own   |  |  |  |  |

|                                   |                                                                                                    |                                             | ,             |                   |                 |                 |       |  |  |  |  |

| oit 15-11                         | •                                                                                                  | nted: Read as '0                            |               |                   |                 |                 |       |  |  |  |  |

| bit 10                            |                                                                                                    | CMPMD: Triple Comparator Module Disable bit |               |                   |                 |                 |       |  |  |  |  |

|                                   |                                                                                                    | 1 = Module is disabled                      |               |                   |                 |                 |       |  |  |  |  |

|                                   | •                                                                                                  | power and clock                             |               | enabled           |                 |                 |       |  |  |  |  |

| bit 9                             |                                                                                                    | TCC Module Dis                              | able bit      |                   |                 |                 |       |  |  |  |  |

|                                   | <ol> <li>1 = Module is disabled</li> <li>0 = Module power and clock sources are enabled</li> </ol> |                                             |               |                   |                 |                 |       |  |  |  |  |

| bit 8                             | •                                                                                                  | nanced Parallel                             |               |                   |                 |                 |       |  |  |  |  |

|                                   | 1 = Module i                                                                                       |                                             |               | isable bit        |                 |                 |       |  |  |  |  |

|                                   |                                                                                                    | ower and clock                              | sources are   | enabled           |                 |                 |       |  |  |  |  |

| oit 7                             | -                                                                                                  | C Module Disab                              |               |                   |                 |                 |       |  |  |  |  |

|                                   | 1 = Module i                                                                                       | s disabled                                  |               |                   |                 |                 |       |  |  |  |  |

|                                   | 0 = Module                                                                                         | oower and clock                             | sources are   | enabled           |                 |                 |       |  |  |  |  |

| oit 6-2                           | Unimplemer                                                                                         | nted: Read as 'o                            | 3             |                   |                 |                 |       |  |  |  |  |

| oit 1                             | 12C2MD: 12C                                                                                        | 2 Module Disab                              | le bit        |                   |                 |                 |       |  |  |  |  |

|                                   | 1 = Module i                                                                                       | s disabled                                  |               |                   |                 |                 |       |  |  |  |  |

|                                   | 0 = Module                                                                                         | power and clock                             | sources are e | enabled           |                 |                 |       |  |  |  |  |

| bit 0                             | Unimplemer                                                                                         | nted: Read as 'o                            | ,             |                   |                 |                 |       |  |  |  |  |

| U-0                                | U-0           | R/W-0           | R/W-0          | R/W-0                              | R/W-0            | R/W-0           | R/W-0          |  |

|------------------------------------|---------------|-----------------|----------------|------------------------------------|------------------|-----------------|----------------|--|

| _                                  | —             | RP1R5           | RP1R4          | RP1R3                              | RP1R2            | RP1R1           | RP1R0          |  |

| bit 15                             | ·             | -               |                | -                                  |                  |                 | bit 8          |  |

|                                    |               |                 |                |                                    |                  |                 |                |  |

| U-0                                | U-0           | R/W-0           | R/W-0          | R/W-0                              | R/W-0            | R/W-0           | R/W-0          |  |

| —                                  | —             | RP0R5           | RP0R4          | RP0R3                              | RP0R2            | RP0R1           | RP0R0          |  |

| bit 7                              |               |                 |                |                                    |                  |                 | bit 0          |  |

|                                    |               |                 |                |                                    |                  |                 |                |  |

| Legend:                            |               |                 |                |                                    |                  |                 |                |  |

| R = Readable bit W = Writable bit  |               |                 | bit            | U = Unimplemented bit, read as '0' |                  |                 |                |  |

| -n = Value at POR '1' = Bit is set |               |                 |                | '0' = Bit is cleared x = Bit is    |                  |                 | unknown        |  |

|                                    |               |                 |                |                                    |                  |                 |                |  |

| bit 15-14                          | Unimplemen    | ted: Read as 'd | )'             |                                    |                  |                 |                |  |

| bit 13-8                           | RP1R<5:0>:    | RP1 Output Pir  | n Mapping bits |                                    |                  |                 |                |  |

|                                    | Peripheral Ou | itput Number n  | is assigned to | pin, RP1 (see                      | Table 11-7 for p | peripheral func | tion numbers). |  |

|                                    |               |                 |                |                                    |                  |                 |                |  |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **RP0R<5:0>:** RP0 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP0 (see Table 11-7 for peripheral function numbers).

#### REGISTER 11-33: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| <b>Legend:</b><br>R = Readable bit W = Writable bit |     |       | U = Unimplen | nented bit, read | l as '0' |       |       |

|-----------------------------------------------------|-----|-------|--------------|------------------|----------|-------|-------|

| bit 7                                               |     |       |              |                  |          |       | bit 0 |

| _                                                   | _   | RP2R5 | RP2R4        | RP2R3            | RP2R2    | RP2R1 | RP2R0 |

| U-0                                                 | U-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 | R/W-0 |

| bit 15                                              |     |       |              |                  |          |       | bit 8 |

|                                                     | —   | RP3R5 | RP3R4        | RP3R3            | RP3R2    | RP3R1 | RP3R0 |

| U-0                                                 | U-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 | R/W-0 |

bit 15-14 Unimplemented: Read as '0'

-n = Value at POR

bit 13-8 **RP3R<5:0>:** RP3 Output Pin Mapping bits

'1' = Bit is set

Peripheral Output Number n is assigned to pin, RP3 (see Table 11-7 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP2R<5:0>: RP2 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP2 (see Table 11-7 for peripheral function numbers).

'0' = Bit is cleared

x = Bit is unknown

| U-0     | U-0 | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | —      | —      | —      | —      | —      | —      |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

## REGISTER 11-46: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP28R<5:0>:** RP28 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP28 (see Table 11-7 for peripheral function numbers).

| U-0                               | U-0                                                                                                                                                              | U-0                                                                            | U-0              | U-0               | U-0               | U-0             | U-0   |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------|-------------------|-------------------|-----------------|-------|--|--|--|

| —                                 | —                                                                                                                                                                | —                                                                              | —                | —                 | —                 | —               | —     |  |  |  |

| bit 15                            |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 | bit 8 |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 |       |  |  |  |

| U-0                               | U-0                                                                                                                                                              | U-0                                                                            | R-0              | R-0               | R-0               | R-0             | R-0   |  |  |  |

| —                                 | —                                                                                                                                                                | —                                                                              | PRLWIP           | TMRHWIP           | TMRLWIP           | RBWIP           | RAWIP |  |  |  |

| bit 7                             |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 | bit ( |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 |       |  |  |  |

| Legend:                           |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 |       |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                                                  | bit                                                                            | U = Unimplem     | nented bit, read  | l as '0'          |                 |       |  |  |  |

| -n = Value a                      | at POR                                                                                                                                                           | '1' = Bit is set                                                               |                  | '0' = Bit is clea | ared              | x = Bit is unkr | iown  |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 |       |  |  |  |

| bit 15-5                          | Unimplemen                                                                                                                                                       | ted: Read as '                                                                 | כי               |                   |                   |                 |       |  |  |  |

| bit 4                             | PRLWIP: CC                                                                                                                                                       | PxPRL Write in                                                                 | Progress Stat    | us bit            |                   |                 |       |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  | h the buffered    | contents is in p  | rogress         |       |  |  |  |

|                                   | •                                                                                                                                                                |                                                                                | 0                | not in progress   |                   |                 |       |  |  |  |

| bit 3                             |                                                                                                                                                                  | CPxTMRH Wr                                                                     | 0                |                   |                   |                 |       |  |  |  |

|                                   | <ol> <li>An update to the CCPxTMRH register with the buffered contents is in progress</li> <li>An update to the CCPxTMRH register is not in progress.</li> </ol> |                                                                                |                  |                   |                   |                 |       |  |  |  |

| bit 2                             | -                                                                                                                                                                | CPxTMRL Writ                                                                   | -                |                   | 55.               |                 |       |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                | •                | vith the buffered | l contente is in  | progress        |       |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                | 0                | s not in progres  |                   | progress        |       |  |  |  |

| bit 1                             | •                                                                                                                                                                | xRB Write in P                                                                 | •                |                   |                   |                 |       |  |  |  |

|                                   | 1 = An update                                                                                                                                                    | 1 = An update to the CCPxRB register with the buffered contents is in progress |                  |                   |                   |                 |       |  |  |  |

|                                   | 0 = An update                                                                                                                                                    | e to the CCPxR                                                                 | B register is no | ot in progress    |                   | -               |       |  |  |  |

| bit 0                             | RAWIP: CCP                                                                                                                                                       | xRA Write in P                                                                 | rogress Status   | bit               |                   |                 |       |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  | the buffered co   | ontents is in pro | ogress          |       |  |  |  |

|                                   | 0 = An update                                                                                                                                                    | e to the CCPxR                                                                 | A register is no | ot in progress    |                   |                 |       |  |  |  |

|                                   |                                                                                                                                                                  |                                                                                |                  |                   |                   |                 |       |  |  |  |

## REGISTER 16-8: CCPxSTATH: CCPx STATUS REGISTER HIGH

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | —   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

|        |     |                       |                       |                       |          |          |          |

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

| —      | —   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2   | TXELM1   | TXELM0   |

| bit 7  |     |                       |                       |                       |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clear | HSC = Hardware Settable/Clearable bit   |  |  |  |  |

|-------------------|-------------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

**3:** RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

'1' = Bit is set

## REGISTER 17-11: SPIxURDTL: SPIx UNDERRUN DATA REGISTER LOW

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|-----------|-------|-------|-------|

|                                                                      |       |       | URDA  | \TA<15:8> |       |       |       |

| bit 15                                                               |       |       |       |           |       |       | bit 8 |

|                                                                      |       |       |       |           |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | URD   | ATA<7:0>  |       |       |       |

| bit 7                                                                |       |       |       |           |       |       | bit 0 |

|                                                                      |       |       |       |           |       |       |       |

| Legend:                                                              |       |       |       |           |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |           |       |       |       |

|                                                                      |       |       |       |           |       |       |       |

bit 15-0 **URDATA<15:0>:** SPIx Underrun Data bits These bits are only used when URDTEN = 1. This register holds the data to transmit when a Transmit

> Underrun condition occurs. When the MODE<32,16> or WLENGTH<4:0> bits select 16 to 9-bit data, the SPIx only uses URDATA<15:0>. When the MODE<32,16> or WLENGTH<4:0> bits select 8 to 2-bit data, the SPIx only uses URDATA<7:0>.

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 17-12: SPIxURDTH: SPIx UNDERRUN DATA REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0                                  | R/W-0 | R/W-0        | R/W-0          | R/W-0    | R/W-0 |

|------------------------------------|-------|----------------------------------------|-------|--------------|----------------|----------|-------|

|                                    |       |                                        | URD   | ATA<31:24>   |                |          |       |

| bit 15                             |       |                                        |       |              |                |          | bit 8 |

|                                    |       |                                        |       |              |                |          |       |

| R/W-0                              | R/W-0 | R/W-0                                  | R/W-0 | R/W-0        | R/W-0          | R/W-0    | R/W-0 |

|                                    |       |                                        | URD   | ATA<23:16>   |                |          |       |

| bit 7                              |       |                                        |       |              |                |          | bit 0 |

|                                    |       |                                        |       |              |                |          |       |

| Legend:                            |       |                                        |       |              |                |          |       |

| R = Readable                       | e bit | W = Writable bit                       |       | U = Unimplem | ented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |       |              | iown           |          |       |

bit 15-0 URDATA<31:16>: SPIx Underrun Data bits

These bits are only used when URDTEN = 1. This register holds the data to transmit when a Transmit Underrun condition occurs.

When the MODE<32,16> or WLENGTH<4:0> bits select 32 to 25-bit data, the SPIx only uses URDATA<31:16>. When the MODE<32,16> or WLENGTH<4:0> bits select 24 to 17-bit data, the SPIx only uses URDATA<23:16>.

-n = Value at POR

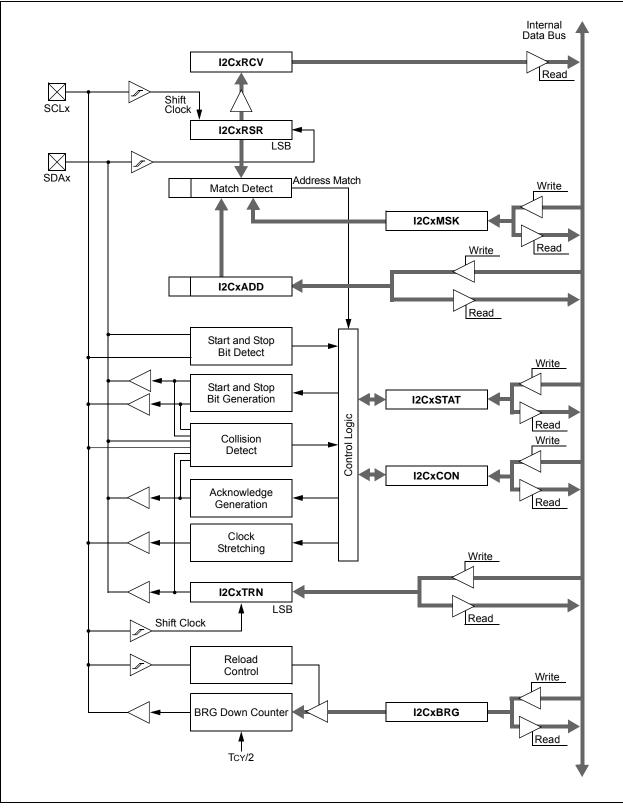

## FIGURE 18-1: I2Cx BLOCK DIAGRAM

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                    | R/W-0                         | R/W-0                                                                 | U-0             | U-0              | U-0              |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|-----------------|------------------|------------------|--|--|--|

| ACKM1            | ACKM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AMWAIT2                                                                                  | AMWAIT1                       | AMWAIT0                                                               |                 | —                | —                |  |  |  |

| bit 15           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                          |                               |                                                                       |                 |                  | bit 8            |  |  |  |

| DAMA             | DAMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DANO                                                                                     | DAVA                          | DAMA                                                                  | DAMA            | DAALO            | DAMA             |  |  |  |

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                    | R/W-0                         | R/W-0                                                                 | R/W-0           | R/W-0            | R/W-0            |  |  |  |

| DWAITB1<br>bit 7 | DWAITB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DWAITM3                                                                                  | DWAITM2                       | DWAITM1                                                               | DWAITM0         | DWAITE1          | DWAITE0<br>bit 0 |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                          |                               |                                                                       |                 |                  | bit e            |  |  |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                          |                               |                                                                       |                 |                  |                  |  |  |  |