#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT               |

| Number of I/O              | 22                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga702t-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

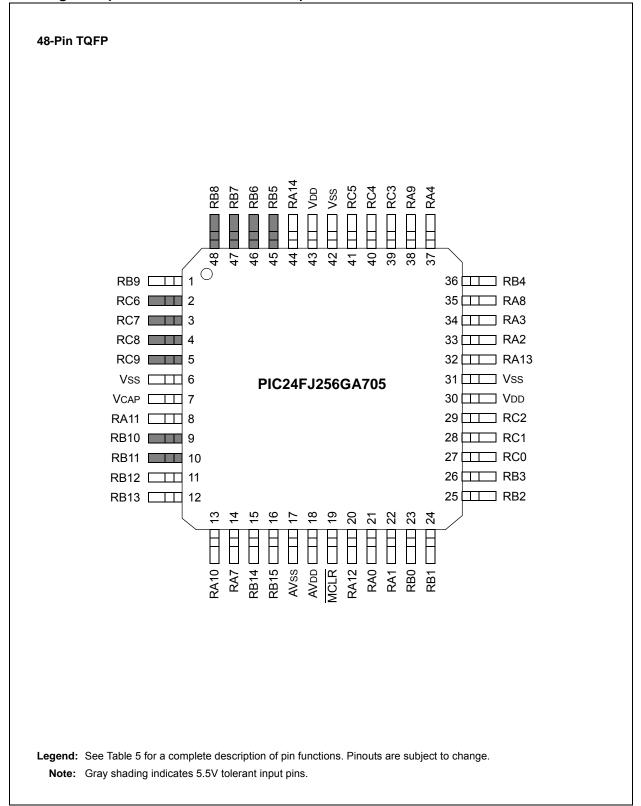

## Pin Diagrams (PIC24FJ256GA705 Devices)

| Pin                  | F                           | in Number/G         | rid Locator    |                    |     | Innut           |                                                                             |

|----------------------|-----------------------------|---------------------|----------------|--------------------|-----|-----------------|-----------------------------------------------------------------------------|

| Function             | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                                 |

| PGC1                 | 5                           | 2                   | 22             | 24                 | I   | ST              | ICSP™ Programming Clock                                                     |

| PGC2                 | 22                          | 19                  | 9              | 10                 | Ι   | ST              |                                                                             |

| PGC3                 | 15                          | 12                  | 42             | 46                 | Ι   | ST              |                                                                             |

| PGD1                 | 4                           | 1                   | 21             | 23                 | I/O | DIG/ST          | ICSP Programming Data                                                       |

| PGD2                 | 21                          | 18                  | 8              | 9                  | I/O | DIG/ST          |                                                                             |

| PGD3                 | 14                          | 11                  | 41             | 45                 | I/O | DIG/ST          |                                                                             |

| PMA0                 | —                           | —                   | 3              | 3                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<0>/<br>Address Latch Low                       |

| PMA1                 | —                           | —                   | 2              | 2                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<1>/<br>Address Latch High                      |

| PMA2                 | _                           | —                   | 12             | 13                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<2>                                             |

| PMA3                 | _                           | _                   | 38             | 41                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<3>                                             |

| PMA4                 | —                           | _                   | 37             | 40                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<4>                                             |

| PMA5                 | _                           | _                   | 4              | 4                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<5>                                             |

| PMA6                 | _                           | _                   | 5              | 5                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<6>                                             |

| PMA7                 | —                           | —                   | 13             | 14                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<7>                                             |

| PMA8                 | —                           | —                   | 32             | 35                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<8>                                             |

| PMA9                 | _                           | —                   | 35             | 38                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<9>                                             |

| PMA14/PMCS/<br>PMCS1 | _                           | —                   | 15             | 16                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<14>/<br>Slave Chip Select/Chip Select 1 Strobe |

#### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

© 2016 Microchip Technology Inc.

| File Name        | Address          | All Resets | File Name                    | Address | All Resets |

|------------------|------------------|------------|------------------------------|---------|------------|

| SPI (CONTINUED   | )                |            | I <sup>2</sup> C (CONTINUED) | 0498    | 0000       |

| SPI1BUFL         | 0400             | 0000       | I2C1BRG                      | 0498    | 0000       |

| SPI1BUFH         | 0402             | 0000       | I2C1CONL                     | 049A    | 1000       |

| SPI1BRGL         | 0404             | xxxx       | I2C1CONH                     | 049C    | 0000       |

| SPI1IMSKL        | 0408             | 0000       | I2C1STAT                     | 049E    | 0000       |

| SPI1IMSKH        | ISKH 040A 0000   |            | I2C1ADD                      | 04A0    | 0000       |

| SPI1URDTL        | 040C             | 0000       | I2C1MSK                      | 04A2    | 0000       |

| SPI1URDTH        | 040E             | 0000       | I2C2RCV                      | 04A4    | 0000       |

| SPI2CON1L        | 0410             | 0x00       | I2C2TRN                      | 04A6    | 00FF       |

| SPI2CON1H        | 0412             | 0000       | I2C2BRG                      | 04A8    | 0000       |

| SPI2CON2L        | 0414             | 0000       | I2C2CONL                     | 04AA    | 1000       |

| SPI2STATL        | 0418             | 0028       | I2C2CONH                     | 04AC    | 0000       |

| SPI2STATH        | 041A             | 0000       | I2C2STAT                     | 04AE    | 0000       |

| SPI2BUFL         | 041C             | 0000       | I2C2ADD                      | 04B0    | 0000       |

| SPI2BUFH         | 041E             | 0000       | I2C2MSK                      | 04B2    | 0000       |

| SPI2BRGL         | 0420             | xxxx       | DMA                          |         | 1          |

| SPI2IMSKL        | 0424             | 0000       | DMACON                       | 04C4    | 0000       |

| SPI2IMSKH        | 0426             | 0000       | DMABUF                       | 04C6    | 0000       |

| SPI2URDTL        | 0428             | 0000       | DMAL                         | 04C8    | 0000       |

| SPI2URDTH        | 042A             | 0000       | DMAH                         | 04CA    | 0000       |

| SPI3CON1L        | 042C             | 0x00       | DMACH0                       | 04CC    | 0000       |

| SPI3CON1H        | 042E             | 0000       | DMAINT0                      | 04CE    | 0000       |

| SPI3CON2L        | 0430             | 0000       | DMASRC0                      | 04D0    | 0000       |

| SPI3STATL        | 0434             | 0028       | DMADST0                      | 04D2    | 0000       |

| SPI3STATH        | 0436             | 0000       | DMACNT0                      | 04D4    | 0001       |

| SPI3BUFL         | 0438             | 0000       | DMACH1                       | 04D6    | 0000       |

| SPI3BUFH         | 043A             | 0000       | DMAINT1                      | 04D8    | 0000       |

| SPI3BRGL         | 043C             | xxxx       | DMASRC1                      | 04DA    | 0000       |

| SPI3IMSKL        | 0440             | 0000       | DMADST1                      | 04DC    | 0000       |

| SPI3IMSKH        | 0442             | 0000       | DMACNT1                      | 04DE    | 0001       |

| SPI3URDTL        | 0444             | 0000       | DMACH2                       | 04E0    | 0000       |

| SPI3URDTH        | 0446             | 0000       | DMAINT2                      | 04E2    | 0000       |

| CONFIGURABLE     | LOGIC CELL (CLC) |            | DMASRC2                      | 04E4    | 0000       |

| CLC1CONL         | 0464             | 0000       | DMADST2                      | 04E6    | 0000       |

| CLC1CONH         | 0466             | 0000       | DMACNT2                      | 04E8    | 0001       |

| CLC1SEL          | 0468             | 0000       | DMACH3                       | 04EA    | 0000       |

| CLC1GLSL         | 046C             | 0000       | DMAINT3                      | 04EC    | 0000       |

| CLC1GLSH         | 046E             | 0000       | DMASRC3                      | 04EE    | 0000       |

| CLC2CONL         | 0470             | 0000       | DMADST3                      | 04F0    | 0000       |

| CLC2CONH         | 0472             | 0000       | DMACNT3                      | 04F2    | 0001       |

| CLC2SEL          | 0474             | 0000       | DMACH4                       | 04F4    | 0000       |

| CLC2GLSL         | 0478             | 0000       | DMAINT4                      | 04F6    | 0000       |

| CLC2GLSH         | 047A             | 0000       | DMASRC4                      | 04F8    | 0000       |

| l <sup>2</sup> C |                  |            | DMADST4                      | 04FA    | 0000       |

| I2C1RCV          | 0494             | 0000       | DMACNT4                      | 04FC    | 0001       |

| I2C1TRN          | 0496             | 00FF       | DMACH5                       | 04FE    | 0000       |

| R/W-0  | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| DMAEN  | —   | —   | —   | —   | —   | —   | —      |

| bit 15 |     |     |     |     |     |     | bit 8  |

|        |     |     |     |     |     |     |        |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| —      | —   | —   | —   |     |     | _   | PRSSEL |

| bit 7  |     |     |     |     |     |     | bit 0  |

|        |     |     |     |     |     |     |        |

## REGISTER 5-1: DMACON: DMA ENGINE CONTROL REGISTER

## Legend:

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 DMAEN: DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round-robin scheme

0 = Fixed priority scheme

| DISI                              | #5                                                 | ; Block all interrupts with priority <7<br>; for next 5 instructions                            |

|-----------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|

| MOV.B<br>MOV<br>MOV.B<br>MOV      | #0x55, W0<br>W0, NVMKEY<br>#0xAA, W1<br>W1, NVMKEY | ; Write the 0x55 key<br>;<br>; Write the 0xAA key                                               |

| BSET<br>NOP<br>NOP<br>BTSC<br>BRA | NVMCON, #WR<br>NVMCON, #15<br>\$-2                 | ; Start the programming sequence<br>; Required delays<br>; and wait for it to be<br>; completed |

|                                   |                                                    |                                                                                                 |

#### EXAMPLE 6-2: INITIATING A PROGRAMMING SEQUENCE

## REGISTER 9-8: REFOTRIML: REFERENCE OSCILLATOR TRIM REGISTER LOW

| R/W-0         | R/W-0      | R/W-0            | R/W-0         | R/W-0                             | R/W-0           | R/W-0            | R/W-0     |

|---------------|------------|------------------|---------------|-----------------------------------|-----------------|------------------|-----------|

|               |            |                  | ROTE          | RIM<0:7>                          |                 |                  |           |

| bit 15        |            |                  |               |                                   |                 |                  | bit 8     |

|               |            |                  |               |                                   |                 |                  |           |

| R/W-0         | U-0        | U-0              | U-0           | U-0                               | U-0             | U-0              | U-0       |

| ROTRIM8       | —          | —                | —             | —                                 | —               | —                | —         |

| bit 7         |            |                  |               |                                   |                 |                  | bit C     |

|               |            |                  |               |                                   |                 |                  |           |

| Legend:       |            |                  |               |                                   |                 |                  |           |

| R = Readable  | e bit      | W = Writable I   | oit           | U = Unimplem                      | nented bit, rea | d as '0'         |           |

| -n = Value at | POR        | '1' = Bit is set |               | '0' = Bit is clea                 | ared            | x = Bit is unkr  | nown      |

|               |            |                  |               |                                   |                 |                  |           |

| bit 15-7      | ROTRIM<0:8 | B>: REFO Trim b  | oits          |                                   |                 |                  |           |

|               |            |                  |               | the RODIVx valu<br>the RODIVx val |                 | period of the RE | FO clock. |

|               | 000000001  | = 1/512 (0.0019  | 53125 divisoi | r added to the R                  | ODIVx value)    |                  |           |

|               | 00000010   | = 2/512 (0.0039  | 0625 divisor  | added to the RO                   | DIVx value)     |                  |           |

|               | •          |                  |               |                                   |                 |                  |           |

|               | •          |                  |               |                                   |                 |                  |           |

|               | 100000000  | = 256/512 (0.50  | 00 divisor ad | ded to the RODI                   | Vx value)       |                  |           |

|               | •          |                  |               |                                   |                 |                  |           |

|               | •          |                  |               |                                   |                 |                  |           |

|               | 111111110  | - 510/512 (0.00  | 600375 divis  | or added to the F                 |                 | <b>`</b>         |           |

111111110 = 510/512 (0.99609375 divisor added to the RODIVx value) 111111111 = 511/512 (0.998046875 divisor added to the RODIVx value)

bit 6-0 Unimplemented: Read as '0'

| Device             |      | PORTA I/O Pins |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

|--------------------|------|----------------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Device             | RA15 | RA14           | RA13 | RA12 | RA11 | RA10 | RA9 | RA8 | RA7 | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 |

| PIC24FJXXXGA705    | _    | Х              | Х    | Х    | Х    | Х    | Х   | Х   | Х   | —   | _   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA704    | _    | _              | _    | —    | _    | Х    | Х   | Х   | Х   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA702    | _    | _              | _    | _    | _    | _    | _   | _   | _   | _   | _   | Х   | Х   | Х   | Х   | Х   |

| ANSELA bit present |      | _              | _    | _    |      |      | _   |     |     | _   |     |     | Х   | Х   | Х   | Х   |

## TABLE 11-3: PORTA PIN AND ANSELx AVAILABILITY

# TABLE 11-4: PORTB PIN AND ANSELx AVAILABILITY

| Device             |      | PORTB I/O Pins |      |      |      |      |     |     |     |     |     |     |     |     | _   |     |

|--------------------|------|----------------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Device             | RB15 | RB14           | RB13 | RB12 | RB11 | RB10 | RB9 | RB8 | RB7 | RB6 | RB5 | RB4 | RB3 | RB2 | RB1 | RB0 |

| PIC24FJXXXGA705    | Х    | Х              | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA704    | Х    | Х              | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA702    | Х    | Х              | Х    | Х    | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| ANSELB bit present | Х    | Х              | Х    | Х    | _    | _    | Х   |     |     |     |     | _   | Х   | Х   | Х   | Х   |

### TABLE 11-5: PORTC PIN AND ANSELX AVAILABILITY

| Device             |      | PORTC I/O Pins |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

|--------------------|------|----------------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Device             | RC15 | RC14           | RC13 | RC12 | RC11 | RC10 | RC9 | RC8 | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| PIC24FJXXXGA705    | —    | _              | —    |      | —    |      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA704    |      | _              | _    | _    |      | _    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| PIC24FJXXXGA702    |      | _              | _    | _    |      | _    | _   | _   | _   | _   | _   | _   | _   | _   | _   | —   |

| ANSELC bit present |      | _              | _    | _    |      | _    |     |     |     |     |     | _   | Х   | Х   | Х   | Х   |

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| _             | —     | RP5R5            | RP5R4 | RP5R3             | RP5R2            | RP5R1           | RP5R0 |

| bit 15        |       |                  |       |                   |                  |                 | bit 8 |

|               |       |                  |       |                   |                  |                 |       |

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| _             | —     | RP4R5            | RP4R4 | RP4R3             | RP4R2            | RP4R1           | RP4R0 |

| bit 7         |       |                  |       |                   |                  |                 | bit 0 |

|               |       |                  |       |                   |                  |                 |       |

| Legend:       |       |                  |       |                   |                  |                 |       |

| R = Readable  | e bit | W = Writable I   | bit   | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

### REGISTER 11-34: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

- bit 13-8**RP5R<5:0>:** RP5 Output Pin Mapping bits<br/>Peripheral Output Number n is assigned to pin, RP5 (see Table 11-7 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

- bit 5-0 **RP4R<5:0>:** RP4 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP4 (see Table 11-7 for peripheral function numbers).

## REGISTER 11-35: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

|---------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

| R = Readable  | e bit | W = Writable I   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| Legend:       |       |                  |       |                                         |       |       |       |

|               |       |                  |       |                                         |       |       | Sit 0 |

| bit 7         |       |                  |       | 1                                       |       |       | bit 0 |

| _             | —     | RP6R5            | RP6R4 | RP6R3                                   | RP6R2 | RP6R1 | RP6R0 |

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|               |       |                  |       |                                         |       |       |       |

| bit 15        |       |                  |       |                                         |       |       | bit 8 |

|               | _     | RP7R5            | RP7R4 | RP7R3                                   | RP7R2 | RP7R1 | RP7R0 |

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP7R<5:0>:** RP7 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP7 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP6R<5:0>:** RP6 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP6 (see Table 11-7 for peripheral function numbers).

| Legend: |     |        |        |        |        |        |        |

|---------|-----|--------|--------|--------|--------|--------|--------|

| bit 7   |     |        |        |        |        |        | bit 0  |

| _       |     | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|         |     |        |        |        |        |        |        |

| bit 15  |     |        |        | •      |        |        | bit 8  |

| _       | _   | RP13R5 | RP13R4 | RP13R3 | RP13R2 | RP13R1 | RP13R0 |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

#### REGISTER 11-38: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

'1' = Bit is set

-n = Value at POR

bit 13-8RP13R<5:0>: RP13 Output Pin Mapping bits<br/>Peripheral Output Number n is assigned to pin, RP13 (see Table 11-7 for peripheral function numbers).bit 7-6Unimplemented: Read as '0'

'0' = Bit is cleared

x = Bit is unknown

bit 5-0 **RP12R<5:0>:** RP12 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP12 (see Table 11-7 for peripheral function numbers).

## REGISTER 11-39: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| _       | —   | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

| _ogona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP15R<5:0>:** RP15 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP15 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP14R<5:0>:** RP14 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP14 (see Table 11-7 for peripheral function numbers).

| U-0     | U-0 | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | —      | —      | —      | —      | —      | —      |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

## REGISTER 11-46: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP28R<5:0>:** RP28 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP28 (see Table 11-7 for peripheral function numbers).

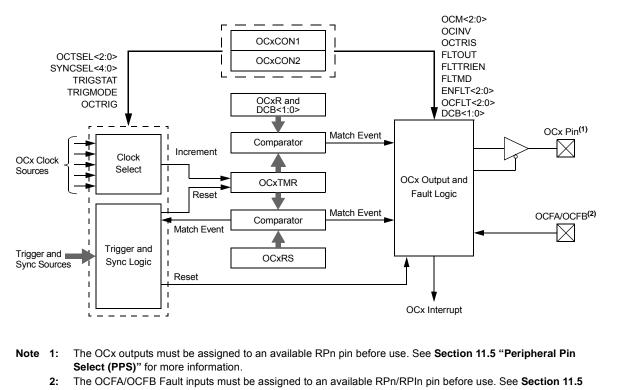

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

"Peripheral Pin Select (PPS)" for more information.

# 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for Single-Shot or Continuous mode pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins if available on the OCx module you are using. Otherwise, configure the dedicated OCx output pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation (= 0xx).

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure Trigger mode operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the Trigger or Sync source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no Sync/Trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a Trigger source event occurs.

## **REGISTER 16-5:** CCPxCON3L: CCPx CONTROL 3 LOW REGISTERS<sup>(1)</sup>

| U-0             | U-0 | U-0              | U-0     | U-0                                     | U-0   | U-0   | U-0   |  |  |

|-----------------|-----|------------------|---------|-----------------------------------------|-------|-------|-------|--|--|

| —               | _   | —                | —       | —                                       | —     | —     | —     |  |  |

| bit 15          |     |                  |         |                                         |       |       | bit 8 |  |  |

|                 |     |                  |         |                                         |       |       |       |  |  |

| U-0             | U-0 | R/W-0            | R/W-0   | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

| —               | _   |                  | DT<5:0> |                                         |       |       |       |  |  |

| bit 7           |     |                  |         |                                         |       |       | bit 0 |  |  |

|                 |     |                  |         |                                         |       |       |       |  |  |

| Legend:         |     |                  |         |                                         |       |       |       |  |  |

| R = Readable    | bit | W = Writable I   | oit     | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at F | POR | '1' = Bit is set |         | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |

|                 |     |                  |         |                                         |       |       |       |  |  |

#### bit 15-6 Unimplemented: Read as '0'

bit 5-0 DT<5:0>: CCPx Dead-Time Select bits<sup>(1)</sup> 111111 = Inserts 63 dead-time delay periods between complementary output signals 11110 = Inserts 62 dead-time delay periods between complementary output signals ... 000010 = Inserts 2 dead-time delay periods between complementary output signals 000001 = Inserts 1 dead-time delay period between complementary output signals 000000 = Dead-time logic is disabled

Note 1: This register is implemented in the MCCP1 module only.

### REGISTER 17-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0          | U-0                            | U-0              | U-0           | U-0                  | U-0              | U-0             | U-0   |

|--------------|--------------------------------|------------------|---------------|----------------------|------------------|-----------------|-------|

|              | —                              | _                | _             | —                    | _                | _               | —     |

| bit 15       |                                |                  |               |                      |                  |                 | bit 8 |

|              |                                |                  |               |                      |                  |                 |       |

| U-0          | U-0                            | U-0              | R/W-0         | R/W-0                | R/W-0            | R/W-0           | R/W-0 |

|              | _                              |                  |               | W                    | LENGTH<4:0>      | (1,2)           |       |

| bit 7        |                                |                  |               |                      |                  |                 | bit 0 |

|              |                                |                  |               |                      |                  |                 |       |

| Legend:      |                                |                  |               |                      |                  |                 |       |

| R = Readab   | le bit                         | W = Writable     | bit           | U = Unimplen         | nented bit, read | d as '0'        |       |

| -n = Value a | It POR                         | '1' = Bit is set |               | '0' = Bit is cle     | ared             | x = Bit is unkr | nown  |

|              |                                |                  |               |                      |                  |                 |       |

| bit 15-5     | =                              | ted: Read as '   |               | (1.0)                |                  |                 |       |

| bit 4-0      |                                | 1:0>: Variable V | Nord Length b | its <sup>(1,2)</sup> |                  |                 |       |

|              | 11111 = 32-b                   |                  |               |                      |                  |                 |       |

|              | 11110 = 31-b<br>11101 = 30-b   |                  |               |                      |                  |                 |       |

|              | 11100 <b>= 29-</b> b           |                  |               |                      |                  |                 |       |

|              | 11011 <b>= 28-</b> b           |                  |               |                      |                  |                 |       |

|              | 11010 <b>= 27-</b> b           |                  |               |                      |                  |                 |       |

|              | 11001 <b>= 26-</b> b           | oit data         |               |                      |                  |                 |       |

|              | 11000 <b>= 25-</b> b           |                  |               |                      |                  |                 |       |

|              | 10111 <b>= 24</b> -b           |                  |               |                      |                  |                 |       |

|              | 10110 = 23-b                   |                  |               |                      |                  |                 |       |

|              | 10101 = 22-b<br>10100 = 21-b   |                  |               |                      |                  |                 |       |

|              | 10011 = 20-b                   |                  |               |                      |                  |                 |       |

|              | 10010 = <b>19</b> -b           |                  |               |                      |                  |                 |       |

|              | 10001 <b>= 18-</b> b           | oit data         |               |                      |                  |                 |       |

|              | 10000 <b>= 17</b> -b           |                  |               |                      |                  |                 |       |

|              | 01111 = <b>16</b> -b           |                  |               |                      |                  |                 |       |

|              | 01110 = 15-b<br>01101 = 14-b   |                  |               |                      |                  |                 |       |

|              | 01100 = 13-b                   |                  |               |                      |                  |                 |       |

|              | 01011 = <b>12</b> -b           |                  |               |                      |                  |                 |       |

|              | 01010 = <b>11</b> -b           |                  |               |                      |                  |                 |       |

|              | 01001 = <b>10</b> -b           | oit data         |               |                      |                  |                 |       |

|              | 01000 <b>= 9-bit</b>           |                  |               |                      |                  |                 |       |

|              | 00111 <b>= 8-bit</b>           |                  |               |                      |                  |                 |       |

|              | 00110 = 7-bit<br>00101 = 6-bit |                  |               |                      |                  |                 |       |

|              | 00101 = 6-bit<br>00100 = 5-bit |                  |               |                      |                  |                 |       |

|              | 000100 <b>= 3-bi</b>           |                  |               |                      |                  |                 |       |

|              | 00010 = <b>3</b> -bit          |                  |               |                      |                  |                 |       |

|              | 00001 = <b>2-bit</b>           |                  |               |                      |                  |                 |       |

|              |                                |                  |               | CON1L<11:10>         |                  |                 |       |

- **Note 1:** These bits are effective when AUDEN = 0 only.

- 2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

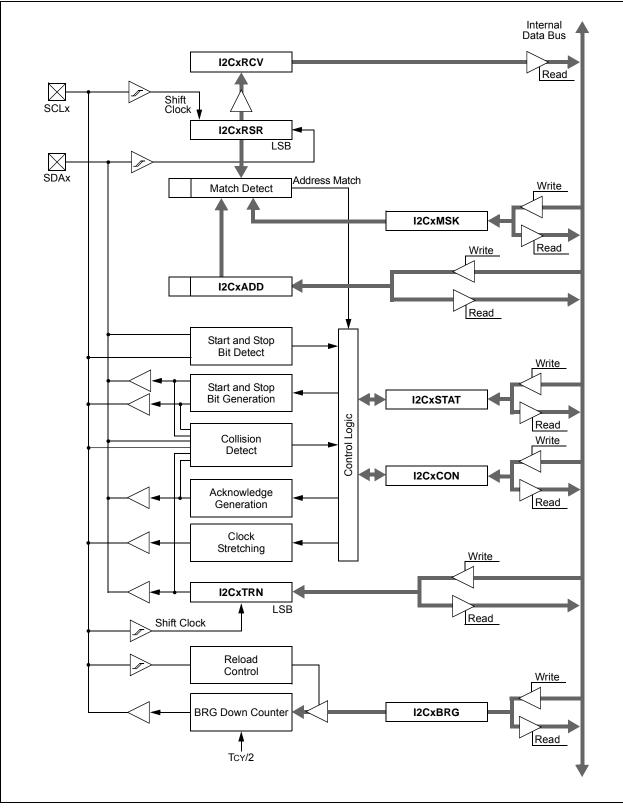

# FIGURE 18-1: I2Cx BLOCK DIAGRAM

## REGISTER 25-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    | -                                 |                |                  |                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|------------------|----------------|

| R/W-0            | R/W-0                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                | U-0                               | U-0            | R/W-0, HS        | R-0, HSC       |

| CEN              | COE                                                                                                                                                                 | CPOL                                                                                                                                                                                                                                                                    | —                                                                                                                                                                  | —                                 | —              | CEVT             | COUT           |

| bit 15           |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  | bit 8          |

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| R/W-0            | R/W-0                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                              | U-0                               | U-0            | R/W-0            | R/W-0          |

| EVPOL1           | EVPOL0                                                                                                                                                              | —                                                                                                                                                                                                                                                                       | CREF                                                                                                                                                               | —                                 | —              | CCH1             | CCH0           |

| bit 7            |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  | bit 0          |

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| Legend:          |                                                                                                                                                                     | HS = Hardware                                                                                                                                                                                                                                                           | e Settable bit                                                                                                                                                     | HSC = Hardv                       | vare Settable  | /Clearable bit   |                |

| R = Readabl      | e bit                                                                                                                                                               | W = Writable b                                                                                                                                                                                                                                                          | oit                                                                                                                                                                | U = Unimpler                      | mented bit, re | ad as '0'        |                |

| -n = Value at    | POR                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                                                                                                        |                                                                                                                                                                    | '0' = Bit is cle                  | eared          | x = Bit is unkr  | nown           |

| bit 15<br>bit 14 | 1 = Compara<br>0 = Compara<br><b>COE:</b> Compa<br>1 = Compara                                                                                                      | arator Enable bit<br>ator is enabled<br>ator is disabled<br>arator Output En-<br>ator output is pre<br>ator output is inte                                                                                                                                              | sent on the C>                                                                                                                                                     | OUT pin                           |                |                  |                |

| bit 13           | •                                                                                                                                                                   | parator Output P                                                                                                                                                                                                                                                        | 5                                                                                                                                                                  | oit                               |                |                  |                |

|                  | 1 = Compara                                                                                                                                                         | ator output is inv<br>ator output is not                                                                                                                                                                                                                                | erted                                                                                                                                                              |                                   |                |                  |                |

| bit 12-10        | Unimplemer                                                                                                                                                          | nted: Read as '0                                                                                                                                                                                                                                                        | ,                                                                                                                                                                  |                                   |                |                  |                |

| bit 9            | CEVT: Comp                                                                                                                                                          | arator Event bit                                                                                                                                                                                                                                                        |                                                                                                                                                                    |                                   |                |                  |                |

|                  | are disal                                                                                                                                                           | ator event that is<br>bled until the bit<br>ator event has no                                                                                                                                                                                                           | is cleared                                                                                                                                                         | POL<1:0> has c                    | occurred; sub  | sequent triggers | and interrupts |

| bit 8            | COUT: Comp                                                                                                                                                          | parator Output bi                                                                                                                                                                                                                                                       | t                                                                                                                                                                  |                                   |                |                  |                |

|                  | $\frac{\text{When CPOL}}{1 = \text{VIN} + > \text{V}}$ $0 = \text{VIN} + < \text{V}$                                                                                | /in-<br>/in-                                                                                                                                                                                                                                                            |                                                                                                                                                                    |                                   |                |                  |                |

|                  | $\frac{\text{When CPOL}}{1 = \text{VIN} + < \text{V}}$                                                                                                              |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

|                  | 0 = VIN + > V                                                                                                                                                       |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| bit 7-6          | 11 = Trigger/<br>10 = Trigger/<br>High-to<br><u>If CPOI</u><br>Low-to-<br>01 = Trigger/<br><u>If CPOI</u><br>Low-to-<br><u>If CPOI</u><br>Low-to-<br><u>If CPOI</u> | Trigger/Event/<br>/event/interrupt is<br>/event/interrupt is<br>_ = 0 (non-inverter<br>-low transition or<br>_ = 1 (inverted pot<br>high transition of<br>/event/interrupt is<br>_ = 0 (non-inverter<br>high transition of<br>_ = 1 (inverted pot<br>-low transition or | s generated on<br>s generated on<br><u>ed polarity):</u><br>nly.<br><u>plarity):</u><br>nly.<br>s generated on<br><u>ed polarity):</u><br>nly.<br><u>plarity):</u> | any change of<br>transition of th | e comparator   | output:          | CEVT = 0)      |

|                  | 00 = Trigger/                                                                                                                                                       | /event/interrupt g                                                                                                                                                                                                                                                      | eneration is di                                                                                                                                                    | sabled                            |                |                  |                |

| bit 5            | Unimplemer                                                                                                                                                          | nted: Read as '0                                                                                                                                                                                                                                                        | ,                                                                                                                                                                  |                                   |                |                  |                |

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>  | 1             | 2              | None                     |

| TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

NOTES:

#### TABLE 32-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CH        | ARACTE            | RISTICS                                                                     | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |          |     |                                                    |  |  |  |

|--------------|-------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|----------------------------------------------------|--|--|--|

| Param<br>No. | Symbol            | Characteristic                                                              | Min                                                                                                                                             | Тур | Max Unit |     | Conditions                                         |  |  |  |

| Operati      | Operating Voltage |                                                                             |                                                                                                                                                 |     |          |     |                                                    |  |  |  |

| DC10         | Vdd               | Supply Voltage                                                              | 2.0                                                                                                                                             | —   | 3.6      | V   | BOR is disabled                                    |  |  |  |

|              |                   |                                                                             | VBOR                                                                                                                                            | _   | 3.6      | V   | BOR is enabled                                     |  |  |  |

| DC12         | Vdr               | RAM Data Retention<br>Voltage <sup>(1)</sup>                                | Greater of:<br>VPORREL or<br>VBOR                                                                                                               | —   |          | V   | VBOR is used only if BOR<br>is enabled (BOREN = 1) |  |  |  |

| DC16         | VPOR              | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            | Vss                                                                                                                                             | _   |          | V   | (Note 2)                                           |  |  |  |

| DC17A        | SVDD              | Recommended<br>VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal | 1V/20 ms                                                                                                                                        | _   | 1V/10 µS | Sec | (Note 2, Note 4)                                   |  |  |  |

| DC17B        | VBOR              | Brown-out Reset<br>Voltage on VDD<br>Transition, High-to-Low                | 2.0                                                                                                                                             | 2.1 | 2.2      | V   | (Note 3)                                           |  |  |  |

**Note 1:** This is the limit to which VDD may be lowered and the RAM contents will always be retained.

**2:** If the VPOR or SVDD parameters are not met, or the application experiences slow power-down VDD ramp rates, it is recommended to enable and use BOR.

**3:** On a rising VDD power-up sequence, application firmware execution begins at the higher of the VPORREL or VBOR level (when BOREN = 1).

4: VDD rise times outside this window may not internally reset the processor and are not parametrically tested.

| TABLE 32-11: | <b>INTERNAL VOLTAG</b> | E REGULATOR SPECIFICATION | ١S |

|--------------|------------------------|---------------------------|----|

|--------------|------------------------|---------------------------|----|

| <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |        |                                         |      |     |      |       |                                                                    |  |

|---------------------------------------------------------------------------|--------|-----------------------------------------|------|-----|------|-------|--------------------------------------------------------------------|--|

| Param<br>No.                                                              | Symbol | Characteristics                         | Min  | Тур | Max  | Units | Comments                                                           |  |

| DVR                                                                       | TVREG  | Voltage Regulator Start-up Time         |      | 10  | -    | μS    | VREGS = 0 with any POR or<br>BOR                                   |  |

| DVR10                                                                     | Vbg    | Internal Band Gap Reference             | 1.14 | 1.2 | 1.26 | V     |                                                                    |  |

| DVR11                                                                     | Tbg    | Band Gap Reference<br>Start-up Time     | _    | 1   | -    | ms    |                                                                    |  |

| DVR20                                                                     | Vrgout | Regulator Output Voltage                | 1.6  | 1.8 | 2.0  | V     | Vdd > 1.9V                                                         |  |

| DVR21                                                                     | CEFC   | External Filter Capacitor Value         | 10   | —   | —    | μF    | Series resistance < $3\Omega$<br>recommended; < $5\Omega$ required |  |

| DVR30                                                                     | Vlvr   | Low-Voltage Regulator<br>Output Voltage |      | 1.2 | _    | V     | $RETEN = 1, \overline{LPCFG} = 0$                                  |  |

#### TABLE 32-12: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS Г

| <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |        |                                          |                                  |      |      |      |       |                           |  |

|---------------------------------------------------------------------------|--------|------------------------------------------|----------------------------------|------|------|------|-------|---------------------------|--|

| Param<br>No.                                                              | Symbol | Charac                                   | teristic                         | Min  | Тур  | Max  | Units | Conditions                |  |

| DC18                                                                      | Vhlvd  | HLVD Voltage on VDD                      | HLVDL<3:0> = 0100 <sup>(1)</sup> | 3.45 | _    | 3.73 | V     |                           |  |

|                                                                           |        | Transition                               | HLVDL<3:0> = 0101                | 3.25 |      | 3.58 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 0110                | 2.95 |      | 3.25 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 0111                | 2.75 | —    | 3.04 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1000                | 2.65 |      | 2.92 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1001                | 2.45 | —    | 2.70 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1010                | 2.35 |      | 2.60 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1011                | 2.25 | —    | 2.49 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1100                | 2.15 | —    | 2.39 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1101                | 2.08 | —    | 2.28 | V     |                           |  |

|                                                                           |        |                                          | HLVDL<3:0> = 1110                | 2.00 |      | 2.15 | V     |                           |  |

| DC101                                                                     | VTHL   | HLVD Voltage on<br>HLVDIN Pin Transition | HLVDL<3:0> = 1111                | _    | 1.20 | —    | V     |                           |  |

| DC105                                                                     | TONLVD | HLVD Module Enable 1                     | īme                              | _    | 5    |      | μS    | From POR or<br>HLVDEN = 1 |  |

**Note 1:** Trip points for values of HLVD<3:0>, from '0000' to '0011', are not implemented.

| AC CH        | ARACTER               | ISTICS                                               | Standard Operating te              |          |                                   | : 2.0V to 3.6V (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial |                                                                                                |  |

|--------------|-----------------------|------------------------------------------------------|------------------------------------|----------|-----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol Characteristic |                                                      | Min.                               | Тур      | Max.                              | Units                                                                                   | Conditions                                                                                     |  |

|              |                       |                                                      | Devid                              | e Supp   | ly                                |                                                                                         |                                                                                                |  |

| AD01         | AVDD                  | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 2.2 |          | Lesser of:<br>VDD + 0.3<br>or 3.6 | V                                                                                       |                                                                                                |  |

| AD02         | AVss                  | Module Vss Supply                                    | Vss – 0.3                          |          | Vss + 0.3                         | V                                                                                       |                                                                                                |  |

|              |                       |                                                      | Refere                             | nce Inp  | uts                               |                                                                                         |                                                                                                |  |

| AD05         | VREFH                 | Reference Voltage High                               | AVss + 1.7                         |          | AVDD                              | V                                                                                       |                                                                                                |  |

| AD06         | VREFL                 | Reference Voltage Low                                | AVss                               |          | AVDD – 1.7                        | V                                                                                       |                                                                                                |  |

| AD07         | VREF                  | Absolute Reference<br>Voltage                        | AVss – 0.3                         |          | AVDD + 0.3                        | V                                                                                       |                                                                                                |  |

|              |                       | •                                                    | Anal                               | og Input | ts                                |                                                                                         |                                                                                                |  |

| AD10         | VINH-VINL             | Full-Scale Input Span                                | VREFL                              | _        | VREFH                             | V                                                                                       | (Note 2)                                                                                       |  |

| AD11         | VIN                   | Absolute Input Voltage                               | AVss - 0.3                         | _        | AVDD + 0.3                        | V                                                                                       |                                                                                                |  |

| AD12         | Vinl                  | Absolute VINL Input<br>Voltage                       | AVss – 0.3                         | _        | AVDD/3                            | V                                                                                       |                                                                                                |  |