Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT               |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 14x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga704t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | F                           | Pin Number/Grid Locator |                |                    |     |                 |                                      |  |  |

|-----------------|-----------------------------|-------------------------|----------------|--------------------|-----|-----------------|--------------------------------------|--|--|

| Pin<br>Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN     | 44-Pin<br>TQFP | 48-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                          |  |  |

| AN0             | 2                           | 27                      | 19             | 21                 | Ι   | ANA             | A/D Analog Inputs                    |  |  |

| AN1             | 3                           | 28                      | 20             | 22                 | I   | ANA             |                                      |  |  |

| AN2             | 4                           | 1                       | 21             | 23                 | I   | ANA             |                                      |  |  |

| AN3             | 5                           | 2                       | 22             | 24                 | I   | ANA             |                                      |  |  |

| AN4             | 6                           | 3                       | 23             | 25                 | I   | ANA             |                                      |  |  |

| AN5             | 7                           | 4                       | 24             | 26                 | I   | ANA             |                                      |  |  |

| AN6             | 25                          | 22                      | 14             | 15                 | Ι   | ANA             | ]                                    |  |  |

| AN7             | 24                          | 21                      | 11             | 12                 | I   | ANA             |                                      |  |  |

| AN8             | 23                          | 20                      | 10             | 11                 | I   | ANA             |                                      |  |  |

| AN9             | 26                          | 23                      | 15             | 16                 | I   | ANA             |                                      |  |  |

| AN10            | _                           | _                       | 25             | 27                 | I   | ANA             |                                      |  |  |

| AN11            | _                           |                         | 26             | 28                 | I   | ANA             | ]                                    |  |  |

| AN12            | _                           | —                       | 27             | 29                 | I   | ANA             |                                      |  |  |

| AN13            | _                           | _                       | 36             | 39                 | I   | ANA             |                                      |  |  |

| AVdd            | 28                          | 25                      | 17             | 18                 | Р   | _               | Positive Supply for Analog modules   |  |  |

| AVss            | 27                          | 24                      | 16             | 17                 | Р   | _               | Ground Reference for Analog modules  |  |  |

| C1INA           | 7                           | 4                       | 24             | 26                 | I   | ANA             | Comparator 1 Input A                 |  |  |

| C1INB           | 6                           | 3                       | 23             | 25                 | Ι   | ANA             | Comparator 1 Input B                 |  |  |

| C1INC           | 18, 24                      | 15, 21                  | 1, 11          | 1, 12              | I   | ANA             | Comparator 1 Input C                 |  |  |

| C1IND           | 9                           | 6                       | 30             | 33                 | I   | ANA             | Comparator 1 Input D                 |  |  |

| C2INA           | 5                           | 2                       | 22             | 24                 | Ι   | ANA             | Comparator 2 Input A                 |  |  |

| C2INB           | 4                           | 1                       | 21             | 23                 | I   | ANA             | Comparator 2 Input B                 |  |  |

| C2INC           | 18                          | 15                      | 1              | 1                  | Ι   | ANA             | Comparator 2 Input C                 |  |  |

| C2IND           | 10                          | 7                       | 31             | 34                 | I   | ANA             | Comparator 2 Input D                 |  |  |

| C3INA           | 26                          | 23                      | 15             | 16                 | Ι   | ANA             | Comparator 3 Input A                 |  |  |

| C3INB           | 25                          | 22                      | 14             | 15                 | I   | ANA             | Comparator 3 Input B                 |  |  |

| C3INC           | 2, 18                       | 15, 27                  | 1, 19          | 1, 21              | I   | ANA             | Comparator 3 Input C                 |  |  |

| C3IND           | 3                           | 28                      | 20             | 22                 | I   | ANA             | Comparator 3 Input D                 |  |  |

| CLKI            | 9                           | 6                       | 30             | 33                 | —   | —               | Main Clock Input Connection          |  |  |

| CLKO            | 10                          | 7                       | 31             | 34                 | 0   | DIG             | System Clock Output                  |  |  |

| CTCMP           | 4                           | 1                       | 21             | 23                 | 0   | ANA             | CTMU Comparator 2 Input (Pulse mode) |  |  |

### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

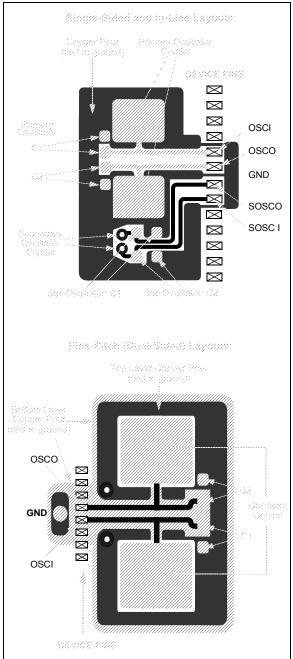

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

- AN1798, "Crystal Selection for Low-Power Secondary Oscillator"

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### REGISTER 5-3: DMAINTn: DMA CHANNEL n INTERRUPT REGISTER

| R-0                     | R/W-0                                                                                                                        | R/W-0                                            | R/W-0                                           | R/W-0                                                    | R/W-0           | R/W-0           | R/W-0           |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|-----------------|-----------------|-----------------|

| DBUFWF <sup>(1)</sup>   | CHSEL6                                                                                                                       | CHSEL5                                           | CHSEL4                                          | CHSEL3                                                   | CHSEL2          | CHSEL1          | CHSEL0          |

| bit 15                  | 1                                                                                                                            |                                                  | I                                               | 4                                                        |                 |                 | bit 8           |

|                         |                                                                                                                              |                                                  |                                                 |                                                          |                 |                 |                 |

| R/W-0                   | R/W-0                                                                                                                        | R/W-0                                            | R/W-0                                           | R/W-0                                                    | U-0             | U-0             | R/W-0           |

| HIGHIF <sup>(1,2)</sup> | LOWIF <sup>(1,2)</sup>                                                                                                       | DONEIF <sup>(1)</sup>                            | HALFIF <sup>(1)</sup>                           | OVRUNIF <sup>(1)</sup>                                   | —               | _               | HALFEN          |

| bit 7                   |                                                                                                                              |                                                  |                                                 |                                                          |                 |                 | bit             |

| Legend:                 |                                                                                                                              |                                                  |                                                 |                                                          |                 |                 |                 |

| R = Readable            | , bit                                                                                                                        | W = Writable                                     | hit                                             | U = Unimplem                                             | ontod hit roa   | d as '0'        |                 |

|                         |                                                                                                                              | '1' = Bit is set                                 |                                                 | '0' = Bit is clea                                        |                 |                 | 0000            |

| -n = Value at           | PUR                                                                                                                          |                                                  |                                                 |                                                          | areu            | x = Bit is unkr | IOWII           |

| bit 15                  | 1 = The cont<br>DMASRO                                                                                                       | Cn in Null Write<br>ent of the DMA               | A buffer has r<br>mode                          | bit <b>(1)</b><br>not been writter<br>n written to the k |                 | ·               |                 |

| bit 14-8                |                                                                                                                              | : DMA Channe                                     |                                                 | ction bits                                               |                 |                 |                 |

|                         |                                                                                                                              | for a complete                                   |                                                 | (1 2)                                                    |                 |                 |                 |

| bit 7                   | 1 = The DMA<br>data RAM                                                                                                      | ∕l space                                         | ttempted to ac                                  | cess an addres                                           | -               | DMAH or the up  | per limit of th |

| bit 6                   |                                                                                                                              | Low Address I                                    |                                                 | -                                                        |                 |                 |                 |

|                         | 1 = The DMA<br>the SFR                                                                                                       | A channel has a range (07FFh)                    | attempted to a                                  | ccess the DMA<br>low address lin                         |                 | lower than DM   | AL, but abov    |

| bit 5                   |                                                                                                                              | A Complete Op                                    |                                                 |                                                          | int interrupt   |                 |                 |

|                         | $\frac{\text{If CHEN} = 1:}{1 = \text{The prev}}$ $0 = \text{The current}$ $\frac{\text{If CHEN} = 0:}{1 = \text{The prev}}$ | ious DMA sess<br>ent DMA sessic<br>ious DMA sess | ion has ended<br>n has not yet<br>ion has ended | with completion                                          | n               |                 |                 |

| bit 4                   |                                                                                                                              | A 50% Waterma                                    |                                                 |                                                          |                 |                 |                 |

|                         | 1 = DMACN                                                                                                                    | Γn has reached<br>Γn has not reac                | the halfway p                                   | oint to 0000h                                            |                 |                 |                 |

| bit 3                   |                                                                                                                              | MA Channel Ov                                    |                                                 | • •                                                      |                 |                 |                 |

|                         | 1 = The DMA                                                                                                                  |                                                  | gered while it is                               | s still completing                                       | the operation   | based on the p  | revious trigge  |

| bit 2-1                 | Unimplemen                                                                                                                   | ted: Read as '                                   | )'                                              |                                                          |                 |                 |                 |

| bit 0                   | -                                                                                                                            | Ifway Completion                                 |                                                 | bit                                                      |                 |                 |                 |

|                         | 1 = Interrupts                                                                                                               | s are invoked w                                  | hen DMACNT                                      | n has reached i pletion of the tra                       |                 | nt and at comp  | etion           |

| Note 1: Se              | etting these flag                                                                                                            | s in software de                                 | oes not genera                                  | ate an interrupt.                                        |                 |                 |                 |

|                         | sting for addres<br>//AL) is NOT do                                                                                          |                                                  |                                                 | or DMADSTn is                                            | s either greate | r than DMAH o   | r less than     |

DMAL) is NOT done before the actual access.

**RCON: RESET CONTROL REGISTER**

**REGISTER 7-1:**

| R/W-0                | R/W-0                         | R/W-1                                  | R/W-0                  | U-0                                         | U-0                 | R/W-0              | R/W-0                |

|----------------------|-------------------------------|----------------------------------------|------------------------|---------------------------------------------|---------------------|--------------------|----------------------|

| TRAPR <sup>(1)</sup> | ) IOPUWR <sup>(1)</sup>       | SBOREN <sup>(5)</sup>                  | RETEN <sup>(2)</sup>   | _                                           | _                   | CM <sup>(1)</sup>  | VREGS <sup>(3)</sup> |

| bit 15               |                               |                                        |                        |                                             |                     | •                  | bit 8                |

| R/W-0                | R/W-0                         | R/W-0                                  | R/W-0                  | R/W-0                                       | R/W-0               | R/W-1              | R/W-1                |

| EXTR <sup>(1)</sup>  | SWR <sup>(1)</sup>            | SWDTEN <sup>(4)</sup>                  | WDTO <sup>(1)</sup>    | SLEEP <sup>(1)</sup>                        | IDLE <sup>(1)</sup> | BOR <sup>(1)</sup> | POR <sup>(1)</sup>   |

| bit 7                | own                           | OWDIEN                                 | WDTO                   | OLLLI                                       | IDEE                | Bort               | bit C                |

|                      |                               |                                        |                        |                                             |                     |                    | _                    |

| Legend:              |                               |                                        |                        |                                             |                     |                    |                      |

| R = Readal           |                               | W = Writable b                         | it                     | U = Unimpleme                               |                     |                    |                      |

| -n = Value a         | at POR                        | '1' = Bit is set                       |                        | '0' = Bit is clear                          | ed                  | x = Bit is unkı    | nown                 |

| bit 15               | TRAPR: Trap                   | o Reset Flag bit <sup>(1</sup>         | 1)                     |                                             |                     |                    |                      |

|                      |                               | onflict Reset has<br>onflict Reset has |                        | 1                                           |                     |                    |                      |

| bit 14               | •                             |                                        |                        | ·<br>V Register Acces                       | s Reset Flag        | hit(1)             |                      |

|                      |                               | • .                                    |                        | al address mode                             | •                   |                    | is used as ar        |

|                      | Address                       | Pointer and cau                        | sed a Reset            |                                             |                     | Ū.                 |                      |

|                      | -                             | -                                      |                        | gister Reset has                            | not occurred        |                    |                      |

| bit 13               |                               | oftware Control C                      | Over the BOR           | Function bit <sup>(5)</sup>                 |                     |                    |                      |

|                      | 1 = BOR is e<br>0 = BOR is di |                                        |                        |                                             |                     |                    |                      |

| bit 12               | RETEN: Rete                   | ention Mode Ena                        | ble bit <sup>(2)</sup> |                                             |                     |                    |                      |

|                      |                               |                                        |                        | e is in Sleep mod<br>Itage levels are p     |                     | lator supplies t   | o the core)          |

| bit 11-10            | Unimplemen                    | ted: Read as '0                        | ,                      |                                             |                     |                    |                      |

| bit 9                | CM: Configur                  | ation Word Misn                        | natch Reset F          | =lag bit <sup>(1)</sup>                     |                     |                    |                      |

|                      |                               | uration Word Mis<br>uration Word Mis   |                        | has occurred<br>has not occurred            | 1                   |                    |                      |

| bit 8                | •                             | t Wake-up from                         |                        |                                             |                     |                    |                      |

|                      | 1 = Fast wak                  | e-up is disabled<br>e-up is enabled    | (lower power           |                                             |                     |                    |                      |

| bit 7                |                               | nal Reset (MCLF                        |                        | ,                                           |                     |                    |                      |

| on r                 |                               | Clear (pin) Rese                       | -                      | ed                                          |                     |                    |                      |

|                      |                               | Clear (pin) Rese                       |                        |                                             |                     |                    |                      |

| bit 6                | SWR: Softwa                   | are RESET (Instru                      | uction) Flag b         | it(1)                                       |                     |                    |                      |

|                      |                               | instruction has to instruction has r   |                        |                                             |                     |                    |                      |

|                      |                               | -                                      | e set or cleare        | ed in software. Se                          | tting one of t      | hese bits in sof   | tware does not       |

|                      | cause a device R              |                                        | (a) (                  |                                             |                     | dis shis d su      |                      |

|                      |                               |                                        |                        | mmed), the retent<br>e SRAM contents        |                     |                    | Id the REIEN         |

|                      |                               |                                        |                        | r mode will add a o<br>or should set this b |                     |                    |                      |

| 4:                   | • •                           | 1:0> Configuration                     | • •                    | L' (unprogrammed                            |                     | •                  | •                    |

|                      |                               | -                                      | onfiguration b         | nite must he set to                         | '01' in order       |                    | have an offect       |

### 5: The BOREN<1:0> (FPOR<1:0>) Configuration bits must be set to '01' in order for SBOREN to have an effect.

## 8.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                              |

#### 8.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## 8.4 Interrupt Control and Status Registers

PIC24FJ256GA705 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON4

- IFS0 through IFS7

- IEC0 through IEC7

- IPC0 through ICP29

- INTTREG

### 8.4.1 INTCON1-INTCON4

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources.

The INTCON2 register controls global interrupt generation, the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

The INTCON4 register contains the Software Generated Hard Trap bit (SGHT) and ECC Double-Bit Error (ECCDBE) trap.

### 8.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal, and is cleared via software.

### 8.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 8.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 8.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 8-2. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IPx bits in the first position of IPC0 (IPC0<2:0>).

### 8.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "CPU with Extended Data Space (EDS)" (DS39732) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 8-3 through Register 8-6 in the following pages.

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

| U-0                                | U-0       | U-0               | U-0                                     | U-0                                | U-0   | U-0   | U-0   |  |

|------------------------------------|-----------|-------------------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| _                                  | _         | —                 |                                         | —                                  | _     | —     | —     |  |

| bit 15                             |           |                   |                                         |                                    |       |       | bit 8 |  |

| U-0                                | U-0       | R/W-0             | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| 0-0                                | 0-0       | R/W-0             | R/ VV-U                                 | TUN                                | -     | R/W-0 | R/W-0 |  |

| —                                  |           |                   |                                         | TUN                                | \$.0> |       |       |  |

| bit 7                              |           |                   |                                         |                                    |       |       | bit 0 |  |

| Legend:                            |           |                   |                                         |                                    |       |       |       |  |

| R = Readable                       | bit       | W = Writable b    | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |           |                   | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |

|                                    |           |                   |                                         |                                    |       |       |       |  |

| bit 15-6                           | Unimpleme | nted: Read as '0  | ,                                       |                                    |       |       |       |  |

| bit 5-0                            | TUN<5:0>: | FRC Oscillator Tu | uning bits                              |                                    |       |       |       |  |

#### 11.5.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-13 through Register 11-31). Each register contains one or two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn/RPIn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

| TABLE 11-6 | SELECTABLE INPUT SOURCES | (MAPS INPUT TO FUNCTION) <sup>(1)</sup> |

|------------|--------------------------|-----------------------------------------|

|            |                          |                                         |

| Input Name                   | Function Name | Register      | Function Mapping<br>Bits |

|------------------------------|---------------|---------------|--------------------------|

| Output Compare Trigger 1     | OCTRIG1       | RPINR0<5:0>   | OCTRIG1R<5:0>            |

| External Interrupt 1         | INT1          | RPINR0<13:8>  | INT1R<5:0>               |

| External Interrupt 2         | INT2          | RPINR1<5:0>   | INT2R<5:0>               |

| External Interrupt 3         | INT3          | RPINR1<13:8>  | INT3R<5:0>               |

| External Interrupt 4         | INT4          | RPINR2<5:0>   | INT4R<5:0>               |

| Output Compare Trigger 2     | OCTRIG2       | RPINR2<13:8>  | OCTRIG2R<5:0>            |

| Timer2 External Clock        | T2CK          | RPINR3<5:0>   | T2CKR<5:0>               |

| Timer3 External Clock        | T3CK          | RPINR3<13:8>  | T3CKR<5:0>               |

| Input Capture 1              | ICM1          | RPINR5<5:0>   | ICM1R<5:0>               |

| Input Capture 2              | ICM2          | RPINR5<13:8>  | ICM2R<5:0>               |

| Input Capture 3              | ICM3          | RPINR6<5:0>   | ICM3R<5:0>               |

| Input Capture 4              | ICM4          | RPINR6<13:8>  | ICM4R<5:0>               |

| Input Capture 1              | IC1           | RPINR7<5:0>   | IC1R<5:0>                |

| Input Capture 2              | IC2           | RPINR7<13:8>  | IC2R<5:0>                |

| Input Capture 3              | IC3           | RPINR8<5:0>   | IC3R<5:0>                |

| Output Compare Fault A       | OCFA          | RPINR11<5:0>  | OCFAR<5:0>               |

| Output Compare Fault B       | OCFB          | RPINR11<13:8> | OCFBR<5:0>               |

| CCP Clock Input A            | TCKIA         | RPINR12<5:0>  | TCKIAR<5:0>              |

| CCP Clock Input B            | TCKIB         | RPINR12<13:8> | TCKIBR<5:0>              |

| UART1 Receive                | U1RX          | RPINR18<5:0>  | U1RXR<5:0>               |

| UART1 Clear-to-Send          | U1CTS         | RPINR18<13:8> | U1CTSR<5:0>              |

| UART2 Receive                | U2RX          | RPINR19<5:0>  | U2RXR<5:0>               |

| UART2 Clear-to-Send          | U2CTS         | RPINR19<13:8> | U2CTSR<5:0>              |

| SPI1 Data Input              | SDI1          | RPINR20<5:0>  | SDI1R<5:0>               |

| SPI1 Clock Input             | SCK1IN        | RPINR20<13:8> | SCK1R<5:0>               |

| SPI1 Slave Select Input      | SS1IN         | RPINR21<5:0>  | SS1R<5:0>                |

| SPI2 Data Input              | SDI2          | RPINR22<5:0>  | SDI2R<5:0>               |

| SPI2 Clock Input             | SCK2IN        | RPINR22<13:8> | SCK2R<5:0>               |

| SPI2 Slave Select Input      | SS2IN         | RPINR23<5:0>  | SS2R<5:0>                |

| Generic Timer External Clock | TxCK          | RPINR23<13:8> | TXCKR<5:0>               |

| CLC Input A                  | CLCINA        | RPINR25<5:0>  | CLCINAR<5:0>             |

| CLC Input B                  | CLCINB        | RPINR25<13:8> | CLCINBR<5:0>             |

| SPI3 Data Input              | SDI3          | RPINR28<5:0>  | SDI3R<5:0>               |

| SPI3 Clock Input             | SCK3IN        | RPINR28<13:8> | SCK3R<5:0>               |

| SPI3 Slave Select Input      | SS3IN         | RPINR29<5:0>  | SS3R<5:0>                |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

| U-0           | U-0   | R/W-1            | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |

|---------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

| —             | —     | IC2R5            | IC2R4 | IC2R3                                   | IC2R2 | IC2R1 | IC2R0 |

| bit 15        |       |                  |       |                                         |       |       | bit 8 |

|               |       |                  |       |                                         |       |       |       |

| U-0           | U-0   | R/W-1            | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |

| —             | —     | IC1R5            | IC1R4 | IC1R3                                   | IC1R2 | IC1R1 | IC1R0 |

| bit 7         |       |                  |       |                                         |       |       | bit 0 |

|               |       |                  |       |                                         |       |       |       |

| Legend:       |       |                  |       |                                         |       |       |       |

| R = Readable  | e bit | W = Writable I   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

#### REGISTER 11-19: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC2R<5:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC1R<5:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 11-20: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC3R5 | IC3R4 | IC3R3 | IC3R2 | IC3R1 | IC3R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 IC3R<5:0>: Assign Input Capture 3 (IC3) to Corresponding RPn or RPIn Pin bits

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | _   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

|--------|-----------|-----|----------|----------|----------|----------|----------|

| ICTRIG | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |     |          |          |          |          | bit 0    |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC32: Cascade Two Input Capture Modules Enable bit (32-bit operation)                                                                                                                     |

|          | <ul> <li>1 = ICx and ICy operate in cascade as a 32-bit module (this bit must be set in both modules)</li> <li>0 = ICx functions independently as a 16-bit module</li> </ul>              |

| bit 7    | ICTRIG: Input Capture x Sync/Trigger Select bit                                                                                                                                           |

|          | <ul> <li>1 = Triggers ICx from the source designated by the SYNCSELx bits</li> <li>0 = Synchronizes ICx with the source designated by the SYNCSELx bits</li> </ul>                        |

| bit 6    | TRIGSTAT: Timer Trigger Status bit                                                                                                                                                        |

|          | <ul> <li>1 = Timer source has been triggered and is running (set in hardware, can be set in software)</li> <li>0 = Timer source has not been triggered and is being held clear</li> </ul> |

| bit 5    | Unimplemented: Read as '0'                                                                                                                                                                |

- **Note 1:** Use these inputs as Trigger sources only and never as Sync sources.

- 2: Never use an Input Capture x module as its own Trigger source by selecting this mode.

| R/W-0         | U-0                                                                                                                                     | R/W-0            | R/W-0          | R/W-0                              | R/W-0          | R/W-0           | R/W-0   |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------------------------|----------------|-----------------|---------|--|--|--|

| CCPON         |                                                                                                                                         | CCPSIDL          | CCPSLP         | TMRSYNC                            | CLKSEL2        | CLKSEL1         | CLKSEL0 |  |  |  |

| bit 15        |                                                                                                                                         |                  |                |                                    |                |                 | bit 8   |  |  |  |

|               |                                                                                                                                         |                  |                |                                    |                |                 |         |  |  |  |

| R/W-0         | R/W-0                                                                                                                                   | R/W-0            | R/W-0          | R/W-0                              | R/W-0          | R/W-0           | R/W-0   |  |  |  |

| TMRPS1        | TMRPS0                                                                                                                                  | T32              | CCSEL          | MOD3                               | MOD2           | MOD1            | MOD0    |  |  |  |

| bit 7         |                                                                                                                                         |                  |                |                                    |                |                 | bit     |  |  |  |

| Legend:       |                                                                                                                                         |                  |                |                                    |                |                 |         |  |  |  |

| R = Readable  | > hit                                                                                                                                   | W = Writable     | bit            | U = Unimplem                       | ented hit read | 1 as '0'        |         |  |  |  |

| -n = Value at |                                                                                                                                         | '1' = Bit is set |                | '0' = Bit is clea                  |                | x = Bit is unkr | nown    |  |  |  |

|               |                                                                                                                                         | 1 Dit lo dot     |                |                                    |                | X Dit lo uniti  |         |  |  |  |

| bit 15        | CCPON: CCF                                                                                                                              | Px Module Enal   | ble bit        |                                    |                |                 |         |  |  |  |

|               | 1 = Module is                                                                                                                           | s enabled with   | an operating m | node specified b                   | y the MOD<3:   | 0> control bits |         |  |  |  |

|               | 0 = Module is                                                                                                                           | s disabled       |                |                                    | -              |                 |         |  |  |  |

| bit 14        | Unimplemen                                                                                                                              | ted: Read as '   | כי             |                                    |                |                 |         |  |  |  |

| bit 13        | CCPSIDL: CO                                                                                                                             | CPx Stop in Idle | e Mode Bit     |                                    |                |                 |         |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                  |                |                                    |                |                 |         |  |  |  |

| L:1 4 0       |                                                                                                                                         | -                |                | de                                 |                |                 |         |  |  |  |

| bit 12        | <b>CCPSLP:</b> CCPx Sleep Mode Enable bit<br>1 = Module continues to operate in Sleep modes                                             |                  |                |                                    |                |                 |         |  |  |  |

|               | 0 = Module does not operate in Sleep modes                                                                                              |                  |                |                                    |                |                 |         |  |  |  |

| bit 11        |                                                                                                                                         | ime Base Cloc    | -              |                                    |                |                 |         |  |  |  |

|               | 1 = Module time base clock is synchronized to the internal system clocks; timing restrictions apply                                     |                  |                |                                    |                |                 |         |  |  |  |

|               | 0 = Module time base clock is not synchronized to the internal system clocks                                                            |                  |                |                                    |                |                 |         |  |  |  |

| bit 10-8      | CLKSEL<2:0>: CCPx Time Base Clock Select bits                                                                                           |                  |                |                                    |                |                 |         |  |  |  |

|               | 111 = TCKIA pin                                                                                                                         |                  |                |                                    |                |                 |         |  |  |  |

|               | 110 = TCKIB pin<br>101 = PLL clock                                                                                                      |                  |                |                                    |                |                 |         |  |  |  |

|               | 100 = 2x peripheral clock                                                                                                               |                  |                |                                    |                |                 |         |  |  |  |

|               | 010 = SOSC clock                                                                                                                        |                  |                |                                    |                |                 |         |  |  |  |

|               | 001 = Reference clock output                                                                                                            |                  |                |                                    |                |                 |         |  |  |  |

|               | 000 = System clock<br>For MCCP1:                                                                                                        |                  |                |                                    |                |                 |         |  |  |  |

|               | 011 = CLC1 output                                                                                                                       |                  |                |                                    |                |                 |         |  |  |  |

|               | For MCCP2:                                                                                                                              |                  |                |                                    |                |                 |         |  |  |  |

|               | 011 = CLC2 o                                                                                                                            | output           |                |                                    |                |                 |         |  |  |  |

| bit 7-6       |                                                                                                                                         | : Time Base Pi   | rescale Select | bits                               |                |                 |         |  |  |  |

|               | 11 = 1:64 Prescaler                                                                                                                     |                  |                |                                    |                |                 |         |  |  |  |

|               | 10 = 1:16 Prescaler<br>01 = 1:4 Prescaler                                                                                               |                  |                |                                    |                |                 |         |  |  |  |

|               | 01 = 1.4 Prescaler                                                                                                                      |                  |                |                                    |                |                 |         |  |  |  |

| bit 5         |                                                                                                                                         | me Base Selec    | t bit          |                                    |                |                 |         |  |  |  |

|               |                                                                                                                                         |                  |                | edge output con<br>edge output con |                |                 |         |  |  |  |

| L:1 /         |                                                                                                                                         |                  |                |                                    | 1              | 1               |         |  |  |  |

| DIL 4         | CCSEL: Capture/Compare Mode Select bit                                                                                                  |                  |                |                                    |                |                 |         |  |  |  |

| bit 4         | -                                                                                                                                       | ture peripheral  |                | t                                  |                |                 |         |  |  |  |

## REGISTER 16-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| SYNC<4:0> | Synchronization Source                            |

|-----------|---------------------------------------------------|

| 11111     | None; Timer with Rollover on CCPxPR Match or FFFh |

| 11110     | Reserved                                          |

| 11101     | Reserved                                          |

| 11100     | CTMU Trigger                                      |

| 11011     | A/D Start Conversion                              |

| 11010     | CMP3 Trigger                                      |

| 11001     | CMP2 Trigger                                      |

| 11000     | CMP1 Trigger                                      |

| 10111     | Reserved                                          |

| 10110     | Reserved                                          |

| 10101     | Reserved                                          |

| 10100     | Reserved                                          |

| 10011     | Reserved                                          |

| 10010     | Reserved                                          |

| 10001     | CLC2 Out                                          |

| 10000     | CLC1 Out                                          |

| 01111     | Reserved                                          |

| 01110     | Reserved                                          |

| 01101     | Reserved                                          |

| 01100     | Reserved                                          |

| 01011     | INT2 Pad                                          |

| 01010     | INT1 Pad                                          |

| 01001     | INT0 Pad                                          |

| 01000     | Reserved                                          |

| 00111     | Reserved                                          |

| 00110     | Reserved                                          |

| 00101     | MCCP4 Sync Out                                    |

| 00100     | MCCP3 Sync Out                                    |

| 00011     | MCCP2 Sync Out                                    |

| 00010     | MCCP1 Sync Out                                    |

| 00001     | MCCPx Sync Out <sup>(1)</sup>                     |

| 00000     | MCCPx Timer Sync Out <sup>(1)</sup>               |

## TABLE 16-5: SYNCHRONIZATION SOURCES

**Note 1:** CCP1 when connected to CCP1, CCP2 when connected to CCP2, etc.

| R/W-0           | R/W-0                                                                                                                                                                                                                                      | U-0               | R/W-0          | U-0                            | U-0              | U-0             | U-0   |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------------------------------|------------------|-----------------|-------|

| PWMRSEN         | ASDGM                                                                                                                                                                                                                                      | —                 | SSDG           | —                              | —                | —               | —     |

| bit 15          |                                                                                                                                                                                                                                            |                   |                |                                |                  |                 | bit 8 |

|                 |                                                                                                                                                                                                                                            |                   |                |                                |                  |                 |       |

| R/W-0           | R/W-0                                                                                                                                                                                                                                      | R/W-0             | R/W-0          | R/W-0                          | R/W-0            | R/W-0           | R/W-0 |

| ASDG7           | ASDG6                                                                                                                                                                                                                                      | ASDG5             | ASDG4          | ASDG3                          | ASDG2            | ASDG1           | ASDG0 |

| bit 7           |                                                                                                                                                                                                                                            |                   |                |                                |                  |                 | bit C |

| Legend:         |                                                                                                                                                                                                                                            |                   |                |                                |                  |                 |       |

| R = Readable    | bit                                                                                                                                                                                                                                        | W = Writable      | bit            | U = Unimplem                   | nented bit, read | d as '0'        |       |

| -n = Value at I | POR                                                                                                                                                                                                                                        | '1' = Bit is set  |                | '0' = Bit is cleared           |                  | x = Bit is unkr | iown  |

| bit 14          |                                                                                                                                                                                                                                            | -                 |                | e to resume PW<br>e Enable bit | M activity on c  | output pins     |       |

| 511 14          | 1 = Waits uni                                                                                                                                                                                                                              | til the next Time | e Base Reset o | or rollover for sh             | utdown to occ    | ur              |       |

| L:1 40          |                                                                                                                                                                                                                                            | n event occurs    | ,              |                                |                  |                 |       |

| bit 13          | -                                                                                                                                                                                                                                          | ted: Read as '    |                |                                |                  |                 |       |

| bit 12          | <ul> <li>SSDG: CCPx Software Shutdown/Gate Control bit</li> <li>1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting o ASDGM bit still applies)</li> <li>0 = Normal module operation</li> </ul> |                   |                |                                |                  |                 |       |

| bit 11-8        | Unimplemen                                                                                                                                                                                                                                 | ted: Read as '    | 0'             |                                |                  |                 |       |

| bit 7-0         | ASDG<7:0>:                                                                                                                                                                                                                                 | CCPx Auto-Sh      | utdown/Gating  | Source Enable                  | e bits           |                 |       |

|                 |                                                                                                                                                                                                                                            | Source n is ena   | hled (see Tabl | a 16-6 for auto-               | shutdown/aati    | na sources)     |       |

## REGISTER 16-3: CCPxCON2L: CCPx CONTROL 2 LOW REGISTERS

#### TABLE 16-6: AUTO-SHUTDOWN SOURCES

| ASDC .7.0 | Auto-Shutdown Source |          |       |       |  |  |  |

|-----------|----------------------|----------|-------|-------|--|--|--|

| ASDG<7:0> | MCCP1                | MCCP2    | МССР3 | MCCP4 |  |  |  |

| 1xxx xxxx | OCFB                 |          |       |       |  |  |  |

| x1xx xxxx | OCFA                 |          |       |       |  |  |  |

| xx1x xxxx | CLC1 CLC2 Not Used   |          |       |       |  |  |  |

| xxx1 xxxx |                      | Not Used |       |       |  |  |  |

| xxxx 1xxx | Not Used             |          |       |       |  |  |  |

| xxxx x1xx | CMP3 Out             |          |       |       |  |  |  |

| xxxx xx1x | CMP2 Out             |          |       |       |  |  |  |

| xxxx xxx1 | CMP1 Out             |          |       |       |  |  |  |

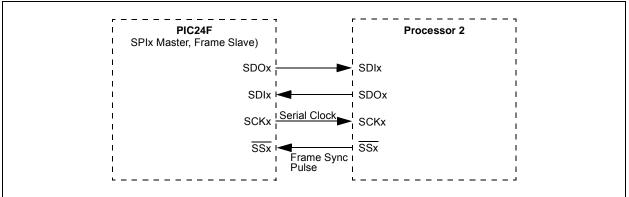

#### FIGURE 17-5: SPIX MASTER, FRAME SLAVE CONNECTION DIAGRAM

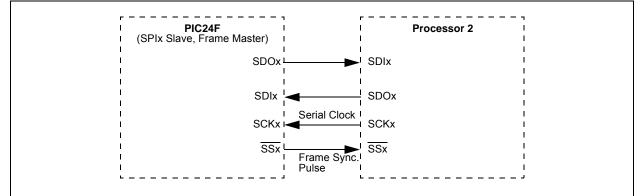

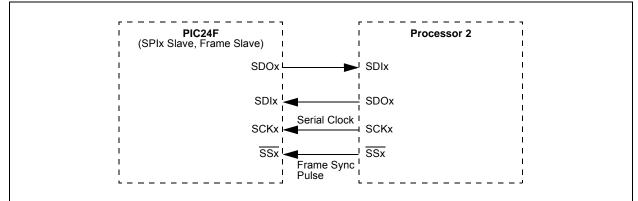

### FIGURE 17-7: SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

### EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

$Baud Rate = \frac{FPB}{(2 * (SPIxBRG + 1))}$ Where: FPB is the Peripheral Bus Clock Frequency.

| R/W-0                 | U-0                          | R/W-0                                                                      | R/W-0                           | R/W-0                 | U-0                       | R/W-0             | R/W-0           |  |  |  |

|-----------------------|------------------------------|----------------------------------------------------------------------------|---------------------------------|-----------------------|---------------------------|-------------------|-----------------|--|--|--|

| UARTEN <sup>(1)</sup> | ) _                          | USIDL                                                                      | IREN <sup>(2)</sup>             | RTSMD                 |                           | UEN1              | UEN0            |  |  |  |

| bit 15                |                              |                                                                            |                                 |                       |                           |                   | bit             |  |  |  |

|                       | DAVA                         |                                                                            | <b>D</b> 444.0                  | D 444 0               | DAMO                      |                   | DANCO           |  |  |  |

| R/W-0, HC             |                              | R/W-0, HC                                                                  | R/W-0                           | R/W-0                 | R/W-0                     | R/W-0             | R/W-0           |  |  |  |

| WAKE                  | LPBACK                       | ABAUD                                                                      | URXINV                          | BRGH                  | PDSEL1                    | PDSEL0            | STSEL           |  |  |  |

| bit 7                 |                              |                                                                            |                                 |                       |                           |                   | bit             |  |  |  |

| Legend:               |                              | HC = Hardwar                                                               | e Clearable bi                  | t                     |                           |                   |                 |  |  |  |

| R = Readal            | ole bit                      | W = Writable b                                                             | bit                             | U = Unimplem          | nented bit, read          | l as '0'          |                 |  |  |  |

| -n = Value a          | at POR                       | '1' = Bit is set                                                           |                                 | '0' = Bit is clea     |                           | x = Bit is unkno  | own             |  |  |  |

|                       |                              |                                                                            |                                 |                       |                           |                   |                 |  |  |  |

| bit 15                | UARTEN: UA                   | ARTx Enable bit                                                            | 1)                              |                       |                           |                   |                 |  |  |  |

|                       | 1 = UARTx is                 | enabled; all UA                                                            | RTx pins are o                  | controlled by UA      | ARTx as define            | d by UEN<1:0>     |                 |  |  |  |

|                       | 0 = UARTx is                 | disabled; all UAF                                                          | RTx pins are co                 | ntrolled by port      | atches, UARTx             | power consump     | tion is minima  |  |  |  |

| bit 14                | Unimplemen                   | ted: Read as '0                                                            | 3                               |                       |                           |                   |                 |  |  |  |

| bit 13                |                              | Tx Stop in Idle N                                                          |                                 |                       |                           |                   |                 |  |  |  |

|                       |                              | ues module ope<br>s module operat                                          |                                 |                       | e mode                    |                   |                 |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup>      | Encoder and De                                                             | coder Enable                    | bit <sup>(2)</sup>    |                           |                   |                 |  |  |  |

|                       |                              | oder and decode                                                            |                                 |                       |                           |                   |                 |  |  |  |

| bit 11                | RTSMD: Mod                   | le Selection for                                                           | UxRTS Pin bit                   |                       |                           |                   |                 |  |  |  |

|                       |                              | in is in Simplex r<br>in is in Flow Cor                                    |                                 |                       |                           |                   |                 |  |  |  |

| bit 10                | Unimplemen                   | ted: Read as '0                                                            | ,                               |                       |                           |                   |                 |  |  |  |