Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 40                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

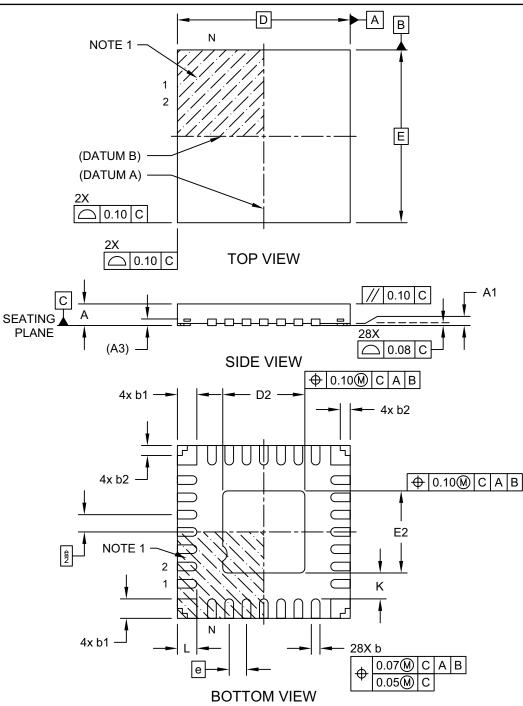

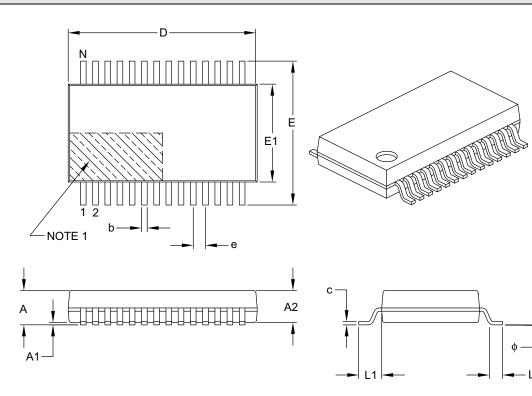

| Package / Case             | 48-TQFP                                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga705-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/ +80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

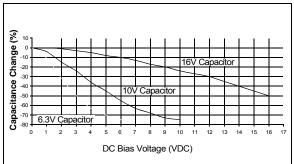

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at a minimum of 16V for the 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

# 2.5 ICSP Pins

The PGCx and PGDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGCx and PGDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" pins (i.e., PGCx/PGDx) programmed into the device match the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

| File Name      | Address           | All Resets | File Name                                      | Address | All Resets |  |  |  |

|----------------|-------------------|------------|------------------------------------------------|---------|------------|--|--|--|

| INPUT CAPTURE  | -                 |            | MULTIPLE OUTPUT CAPTURE/COMPARE/PWM (CONTINUED |         |            |  |  |  |

| IC1CON1        | 0200              | 0000       | CCP1RAH                                        | 0286    | 0000       |  |  |  |

| IC1CON2        | 0202              | 000D       | CCP1RBL                                        | 0288    | 0000       |  |  |  |

| IC1BUF         | 0204              | 0000       | CCP1RBH                                        | 028A    | 0000       |  |  |  |

| IC1TMR         | 0206              | 0000       | CCP1BUFL                                       | 028C    | 0000       |  |  |  |

| IC2CON1        | 0208              | 0000       | CCP1BUFH                                       | 028E    | 0000       |  |  |  |

| IC2CON2        | 020A              | 000D       | CCP2CON1L                                      | 0290    | 0000       |  |  |  |

| IC2BUF         | 020C              | 0000       | CCP2CON1H                                      | 0292    | 0000       |  |  |  |

| IC2TMR         | 020E              | 0000       | CCP2CON2L                                      | 0294    | 0000       |  |  |  |

| IC3CON1        | 0210              | 0000       | CCP2CON2H                                      | 0296    | 0100       |  |  |  |

| IC3CON2        | 0212              | 000D       | CCP2CON3L                                      | 0298    | 0000       |  |  |  |

| IC3BUF         | 0214              | 0000       | CCP2CON3H                                      | 029A    | 0000       |  |  |  |

| IC3TMR         | 0216              | 0000       | CCP2STATL                                      | 029C    | 00x0       |  |  |  |

| OUTPUT COMPAR  |                   |            | CCP2STATH                                      | 029E    | 0000       |  |  |  |

| OC1CON1        | 0230              | 0000       | CCP2TMRL                                       | 02A0    | 0000       |  |  |  |

| OC1CON2        | 0232              | 000C       | CCP2TMRH                                       | 02A2    | 0000       |  |  |  |

| OC1RS          | 0234              | xxxx       | CCP2PRL                                        | 02A4    | FFFF       |  |  |  |

| OC1R           | 0236              | xxxx       | CCP2PRH                                        | 02A6    | FFFF       |  |  |  |

| OC1TMR         | 0238              | xxxx       | CCP2RAL                                        | 02A8    | 0000       |  |  |  |

| OC2CON1        | 023A              | 0000       | CCP2RAH                                        | 02AA    | 0000       |  |  |  |

| OC2CON2        | 023C              | 000C       | CCP2RBL                                        | 02AC    | 0000       |  |  |  |

| OC2RS          | 023E              | xxxx       | CCP2RBH                                        | 02AE    | 0000       |  |  |  |

| OC2R           | 0240              | xxxx       | CCP2BUFL                                       | 02B0    | 0000       |  |  |  |

| OC2TMR         | 0242              | xxxx       | CCP2BUFH                                       | 02B2    | 0000       |  |  |  |

| OC3CON1        | 0244              | 0000       | CCP3CON1L                                      | 02B4    | 0000       |  |  |  |

| OC3CON2        | 0246              | 000C       | CCP3CON1H                                      | 02B6    | 0000       |  |  |  |

| OC3RS          | 0248              | xxxx       | CCP3CON2L                                      | 02B8    | 0000       |  |  |  |

| OC3R           | 024A              | xxxx       | CCP3CON2H                                      | 02BA    | 0100       |  |  |  |

| OC3TMR         | 024C              | xxxx       | CCP3CON3L                                      | 02BC    | 0000       |  |  |  |

| MULTIPLE OUTPU | T CAPTURE/COMPARE |            | CCP3CON3H                                      | 02BE    | 0000       |  |  |  |

| CCP1CON1L      | 026C              | 0000       | CCP3STATL                                      | 02C0    | 00x0       |  |  |  |

| CCP1CON1H      | 026E              | 0000       | CCP3STATH                                      | 02C2    | 0000       |  |  |  |

| CCP1CON2L      | 0270              | 0000       | CCP3TMRL                                       | 02C4    | 0000       |  |  |  |

| CCP1CON2H      | 0272              | 0100       | CCP3TMRH                                       | 02C6    | 0000       |  |  |  |

| CCP1CON3L      | 0274              | 0000       | CCP3PRL                                        | 02C8    | FFFF       |  |  |  |

| CCP1CON3H      | 0276              | 0000       | CCP3PRH                                        | 02CA    | FFFF       |  |  |  |

| CCP1STATL      | 0278              | 00x0       | CCP3RAL                                        | 02CC    | 0000       |  |  |  |

| CCP1STATH      | 027A              | 0000       | CCP3RAH                                        | 02CE    | 0000       |  |  |  |

| CCP1TMRL       | 027C              | 0000       | CCP3RBL                                        | 02D0    | 0000       |  |  |  |

| CCP1TMRH       | 027E              | 0000       | CCP3RBH                                        | 02D2    | 0000       |  |  |  |

| CCP1PRL        | 0280              | FFFF       | CCP3BUFL                                       | 02D4    | 0000       |  |  |  |

| CCP1PRH        | 0282              | FFFF       | CCP3BUFH                                       | 02D6    | 0000       |  |  |  |

| CCP1RAL        | 0284              | 0000       |                                                |         | 1 2000     |  |  |  |

TABLE 4-6: SFR MAP: 0200h BLOCK

**Legend:** x = undefined. Reset values are shown in hexadecimal.

| DSRPAG<br>(Data Space Read<br>Register) | DSWPAG<br>(Data Space Write<br>Register) | Source/Destination<br>Address while<br>Indirect<br>Addressing | 24-Bit EA<br>Pointing to EDS | Comment                           |  |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------|-----------------------------------|--|

| x <sup>(1)</sup>                        | х <sup>(1)</sup>                         | 0000h to 1FFFh                                                | 000000h to<br>001FFFh        | Near Data Space <sup>(2)</sup>    |  |

|                                         |                                          | 2000h to 7FFFh                                                | 002000h to<br>007FFFh        |                                   |  |

| 001h                                    | 001h                                     |                                                               | 008000h to<br>00FFFEh        |                                   |  |

| 002h                                    | 002h                                     |                                                               | 010000h to<br>017FFEh        |                                   |  |

| 003h<br>•                               | 003h<br>•                                |                                                               | 018000h to<br>0187FEh        | EPMP Memory Space                 |  |

| •                                       | •                                        | 8000h to FFFFh                                                | •                            |                                   |  |

| •                                       | •                                        |                                                               | •                            |                                   |  |

| •                                       |                                          |                                                               | •                            |                                   |  |

| 1FFh                                    | 1FFh                                     |                                                               | FF8000h to<br>FFFFFEh        |                                   |  |

| 000h                                    | 000h                                     |                                                               | Invalid Address              | Address Error Trap <sup>(3)</sup> |  |

#### TABLE 4-13: EDS MEMORY ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

Note 1: If the source/destination address is below 8000h, the DSRPAG and DSWPAG registers are not considered.

2: This Data Space can also be accessed by Direct Addressing.

**3:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

#### 4.2.6 SOFTWARE STACK

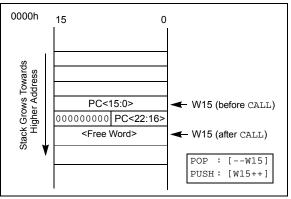

Apart from its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value register (SPLIM), associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be wordaligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 4-6: CALL STACK FRAME

| R/W-0  | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| DMAEN  | —   | —   | —   | _   | —   | —   | —      |

| bit 15 |     |     |     |     |     |     | bit 8  |

|        |     |     |     |     |     |     |        |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| —      | —   | —   | —   |     |     | _   | PRSSEL |

| bit 7  |     |     |     |     |     |     | bit 0  |

|        |     |     |     |     |     |     |        |

# REGISTER 5-1: DMACON: DMA ENGINE CONTROL REGISTER

# Legend:

| Legend:           |                                                              |                      |                    |  |  |

|-------------------|--------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | adable bit W = Writable bit U = Unimplemented bit, read as ' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                             | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15 DMAEN: DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round-robin scheme

0 = Fixed priority scheme

# TABLE 10-2: PERIPHERAL MODULE DISABLE REGISTER SUMMARY

| Register | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1     | _      | _      | T3MD   | T2MD   | T1MD   |        | _      | _     | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | _      | _      | ADCMD  | 0000          |

| PMD2     | _      |        | _      | -      | _      | IC3MD  | IC2MD  | IC1MD | _      | _     | _      |        | _      | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3     | _      |        | _      | -      | _      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _     | _      |        | _      | _      | I2C2MD | —      | 0000          |

| PMD4     | _      |        | _      | -      | _      | _      | _      | _     | _      | _     | _      |        | REFOMD | CTMUMD | LVDMD  | —      | 0000          |

| PMD5     | _      |        | _      | -      | _      | _      | _      | _     | _      | _     | _      |        | CCP4MD | CCP3MD | CCP2MD | CCP1MD | 0000          |

| PMD6     | _      |        | _      | -      | _      | _      | _      | _     | _      | _     | _      |        | _      | -      | _      | SPI3MD | 0000          |

| PMD7     | _      |        | _      | -      | _      | _      | _      | _     | _      | _     | DMA1MD | DMA0MD | _      | -      | _      | —      | 0000          |

| PMD8     | —      | _      | —      | _      | _      | _      | -      | _     | —      | —     | —      | —      | CLC2MD | CLC1MD | —      | —      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 11.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 11.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

# 11.2 Configuring Analog Port Pins (ANSx)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANSx bits, which decide if the pin function should be analog or digital. Refer to Table 11-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORTx register, all pins configured as analog input channels will read as cleared (a low level).

# 11.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Most input pins are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. However, several pins can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided.

Table 11-2 summarizes the different voltage tolerances. For more information, refer to **Section 32.0 "Electrical Characteristics"** for more details.

## TABLE 11-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

## TABLE 11-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin        | Tolerated Input | Description                              |

|--------------------|-----------------|------------------------------------------|

| PORTB<11:10,8:5>   | 5.5V            | Tolerates input levels above VDD; useful |

| PORTC<9:6>         | 5.5V            | for most standard logic.                 |

| PORTA<14:7,4:0>    |                 |                                          |

| PORTB<15:12,9,4:0> | VDD             | Only VDD input levels are tolerated.     |

| PORTC<5:0>         |                 |                                          |

| U-0                               | U-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0            |  |

|-----------------------------------|-----|------------------|-------|------------------------------------|-------|-----------------|------------------|--|

| _                                 | —   | RP5R5            | RP5R4 | RP5R3                              | RP5R2 | RP5R1           | RP5R0            |  |

| bit 15                            |     |                  |       |                                    |       |                 | bit 8            |  |

|                                   |     |                  |       |                                    |       |                 |                  |  |

| U-0                               | U-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0            |  |

| _                                 | —   | RP4R5            | RP4R4 | RP4R3                              | RP4R2 | RP4R1           | RP4R0            |  |

| bit 7                             |     |                  |       |                                    |       |                 | bit 0            |  |

|                                   |     |                  |       |                                    |       |                 |                  |  |

| Legend:                           |     |                  |       |                                    |       |                 |                  |  |

| R = Readable bit W = Writable bit |     |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |                  |  |

| -n = Value at                     | POR | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | = Bit is unknown |  |

# REGISTER 11-34: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

- bit 13-8**RP5R<5:0>:** RP5 Output Pin Mapping bits<br/>Peripheral Output Number n is assigned to pin, RP5 (see Table 11-7 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

- bit 5-0 **RP4R<5:0>:** RP4 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP4 (see Table 11-7 for peripheral function numbers).

# REGISTER 11-35: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|

| R = Readable                       | e bit | W = Writable I | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |

|                                    |       |                |       |                                         |       |       | Sit 0 |  |

| bit 7                              |       |                |       | 1                                       |       |       | bit 0 |  |

| _                                  | —     | RP6R5          | RP6R4 | RP6R3                                   | RP6R2 | RP6R1 | RP6R0 |  |

| U-0                                | U-0   | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |

|                                    | _     | RP7R5          | RP7R4 | RP7R3                                   | RP7R2 | RP7R1 | RP7R0 |  |

| U-0                                | U-0   | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP7R<5:0>:** RP7 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP7 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP6R<5:0>:** RP6 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP6 (see Table 11-7 for peripheral function numbers).

# 13.0 TIMER2/3

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Timers"** (DS39704), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Timer2/3 module is a 32-bit timer, which can also be configured as independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 can operate in three modes:

- Two Independent 16-Bit Timers with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- A/D Event Trigger (on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode)

Individually, all of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D event trigger. This trigger is implemented only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON is shown in generic form in Register 13-1; T3CON is shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 is the least significant word; Timer3 is the most significant word of the 32-bit timer.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bits are used for setup and control. Timer2 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags. To configure Timer2/3 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TyCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- Load the timer period value. PR3 will contain the most significant word (msw) of the value, while PR2 contains the least significant word (lsw).

- 5. If interrupts are required, set the interrupt enable bit, T3IE. Use the priority bits, T3IP<2:0>, to set the interrupt priority. Note that while Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2>. TMR3 always contains the most significant word of the count, while TMR2 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit (T2CON<3>).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 11.5 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON (TxCON<15> = 1) bit.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 11111 = Not used

- 11110 = Not used 11101 = Not used 11100 = CTMU trigger<sup>(1)</sup> 11011 = A/D interrupt<sup>(1)</sup>

- 11010 = CMP3 trigger<sup>(1)</sup>

- 11001 = CMP2 trigger<sup>(1)</sup>

- 11000 = CMP1 trigger<sup>(1)</sup>

- 10111 = Not used

- 10110 = MCCP4 IC/OC interrupt

- 10101 = MCCP3 IC/OC interrupt

- 10100 = MCCP2 IC/OC interrupt

- 10011 = MCCP1 IC/OC interrupt

- 10010 = IC3 interrupt<sup>(2)</sup>

- 10001 = IC2 interrupt<sup>(2)</sup>

- 10000 = IC1 interrupt<sup>(2)</sup>

- 01111 = Not used

- 01110 = Not used

- 01101 = Timer3 match event

- 01100 = Timer2 match event

- 01011 = Timer1 match event

- 01010 = Not used

- 01001 = Not used

- 01000 = Not used

- 00111 = MCCP4 Sync/Trigger out

- 00110 = MCCP3 Sync/Trigger out

- 00101 = MCCP2 Sync/Trigger out

- 00100 = MCCP1 Sync/Trigger out

- 00011 = OC3 Sync/Trigger out

- 00010 = OC2 Sync/Trigger out

- 00001 = OC1 Sync/Trigger out

- 00000 **= Off**

- Note 1: Use these inputs as Trigger sources only and never as Sync sources.

- 2: Never use an Input Capture x module as its own Trigger source by selecting this mode.

## **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is only cleared by software

bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on  $OCx^{(2)}$

- 110 = Edge-Aligned PWM mode on  $OCx^{(2)}$

- 101 = Double Compare Continuous Pulse mode: Initializes the OCx pin low; toggles the OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes the OCx pin low; toggles the OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low; compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- 2: The Fault input enable and Fault status bits are valid when OCM<2:0> = 111 or 110.

- 3: The Comparator 1 output controls the OC1-OC3 channels.

- 4: The OCFA/OCFB Fault input must also be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

# 16.2 General Purpose Timer

Timer mode is selected when CCSEL = 0 and MOD<3:0> = 0000. The timer can function as a 32-bit timer or a dual 16-bit timer, depending on the setting of the T32 bit (Table 16-1).

| T32<br>(CCPxCON1L<5>) | Operating Mode           |  |  |  |  |

|-----------------------|--------------------------|--|--|--|--|

| 0                     | Dual Timer Mode (16-bit) |  |  |  |  |

| 1                     | Timer Mode (32-bit)      |  |  |  |  |

TABLE 16-1: TIMER OPERATION MODE

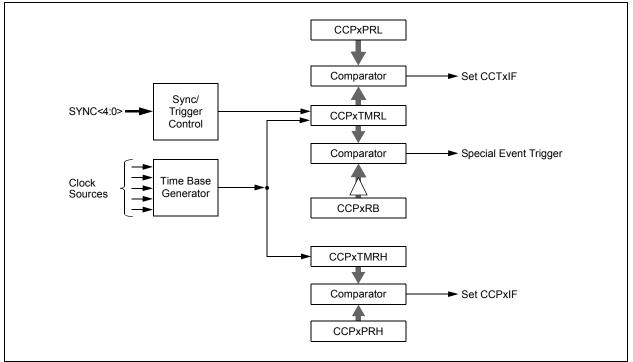

Dual 16-Bit Timer mode provides a simple timer function with two independent 16-bit timer/counters. The primary timer uses the CCPxTMRL and CCPxPRL registers. Only the primary timer can interact with other modules on the device. It generates the MCCPx Sync out signals for use by other MCCPx modules. It can also use the SYNC<4:0> bits signal generated by other modules.

The secondary timer uses the CCPxTMRH and CCPxPRH registers. It is intended to be used only as a periodic interrupt source for scheduling CPU events. It does not generate an output Sync/Trigger signal like the primary time base. In Dual Timer mode, the Timer Period High register, CCPxPRH, generates the MCCPx compare event (CCPxIF) used by many other modules on the device.

The 32-Bit Timer mode uses the CCPxTMRL and CCPxTMRH registers, together, as a single 32-bit timer. When CCPxTMRL overflows, CCPxTMRH increments

FIGURE 16-3: DUAL 16-BIT TIMER MODE

by one. This mode provides a simple timer function when it is important to track long time periods. Note that the T32 bit (CCPxCON1L<5>) should be set before the CCPxTMRL or CCPxPRH registers are written to initialize the 32-bit timer.

## 16.2.1 SYNC AND TRIGGER OPERATION

In both 16-bit and 32-bit modes, the timer can also function in either Synchronization ("Sync") or Trigger mode operation. Both use the SYNC<4:0> bits (CCPxCON1H<4:0>) to determine the input signal source. The difference is how that signal affects the timer.

In Sync operation, the Timer Reset or clear occurs when the input selected by SYNC<4:0> is asserted. The timer immediately begins to count again from zero unless it is held for some other reason. Sync operation is used whenever the TRIGEN bit (CCPxCON1H<7>) is cleared. The SYNC<4:0> bits can have any value except '11111'.

In Trigger mode operation, the timer is held in Reset until the input selected by SYNC<4:0> is asserted; when it occurs, the timer starts counting. Trigger operation is used whenever the TRIGEN bit is set. In Trigger mode, the timer will continue running after a trigger event as long as the CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG, the TRCLR bit (CCPxSTATL<5>) must be set to clear the trigger event, reset the timer and hold it at zero until another trigger event occurs. On PIC24FJ256GA705 family devices, Trigger mode operation can only be used when the system clock is the time base source (CLKSEL<2:0> = 000).

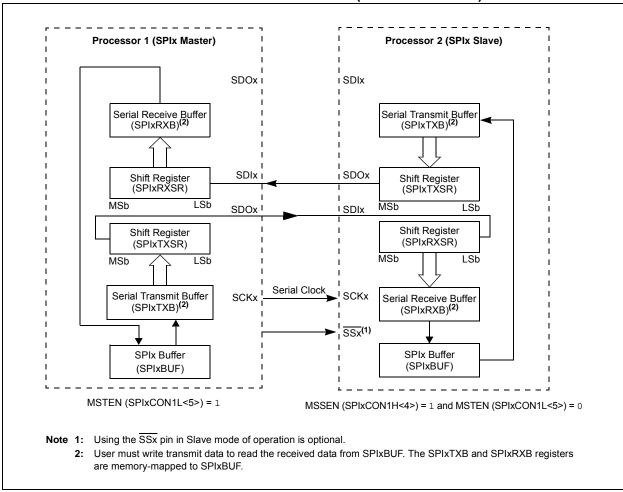

# 17.4 SPI Control Registers

# REGISTER 17-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| R/W-0               | U-0                                                                                                                                     | R/W-0                                                                                                                                                         | R/W-0           | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-------------------------|----------------|--------------------|--|--|--|--|

| SPIEN               |                                                                                                                                         | SPISIDL                                                                                                                                                       | DISSDO          | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP            | CKE <sup>(1)</sup> |  |  |  |  |

| bit 15              |                                                                                                                                         |                                                                                                                                                               | I               | 1                       | 1 1                     |                | bit 8              |  |  |  |  |

|                     |                                                                                                                                         |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| R/W-0               | R/W-0                                                                                                                                   | R/W-0                                                                                                                                                         | R/W-0           | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                     | MSTEN                                                                                                                                                         | DISSDI          | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE          | ENHBUF             |  |  |  |  |

| bit 7               |                                                                                                                                         |                                                                                                                                                               |                 |                         |                         |                | bit C              |  |  |  |  |

| Legend:             |                                                                                                                                         |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| R = Readab          | le bit                                                                                                                                  | W = Writable                                                                                                                                                  | bit             | U = Unimpler            | nented bit, read        | as '0'         |                    |  |  |  |  |

| -n = Value a        |                                                                                                                                         | '1' = Bit is set                                                                                                                                              |                 | '0' = Bit is clea       |                         | x = Bit is unk | nown               |  |  |  |  |

|                     |                                                                                                                                         |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| bit 15              | SPIEN: SPIX (                                                                                                                           | On bit                                                                                                                                                        |                 |                         |                         |                |                    |  |  |  |  |

|                     | 1 = Enables n                                                                                                                           |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

|                     | <ul> <li>0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR<br/>modifications</li> </ul> |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| bit 14              | Unimplement                                                                                                                             | ed: Read as '                                                                                                                                                 | )'              |                         |                         |                |                    |  |  |  |  |

| bit 13              | SPISIDL: SPI                                                                                                                            | x Stop in Idle N                                                                                                                                              | lode bit        |                         |                         |                |                    |  |  |  |  |

|                     | 1 = Halts in Cl                                                                                                                         | PU Idle mode                                                                                                                                                  |                 |                         |                         |                |                    |  |  |  |  |

|                     | 0 = Continues to operate in CPU Idle mode                                                                                               |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| bit 12              | DISSDO: Disable SDOx Output Port bit                                                                                                    |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

|                     | 1 = SDOx pin is not used by the module; pin is controlled by the port function                                                          |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

|                     | 0 = SDOx pin                                                                                                                            |                                                                                                                                                               |                 | 4)                      |                         |                |                    |  |  |  |  |

| bit 11-10           | MODE<32,16                                                                                                                              | Serial Word                                                                                                                                                   | Length bits(',  | -,                      |                         |                |                    |  |  |  |  |

|                     | <u>AUDEN = 0:</u><br>MODE32                                                                                                             | 2 MODE16                                                                                                                                                      | COMMUN          |                         |                         |                |                    |  |  |  |  |

|                     | 1                                                                                                                                       | x                                                                                                                                                             | 32-Bit          |                         |                         |                |                    |  |  |  |  |

|                     | 0                                                                                                                                       | 1                                                                                                                                                             | 16-Bit          |                         |                         |                |                    |  |  |  |  |

|                     | 0                                                                                                                                       | 0                                                                                                                                                             | 8-Bit           |                         |                         |                |                    |  |  |  |  |

|                     | AUDEN = 1:                                                                                                                              |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

|                     | MODE32                                                                                                                                  | 2 MODE16                                                                                                                                                      | COMMUN          |                         |                         |                |                    |  |  |  |  |

|                     | 1                                                                                                                                       | 1                                                                                                                                                             |                 |                         | 2-Bit Channel/6         |                |                    |  |  |  |  |

|                     |                                                                                                                                         | 1         0         32-Bit Data, 32-Bit FIFO, 32-Bit Channel/64-Bit Frame           0         1         16-Bit Data, 16-Bit FIFO, 32-Bit Channel/64-Bit Frame |                 |                         |                         |                |                    |  |  |  |  |

|                     | 0                                                                                                                                       | 1                                                                                                                                                             |                 |                         |                         |                |                    |  |  |  |  |

| bit 9               | 0 0 16-Bit Data, 16-Bit FIFO, 16-Bit Channel/32-Bit Frame<br>SMP: SPIx Data Input Sample Phase bit                                      |                                                                                                                                                               |                 |                         |                         |                |                    |  |  |  |  |

| bit 9               | Master Mode:                                                                                                                            |                                                                                                                                                               | ie i nase bit   |                         |                         |                |                    |  |  |  |  |

|                     | 1 = Input data                                                                                                                          | is sampled at                                                                                                                                                 | the end of dat  | ta output time          |                         |                |                    |  |  |  |  |

|                     |                                                                                                                                         | •                                                                                                                                                             |                 | data output time        | 9                       |                |                    |  |  |  |  |

|                     | Slave Mode:                                                                                                                             | •                                                                                                                                                             |                 |                         |                         |                |                    |  |  |  |  |

|                     |                                                                                                                                         | lways sampled                                                                                                                                                 | l at the middle | e of data output        | time, regardless        | of the SMP     | setting.           |  |  |  |  |

| Note 1: W           | Vhen AUDEN = 1                                                                                                                          | , this module f                                                                                                                                               | unctions as if  | CKE = 0, regard         | dless of its actua      | al value.      |                    |  |  |  |  |

| <b>2</b> : V        | hen FRMEN = 1                                                                                                                           | , SSEN is not                                                                                                                                                 | used.           |                         |                         |                |                    |  |  |  |  |

| 3: N                | ICLKEN can only                                                                                                                         | v be written wh                                                                                                                                               | en the SPIEN    | bit = 0.                |                         |                |                    |  |  |  |  |

| <b>4:</b> T         | his channel is no                                                                                                                       | t meaningful fo                                                                                                                                               | or DSP/PCM r    | node as I RC fo         | llows the FRMS          | YPW bit        |                    |  |  |  |  |

4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

# 21.3.2 RTCVAL REGISTER MAPPINGS

# REGISTER 21-4: RTCCON2H: RTCC CONTROL REGISTER 2 (HIGH)<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-------|-------|-------|-------|-------|-------|-------|

|         |       |       | DIV<  | 15:8> |       |       |       |

| bit 15  |       |       |       |       |       |       | bit 8 |

|         |       |       |       |       |       |       |       |

| R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|         |       |       | DIV   | <7:0> |       |       |       |

| bit 7   |       |       |       |       |       |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

|         |       |       |       |       |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 DIV<15:0>: Clock Divide bits

Sets the period of the clock divider counter; value should cause a nominal 1/2 second underflow.

**Note 1:** A write to this register is only allowed when WRLOCK = 1.

# **REGISTER 29-6: FWDT CONFIGURATION REGISTER (CONTINUED)**

- bit 3-0 WDTPS<3:0>: Watchdog Timer Postscale Select bits 1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 = 1:512 1000 = 1:256 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16

- 0011 = 1:8 0010 = 1:4

- 0001 = 1:2

- 0000 = 1:1

| Assembly<br>Mnemonic |       | Assembly Syntax       | Description                                                                                                                                                                                                         | # of<br>Words                                                                                                                                                                                                                                                                                                                              | # of<br>Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Status Flags<br>Affected |

|----------------------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| ADD                  | ADD   | f                     | f = f + WREG                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADD   | f,WREG                | WREG = f + WREG                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADD   | #lit10,Wn             | Wd = lit10 + Wd                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADD   | Wb,Ws,Wd              | Wd = Wb + Ws                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADD   | Wb,#lit5,Wd           | Wd = Wb + lit5                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

| ADDC                 | ADDC  | f                     | f = f + WREG + (C)                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADDC  | f,WREG                | WREG = f + WREG + (C)                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADDC  | #lit10,Wn             | Wd = lit10 + Wd + (C)                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,Ws,Wd              | Wd = Wb + Ws + (C)                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

|                      | ADDC  | Wb,#lit5,Wd           | Wd = Wb + lit5 + (C)                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C, DC, N, OV, Z          |

| AND                  | AND   | f                     | f = f .AND. WREG                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N, Z                     |