Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | · ·                                                                            |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga702-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

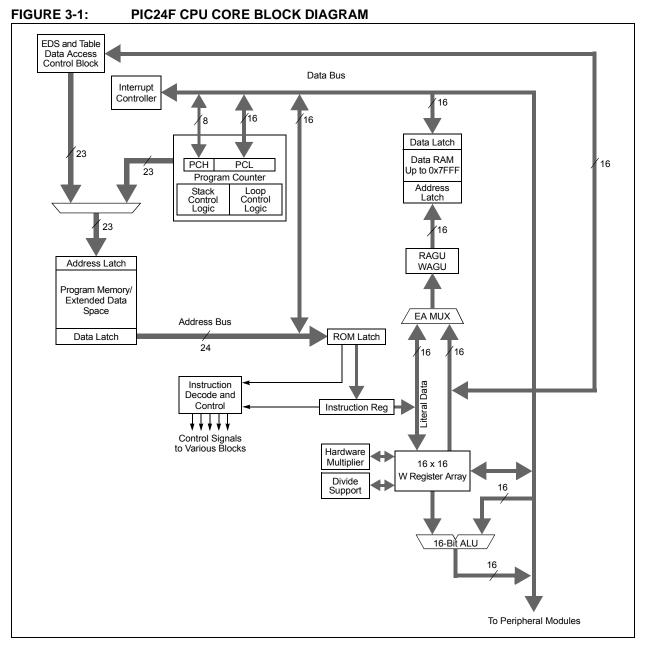

| TABLE 3-1: CPU CORE REGISTER |

|------------------------------|

|------------------------------|

| Register(s) Name | Description                        |  |

|------------------|------------------------------------|--|

| W0 through W15   | Working Register Array             |  |

| PC               | 23-Bit Program Counter             |  |

| SR               | ALU STATUS Register                |  |

| SPLIM            | Stack Pointer Limit Value Register |  |

| TBLPAG           | Table Memory Page Address Register |  |

| RCOUNT           | REPEAT Loop Counter Register       |  |

| CORCON           | CPU Control Register               |  |

| DISICNT          | Disable Interrupt Count Register   |  |

| DSRPAG           | Data Space Read Page Register      |  |

| DSWPAG           | Data Space Write Page Register     |  |

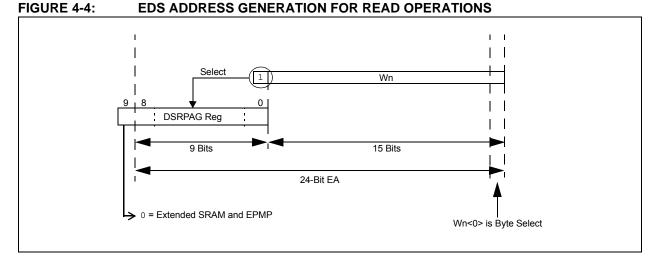

### 4.2.5.1 Data Read from EDS

In order to read the data from the EDS space, first, an Address Pointer is set up by loading the required EDS page number into the DSRPAG register and assigning the offset address to one of the W registers. Once the above assignment is done, the EDS window is enabled by setting bit 15 of the Working register which is assigned with the offset address; then, the contents of the pointed EDS location can be read.

Figure 4-4 illustrates how the EDS space address is generated for read operations.

When the Most Significant bit (MSb) of EA is '1' and DSRPAG<9> = 0, the lower 9 bits of DSRPAG are concatenated to the lower 15 bits of EA to form a 24-bit EDS space address for read operations.

Example 4-1 shows how to read a byte, word and double word from EDS.

Note: All read operations from EDS space have an overhead of one instruction cycle. Therefore, a minimum of two instruction cycles are required to complete an EDS read. EDS reads under the REPEAT instruction; the first two accesses take three cycles and the subsequent accesses take one cycle.

EXAMPLE 4-1: EDS READ CODE IN ASSEMBLY ; Set the EDS page from where the data to be read mov #0x0002, w0 w0, DSRPAG ;page 2 is selected for read mov #0x0800, w1 ;select the location (0x800) to be read mov bset wl, #15 ;set the MSB of the base address, enable EDS mode ;Read a byte from the selected location mov.b [w1++], w2 ;read Low byte mov.b [w1++], w3 ;read High byte ;Read a word from the selected location mov [w1], w2 ; ;Read Double - word from the selected location mov.d [w1], w2 ;two word read, stored in w2 and w3

| <b>TABLE 8-2:</b> | INTERRUPT VECTOR DETAILS (CONTINUED) |

|-------------------|--------------------------------------|

|-------------------|--------------------------------------|

|                                     | IRQ |             | Interrupt Bit Location |          |                 |  |

|-------------------------------------|-----|-------------|------------------------|----------|-----------------|--|

| Interrupt Source                    | #   | IVT Address | Flag                   | Enable   | Priority        |  |

| PMP – Parallel Master Port          | 45  | 00006Eh     | IFS2<13>               | IEC2<13> | PMPInterrupt    |  |

| DMA4 – Direct Memory Access 4       | 46  | 000070h     | IFS2<14>               | IEC2<14> | DMA4Interrupt   |  |

|                                     | 47  | —           | _                      | _        | _               |  |

|                                     | 48  | _           | _                      | _        | _               |  |

| SI2C2 – I2C2 Slave Events           | 49  | 000076h     | IFS3<1>                | IEC3<1>  | SI2C2Interrupt  |  |

| MI2C2 – I2C2 Master Events          | 50  | 000078h     | IFS3<2>                | IEC3<2>  | MI2C2Interrupt  |  |

| _                                   | 51  | _           |                        | _        |                 |  |

|                                     | 52  | _           |                        | _        |                 |  |

| INT3 – External Interrupt 3         | 53  | 00007Eh     | IFS3<5>                | IEC3<5>  | INT3Interrupt   |  |

| INT4 – External Interrupt 4         | 54  | 000080h     | IFS3<6>                | IEC3<6>  | INT4Interrupt   |  |

|                                     | 55  | _           |                        | _        | _               |  |

|                                     | 56  | _           | _                      | _        | _               |  |

|                                     | 57  | _           |                        | _        | _               |  |

| SPI1RX – SPI1 Receive Done          | 58  | 000088h     | IFS3<10>               | IEC3<10> | SPI1RXInterrupt |  |

| SPI2RX – SPI2 Receive Done          | 59  | 00008Ah     | IFS3<11>               | IEC3<11> | SPI2RXInterrupt |  |

| SPI3RX – SPI3 Receive Done          | 60  | 00008Ch     | IFS3<12>               | IEC3<12> | SPI3RXInterrupt |  |

| DMA5 – Direct Memory Access 5       | 61  | 00008Eh     | IFS3<13>               | IEC3<13> | DMA5Interrupt   |  |

| RTCC – Real-Time Clock and Calendar | 62  | 000090h     | IFS3<14>               | IEC3<14> | RTCCInterrupt   |  |

| CCP1 – Capture/Compare 1            | 63  | 000092h     | IFS3<15>               | IEC3<15> | CCP1Interrupt   |  |

| CCP2 – Capture/Compare 2            | 64  | 000094h     | IFS4<0>                | IEC4<0>  | CCP2Interrupt   |  |

| U1E – UART1 Error                   | 65  | 000096h     | IFS4<1>                | IEC4<1>  | U1EInterrupt    |  |

| U2E – UART2 Error                   | 66  | 000098h     | IFS4<2>                | IEC4<2>  | U2EInterrupt    |  |

| CRC – Cyclic Redundancy Check       | 67  | 00009Ah     | IFS4<3>                | IEC4<3>  | CRCInterrupt    |  |

|                                     | 68  | _           | _                      | _        | _               |  |

| _                                   | 69  | _           |                        | _        | _               |  |

|                                     | 70  | _           |                        | _        | _               |  |

| _                                   | 71  | _           | _                      | _        | _               |  |

| HLVD – High/Low-Voltage Detect      | 72  | 0000A4h     | IFS4<8>                | IEC4<8>  | HLVDInterrupt   |  |

|                                     | 73  | —           | _                      | _        | _               |  |

|                                     | 74  | —           | _                      | _        | _               |  |

| _                                   | 75  | _           | _                      | _        | _               |  |

|                                     | 76  | —           | _                      | _        | _               |  |

| CTMU – Interrupt                    | 77  | 0000AEh     | IFS4<13>               | IEC4<13> | CTMUInterrupt   |  |

|                                     | 78  | _           | _                      | _        | _               |  |

|                                     | 79  | —           | _                      | —        | _               |  |

|                                     | 80  | _           | _                      | _        | —               |  |

|                                     | 81  | l _         | _                      | _        | —               |  |

|                                     | 82  | —           | —                      | —        | _               |  |

|                                     | 83  | _           | _                      | _        | _               |  |

| U-0          | R-x <sup>(2)</sup>                     | R-x <sup>(2)</sup>                               | R-x <sup>(2)</sup>         | U-0                                  | R/W-x <sup>(2)</sup>          | R/W-x <sup>(2)</sup> | R/W-x <sup>(2)</sup> |

|--------------|----------------------------------------|--------------------------------------------------|----------------------------|--------------------------------------|-------------------------------|----------------------|----------------------|

| _            | COSC2                                  | COSC1                                            | COSC0                      | _                                    | NOSC2                         | NOSC1                | NOSC0                |

| oit 15       |                                        |                                                  |                            |                                      |                               |                      | bit 8                |

| R/W-0        | R/W-0                                  | R-0 <sup>(4)</sup>                               | U-0                        | R/CO-0                               | R/W-0                         | R/W-0                | R/W-0                |

| CLKLOCK      | (2)                                    | LOCK                                             |                            | CF                                   | POSCEN                        | SOSCEN               | OSWEN                |

| bit 7        | IOLOOK                                 | LOOK                                             |                            | 0                                    | TOODEN                        | OCCULIN              | bit C                |

|              |                                        |                                                  |                            |                                      |                               |                      |                      |

| Legend:      |                                        | CO = Clearal                                     | ole Only bit               |                                      |                               |                      |                      |

| R = Readal   |                                        | W = Writable                                     |                            | •                                    | nented bit, read              | l as '0'             |                      |

| -n = Value a | at POR                                 | '1' = Bit is set                                 |                            | '0' = Bit is cle                     | ared                          | x = Bit is unkn      | own                  |

| bit 15       | Unimplemen                             | ted: Read as '                                   | ٥'                         |                                      |                               |                      |                      |

| bit 14-12    |                                        |                                                  | o<br>ator Selection b      | nits(2)                              |                               |                      |                      |

| 511 14-12    |                                        |                                                  | ency Divider (O            |                                      |                               |                      |                      |

|              | 110 = Reserv                           |                                                  |                            |                                      |                               |                      |                      |

|              |                                        | ower RC Oscill                                   |                            |                                      |                               |                      |                      |

|              |                                        | dary Oscillator                                  |                            |                                      |                               |                      |                      |

|              |                                        | y Oscillator wit<br>y Oscillator (X <sup>-</sup> |                            | (XTPLL, ECPL                         | L)                            |                      |                      |

|              |                                        |                                                  | th PLL module              | (FRCPLL)                             |                               |                      |                      |

|              |                                        | C Oscillator (F                                  |                            |                                      |                               |                      |                      |

| bit 11       |                                        | ted: Read as '                                   |                            | (a)                                  |                               |                      |                      |

| bit 10-8     |                                        |                                                  | Selection bits             |                                      |                               |                      |                      |

|              |                                        |                                                  | ency Divider (O            | SCFDIV)                              |                               |                      |                      |

|              | 110 = Reserv                           | /ed<br>ower RC Oscill                            | ator (LPPC)                |                                      |                               |                      |                      |

|              |                                        | dary Oscillator                                  | · · ·                      |                                      |                               |                      |                      |

|              | 011 = Primar                           | y Oscillator wit                                 | h PLL module               | (XTPLL, ECPL                         | L)                            |                      |                      |

|              |                                        | y Oscillator (X                                  |                            |                                      |                               |                      |                      |

|              |                                        | C Oscillator wi<br>C Oscillator (F               | th PLL module              | (FRCPLL)                             |                               |                      |                      |

| bit 7        |                                        | ·                                                | Lock Enable b              | bit                                  |                               |                      |                      |

|              | If FSCM is Er                          | nabled (FCKSN                                    | <b>/&lt;1:0&gt; =</b> 00): |                                      |                               |                      |                      |

|              |                                        | d PLL selection                                  |                            | od and may ba                        | modified by ap                | tting the OSME       | N bit                |

|              |                                        | sabled (FCKSI                                    |                            | eu anu may be                        | mounieu by se                 | tting the OSWE       |                      |

|              |                                        |                                                  |                            | and may be m                         | odified by setti              | ng the OSWEN         | bit.                 |

| bit 6        | IOLOCK: I/O                            | Lock Enable b                                    | it <sup>(3)</sup>          | -                                    |                               | -                    |                      |

|              | 1 = I/O lock is                        |                                                  |                            |                                      |                               |                      |                      |

|              | 0 = I/O lock is                        |                                                  | 4)                         |                                      |                               |                      |                      |

| bit 5        |                                        | ock Status bit <sup>(</sup>                      |                            | 1.1.1                                |                               |                      |                      |

|              |                                        |                                                  |                            | start-up timer is<br>timer is runnir | satisfied<br>ng or PLL is dis | abled                |                      |

|              | OSCCON is prote<br>Switching Opera     |                                                  |                            | nt inadvertent c                     | lock switches.                | See Section 9.       | 4 "Clock             |

|              | Reset values for t                     |                                                  |                            | the FNOSCx C                         | onfiguration bits             | S.                   |                      |

| 3:           | The state of the loaddition, if the IO | OLOCK bit car                                    | only be chang              | jed once an un                       | locking sequen                | ce has been ex       |                      |

|              | This hit also reset                    | -                                                |                            |                                      |                               |                      |                      |

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

4: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

# **REGISTER 11-8:** IOCPx: INTERRUPT-ON-CHANGE POSITIVE EDGE x REGISTER<sup>(1,2,3)</sup>

| R/W-0                              | R/W-0 | R/W-0            | R/W-0             | R/W-0        | R/W-0           | R/W-0     | U-0   |

|------------------------------------|-------|------------------|-------------------|--------------|-----------------|-----------|-------|

|                                    |       |                  | IOCF              | Px<15:8>     |                 |           |       |

| bit 15                             |       |                  |                   |              |                 |           | bit 8 |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0             | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                                    |       |                  | IOC               | Px<7:0>      |                 |           |       |

| bit 7                              |       |                  |                   |              |                 |           | bit 0 |

| Legend:                            |       |                  |                   |              |                 |           |       |

| R = Readable                       | e bit | W = Writable bit |                   | U = Unimplem | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                  | '0' = Bit is clea | ared         | x = Bit is unkr | nown      |       |

bit 15-0 **IOCPx<15:0>:** Interrupt-on-Change Positive Edge x Enable bits

- 1 = Interrupt-on-Change is enabled on the IOCx pin for a positive going edge; the associated status bit and interrupt flag will be set upon detecting an edge

- 0 = Interrupt-on-Change is disabled on the IOCx pin for a positive going edge

- **Note 1:** Setting both IOCPx and IOCNx will enable the IOCx pin for both edges, while clearing both registers will disable the functionality.

- 2: Changing the value of this register while the module is enabled (IOCON = 1) may cause a spurious IOC event. The corresponding interrupt must be ignored, cleared (using IOCFx) or masked (within the interrupt controller), or this module must be enabled (IOCON = 0) when changing this register.

- 3: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

## REGISTER 11-9: IOCNX: INTERRUPT-ON-CHANGE NEGATIVE EDGE x REGISTER<sup>(1,2,3)</sup>

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | U-0   |

|-------------|-------|-------|-------|--------|-------|-------|-------|

|             |       |       | IOCN> | <15:8> |       |       |       |

| bit 15      |       |       |       |        |       |       | bit 8 |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|             |       |       | IOCN  | x<7:0> |       |       |       |

| bit 7       |       |       |       |        |       |       | bit 0 |

| bit 7       |       |       |       |        |       |       | bit   |

| I a manual. |       |       |       |        |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **IOCNx<15:0>:** Interrupt-on-Change Negative Edge x Enable bits

- 1 = Interrupt-on-Change is enabled on the IOCx pin for a negative going edge; the associated status bit and interrupt flag will be set upon detecting an edge

- 0 = Interrupt-on-Change is disabled on the IOCx pin for a negative going edge

- **Note 1:** Setting both IOCPx and IOCNx will enable the IOCx pin for both edges, while clearing both registers will disable the functionality.

- 2: Changing the value of this register while the module is enabled (IOCON = 1) may cause a spurious IOC event. The corresponding interrupt must be ignored, cleared (using IOCFx) or masked (within the interrupt controller), or this module must be enabled (IOCON = 0) when changing this register.

- 3: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

| U-0     | U-0 | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | —      | —      | —      | —      | —      | —      |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

# REGISTER 11-46: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP28R<5:0>:** RP28 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP28 (see Table 11-7 for peripheral function numbers).

# **REGISTER 13-1:** TxCON: TIMER2 CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 3 **T32:** 32-Bit Timer Mode Select bit<sup>(3)</sup>

- 1 = Timerx and Timery form a single 32-bit timer

0 = Timerx and Timery act as two 16-bit timers

- In 32-bit mode, T3CON control bits do not affect 32-bit timer operation.

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timerx Clock Source Select bit<sup>(2)</sup> 1 = Timer source is selected by TECS<1:0>

- 0 = Internal clock (Fosc/2)

- bit 0 Unimplemented: Read as '0'

- **Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

- 2: If TCS = 1 and TECS<1:0> = x1, the selected external timer input (TxCK or TyCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- 3: In 32-bit mode, the T3CON control bits do not affect 32-bit timer operation.

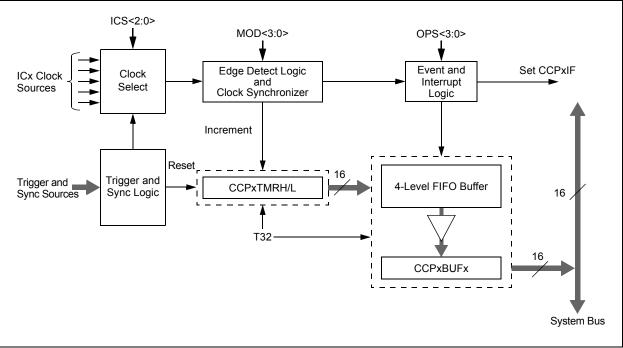

## 16.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 16-6 depicts a simplified block diagram of the Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L registers.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 16-3.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |  |  |

|------------------------------|-----------------------|------------------------------------|--|--|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |  |  |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |  |  |

| 0001                         | 0                     | Every Rising (16-bit capture)      |  |  |

| 0001                         | 1                     | Every Rising (32-bit capture)      |  |  |

| 0010                         | 0                     | Every Falling (16-bit capture)     |  |  |

| 0010                         | 1                     | Every Falling (32-bit capture)     |  |  |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |  |  |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |  |  |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |  |  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |  |  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |  |  |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |  |  |

#### TABLE 16-3: INPUT CAPTURE MODES

| R/W-0         | U-0                                        | R/W-0                                                | R/W-0                                                   | R/W-0                                                | R/W-0            | R/W-0            | R/W-1     |  |  |  |

|---------------|--------------------------------------------|------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|------------------|------------------|-----------|--|--|--|

| OENSYNC       |                                            | OCFEN                                                | OCEEN                                                   | OCDEN                                                | OCCEN            | OCBEN            | OCAEN     |  |  |  |

| bit 15        |                                            |                                                      | 1                                                       |                                                      |                  |                  | bit 8     |  |  |  |

| R/W-0         | R/W-0                                      | U-0                                                  | R/W-0                                                   | R/W-0                                                | R/W-0            | R/W-0            | R/W-0     |  |  |  |

| ICGSM1        | ICGSM0                                     |                                                      | AUXOUT1                                                 | AUXOUT0                                              | ICS2             | ICS1             | ICS0      |  |  |  |

| bit 7         |                                            |                                                      | I                                                       |                                                      |                  |                  | bit       |  |  |  |

| Legend:       |                                            |                                                      |                                                         |                                                      |                  |                  |           |  |  |  |

| R = Readable  | e bit                                      | W = Writable                                         | bit                                                     | U = Unimplem                                         | nented bit, read | d as '0'         |           |  |  |  |

| -n = Value at | POR                                        | '1' = Bit is set                                     |                                                         | '0' = Bit is clea                                    | ared             | x = Bit is unkr  | nown      |  |  |  |

|               |                                            |                                                      |                                                         |                                                      |                  |                  |           |  |  |  |

| bit 15        | 1 = Update b                               | y output enable                                      | Synchronizatior<br>e bits occurs or<br>e bits occurs im | n the next Time                                      | Base Reset o     | r rollover       |           |  |  |  |

| bit 14        | Unimplemented: Read as '0'                 |                                                      |                                                         |                                                      |                  |                  |           |  |  |  |

| bit 13-8      | OCxEN: Output Enable/Steering Control bits |                                                      |                                                         |                                                      |                  |                  |           |  |  |  |

|               | 0 = OCMx pi                                |                                                      | lled by the CCI                                         | odule and prod<br>Px module; the                     |                  |                  |           |  |  |  |

| bit 7-6       | ICGSM<1:0>:                                | : Input Capture                                      | Gating Source                                           | Mode Control                                         | bits             |                  |           |  |  |  |

|               | 01 = One-Sho<br>00 = Level-Se              | ot mode: Fallin<br>ot mode: Rising<br>ensitive mode: | g edge from ga                                          | ting source dis<br>ting source ena<br>om gating sour | bles future ca   | pture events (IC | CDIS = 0) |  |  |  |

| bit 5         | Unimplemen                                 | ted: Read as '                                       | 0'                                                      |                                                      |                  |                  |           |  |  |  |

| bit 4-3       | AUXOUT<1:0                                 | >: Auxiliary O                                       | utput Signal on                                         | Event Selectio                                       | n bits           |                  |           |  |  |  |

|               | 10 = Signal o                              | utput is defined<br>se rollover eve                  | d by module op                                          | t; no signal in T<br>erating mode (s                 |                  | •)               |           |  |  |  |

| bit 2-0       | ICS<2:0>: Input Capture Source Select bits |                                                      |                                                         |                                                      |                  |                  |           |  |  |  |

|               | 010 = Compa<br>001 = Compa                 | ved<br>output                                        | x) I/O pin                                              |                                                      |                  |                  |           |  |  |  |

# REGISTER 16-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

### REGISTER 17-3: SPIxCON2L: SPIx CONTROL REGISTER 2 LOW

| U-0          | U-0                            | U-0              | U-0           | U-0                  | U-0              | U-0             | U-0   |

|--------------|--------------------------------|------------------|---------------|----------------------|------------------|-----------------|-------|

|              | —                              | _                | _             | —                    | _                | _               | —     |

| bit 15       |                                |                  |               |                      |                  |                 | bit 8 |

|              |                                |                  |               |                      |                  |                 |       |

| U-0          | U-0                            | U-0              | R/W-0         | R/W-0                | R/W-0            | R/W-0           | R/W-0 |

|              | _                              |                  |               | W                    | LENGTH<4:0>      | (1,2)           |       |

| bit 7        |                                |                  |               |                      |                  |                 | bit 0 |

|              |                                |                  |               |                      |                  |                 |       |

| Legend:      |                                |                  |               |                      |                  |                 |       |

| R = Readab   | le bit                         | W = Writable     | bit           | U = Unimplen         | nented bit, read | d as '0'        |       |

| -n = Value a | It POR                         | '1' = Bit is set |               | '0' = Bit is cle     | ared             | x = Bit is unkr | nown  |

|              |                                |                  |               |                      |                  |                 |       |

| bit 15-5     | =                              | ted: Read as '   |               | (1.0)                |                  |                 |       |

| bit 4-0      |                                | 1:0>: Variable V | Nord Length b | its <sup>(1,2)</sup> |                  |                 |       |

|              | 11111 = 32-b                   |                  |               |                      |                  |                 |       |

|              | 11110 = 31-b<br>11101 = 30-b   |                  |               |                      |                  |                 |       |

|              | 11100 <b>= 29-</b> b           |                  |               |                      |                  |                 |       |

|              | 11011 <b>= 28-</b> b           |                  |               |                      |                  |                 |       |

|              | 11010 <b>= 27-</b> b           |                  |               |                      |                  |                 |       |

|              | 11001 <b>= 26-</b> b           | oit data         |               |                      |                  |                 |       |

|              | 11000 <b>= 25-</b> b           |                  |               |                      |                  |                 |       |

|              | 10111 <b>= 24</b> -b           |                  |               |                      |                  |                 |       |

|              | 10110 = 23-b                   |                  |               |                      |                  |                 |       |

|              | 10101 = 22-b<br>10100 = 21-b   |                  |               |                      |                  |                 |       |

|              | 10011 = 20-b                   |                  |               |                      |                  |                 |       |

|              | 10010 = <b>19</b> -b           |                  |               |                      |                  |                 |       |

|              | 10001 <b>= 18-</b> b           | oit data         |               |                      |                  |                 |       |

|              | 10000 <b>= 17</b> -b           |                  |               |                      |                  |                 |       |

|              | 01111 = <b>16</b> -b           |                  |               |                      |                  |                 |       |

|              | 01110 = 15-b<br>01101 = 14-b   |                  |               |                      |                  |                 |       |

|              | 01100 = 13-b                   |                  |               |                      |                  |                 |       |

|              | 01011 = <b>12</b> -b           |                  |               |                      |                  |                 |       |

|              | 01010 = <b>11</b> -b           |                  |               |                      |                  |                 |       |

|              | 01001 = <b>10</b> -b           | oit data         |               |                      |                  |                 |       |

|              | 01000 <b>= 9-bit</b>           |                  |               |                      |                  |                 |       |

|              | 00111 <b>= 8-bit</b>           |                  |               |                      |                  |                 |       |

|              | 00110 = 7-bit<br>00101 = 6-bit |                  |               |                      |                  |                 |       |

|              | 00101 = 6-bit<br>00100 = 5-bit |                  |               |                      |                  |                 |       |

|              | 000100 <b>= 3-bi</b>           |                  |               |                      |                  |                 |       |

|              | 00010 = <b>3</b> -bit          |                  |               |                      |                  |                 |       |

|              | 00001 = <b>2-bit</b>           |                  |               |                      |                  |                 |       |

|              |                                |                  |               | CON1L<11:10>         |                  |                 |       |

- **Note 1:** These bits are effective when AUDEN = 0 only.

- 2: Varying the length by changing these bits does not affect the depth of the TX/RX FIFO.

#### REGISTER 17-6: SPIxBUFL: SPIx BUFFER REGISTER LOW

| R/W-0             | R/W-0   | R/W-0            | R/W-0                | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|-------------------|---------|------------------|----------------------|------------------------------------|-------|--------------------|-------|--|--|

|                   |         |                  | DAT                  | A<15:8>                            |       |                    |       |  |  |

| bit 15            |         |                  |                      |                                    |       |                    | bit 8 |  |  |

|                   |         |                  |                      |                                    |       |                    |       |  |  |

| R/W-0             | R/W-0   | R/W-0            | R/W-0                | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                   |         |                  | DAT                  | Ā<7:0>                             |       |                    |       |  |  |

| bit 7             |         |                  |                      |                                    |       |                    | bit 0 |  |  |

|                   |         |                  |                      |                                    |       |                    |       |  |  |

| Legend:           |         |                  |                      |                                    |       |                    |       |  |  |

| R = Readab        | ole bit | W = Writable bit |                      | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at POR |         | '1' = Bit is set | '0' = Bit is cleared |                                    |       | x = Bit is unknown |       |  |  |

#### bit 15-0 DATA<15:0>: SPIx FIFO Data bits

When the MODE<32,16> or WLENGTH<4:0> bits select 16 to 9-bit data, the SPIx only uses DATA<15:0>. When the MODE<32,16> or WLENGTH<4:0> bits select 8 to 2-bit data, the SPIx only uses DATA<7:0>.

#### REGISTER 17-7: SPIxBUFH: SPIx BUFFER REGISTER HIGH

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|----------|-------|-------|-------|

|                                                                      |       |       | DATA  | \<31:24> |       |       |       |

| bit 15                                                               |       |       |       |          |       |       | bit 8 |

|                                                                      |       |       |       |          |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | DATA  | \<23:16> |       |       |       |

| bit 7                                                                |       |       |       |          |       |       | bit 0 |

|                                                                      |       |       |       |          |       |       |       |

| Legend:                                                              |       |       |       |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |          |       |       |       |

#### bit 15-0 DATA<31:16>: SPIx FIFO Data bits

'1' = Bit is set

When the MODE<32,16> or WLENGTH<4:0> bits select 32 to 25-bit data, the SPIx uses DATA<31:16>. When the MODE<32,16> or WLENGTH<4:0> bits select 24 to 17-bit data, the SPIx only uses DATA<23:16>.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| U-0          | U-0                                                                                                                                                | U-0                                 | U-0                        | U-0                                 | U-0               | U-0              | U-0             |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------|-------------------------------------|-------------------|------------------|-----------------|--|

| _            | _                                                                                                                                                  | —                                   |                            | —                                   |                   | —                | _               |  |

| bit 15       |                                                                                                                                                    | •                                   |                            |                                     |                   |                  | bit 8           |  |

|              | DAVA                                                                                                                                               | DANA                                | DAMO                       | DAM/ 0                              | DAMO              | DANIO            | DAMO            |  |

| U-0          | R/W-0                                                                                                                                              | R/W-0                               | R/W-0                      | R/W-0<br>SDAHT <sup>(1)</sup>       | R/W-0             | R/W-0            | R/W-0           |  |

|              | PCIE                                                                                                                                               | SCIE                                | BOEN                       | SDAH1.                              | SBCDE             | AHEN             | DHEN            |  |

| bit 7        |                                                                                                                                                    |                                     |                            |                                     |                   |                  | bit (           |  |

| Legend:      |                                                                                                                                                    |                                     |                            |                                     |                   |                  |                 |  |

| R = Readab   | ole bit                                                                                                                                            | W = Writable                        | oit                        | U = Unimplem                        | ented bit, read   | as '0'           |                 |  |

| -n = Value a | It POR                                                                                                                                             | '1' = Bit is set                    |                            | '0' = Bit is clea                   | ired              | x = Bit is unkno | own             |  |

|              |                                                                                                                                                    |                                     |                            |                                     |                   |                  |                 |  |

| bit 15-7     | Unimplemen                                                                                                                                         | ted: Read as '                      | )'                         |                                     |                   |                  |                 |  |

| bit 6        | PCIE: Stop Co                                                                                                                                      | ondition Interru                    | pt Enable bit (            | I <sup>2</sup> C Slave mode         | only)             |                  |                 |  |

|              |                                                                                                                                                    | nterrupt on dete                    |                            | condition                           |                   |                  |                 |  |

| =            | 0 = Stop detection interrupts are disabled                                                                                                         |                                     |                            |                                     |                   |                  |                 |  |

| bit 5        | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)<br>1 = Enables interrupt on detection of Start or Restart conditions |                                     |                            |                                     |                   |                  |                 |  |

|              |                                                                                                                                                    | ction interrupts                    |                            | or Restart condi                    | uons              |                  |                 |  |

| bit 4        |                                                                                                                                                    |                                     |                            | ave mode only)                      |                   |                  |                 |  |

|              |                                                                                                                                                    |                                     | •                          | enerated for a re                   | ceived address    | /data byte, igno | oring the state |  |

|              |                                                                                                                                                    | COV bit only if F                   |                            |                                     |                   |                  |                 |  |

| 1.11.0       |                                                                                                                                                    | is only update                      |                            | / is clear                          |                   |                  |                 |  |

| bit 3        |                                                                                                                                                    | x Hold Time Se                      |                            | ofter the folling                   | adaa af SCI y     |                  |                 |  |

|              |                                                                                                                                                    |                                     |                            | after the falling after the falling |                   |                  |                 |  |

| bit 2        |                                                                                                                                                    |                                     |                            | Enable bit (I <sup>2</sup> C        | -                 | lv)              |                 |  |

|              |                                                                                                                                                    |                                     |                            | mpled low when                      |                   |                  | igh state, the  |  |

|              | BCL bit is set                                                                                                                                     |                                     |                            | Detection mode                      |                   |                  |                 |  |

|              | sequences.                                                                                                                                         | lave bus collisi                    | on intorrunte              |                                     |                   |                  |                 |  |

|              |                                                                                                                                                    | collision interr                    |                            | led                                 |                   |                  |                 |  |

| bit 1        |                                                                                                                                                    | ss Hold Enable                      | •                          |                                     |                   |                  |                 |  |

|              |                                                                                                                                                    |                                     |                            | CLx for a mate                      | hing received     | address byte;    | SCLREL bi       |  |

|              | •                                                                                                                                                  | NL<12>) will be<br>holding is disat |                            | SCLx will be hel                    | d low             |                  |                 |  |

| bit 0        | DHEN: Data I                                                                                                                                       | Hold Enable bit                     | (I <sup>2</sup> C Slave mo | ode only)                           |                   |                  |                 |  |

|              |                                                                                                                                                    |                                     |                            | for a received da                   | ata byte; slave l | nardware clears  | the SCLREI      |  |

|              |                                                                                                                                                    | CONL<12>) and                       | d SCLx is held             | llow                                |                   |                  |                 |  |

|              | 0 = Data noic                                                                                                                                      | ling is disabled                    |                            |                                     |                   |                  |                 |  |

### REGISTER 18-2: I2CxCONH: I2Cx CONTROL REGISTER HIGH

# 20.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Parallel Master Port (EPMP)" (DS39730), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only) or 8-bit (Master and Slave modes) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD Controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each Chip Select, and then assigning each Chip Select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP. Key features of the EPMP module are:

- Extended Data Space (EDS) Interface Allows

Direct Access from the CPU

- Up to 10 Programmable Address Lines

- Up to 2 Chip Select Lines

- Up to 2 Acknowledgment Lines (one per Chip Select)

- 4-Bit or 8-Bit Wide Data Bus

- Programmable Strobe Options (per Chip Select):

- Individual read and write strobes or;

Read/Write strobe with enable strobe

- Programmable Address/Data Multiplexing

- Programmable Address Wait States

- Programmable Data Wait States (per Chip Select)

- Programmable Polarity on Control Signals (per Chip Select)

- · Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

Only the higher pin count packages in the family implement the EPMP. The EPMP feature is not available on 28-pin devices.

| R/W-0   | U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |  |  |  |

|---------|---------|-----|-----|-----|-----|-----|--------|--|--|--|

| IOCON   |         | —   | —   | —   | —   | —   | —      |  |  |  |

| bit 15  |         |     |     | ·   |     |     | bit 8  |  |  |  |

|         |         |     |     |     |     |     |        |  |  |  |

| U-0     | U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |  |  |

| —       | —       | —   | —   | —   | —   | —   | PMPTTL |  |  |  |

| bit 7   |         | •   | •   | •   |     |     | bit 0  |  |  |  |

|         |         |     |     |     |     |     |        |  |  |  |

| Legend: | Legend: |     |     |     |     |     |        |  |  |  |

|         |         |     |     |     |     | (0) |        |  |  |  |

# REGISTER 20-9: PADCON: PAD CONFIGURATION CONTROL REGISTER

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 IOCON: Used for Non-PMP functionality

bit 14-1 Unimplemented: Read as '0'

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

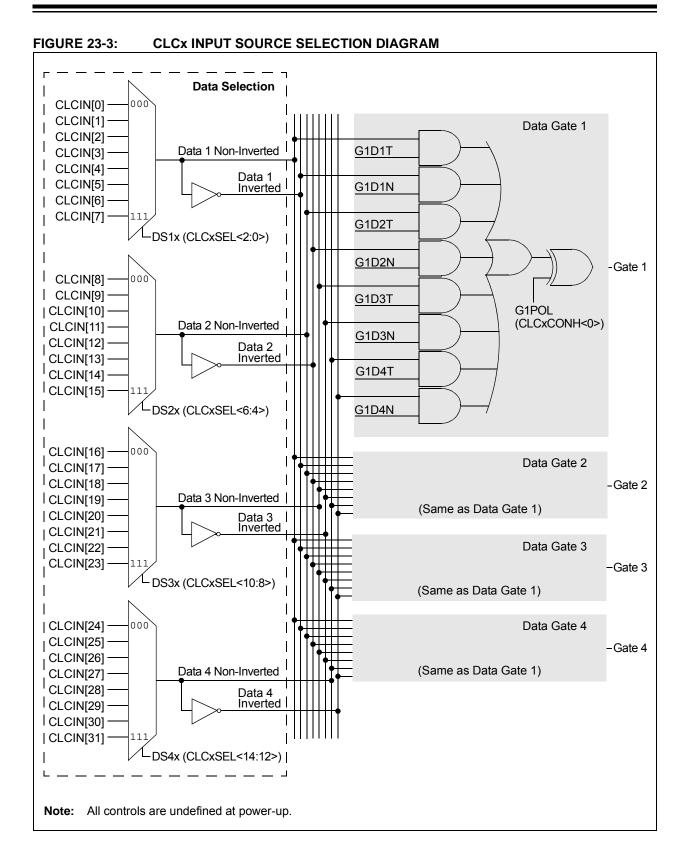

# REGISTER 23-3: CLCxSEL: CLCx INPUT MUX SELECT REGISTER

| U-0          | R/W-0                                                                           | R/W-0                                                                                               | R/W-0         | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|--------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|

|              |                                                                                 | DS4<2:0>                                                                                            |               |                  |                  | DS3<2:0>        |       |  |  |  |

| bit 15       |                                                                                 |                                                                                                     |               |                  |                  |                 | bit 8 |  |  |  |

|              |                                                                                 |                                                                                                     |               |                  |                  |                 |       |  |  |  |

| U-0          | R/W-0                                                                           | R/W-0                                                                                               | R/W-0         | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| —            |                                                                                 | DS2<2:0>                                                                                            |               |                  |                  | DS1<2:0>        |       |  |  |  |

| bit 7        |                                                                                 |                                                                                                     |               |                  |                  |                 | bit 0 |  |  |  |

| Legend:      |                                                                                 |                                                                                                     |               |                  |                  |                 |       |  |  |  |

| R = Readab   | le hit                                                                          | W = Writable I                                                                                      | hit           | U = Unimpler     | mented bit, rea  | d as '0'        |       |  |  |  |

| -n = Value a |                                                                                 | '1' = Bit is set                                                                                    |               | '0' = Bit is cle |                  | x = Bit is unkn | own   |  |  |  |

|              |                                                                                 |                                                                                                     |               |                  | alea             |                 | 0000  |  |  |  |

| bit 15       | Unimpleme                                                                       | nted: Read as '0                                                                                    | )'            |                  |                  |                 |       |  |  |  |

| bit 14-12    | DS4<2:0>:                                                                       | Data Selection M                                                                                    | UX 4 Signal S | Selection bits   |                  |                 |       |  |  |  |

|              |                                                                                 | P3 Compare Eve                                                                                      | -             |                  |                  |                 |       |  |  |  |

|              |                                                                                 | P1 Compare Eve                                                                                      |               |                  |                  |                 |       |  |  |  |

|              | 101 <b>= Unim</b>                                                               |                                                                                                     |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 | 100 = CTMU A/D trigger<br>011 = SPIx Input (SDIx) corresponding to the CLCx module (see Table 23-1) |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 |                                                                                                     | esponding to  | the CLCx modu    | lie (see Table ) | 23-1)           |       |  |  |  |

|              | 010 = Comparator 3 output<br>001 = Module-specific CLCx output (see Table 23-1) |                                                                                                     |               |                  |                  |                 |       |  |  |  |

|              | 000 = CLCINB I/O pin                                                            |                                                                                                     |               |                  |                  |                 |       |  |  |  |

| bit 11       | Unimpleme                                                                       | Unimplemented: Read as '0'                                                                          |               |                  |                  |                 |       |  |  |  |

| bit 10-8     | DS3<2:0>:                                                                       | DS3<2:0>: Data Selection MUX 3 Signal Selection bits                                                |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 | P3 Compare Eve                                                                                      |               | • • •            |                  |                 |       |  |  |  |

|              |                                                                                 | P2 Compare Eve                                                                                      |               | lag (CCP2IF)     |                  |                 |       |  |  |  |

|              |                                                                                 | Channel 1 interr                                                                                    |               | the CLCy mod     | ula (aga Tabla   | 02 1)           |       |  |  |  |

|              |                                                                                 | Output (SDOx) c                                                                                     |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 | parator 2 output                                                                                    | oncoponang    |                  |                  | 10 20 1)        |       |  |  |  |

|              | 001 = CLCx                                                                      | output (see Tab                                                                                     | e 23-1)       |                  |                  |                 |       |  |  |  |

|              | 000 = CLCII                                                                     | •                                                                                                   |               |                  |                  |                 |       |  |  |  |

| bit 7        | -                                                                               | nted: Read as '0                                                                                    |               |                  |                  |                 |       |  |  |  |

| bit 6-4      |                                                                                 | Data Selection M                                                                                    | -             |                  |                  |                 |       |  |  |  |

|              |                                                                                 | P2 Compare Eve<br>P1 Compare Eve                                                                    |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 | Channel 0 interr                                                                                    |               |                  |                  |                 |       |  |  |  |

|              | 100 <b>= A/D c</b>                                                              | onversion done i                                                                                    | nterrupt      |                  |                  |                 |       |  |  |  |

|              |                                                                                 | Tx TX input corre                                                                                   | sponding to t | he CLCx module   | e (see Table 2   | 3-1)            |       |  |  |  |

|              |                                                                                 | parator 1 output<br>coutput (see Tab                                                                | 0 22 1)       |                  |                  |                 |       |  |  |  |

|              | 000 = CLCI                                                                      |                                                                                                     | e 23-1)       |                  |                  |                 |       |  |  |  |

| bit 3        |                                                                                 | nted: Read as '0                                                                                    | )'            |                  |                  |                 |       |  |  |  |

| bit 2-0      | -                                                                               | Data Selection M                                                                                    |               | Selection bits   |                  |                 |       |  |  |  |

|              |                                                                                 | 3 match event                                                                                       | Ū             |                  |                  |                 |       |  |  |  |

|              | 110 <b>= Time</b> r                                                             | 2 match event                                                                                       |               |                  |                  |                 |       |  |  |  |

|              | 101 = Unim                                                                      | -                                                                                                   |               |                  |                  |                 |       |  |  |  |

|              | 100 = REFC                                                                      | ) output<br>C/LPRC clock sc                                                                         | urce          |                  |                  |                 |       |  |  |  |

|              |                                                                                 | C/LPRC Clock SC<br>C clock source                                                                   |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 | em clock (TCY)                                                                                      |               |                  |                  |                 |       |  |  |  |

|              | 000 = CLCII                                                                     | NA I/O pin                                                                                          |               |                  |                  |                 |       |  |  |  |

|              |                                                                                 |                                                                                                     |               |                  |                  |                 |       |  |  |  |

| TABLE 32-11: | INTERNAL | <b>VOLTAGE REGUL</b> | ATOR SPECIFICATIONS |

|--------------|----------|----------------------|---------------------|