# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

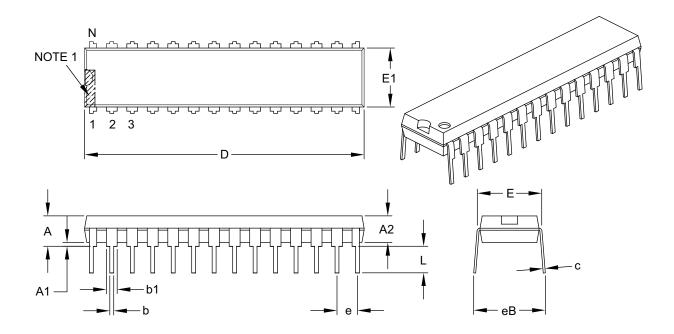

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga702-i-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJXXXGA70X: 44-PIN AND 48-PIN DEVICES |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

| Features                                                               | PIC24FJ64GA70X                                                                                                                                                 | PIC24FJ128GA70X                         | PIC24FJ256GA70X |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|--|--|--|--|

| Operating Frequency                                                    | DC – 32 MHz                                                                                                                                                    |                                         |                 |  |  |  |  |

| Program Memory (bytes)                                                 | 64K                                                                                                                                                            | 128K                                    | 256K            |  |  |  |  |

| Program Memory<br>(instruction words, 24 bits)                         | 22,528                                                                                                                                                         | 45,056                                  | 88,064          |  |  |  |  |

| Data Memory (bytes)                                                    | 16K                                                                                                                                                            |                                         |                 |  |  |  |  |

| Interrupt Sources<br>(soft vectors/NMI traps)                          | 124                                                                                                                                                            |                                         |                 |  |  |  |  |

| I/O Ports                                                              | Ports A, B, C                                                                                                                                                  |                                         |                 |  |  |  |  |

| Total I/O Pins:                                                        |                                                                                                                                                                |                                         |                 |  |  |  |  |

| 44-pin                                                                 | 35                                                                                                                                                             | 35                                      | 35              |  |  |  |  |

| 48-pin                                                                 | 39                                                                                                                                                             | 39                                      | 39              |  |  |  |  |

| Remappable Pins:                                                       |                                                                                                                                                                |                                         |                 |  |  |  |  |

| 44-pin                                                                 |                                                                                                                                                                | 29 (29 I/Os, 0 input only)              |                 |  |  |  |  |

| 48-pin                                                                 |                                                                                                                                                                | 33 (29 I/Os, 4 input only)              |                 |  |  |  |  |

| DMA (6-channel)                                                        |                                                                                                                                                                | 1                                       |                 |  |  |  |  |

| 16-Bit Timers                                                          |                                                                                                                                                                | 3(1)                                    |                 |  |  |  |  |

| Real-Time Clock and Calendar<br>(RTCC)                                 | Yes                                                                                                                                                            |                                         |                 |  |  |  |  |

| Cyclic Redundancy Check (CRC)                                          |                                                                                                                                                                | Yes                                     |                 |  |  |  |  |

| Input Capture Channels                                                 |                                                                                                                                                                | 3 <sup>(1)</sup>                        |                 |  |  |  |  |

| Output Compare/PWM Channels                                            |                                                                                                                                                                | 3 <sup>(1)</sup>                        |                 |  |  |  |  |

| Input Change Notification Interrupt                                    |                                                                                                                                                                | 25 (remappable pins)                    |                 |  |  |  |  |

| Serial Communications:                                                 |                                                                                                                                                                |                                         |                 |  |  |  |  |

| UART                                                                   |                                                                                                                                                                | 2(1)                                    |                 |  |  |  |  |

| SPI (3-wire/4-wire)                                                    |                                                                                                                                                                | 3 <sup>(1)</sup>                        |                 |  |  |  |  |

| l <sup>2</sup> C                                                       |                                                                                                                                                                | 2                                       |                 |  |  |  |  |

| Configurable Logic Cell (CLC)                                          |                                                                                                                                                                | 2(1)                                    |                 |  |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                                  |                                                                                                                                                                | Yes                                     |                 |  |  |  |  |

| Capture/Compare/PWM/Timer<br>Modules (MCCP)                            |                                                                                                                                                                | 4 Modules<br>1 (6-output), 3 (2-output) |                 |  |  |  |  |

| JTAG Boundary Scan                                                     |                                                                                                                                                                | Yes                                     |                 |  |  |  |  |

| 10/12-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) |                                                                                                                                                                | 14                                      |                 |  |  |  |  |

| Analog Comparators                                                     |                                                                                                                                                                | 3                                       |                 |  |  |  |  |

| CTMU Interface                                                         |                                                                                                                                                                | Yes                                     |                 |  |  |  |  |

| Universal Serial Bus Controller                                        |                                                                                                                                                                | No                                      |                 |  |  |  |  |

| Resets (and delays)                                                    | Core POR, VDD POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                                         |                 |  |  |  |  |

| Instruction Set                                                        | 76 Base Instru                                                                                                                                                 | ctions, Multiple Addressing N           | Mode Variations |  |  |  |  |

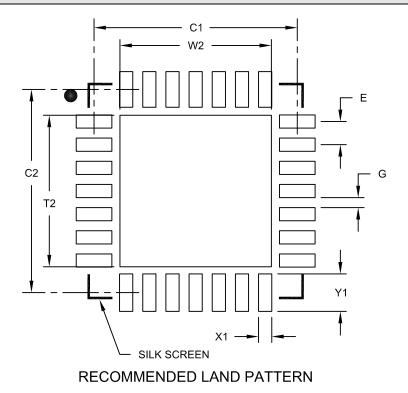

| Packages                                                               |                                                                                                                                                                | Pin TQFP, 48-Pin TQFP and               |                 |  |  |  |  |

**Note 1:** Some peripherals are accessible through remappable pins.

| Pin                  | Pin Number/Grid Locator     |                                 |    |                         |     | Innut           |                                                                             |  |

|----------------------|-----------------------------|---------------------------------|----|-------------------------|-----|-----------------|-----------------------------------------------------------------------------|--|

| Function             | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN, 44-Pin<br>UQFN TQFP |    | 48-Pin<br>QFN/TQFP      | I/O | Input<br>Buffer | Description                                                                 |  |

| PGC1                 | 5 2 22 24 I ST              |                                 | ST | ICSP™ Programming Clock |     |                 |                                                                             |  |

| PGC2                 | 22                          | 19                              | 9  | 10                      | Ι   | ST              |                                                                             |  |

| PGC3                 | 15                          | 12                              | 42 | 46                      | Ι   | ST              |                                                                             |  |

| PGD1                 | 4                           | 1                               | 21 | 23                      | I/O | DIG/ST          | ICSP Programming Data                                                       |  |

| PGD2                 | 21                          | 18                              | 8  | 9                       | I/O | DIG/ST          |                                                                             |  |

| PGD3                 | 14                          | 11                              | 41 | 45                      | I/O | DIG/ST          |                                                                             |  |

| PMA0                 | —                           | —                               | 3  | 3                       | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<0>/<br>Address Latch Low                       |  |

| PMA1                 | —                           | —                               | 2  | 2                       | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<1>/<br>Address Latch High                      |  |

| PMA2                 | —                           | —                               | 12 | 13                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<2>                                             |  |

| PMA3                 | _                           | _                               | 38 | 41                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<3>                                             |  |

| PMA4                 | —                           | _                               | 37 | 40                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<4>                                             |  |

| PMA5                 | _                           | _                               | 4  | 4                       | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<5>                                             |  |

| PMA6                 | _                           | _                               | 5  | 5                       | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<6>                                             |  |

| PMA7                 | —                           | —                               | 13 | 14                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<7>                                             |  |

| PMA8                 | —                           | —                               | 32 | 35                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<8>                                             |  |

| PMA9                 | _                           | —                               | 35 | 38                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<9>                                             |  |

| PMA14/PMCS/<br>PMCS1 | _                           | —                               | 15 | 16                      | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<14>/<br>Slave Chip Select/Chip Select 1 Strobe |  |

#### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

© 2016 Microchip Technology Inc.

| R/W-0  | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| DMAEN  | —   | —   | —   | _   | —   | —   | —      |

| bit 15 |     |     |     |     |     |     | bit 8  |

|        |     |     |     |     |     |     |        |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| —      | —   | —   | —   |     |     | _   | PRSSEL |

| bit 7  |     |     |     |     |     |     | bit 0  |

|        |     |     |     |     |     |     |        |

## REGISTER 5-1: DMACON: DMA ENGINE CONTROL REGISTER

## Legend:

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 DMAEN: DMA Module Enable bit

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round-robin scheme

0 = Fixed priority scheme

| DISI                              | #5                                                 | ; Block all interrupts with priority <7<br>; for next 5 instructions                            |

|-----------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|

| MOV.B<br>MOV<br>MOV.B<br>MOV      | #0x55, W0<br>W0, NVMKEY<br>#0xAA, W1<br>W1, NVMKEY | ; Write the 0x55 key<br>;<br>; Write the 0xAA key                                               |

| BSET<br>NOP<br>NOP<br>BTSC<br>BRA | NVMCON, #WR<br>NVMCON, #15<br>\$-2                 | ; Start the programming sequence<br>; Required delays<br>; and wait for it to be<br>; completed |

|                                   |                                                    |                                                                                                 |

#### EXAMPLE 6-2: INITIATING A PROGRAMMING SEQUENCE

## 8.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the PIC24FJ256GA705 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24FJ256GA705 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24FJ256GA705 family CPU.

The interrupt controller has the following features:

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

## 8.1 Interrupt Vector Table

The PIC24FJ256GA705 family Interrupt Vector Table (IVT), shown in Figure 8-1, resides in program memory starting at location, 000004h. The IVT contains 6 non-maskable trap vectors and up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The AIVTEN (INTCON2<8>) control bit provides access to the AIVT. If the AIVTEN bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application, and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24FJ256GA705 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 8.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter<br>this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                              |

#### 8.3.1 KEY RESOURCES

- "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## 8.4 Interrupt Control and Status Registers

PIC24FJ256GA705 family devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON4

- IFS0 through IFS7

- IEC0 through IEC7

- IPC0 through ICP29

- INTTREG

## 8.4.1 INTCON1-INTCON4

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources.

The INTCON2 register controls global interrupt generation, the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

The INTCON4 register contains the Software Generated Hard Trap bit (SGHT) and ECC Double-Bit Error (ECCDBE) trap.

## 8.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal, and is cleared via software.

## 8.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 8.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 8.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 8-2. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IPx bits in the first position of IPC0 (IPC0<2:0>).

## 8.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to "CPU with Extended Data Space (EDS)" (DS39732) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 8-3 through Register 8-6 in the following pages.

## **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Power-Saving Features" (DS39698), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ256GA705 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the  ${\tt PWRSAV}$  instruction is shown in Example 10-1.

The MPLAB<sup>®</sup> XC16 C compiler offers "built-in" functions for the power-saving modes as follows:

Idle(); // places part in Idle

Sleep(); // places part in Sleep

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

#### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | SLEEP mode |

|--------|-------------|---|-----|-----|--------|------|------------|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | IDLE mode  |

#### REGISTER 10-5: PMD5: PERIPHERAL MODULE DISABLE REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0    | U-0    |

|--------|-----|-----|-----|--------|--------|--------|--------|

| —      | —   | —   | —   | —      | —      | —      | —      |

| bit 15 |     |     |     |        |        |        | bit 8  |

|        |     |     |     |        |        |        |        |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|        | _   |     |     | CCP4MD | CCP3MD | CCP2MD | CCP1MD |

| bit 7             |                  |                       | b                  | oit 0 |

|-------------------|------------------|-----------------------|--------------------|-------|

|                   |                  |                       |                    |       |

| Legend:           |                  |                       |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |       |

| bit 15-4 | Unimplemented: Read as '0'                     |

|----------|------------------------------------------------|

| bit 3    | CCP4MD: MCCP4 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 2    | CCP3MD: MCCP3 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 1    | CCP2MD: MCCP2 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 0    | CCP1MD: MCCP1 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          |                                                |

0 = Module power and clock sources are enabled

## REGISTER 10-8: PMD8: PERIPHERAL MODULE DISABLE REGISTER 8

| U-0          | U-0          | U-0              | U-0           | U-0               | U-0              | U-0             | U-0   |

|--------------|--------------|------------------|---------------|-------------------|------------------|-----------------|-------|

|              | —            | _                | —             | —                 | —                | _               | —     |

| bit 15       |              |                  |               |                   |                  |                 | bit 8 |

|              |              |                  |               |                   |                  |                 |       |

| U-0          | U-0          | U-0              | U-0           | R/W-0             | R/W-0            | U-0             | U-0   |

| _            | —            | —                | —             | CLC2MD            | CLC1MD           | —               | —     |

| bit 7        |              |                  |               |                   |                  |                 | bit 0 |

|              |              |                  |               |                   |                  |                 |       |

| Legend:      |              |                  |               |                   |                  |                 |       |

| R = Readab   | ole bit      | W = Writable     | bit           | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |              |                  |               |                   |                  |                 |       |

| bit 15-4     | Unimplemer   | ted: Read as '   | )'            |                   |                  |                 |       |

| bit 3        | CLC2MD: CI   | C2 Module Dis    | able bit      |                   |                  |                 |       |

|              | 1 = Module i | s disabled       |               |                   |                  |                 |       |

|              | 0 = Module   | power and clock  | sources are e | nabled            |                  |                 |       |

- 0 = Module power and clock sources are enabled

bit 2

CLC1MD: CLC1 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

- bit 1-0 Unimplemented: Read as '0'

## 11.4 I/O Port Control Registers

| U-0    |

|-----|-----|-----|-----|-----|-----|--------|

|     | —   | —   | —   | —   | _   | —      |

|     |     |     |     |     |     | bit 8  |

|     |     |     |     |     |     |        |

| U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| _   | —   | —   | —   | —   | _   | PMPTTL |

|     |     |     |     |     |     | bit 0  |

|     | _   |     |     |     |     |        |

#### **REGISTER 11-1: PADCON: PORT CONFIGURATION REGISTER**

## Legend:

| =ogonan           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

| IOCON: Interrupt-on-Change Enable bit                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Interrupt-on-Change functionality is enabled</li> <li>0 = Interrupt-on-Change functionality is disabled</li> </ul> |

| Unimplemented: Read as '0'                                                                                                      |

| PMPTTL: PMP Port Type bit                                                                                                       |

| <ol> <li>1 = TTL levels on PMP port pins</li> <li>0 = Schmitt Triggers on PMP port pins</li> </ol>                              |

|                                                                                                                                 |

## REGISTER 11-2: IOCSTAT: INTERRUPT-ON-CHANGE STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   |     |     |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/HS/HC-0 | R/HS/HC-0 | R/HS/HC-0 |

|-------|-----|-----|-----|-----|-----------|-----------|-----------|

| —     | —   | —   | —   | —   | IOCPCF    | IOCPBF    | IOCPAF    |

| bit 7 |     |     |     |     |           |           | bit 0     |

| Legend:           | HS = Hardware Settable bit | Hardware Clearable bit     |                    |

|-------------------|----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-3 | Unimplemented: Read as '0'                                                                                                                                    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2    | IOCPCF: Interrupt-on-Change PORTC Flag bit                                                                                                                    |

|          | <ul> <li>1 = A change was detected on an IOC-enabled pin on PORTC</li> <li>0 = No change was detected or the user has cleared all detected changes</li> </ul> |

| bit 1    | IOCPBF: Interrupt-on-Change PORTB Flag bit                                                                                                                    |

|          | <ul> <li>1 = A change was detected on an IOC-enabled pin on PORTB</li> <li>0 = No change was detected or the user has cleared all detected changes</li> </ul> |

| bit 0    | IOCPAF: Interrupt-on-Change PORTA Flag bit                                                                                                                    |

|          | <ul> <li>1 = A change was detected on an IOC-enabled pin on PORTA</li> <li>0 = No change was detected, or the user has cleared all detected change</li> </ul> |

## REGISTER 11-10: IOCFx: INTERRUPT-ON-CHANGE FLAG x REGISTER<sup>(1,2)</sup>

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0        | R/W-0          | R/W-0     | U-0   |

|------------------------------------|-------|-----------------------------------------|-------|--------------|----------------|-----------|-------|

|                                    |       |                                         | IOCF  | Fx<15:8>     |                |           |       |

| bit 15                             |       |                                         |       |              |                |           | bit 8 |

|                                    |       |                                         |       |              |                |           |       |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0        | R/W-0          | R/W-0     | R/W-0 |

|                                    |       |                                         | IOC   | Fx<7:0>      |                |           |       |

| bit 7                              |       |                                         |       |              |                |           | bit 0 |

|                                    |       |                                         |       |              |                |           |       |

| Legend:                            |       |                                         |       |              |                |           |       |

| R = Readable                       | e bit | W = Writable bit                        |       | U = Unimplem | ented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |              | nown           |           |       |

bit 15-0 **IOCFx<15:0>:** Interrupt-on-Change Flag x bits

- 1 = An enabled change was detected on the associated pin; set when IOCPx = 1 and a positive edge was detected on the IOCx pin, or when IOCNx = 1 and a negative edge was detected on the IOCx pin

0 = No change was detected or the user cleared the detected change

- **Note 1:** It is not possible to set the IOCFx register bits with software writes (as this would require the addition of significant logic). To test IOC interrupts, it is recommended to enable the IOC functionality on one or more GPIO pins and then use the corresponding LATx register bit(s) to trigger an IOC interrupt.

- 2: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

#### REGISTER 11-11: IOCPUx: INTERRUPT-ON-CHANGE PULL-UP ENABLE x REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | U-0   |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | IOCPU | x<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | IOCPL | Jx<7:0> |       |       |       |

| bit 7  |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 IOCPUx<15:0>: Interrupt-on-Change Pull-up Enable x bits

1 = Pull-up is enabled

0 = Pull-up is disabled

Note 1: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

| U-0                               | U-0 | R/W-0  | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

|-----------------------------------|-----|--------|--------|--------------|------------------|--------|--------|

| _                                 | _   | RP13R5 | RP13R4 | RP13R3       | RP13R2           | RP13R1 | RP13R0 |

| bit 15                            |     |        |        |              |                  |        | bit 8  |

|                                   |     |        |        |              |                  |        |        |

| U-0                               | U-0 | R/W-0  | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

| —                                 | —   | RP12R5 | RP12R4 | RP12R3       | RP12R2           | RP12R1 | RP12R0 |

| bit 7                             |     |        |        |              |                  |        | bit 0  |

|                                   |     |        |        |              |                  |        |        |

| Legend:                           |     |        |        |              |                  |        |        |

| R = Readable bit W = Writable bit |     |        | bit    | U = Unimplem | nented bit, read | as '0' |        |

#### REGISTER 11-38: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

'1' = Bit is set

-n = Value at POR

bit 13-8RP13R<5:0>: RP13 Output Pin Mapping bits<br/>Peripheral Output Number n is assigned to pin, RP13 (see Table 11-7 for peripheral function numbers).bit 7-6Unimplemented: Read as '0'

'0' = Bit is cleared

x = Bit is unknown

bit 5-0 **RP12R<5:0>:** RP12 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP12 (see Table 11-7 for peripheral function numbers).

## REGISTER 11-39: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| _       | —   | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |

| bit 15  |     |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —       | —   | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP15R<5:0>:** RP15 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP15 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP14R<5:0>:** RP14 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP14 (see Table 11-7 for peripheral function numbers).

NOTES:

## REGISTER 17-2: SPIxCON1H: SPIx CONTROL REGISTER 1 HIGH (CONTINUED)

| bit 6   | FRMSYNC: Frame Sync Pulse Direction Control bit                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Frame Sync pulse input (slave)                                                                                                                                                 |

|         | 0 = Frame Sync pulse output (master)                                                                                                                                               |

| bit 5   | FRMPOL: Frame Sync/Slave Select Polarity bit                                                                                                                                       |

|         | 1 = Frame Sync pulse/slave select is active-high                                                                                                                                   |

|         | 0 = Frame Sync pulse/slave select is active-low                                                                                                                                    |

| bit 4   | MSSEN: Master Mode Slave Select Enable bit                                                                                                                                         |

|         | <ul> <li>SPIx slave select support is enabled with polarity determined by FRMPOL (SSx pin is automatically<br/>driven during transmission in Master mode)</li> </ul>               |

|         | 0 = SPIx slave select support is disabled (SSx pin will be controlled by port IO)                                                                                                  |

| bit 3   | FRMSYPW: Frame Sync Pulse-Width bit                                                                                                                                                |

|         | <ul> <li>1 = Frame Sync pulse is one serial word length wide (as defined by MODE&lt;32,16&gt;/WLENGTH&lt;4:0&gt;)</li> <li>0 = Frame Sync pulse is one clock (SCK) wide</li> </ul> |

| bit 2-0 | FRMCNT<2:0>: Frame Sync Pulse Counter bits                                                                                                                                         |

|         | Controls the number of serial words transmitted per Sync pulse.                                                                                                                    |

|         | 111 = Reserved                                                                                                                                                                     |

|         | 110 = Reserved                                                                                                                                                                     |

|         | 101 = Generates a Frame Sync pulse on every 32 serial words                                                                                                                        |

|         | 100 = Generates a Frame Sync pulse on every 16 serial words                                                                                                                        |

|         | 011 = Generates a Frame Sync pulse on every 8 serial words                                                                                                                         |

|         | 010 = Generates a Frame Sync pulse on every 4 serial words                                                                                                                         |

|         | 001 = Generates a Frame Sync pulse on every 2 serial words (value used by audio protocols)                                                                                         |

|         | 000 = Generates a Frame Sync pulse on each serial word                                                                                                                             |

- **Note 1:** AUDEN can only be written when the SPIEN bit = 0.

- **2:** AUDMONO can only be written when the SPIEN bit = 0 and is only valid for AUDEN = 1.

- **3:** URDTEN is only valid when IGNTUR = 1.

- **4:** AUDMOD<1:0> bits can only be written when the SPIEN bit = 0 and are only valid when AUDEN = 1. When NOT in PCM/DSP mode, this module functions as if FRMSYPW = 1, regardless of its actual value.

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | —   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

|        |     |                       |                       |                       |          |          |          |

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

| —      | —   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2   | TXELM1   | TXELM0   |

| bit 7  |     |                       |                       |                       |          |          | bit 0    |

| REGISTER 17-5: SPIXSTATH: SPIX STATUS REGISTER HIGH | REGISTER 17-5: | SPIxSTATH: SPIx STATUS REGISTER HIGH |

|-----------------------------------------------------|----------------|--------------------------------------|

|-----------------------------------------------------|----------------|--------------------------------------|

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

**3:** RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

#### REGISTER 24-7: ANCFG: A/D BAND GAP REFERENCE CONFIGURATION REGISTER

| U-0        | U-0                                                                       | U-0            | U-0            | U-0                  | U-0                   | U-0                   | U-0                   |

|------------|---------------------------------------------------------------------------|----------------|----------------|----------------------|-----------------------|-----------------------|-----------------------|

| _          | —                                                                         |                | _              | —                    | —                     | —                     | —                     |

| bit 15     |                                                                           |                |                |                      |                       |                       | bit 8                 |

|            |                                                                           |                |                |                      |                       |                       |                       |

| U-0        | U-0                                                                       | U-0            | U-0            | U-0                  | R/W-0                 | R/W-0                 | R/W-0                 |

| —          | —                                                                         | _              | —              | —                    | VBGEN3 <sup>(1)</sup> | VBGEN2 <sup>(1)</sup> | VBGEN1 <sup>(1)</sup> |

| bit 7      |                                                                           |                |                |                      |                       |                       | bit 0                 |

|            |                                                                           |                |                |                      |                       |                       |                       |

| Legend:    |                                                                           |                |                |                      |                       |                       |                       |

| R = Reada  | ble bit                                                                   | W = Writable   | bit            | U = Unimplem         | nented bit, read      | l as '0'              |                       |

| -n = Value | e at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow          |                | iown           |                      |                       |                       |                       |

|            |                                                                           |                |                |                      |                       |                       |                       |

| bit 15-3   | Unimplemen                                                                | ted: Read as ' | כ'             |                      |                       |                       |                       |

| bit 2      | VBGEN3: A/I                                                               | D Band Gap Re  | eference Enabl | e bit <sup>(1)</sup> |                       |                       |                       |

|            | 1 = Band gap reference is enabled<br>0 = Band gap reference is disabled   |                |                |                      |                       |                       |                       |

| bit 1      | VBGEN2: CTMLL and Comparator Band Gap Reference Enable bit <sup>(1)</sup> |                |                |                      |                       |                       |                       |

- bit 1 **VBGEN2:** CTMU and Comparator Band Gap Reference Enable bit<sup>(1)</sup>

- 1 = Band gap reference is enabled

- 0 = Band gap reference is disabled

## bit 0 VBGEN1: VREG, BOR, HLVD, FRC, NVM and A/D Boost Band Gap Reference Enable bit<sup>(1)</sup>

- 1 = Band gap reference is enabled

- 0 = Band gap reference is disabled

- **Note 1:** When a module requests a band gap reference voltage, that reference will be enabled automatically after a brief start-up time. The user can manually enable the band gap references using the ANCFG register before enabling the module requesting the band gap reference to avoid this start-up time (~1 ms).

## REGISTER 25-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    | -                                 |                |                  |                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|------------------|----------------|

| R/W-0            | R/W-0                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                | U-0                               | U-0            | R/W-0, HS        | R-0, HSC       |

| CEN              | COE                                                                                                                                                                 | CPOL                                                                                                                                                                                                                                                                    | —                                                                                                                                                                  | —                                 | —              | CEVT             | COUT           |

| bit 15           |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  | bit 8          |

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| R/W-0            | R/W-0                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                              | U-0                               | U-0            | R/W-0            | R/W-0          |

| EVPOL1           | EVPOL0                                                                                                                                                              | —                                                                                                                                                                                                                                                                       | CREF                                                                                                                                                               | —                                 | —              | CCH1             | CCH0           |

| bit 7            |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  | bit 0          |

|                  |                                                                                                                                                                     |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| Legend:          |                                                                                                                                                                     | HS = Hardware                                                                                                                                                                                                                                                           | e Settable bit                                                                                                                                                     | HSC = Hardv                       | vare Settable  | /Clearable bit   |                |

| R = Readabl      | e bit                                                                                                                                                               | W = Writable b                                                                                                                                                                                                                                                          | oit                                                                                                                                                                | U = Unimpler                      | mented bit, re | ad as '0'        |                |

| -n = Value at    | POR                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                                                                                                        |                                                                                                                                                                    | '0' = Bit is cle                  | eared          | x = Bit is unkr  | nown           |

| bit 15<br>bit 14 | 1 = Compara<br>0 = Compara<br><b>COE:</b> Compa<br>1 = Compara                                                                                                      | arator Enable bit<br>ator is enabled<br>ator is disabled<br>arator Output En-<br>ator output is pre<br>ator output is inte                                                                                                                                              | sent on the C>                                                                                                                                                     | OUT pin                           |                |                  |                |

| bit 13           | •                                                                                                                                                                   | parator Output P                                                                                                                                                                                                                                                        | 5                                                                                                                                                                  | oit                               |                |                  |                |

|                  | 1 = Compara                                                                                                                                                         | ator output is inv<br>ator output is not                                                                                                                                                                                                                                | erted                                                                                                                                                              |                                   |                |                  |                |

| bit 12-10        | Unimplemented: Read as '0'                                                                                                                                          |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| bit 9            | CEVT: Comp                                                                                                                                                          | arator Event bit                                                                                                                                                                                                                                                        |                                                                                                                                                                    |                                   |                |                  |                |

|                  | are disal                                                                                                                                                           | ator event that is<br>bled until the bit<br>ator event has no                                                                                                                                                                                                           | is cleared                                                                                                                                                         | POL<1:0> has c                    | occurred; sub  | sequent triggers | and interrupts |

| bit 8            | COUT: Comp                                                                                                                                                          | parator Output bi                                                                                                                                                                                                                                                       | t                                                                                                                                                                  |                                   |                |                  |                |

|                  | $\frac{\text{When CPOL}}{1 = \text{VIN} + > \text{V}}$ $0 = \text{VIN} + < \text{V}$                                                                                | /in-<br>/in-                                                                                                                                                                                                                                                            |                                                                                                                                                                    |                                   |                |                  |                |

|                  | $\frac{\text{When CPOL}}{1 = \text{VIN} + < \text{V}}$                                                                                                              |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

|                  | 0 = VIN + > V                                                                                                                                                       |                                                                                                                                                                                                                                                                         |                                                                                                                                                                    |                                   |                |                  |                |

| bit 7-6          | 11 = Trigger/<br>10 = Trigger/<br>High-to<br><u>If CPOI</u><br>Low-to-<br>01 = Trigger/<br><u>If CPOI</u><br>Low-to-<br><u>If CPOI</u><br>Low-to-<br><u>If CPOI</u> | Trigger/Event/<br>/event/interrupt is<br>/event/interrupt is<br>_ = 0 (non-inverter<br>-low transition or<br>_ = 1 (inverted pot<br>high transition of<br>/event/interrupt is<br>_ = 0 (non-inverter<br>high transition of<br>_ = 1 (inverted pot<br>-low transition or | s generated on<br>s generated on<br><u>ed polarity):</u><br>nly.<br><u>plarity):</u><br>nly.<br>s generated on<br><u>ed polarity):</u><br>nly.<br><u>plarity):</u> | any change of<br>transition of th | e comparator   | output:          | CEVT = 0)      |