Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT               |

| Number of I/O              | 22                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

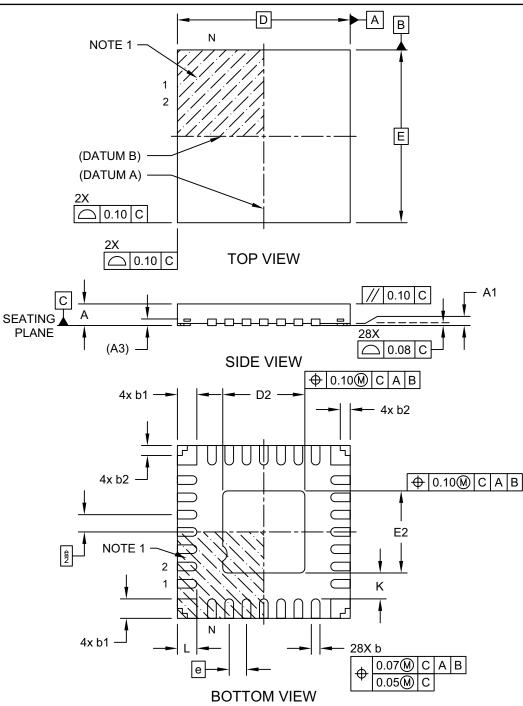

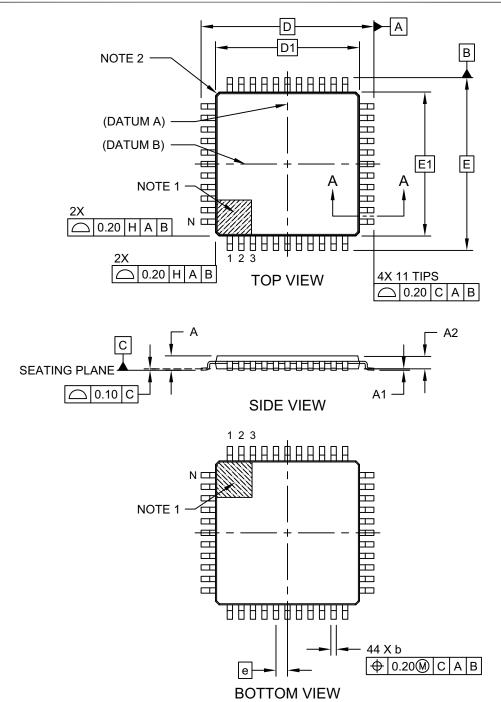

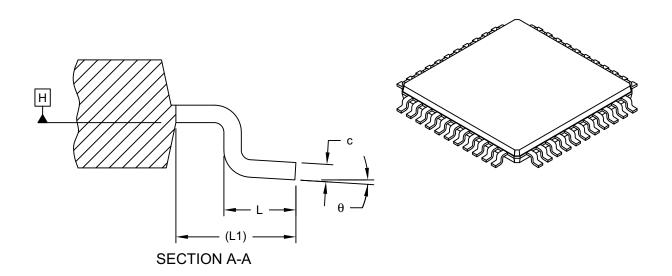

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga702t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name       | Address | All Resets | File Name       | Address | All Resets |

|-----------------|---------|------------|-----------------|---------|------------|

| DMA (CONTINUED) |         |            | DMA (CONTINUED) |         |            |

| DMAINT5         | 0500    | 0000       | DMADST5         | 0504    | 0000       |

| DMASRC5         | 0502    | 0000       | DMACNT5         | 0506    | 0001       |

#### TABLE 4-9: SFR MAP: 0500h BLOCK

Legend: x = undefined. Reset values are shown in hexadecimal.

#### TABLE 4-10: SFR MAP: 0600h BLOCK

| File Name | Address | All Resets | File Name       | Address | All Resets |

|-----------|---------|------------|-----------------|---------|------------|

| I/O       |         |            | PORTB (CONTINUE | D)      |            |

| PADCON    | 065E    | 0000       | ANSB            | 067E    | FFFF       |

| IOCSTAT   | 0660    | 0000       | IOCPB           | 0680    | 0000       |

| PORTA     |         |            | IOCNB           | 0682    | 0000       |

| TRISA     | 0662    | FFFF       | IOCFB           | 0684    | 0000       |

| PORTA     | 0664    | 0000       | IOCPUB          | 0686    | 0000       |

| LATA      | 0666    | 0000       | IOCPDB          | 0688    | 0000       |

| ODCA      | 0668    | 0000       | PORTC           |         |            |

| ANSA      | 066A    | FFFF       | TRISC           | 068A    | FFFF       |

| IOCPA     | 066C    | 0000       | PORTC           | 068C    | 0000       |

| IOCNA     | 066E    | 0000       | LATC            | 068E    | 0000       |

| IOCFA     | 0670    | 0000       | ODCC            | 0690    | 0000       |

| IOCPUA    | 0672    | 0000       | ANSC            | 0692    | FFFF       |

| IOCPDA    | 0674    | 0000       | IOCPC           | 0694    | 0000       |

| PORTB     |         |            | IOCNC           | 0696    | 0000       |

| TRISB     | 0676    | FFFF       | IOCFC           | 0698    | 0000       |

| PORTB     | 0678    | 0000       | IOCPUC          | 069A    | 0000       |

| LATB      | 067A    | 0000       | IOCPDC          | 069C    | 0000       |

| ODCB      | 067C    | 0000       |                 |         |            |

Legend: x = undefined. Reset values are shown in hexadecimal.

### 4.2.5.2 Data Write into EDS

In order to write data to EDS, such as in EDS reads, an Address Pointer is set up by loading the required EDS page number into the DSWPAG register, and assigning the offset address to one of the W registers. Once the above assignment is done, then the EDS window is enabled by setting bit 15 of the Working register, assigned with the offset address, and the accessed location can be written.

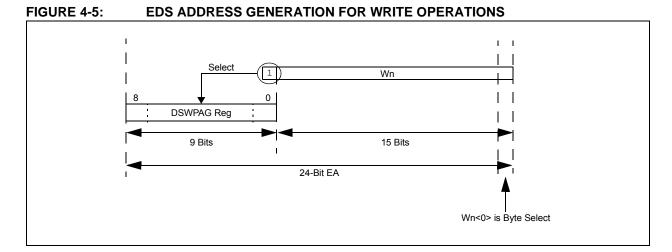

Figure 4-5 illustrates how the EDS address is generated for write operations.

When the MSbs of EA are '1', the lower 9 bits of DSWPAG are concatenated to the lower 15 bits of EA to form a 24-bit EDS address for write operations. Example 4-2 shows how to write a byte, word and double word to EDS.

The Data Space Page registers (DSRPAG/DSWPAG) do not update automatically while crossing a page boundary when the rollover happens from 0xFFFF to

0x8000. While developing code in assembly, care must be taken to update the Data Space Page registers when an Address Pointer crosses the page boundary. The 'C' compiler keeps track of the addressing, and increments or decrements the Page registers accordingly, while accessing contiguous data memory locations.

- **Note 1:** All write operations to EDS are executed in a single cycle.

- 2: Use of Read/Modify/Write operation on any EDS location under a REPEAT instruction is not supported. For example: BCLR, BSW, BTG, RLC f, RLNC f, RRC f, RRNC f, ADD f, SUB f, SUBR f, AND f, IOR f, XOR f, ASR f, ASL f.

- **3:** Use the DSRPAG register while performing Read/Modify/Write operations.

### EXAMPLE 4-2: EDS WRITE CODE IN ASSEMBLY

```

; Set the EDS page where the data to be written

#0x0002, w0

mov

w0, DSWPAG

;page 2 is selected for write

mov

#0x0800, w1

;select the location (0x800) to be written

mov

w1, #15

;set the MSB of the base address, enable EDS mode

bset

;Write a byte to the selected location

mov #0x00A5, w2

mov

#0x003C, w3

mov.b w2, [w1++]

;write Low byte

mov.b w3, [w1++]

;write High byte

;Write a word to the selected location

#0x1234, w2

mov

;

w2, [w1]

mov

;

;Write a Double - word to the selected location

#0x1122, w2

mov

mov

#0x4455, w3

mov.d w2, [w1]

;2 EDS writes

```

| R/S-0, HC <sup>(1)</sup>                 | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                 | R-0, HSC <sup>(1)</sup>                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                            | r-0                                                                                                                                                                                                        | r-0                                                       | U-0                                 | U-0                   |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------|-----------------------|

| WR                                       | WREN                                                                                                                                                                                                                                                                 | WRERR                                                                                                                                                                                                                                                                                                                         | NVMSIDL                                                                                                                                                                                                                                          | —                                                                                                                                                                                                          | —                                                         | —                                   | _                     |

| bit 15                                   |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                           |                                     | bit                   |

| U-0                                      | U-0                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                              | R/W-0 <sup>(1)</sup>                                                                                                                                                                                       | R/W-0 <sup>(1)</sup>                                      | R/W-0 <sup>(1)</sup>                | R/W-0 <sup>(1)</sup>  |

| _                                        | _                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                  | NVMOP3 <sup>(2)</sup>                                                                                                                                                                                      | NVMOP2 <sup>(2)</sup>                                     | NVMOP1 <sup>(2)</sup>               | NVMOP0 <sup>(2)</sup> |

| bit 7                                    |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                           |                                     | bit                   |

|                                          |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                           |                                     |                       |

| Legend:                                  |                                                                                                                                                                                                                                                                      | S = Settable                                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                              | HC = Hardware                                                                                                                                                                                              | Clearable bit                                             | r = Reserved b                      | oit                   |

| R = Readable                             | e bit                                                                                                                                                                                                                                                                | W = Writable                                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                              | '0' = Bit is cleare                                                                                                                                                                                        | ed                                                        | x = Bit is unkn                     | own                   |

| -n = Value at                            | POR                                                                                                                                                                                                                                                                  | '1' = Bit is se                                                                                                                                                                                                                                                                                                               | t                                                                                                                                                                                                                                                | U = Unimpleme                                                                                                                                                                                              | nted bit, read as                                         | s 'O'                               |                       |

| HSC = Hardv                              | vare Settable                                                                                                                                                                                                                                                        | /Clearable bit                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                           |                                     |                       |

| bit 15                                   | WR: Write C                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                           |                                     |                       |

|                                          | cleared                                                                                                                                                                                                                                                              | by hardware of                                                                                                                                                                                                                                                                                                                | nce the oper                                                                                                                                                                                                                                     | or erase operat<br>ation is complete<br>plete and inactive                                                                                                                                                 | -                                                         | on is self-timed                    | and the bit           |

| bit 14                                   | cleared<br>0 = Program                                                                                                                                                                                                                                               | by hardware of                                                                                                                                                                                                                                                                                                                | nce the oper                                                                                                                                                                                                                                     |                                                                                                                                                                                                            | -                                                         | on is self-timed                    | and the bit           |

| bit 14                                   | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables                                                                                                                                                                                                                  | by hardware o<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash prograr                                                                                                                                                                                                                                             | nce the oper<br>ration is com<br>n/erase opera                                                                                                                                                                                                   | ation is complete<br>plete and inactive<br>ations                                                                                                                                                          | -                                                         | on is self-timed                    | and the bit           |

| bit 14                                   | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits                                                                                                                                                                                                  | by hardware o<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>Flash program                                                                                                                                                                                                                            | nce the oper<br>ration is com<br>n/erase oper<br>/erase opera                                                                                                                                                                                    | ation is complete<br>plete and inactive<br>ations<br>tions                                                                                                                                                 | -                                                         | on is self-timed                    | and the bit           |

| bit 14<br>bit 13                         | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits<br>WRERR: W                                                                                                                                                                                      | by hardware o<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>Flash program<br>rite Sequence                                                                                                                                                                                                           | nce the oper<br>ration is com<br>n/erase opera<br>/erase opera<br>Error Flag bit                                                                                                                                                                 | ation is complete<br>plete and inactive<br>ations<br>tions<br>(1)                                                                                                                                          | ;                                                         |                                     |                       |

|                                          | cleared<br>0 = Program<br>WREN: Writi<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa                                                                                                                                                             | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>the Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s                                                                                                                                                                | nce the oper<br>ration is com<br>n/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>set attempt of                                                                                                                                 | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)                                                                                                                  | pt, or terminati                                          |                                     |                       |

| bit 13                                   | cleared<br>0 = Program<br>WREN: Writh<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro                                                                                                                                              | by hardware o<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase                                                                                                                                                    | nce the oper<br>ration is com<br>n/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>et attempt of<br>operation co                                                                                                                  | ation is complete<br>plete and inactive<br>ations<br>tions<br>(1)<br>sequence attem                                                                                                                        | pt, or terminati                                          |                                     |                       |

|                                          | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1                                                                                                                                 | by hardware of<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase                                                                                                                                                   | nce the oper<br>ration is com<br>/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>tet attempt of<br>operation co<br>le bit                                                                                                        | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally                                                                                              | pt, or terminati                                          | ion has occurr                      |                       |

| bit 13                                   | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: N<br>1 = Remove                                                                                                                   | by hardware of<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase<br>NVM Stop in Id<br>es power from                                                                                                                                 | nce the oper<br>ration is com<br>/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>set attempt of<br>operation co<br>le bit<br>the program                                                                                         | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)                                                                                                                  | pt, or terminati                                          | ion has occurr<br>mode              |                       |

| bit 13                                   | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1<br>1 = Remove<br>0 = Powers                                                                                                     | by hardware of<br>n or erase ope<br>e Enable bit <sup>(1)</sup><br>s Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase<br>NVM Stop in Id<br>es power from                                                                                                                                 | nce the oper<br>ration is com<br>/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>set attempt of<br>operation co<br>le bit<br>the program                                                                                         | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de                                                                            | pt, or terminati                                          | ion has occurr<br>mode              |                       |

| bit 13<br>bit 12                         | cleared<br>0 = Program<br>WREN: Writt<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1<br>1 = Removed<br>0 = Powers<br>Reserved: 1<br>Unimpleme                                                                       | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>is Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>ogram or erase<br>NVM Stop in Id<br>es power from<br>program mem<br>Maintain as '0'<br><b>nted:</b> Read as                                                  | nce the oper<br>ration is com<br>/erase opera<br>Error Flag bit<br>n or erase<br>set attempt of<br>operation co<br>le bit<br>the program<br>ory in Standb                                                                                        | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de<br>by mode when the                                                        | pt, or terminati                                          | ion has occurr<br>mode              |                       |

| bit 13<br>bit 12<br>bit 11-10            | cleared<br>0 = Program<br>WREN: Writ<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1<br>1 = Remove<br>0 = Powers<br>Reserved: 1<br>Unimpleme<br>NVMOP<3:0                                                            | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>is Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any sigram or erase<br>NVM Stop in Id<br>es power from<br>program mem<br>Maintain as '0'<br><b>nted:</b> Read as<br><b>D</b> : NVM Operation                          | nce the oper<br>ration is com<br>n/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>et attempt of<br>operation co<br>le bit<br>the program<br>ory in Standb<br>'0'<br>ation Select b                                               | ation is complete<br>plete and inactive<br>ations<br>tions<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de<br>by mode when the                                               | pt, or terminati<br>vice enters Idle<br>e device enters I | ion has occurr<br>mode<br>Idle mode | red (bit is s         |

| bit 13<br>bit 12<br>bit 11-10<br>bit 9-4 | cleared<br>0 = Program<br>WREN: Writt<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1<br>1 = Remove<br>0 = Powers<br>Reserved: 1<br>Unimpleme<br>NVMOP<3:0<br>1110 = Chip                                            | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>is Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase<br>NVM Stop in Id<br>es power from<br>program mem<br>Maintain as '0'<br><b>nted:</b> Read as<br><b>D</b> : NVM Opera<br>o erases user m        | nce the oper<br>ration is com<br>n/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>et attempt of<br>operation co<br>le bit<br>the program<br>ory in Standb<br>'0'<br>ation Select b                                               | ation is complete<br>plete and inactive<br>ations<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de<br>by mode when the                                                        | pt, or terminati<br>vice enters Idle<br>e device enters I | ion has occurr<br>mode<br>Idle mode | red (bit is s         |

| bit 13<br>bit 12<br>bit 11-10<br>bit 9-4 | cleared<br>0 = Program<br>WREN: Writt<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: 1<br>1 = Remove<br>0 = Powers<br>Reserved: 1<br>Unimpleme<br>NVMOP<3:0<br>1110 = Chip<br>0100 = Unu                              | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>is Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase<br>NVM Stop in Id<br>es power from<br>program mem<br>Maintain as '0'<br><b>nted:</b> Read as<br><b>D</b> : NVM Opera<br>o erases user m<br>sed | nce the oper<br>ration is com<br>/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>set attempt of<br>operation co<br>le bit<br>the program<br>ory in Standb<br>'0'<br>ation Select b<br>nemory (does                               | ation is complete<br>plete and inactive<br>ations<br>tions<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de<br>by mode when the<br>bits <sup>(1,2)</sup><br>s not erase Devic | pt, or terminati<br>vice enters Idle<br>e device enters I | ion has occurr<br>mode<br>Idle mode | red (bit is s         |

| bit 13<br>bit 12<br>bit 11-10<br>bit 9-4 | cleared<br>0 = Program<br>WREN: Writt<br>1 = Enables<br>0 = Inhibits<br>WRERR: W<br>1 = An imp<br>automa<br>0 = The pro<br>NVMSIDL: N<br>1 = Remove<br>0 = Powers<br>Reserved: N<br>Unimpleme<br>NVMOP<3:0<br>1110 = Chip<br>0100 = Unu<br>0011 = Eras<br>0100 = Row | by hardware on<br>n or erase ope<br>the Enable bit <sup>(1)</sup><br>is Flash program<br>Flash program<br>rite Sequence<br>proper program<br>tically on any s<br>gram or erase<br>NVM Stop in Id<br>es power from<br>program mem<br>Maintain as '0'<br><b>nted:</b> Read as<br><b>D</b> : NVM Opera<br>o erases user m<br>sed | nce the oper<br>ration is com<br>/erase opera<br>/erase opera<br>Error Flag bit<br>n or erase<br>tet attempt of<br>operation co<br>le bit<br>the program<br>ory in Standb<br>'0'<br>ation Select b<br>nemory (does<br>program or ex<br>operation | ation is complete<br>plete and inactive<br>ations<br>tions<br>(1)<br>sequence attem<br>the WR bit)<br>mpleted normally<br>memory when de<br>by mode when the<br>bits <sup>(1,2)</sup><br>s not erase Devic | pt, or terminati<br>vice enters Idle<br>e device enters I | ion has occurr<br>mode<br>Idle mode | red (bit is s         |

#### REGISTER 6-1. NVMCON: ELASH MEMORY CONTROL REGISTER

2: All other combinations of NVMOP<3:0> are unimplemented.

| DISI                              | #5                                                 | ; Block all interrupts with priority <7<br>; for next 5 instructions                            |

|-----------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|

| MOV.B<br>MOV<br>MOV.B<br>MOV      | #0x55, W0<br>W0, NVMKEY<br>#0xAA, W1<br>W1, NVMKEY | ; Write the 0x55 key<br>;<br>; Write the 0xAA key                                               |

| BSET<br>NOP<br>NOP<br>BTSC<br>BRA | NVMCON, #WR<br>NVMCON, #15<br>\$-2                 | ; Start the programming sequence<br>; Required delays<br>; and wait for it to be<br>; completed |

|                                   |                                                    |                                                                                                 |

#### EXAMPLE 6-2: INITIATING A PROGRAMMING SEQUENCE

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER (CONTINUED)

| bit 5 | SWDTEN: Software Enable/Disable of WDT bit <sup>(4)</sup>                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = WDT is enabled                                                                                                                    |

|       | 0 = WDT is disabled                                                                                                                   |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit <sup>(1)</sup>                                                                                 |

|       | <ul><li>1 = WDT time-out has occurred</li><li>0 = WDT time-out has not occurred</li></ul>                                             |

| bit 3 | SLEEP: Wake from Sleep Flag bit <sup>(1)</sup>                                                                                        |

|       | <ul><li>1 = Device has been in Sleep mode</li><li>0 = Device has not been in Sleep mode</li></ul>                                     |

| bit 2 | IDLE: Wake-up from Idle Flag bit <sup>(1)</sup>                                                                                       |

|       | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                                       |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                                                                          |

|       | <ul><li>1 = A Brown-out Reset has occurred (also set after a Power-on Reset)</li><li>0 = A Brown-out Reset has not occurred</li></ul> |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                                                                                    |

|       | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                                     |

| Noto  | 1. All of the Depart status hits may be set or cleared in software. Setting one of                                                    |

- 2: If the LPCFG Configuration bit is '1' (unprogrammed), the retention regulator is disabled and the RETEN bit has no effect. Retention mode preserves the SRAM contents during Sleep.

- **3:** Re-enabling the regulator after it enters Standby mode will add a delay, TVREG, when waking up from Sleep. Applications that do not use the voltage regulator should set this bit to prevent this delay from occurring.

- 4: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- 5: The BOREN<1:0> (FPOR<1:0>) Configuration bits must be set to '01' in order for SBOREN to have an effect.

| Flag Bit          | Setting Event                                     | Clearing Event                  |

|-------------------|---------------------------------------------------|---------------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                             |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                             |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                             |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                             |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                             |

| WDTO (RCON<4>)    | WDT Time-out                                      | CLRWDT, PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #0 Instruction                             | POR                             |

| IDLE (RCON<2>)    | PWRSAV #1 Instruction                             | POR                             |

| BOR (RCON<1>)     | POR, BOR                                          |                                 |

| POR (RCON<0>)     | POR                                               |                                 |

#### TABLE 7-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

Note 1: All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

| REGISTER 8-1: | SR: ALU STATUS REGISTER <sup>(1)</sup> |

|---------------|----------------------------------------|

|---------------|----------------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   |     | —   | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| 011        | = CPU Interrupt Priority Level is 6 (14)<br>= CPU Interrupt Priority Level is 5 (13)<br>= CPU Interrupt Priority Level is 4 (12)<br>= CPU Interrupt Priority Level is 3 (11)                             |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 010<br>001 | <ul> <li>CPU Interrupt Priority Level is 3 (11)</li> <li>CPU Interrupt Priority Level is 2 (10)</li> <li>CPU Interrupt Priority Level is 1 (9)</li> <li>CPU Interrupt Priority Level is 0 (8)</li> </ul> |

**Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> Status bits are concatenated with the IPL3 Status bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

### REGISTER 9-8: REFOTRIML: REFERENCE OSCILLATOR TRIM REGISTER LOW

| R/W-0         | R/W-0      | R/W-0            | R/W-0         | R/W-0                              | R/W-0        | R/W-0              | R/W-0     |  |  |

|---------------|------------|------------------|---------------|------------------------------------|--------------|--------------------|-----------|--|--|

|               |            |                  | ROTE          | RIM<0:7>                           |              |                    |           |  |  |

| bit 15        |            |                  |               |                                    |              |                    | bit 8     |  |  |

|               |            |                  |               |                                    |              |                    |           |  |  |

| R/W-0         | U-0        | U-0              | U-0           | U-0                                | U-0          | U-0                | U-0       |  |  |

| ROTRIM8       | —          | —                | —             | —                                  | —            | —                  | —         |  |  |

| bit 7         |            |                  |               |                                    |              |                    | bit C     |  |  |

|               |            |                  |               |                                    |              |                    |           |  |  |

| Legend:       |            |                  |               |                                    |              |                    |           |  |  |

| R = Readable  | e bit      | W = Writable I   | oit           | U = Unimplemented bit, read as '0' |              |                    |           |  |  |

| -n = Value at | POR        | '1' = Bit is set |               | '0' = Bit is cleared               |              | x = Bit is unknown |           |  |  |

|               |            |                  |               |                                    |              |                    |           |  |  |

| bit 15-7      | ROTRIM<0:8 | B>: REFO Trim b  | oits          |                                    |              |                    |           |  |  |

|               |            |                  |               | the RODIVx valu<br>the RODIVx val  |              | period of the RE   | FO clock. |  |  |

|               | 000000001  | = 1/512 (0.0019  | 53125 divisoi | r added to the R                   | ODIVx value) |                    |           |  |  |

|               | 00000010   | = 2/512 (0.0039  | 0625 divisor  | added to the RO                    | DIVx value)  |                    |           |  |  |

|               | •          |                  |               |                                    |              |                    |           |  |  |

|               | •          |                  |               |                                    |              |                    |           |  |  |

|               | 100000000  | = 256/512 (0.50  | 00 divisor ad | ded to the RODI                    | Vx value)    |                    |           |  |  |

|               | •          |                  |               |                                    |              |                    |           |  |  |

|               | •          |                  |               |                                    |              |                    |           |  |  |

|               | 111111110  | - 510/512 (0.00  | 600375 divis  | or added to the F                  |              | <b>`</b>           |           |  |  |

111111110 = 510/512 (0.99609375 divisor added to the RODIVx value) 111111111 = 511/512 (0.998046875 divisor added to the RODIVx value)

bit 6-0 Unimplemented: Read as '0'

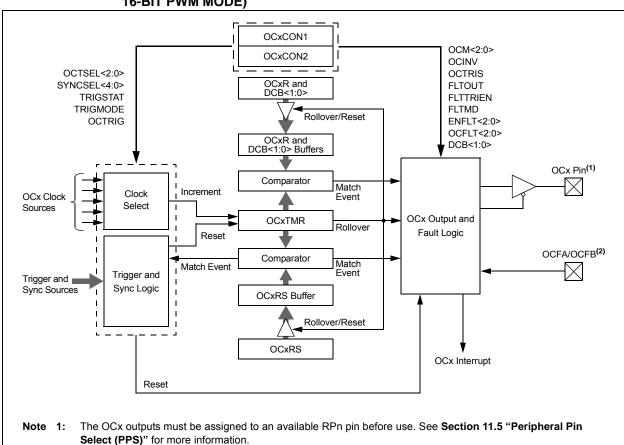

## FIGURE 15-2: OUTPUT COMPARE x BLOCK DIAGRAM (DOUBLE-BUFFERED, 16-BIT PWM MODE)

2: The OCFA/OCFB Fault inputs must be assigned to an available RPn/RPIn pin before use. See Section 11.5 "Peripheral Pin Select (PPS)" for more information.

### 15.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timer Period register. The PWM period can be calculated using Equation 15-1.

### EQUATION 15-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1 \bullet TCY \bullet (Timer Prescale Value)]$

Where: PWM Frequency = 1/[PWM Period]

**Note 1:** Based on TCY = TOSC \* 2; Doze mode and PLL are disabled.

**Note:** A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7, written into the PRy register, will yield a period consisting of 8 time base cycles.

## REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 8 |    | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                                      |

|-------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |    | 1 = Transmit happens on transition from active clock state to Idle clock state                                                                                                                                                      |

|       |    | 0 = Transmit happens on transition from Idle clock state to active clock state                                                                                                                                                      |

| bit 7 |    | SSEN: Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                                           |

|       |    | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select input<br>0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) |

| bit 6 |    | CKP: SPIx Clock Polarity Select bit                                                                                                                                                                                                 |

|       |    | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                            |

| bit 5 |    | MSTEN: Master Mode Enable bit                                                                                                                                                                                                       |

|       |    | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                                   |

| bit 4 |    | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                                 |

|       |    | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                                |

| bit 3 |    | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                                |

|       |    | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                                |

| bit 2 |    | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                                      |

|       |    | 1 = MCLK is used by the BRG<br>0 = PBCLK is used by the BRG                                                                                                                                                                         |

| bit 1 |    | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                             |

|       |    | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                                  |

| bit 0 |    | ENHBUF: Enhanced Buffer Mode Enable bit                                                                                                                                                                                             |

|       |    | <ul> <li>1 = Enhanced Buffer mode is enabled</li> <li>0 = Enhanced Buffer mode is disabled</li> </ul>                                                                                                                               |

| Note  | 1: | When AUDEN = 1, this module functions as if CKE = 0, regardless of its actual value.                                                                                                                                                |

|       | 2: | When FRMEN = 1. SSEN is not used.                                                                                                                                                                                                   |

- 3: MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

#### REGISTER 17-4: SPIx STATL: SPIx STATUS REGISTER LOW

| U-0    | U-0 | U-0 | R/C-0, HS | R-0, HSC | U-0 | U-0 | R-0, HSC              |

|--------|-----|-----|-----------|----------|-----|-----|-----------------------|

| _      | —   | _   | FRMERR    | SPIBUSY  | —   | —   | SPITUR <sup>(1)</sup> |

| bit 15 |     |     |           |          |     |     | bit 8                 |

| R-0, HSC  | R/C-0, HS | R-1, HSC | U-0 | R-1, HSC | U-0 | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|-----|----------|-----|----------|----------|

| SRMT      | SPIROV    | SPIRBE   |     | SPITBE   | —   | SPITBF   | SPIRBF   |

| bit 7 bit |           |          |     |          |     |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         | x = Bit is unknown                    |  |

|-------------------|-------------------|------------------------------------|---------------------------------------|--|

| R = Readable bit  | W = Writable bit  | '0' = Bit is cleared               | HSC = Hardware Settable/Clearable bit |  |

| -n = Value at POR | '1' = Bit is set  | U = Unimplemented bit, read as '0' |                                       |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | FRMERR: SPIx Frame Error Status bit                                                                                                                                                            |

|           | <ul><li>1 = Frame error is detected</li><li>0 = No frame error is detected</li></ul>                                                                                                           |

| bit 11    | SPIBUSY: SPIx Activity Status bit                                                                                                                                                              |

|           | <ul><li>1 = Module is currently busy with some transactions</li><li>0 = No ongoing transactions (at time of read)</li></ul>                                                                    |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 8     | SPITUR: SPIx Transmit Underrun Status bit <sup>(1)</sup>                                                                                                                                       |

|           | <ul> <li>1 = Transmit buffer has encountered a Transmit Underrun condition</li> <li>0 = Transmit buffer does not have a Transmit Underrun condition</li> </ul>                                 |

| bit 7     | SRMT: Shift Register Empty Status bit                                                                                                                                                          |

|           | <ul> <li>1 = No current or pending transactions (i.e., neither SPIxTXB or SPIxTXSR contains data to transmit)</li> <li>0 = Current or pending transactions</li> </ul>                          |

| bit 6     | SPIROV: SPIx Receive Overflow Status bit                                                                                                                                                       |

|           | <ul> <li>1 = A new byte/half-word/word has been completely received when the SPIxRXB is full</li> <li>0 = No overflow</li> </ul>                                                               |

| bit 5     | SPIRBE: SPIx RX Buffer Empty Status bit                                                                                                                                                        |

|           | 1 = RX buffer is empty<br>0 = RX buffer is not empty                                                                                                                                           |

|           | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIxBUF is read from, reading SPIxRXB. Automatically cleared in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. |

|           | Enhanced Buffer Mode:<br>Indicates RXELM<5:0> = 6'b000000.                                                                                                                                     |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3     | SPITBE: SPIx Transmit Buffer Empty Status bit                                                                                                                                                  |

|           | 1 = SPIxTXB is empty<br>0 = SPIxTXB is not empty                                                                                                                                               |

|           | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Automatically cleared in hardware when SPIxBUF is written, loading SPIxTXB.   |

|           | Enhanced Buffer Mode:<br>Indicates TXELM<5:0> = 6'b000000.                                                                                                                                     |

|           |                                                                                                                                                                                                |

**Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

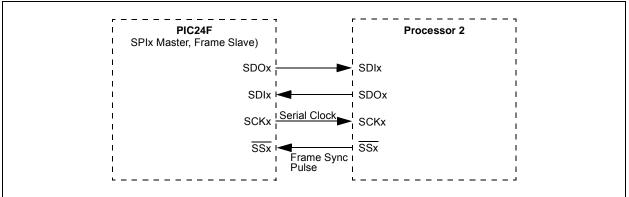

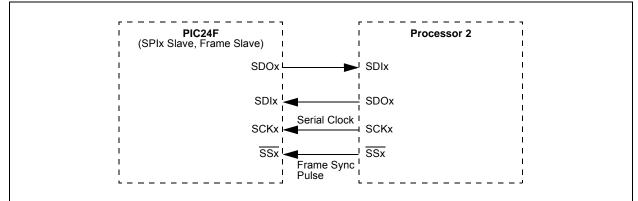

#### FIGURE 17-5: SPIX MASTER, FRAME SLAVE CONNECTION DIAGRAM

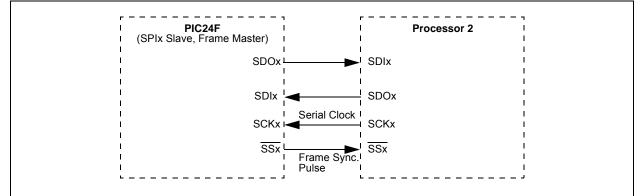

### FIGURE 17-7: SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

### EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

$Baud Rate = \frac{FPB}{(2 * (SPIxBRG + 1))}$ Where: FPB is the Peripheral Bus Clock Frequency.

## REGISTER 20-6: PMCSxBS: EPMP CHIP SELECT x BASE ADDRESS REGISTER<sup>(2)</sup>

| R/W <sup>(1)</sup>                                                         | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup>     | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> |

|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|------------------------|--------------------|--------------------|--------------------|

|                                                                            |                    |                    | BASE               | <23:16>                |                    |                    |                    |

| bit 15                                                                     |                    |                    |                    |                        |                    |                    | bit 8              |

| R/W <sup>(1)</sup>                                                         | U-0                | U-0                | U-0                | R/W <sup>(1)</sup>     | U-0                | U-0                | U-0                |

| BASE15                                                                     | _                  | —                  |                    | BASE11                 | —                  | _                  | _                  |

| bit 7                                                                      |                    |                    |                    |                        |                    |                    | bit 0              |

|                                                                            |                    |                    |                    |                        |                    |                    |                    |

| Legend:                                                                    |                    |                    |                    |                        |                    |                    |                    |

| R = Readable                                                               | bit                | W = Writable b     | bit                | U = Unimplem           | nented bit, read   | d as '0'           |                    |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                    |                    |                    |                        |                    | nown               |                    |

|                                                                            |                    |                    |                    |                        |                    |                    |                    |

| bit 15-7                                                                   | BASE<23:1          | 5>: Chip Select >  | Base Addres        | ss bits <sup>(1)</sup> |                    |                    |                    |

| hit 6.4 Inimplemented: Read as '0'                                         |                    |                    |                    |                        |                    |                    |                    |

bit 6-4 Unimplemented: Read as '0'

bit 3 BASE11: Chip Select x Base Address bit<sup>(1)</sup>

bit 2-0 Unimplemented: Read as '0'

**Note 1:** The value at POR is 0080h for PMCS1BS and 8080h for PMCS2BS.

2: If the whole PMCS2BS register is written together as 0x0000, then the last EDS address for the Chip Select 1 will be FFFFFh. In this case, Chip Select 2 should not be used. PMCS1BS has no such feature.

#### 21.3.2 RTCVAL REGISTER MAPPINGS

## REGISTER 21-4: RTCCON2H: RTCC CONTROL REGISTER 2 (HIGH)<sup>(1)</sup>

| R/W-0   | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-------|-------|-------|-------|-------|-------|-------|

|         |       |       | DIV<  | 15:8> |       |       |       |

| bit 15  |       |       |       |       |       |       | bit 8 |

|         |       |       |       |       |       |       |       |

| R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|         |       |       | DIV   | <7:0> |       |       |       |

| bit 7   |       |       |       |       |       |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

|         |       |       |       |       |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 DIV<15:0>: Clock Divide bits

Sets the period of the clock divider counter; value should cause a nominal 1/2 second underflow.

**Note 1:** A write to this register is only allowed when WRLOCK = 1.

| R/W-0               | R/W-0                                                                                                                            | R/W-0            | R/W-0    | R/W-0             | R/W-0           | R/W-0          | R/W-0    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-------------------|-----------------|----------------|----------|

| PWCSAMP7            | PWCSAMP6                                                                                                                         | PWCSAMP5         | PWCSAMP4 | PWCSAMP3          | PWCSAMP2        | PWCSAMP1       | PWCSAMP0 |

| bit 15              |                                                                                                                                  |                  |          |                   |                 |                | bit 8    |

|                     |                                                                                                                                  |                  |          |                   |                 |                |          |

| R/W-0               | R/W-0                                                                                                                            | R/W-0            | R/W-0    | R/W-0             | R/W-0           | R/W-0          | R/W-0    |

| PWCSTAB7            | PWCSTAB6                                                                                                                         | PWCSTAB5         | PWCSTAB4 | PWCSTAB3          | PWCSTAB2        | PWCSTAB1       | PWCSTAB0 |

| bit 7               |                                                                                                                                  |                  |          |                   |                 |                | bit 0    |

|                     |                                                                                                                                  |                  |          |                   |                 |                |          |

| Legend:             |                                                                                                                                  |                  |          |                   |                 |                |          |

| R = Readable        | bit                                                                                                                              | W = Writable b   | bit      | U = Unimplem      | ented bit, read | as '0'         |          |

| -n = Value at P     | POR                                                                                                                              | '1' = Bit is set |          | '0' = Bit is clea | red             | x = Bit is unk | nown     |

| bit 15-8<br>bit 7-0 | <pre>11111111 = Sample window is always enabled, even when PWCEN = 0 11111110 = Sample window is 254 TPwccLk clock periods</pre> |                  |          |                   |                 |                |          |

## REGISTER 21-5: RTCCON3L: RTCC CONTROL REGISTER 3 (LOW)

Note 1: The sample window always starts when the stability window timer expires, except when its initial value is 00h.

| U-0           | U-0                           | R/W-0            | R/W-0            | R/W-0                | R/W-0            | R/W-0              | R/W-0       |  |

|---------------|-------------------------------|------------------|------------------|----------------------|------------------|--------------------|-------------|--|

| —             | —                             | HRTEN1           | HRTEN0           | HRONE3               | HRONE2           | HRONE1             | HRONE0      |  |

| bit 15        |                               | •                | •                | ·                    | •                |                    | bit 8       |  |

|               |                               |                  |                  |                      |                  |                    |             |  |

| U-0           | R/W-0                         | R/W-0            | R/W-0            | R/W-0                | R/W-0            | R/W-0              | R/W-0       |  |

|               | MINTEN2                       | MINTEN1          | MINTEN0          | MINONE3              | MINONE2          | MINONE1            | MINONE0     |  |

| bit 7         |                               | •                |                  | •                    | •                |                    | bit (       |  |

|               |                               |                  |                  |                      |                  |                    |             |  |

| Legend:       |                               |                  |                  |                      |                  |                    |             |  |

| R = Readable  | e bit                         | W = Writable     | bit              | U = Unimplem         | nented bit, read | d as '0'           |             |  |

| -n = Value at | POR                           | '1' = Bit is set |                  | '0' = Bit is cleared |                  | x = Bit is unknown |             |  |

|               |                               |                  |                  |                      |                  |                    |             |  |

| bit 15-14     | Unimplemen                    | ted: Read as '   | 0'               |                      |                  |                    |             |  |

| bit 13-12     | HRTEN<1:0>                    | : Binary Codeo   | d Decimal Valu   | e of Hours '10'      | Digit bits       |                    |             |  |

|               | Contains a va                 | lue from 0 to 2  |                  |                      |                  |                    |             |  |

| bit 11-8      | HRONE<3:0>                    | Binary Code      | d Decimal Valu   | e of Hours '1' I     | Digit bits       |                    |             |  |

|               | Contains a va                 | lue from 0 to 9  |                  |                      |                  |                    |             |  |

| bit 7         | Unimplemen                    | ted: Read as '   | 0'               |                      |                  |                    |             |  |

| bit 6-4       | MINTEN<2:0                    | >: Binary Code   | d Decimal Valu   | ue of Minutes '1     | 0' Digit bits    |                    |             |  |

|               | Contains a value from 0 to 5. |                  |                  |                      |                  |                    |             |  |