#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT               |

| Number of I/O              | 22                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

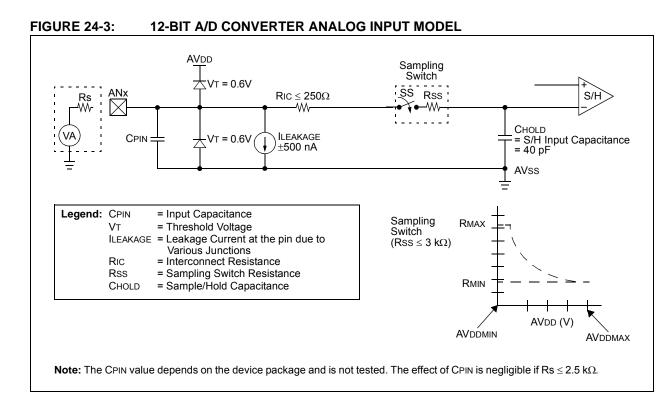

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

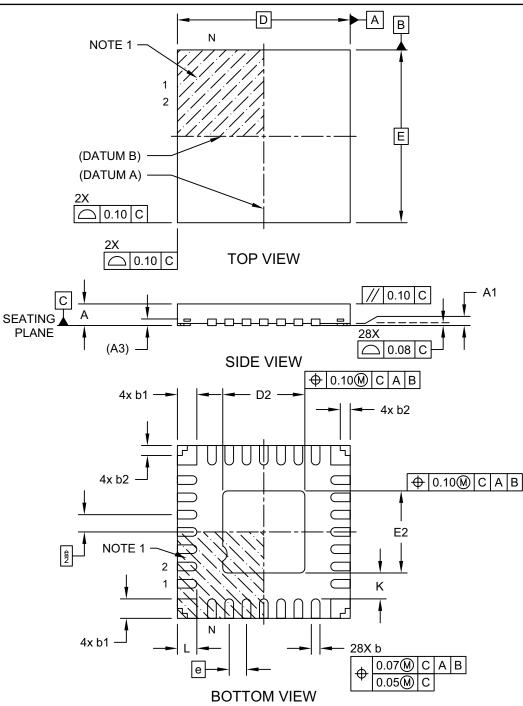

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga702t-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin                  | Pin Number/Grid Locator     |                     | Innut          |                    |     |                 |                                                                             |

|----------------------|-----------------------------|---------------------|----------------|--------------------|-----|-----------------|-----------------------------------------------------------------------------|

| Function             | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN | 44-Pin<br>TQFP | 48-Pin<br>QFN/TQFP | I/O | Input<br>Buffer | Description                                                                 |

| PGC1                 | 5                           | 2                   | 22             | 24                 | I   | ST              | ICSP™ Programming Clock                                                     |

| PGC2                 | 22                          | 19                  | 9              | 10                 | Ι   | ST              |                                                                             |

| PGC3                 | 15                          | 12                  | 42             | 46                 | Ι   | ST              |                                                                             |

| PGD1                 | 4                           | 1                   | 21             | 23                 | I/O | DIG/ST          | ICSP Programming Data                                                       |

| PGD2                 | 21                          | 18                  | 8              | 9                  | I/O | DIG/ST          |                                                                             |

| PGD3                 | 14                          | 11                  | 41             | 45                 | I/O | DIG/ST          |                                                                             |

| PMA0                 | —                           | —                   | 3              | 3                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<0>/<br>Address Latch Low                       |

| PMA1                 | —                           | —                   | 2              | 2                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<1>/<br>Address Latch High                      |

| PMA2                 | _                           | —                   | 12             | 13                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<2>                                             |

| PMA3                 | _                           | _                   | 38             | 41                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<3>                                             |

| PMA4                 | —                           | _                   | 37             | 40                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<4>                                             |

| PMA5                 | _                           | _                   | 4              | 4                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<5>                                             |

| PMA6                 | _                           | _                   | 5              | 5                  | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<6>                                             |

| PMA7                 | —                           | —                   | 13             | 14                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<7>                                             |

| PMA8                 | —                           | —                   | 32             | 35                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<8>                                             |

| PMA9                 | _                           | —                   | 35             | 38                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<9>                                             |

| PMA14/PMCS/<br>PMCS1 | _                           | —                   | 15             | 16                 | I/O | DIG/ST/<br>TTL  | Parallel Master Port Address<14>/<br>Slave Chip Select/Chip Select 1 Strobe |

#### TABLE 1-3: PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

© 2016 Microchip Technology Inc.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

## 2.1 Basic Connection Requirements

Getting started with the PIC24FJ256GA705 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

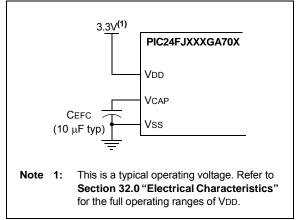

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

VCAP pin (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGCx/PGDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

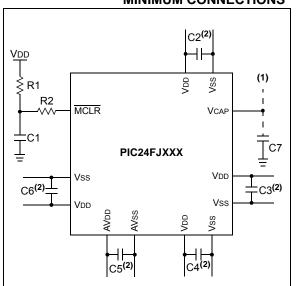

The minimum mandatory connections are shown in Figure 2-1.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu$ F, 50V ceramic

C7: 10 µF, 16V or greater, ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for an explanation of voltage regulator pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS39712), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

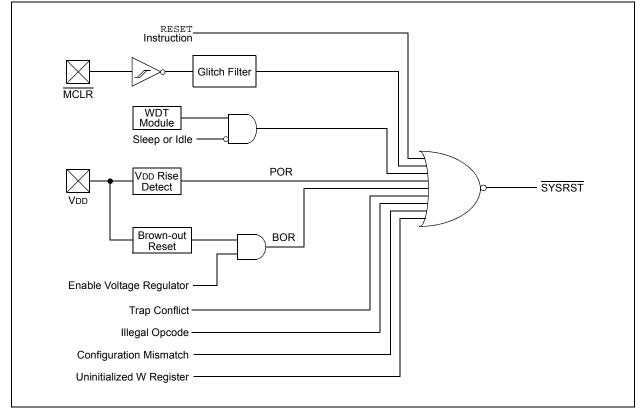

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

#### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

© 2016 Microchip Technology Inc.

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes   |

|----------------------------------------------------|-------------------|-------------|------------|---------|

| Oscillator with Frequency Division (OSCFDIV)       | Internal/External | 11          | 111        | 1, 2, 3 |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 3       |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 11          | 100        | 3       |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |         |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |         |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |         |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |         |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |         |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 3       |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 3       |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** The input oscillator to the OSCFDIV Clock mode is determined by the RCDIV<2:0> (CLKDIV<10:8) bits. At POR, the default value selects the FRC module.

- 2: This is the default Oscillator mode for an unprogrammed (erased) device.

- 3: OSCO pin function is determined by the OSCIOFCN Configuration bit.

## 9.3 Control Registers

The operation of the oscillator is controlled by five Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

- OSCDIV

- OSCFDIV

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. OSCCON is protected by a write lock to prevent inadvertent clock switches. See **Section 9.4** "**Clock Switching Operation**" for more information. The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscalers for the OSCFDIV Clock mode and the PLL module.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 1.5\%$ .

The OSCDIV and OSCFDIV registers provide control for the system oscillator frequency divider.

#### REGISTER 11-31: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0                                | U-0 | U-0                                     | U-0                                | U-0   | U-0   | U-0   | U-0   |

|------------------------------------|-----|-----------------------------------------|------------------------------------|-------|-------|-------|-------|

| —                                  |     | —                                       |                                    | _     | —     | _     | —     |

| bit 15                             |     |                                         |                                    |       |       |       | bit 8 |

|                                    |     |                                         |                                    |       |       |       |       |

| U-0                                | U-0 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| _                                  | —   | SS3R5                                   | SS3R4                              | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7                              |     |                                         |                                    |       |       |       | bit 0 |

|                                    |     |                                         |                                    |       |       |       |       |

| Legend:                            |     |                                         |                                    |       |       |       |       |

| R = Readable bit W = Writable bit  |     | oit                                     | U = Unimplemented bit, read as '0' |       |       |       |       |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown  |       |       |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS3IN) to Corresponding RPn or RPIn Pin bits

## 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Output Compare with Dedicated Timer" (DS70005159), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

All devices in the PIC24FJ256GA705 family feature three independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-Configurable for 32-Bit Operation in All modes by Cascading Two Adjacent modules

- Synchronous and Trigger modes of Output Compare Operation with up to 31 User-Selectable Sync/Trigger Sources Available

- Two Separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for Greater Flexibility in Generating Pulses of Varying Widths

- Configurable for Single Pulse or Continuous Pulse Generation on an Output Event, or Continuous PWM Waveform Generation

- Up to 6 Clock Sources Available for Each module, Driving a Separate Internal 16-Bit Counter

### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected Sync source, the module's internal counter is reset. In Trigger mode, the module waits for a Sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSEL<4:0> bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the Sync/Trigger source.

#### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-Bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module (OCy) provides the Most Significant 16 bits. Wrap-arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more details on cascading, refer to the *"dsPIC33/ PIC24 Family Reference Manual"*, **"Output Compare with Dedicated Timer"** (DS70005159).

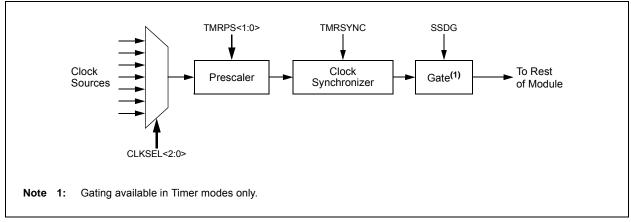

#### 16.1 Time Base Generator

The Timer Clock Generator (TCG) generates a clock for the module's internal time base using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 16-2. There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator and the TCLKI external clock inputs. The system clock is the default source (CLKSEL<2:0> = 000). On PIC24FJ256GA705 family devices, clock sources to the MCCPx module must be synchronized with the system clock. As a result, when clock sources are selected, clock input timing restrictions or module operating restrictions may exist.

### FIGURE 16-2: TIMER CLOCK GENERATOR

| R/W-0                 | R/W-0                                                                                                                                    | U-0                                                                                  | U-0            | R/W-0                           | R/W-0               | R/W-0               | R/W-0               |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|---------------------------------|---------------------|---------------------|---------------------|--|--|--|

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                                                                                                                    | _                                                                                    |                | OPS3 <sup>(3)</sup>             | OPS2 <sup>(3)</sup> | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |  |  |  |

| bit 15                |                                                                                                                                          |                                                                                      |                |                                 |                     |                     | bit 8               |  |  |  |

| R/W-0                 | R/W-0                                                                                                                                    | R/W-0                                                                                | R/W-0          | R/W-0                           | R/W-0               | R/W-0               | R/W-0               |  |  |  |

| TRIGEN                | ONESHOT                                                                                                                                  | ALTSYNC                                                                              | SYNC4          | SYNC3                           | SYNC2               | SYNC1               | SYNC0               |  |  |  |

| bit 7                 |                                                                                                                                          |                                                                                      |                |                                 |                     |                     | bit                 |  |  |  |

| Legend:               |                                                                                                                                          |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

| R = Readable          | e bit                                                                                                                                    | W = Writable I                                                                       | oit            | U = Unimplem                    | nented bit, rea     | d as '0'            |                     |  |  |  |

| -n = Value at         |                                                                                                                                          | '1' = Bit is set                                                                     |                | '0' = Bit is clea               |                     | x = Bit is unkr     | iown                |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

| bit 15                | OPSSRC: Ou                                                                                                                               | Itput Postscaler                                                                     | Source Selec   | ct bit <sup>(1)</sup>           |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                | er output events                | 6                   |                     |                     |  |  |  |

|                       | • •                                                                                                                                      | ostscaler scales                                                                     |                | terrupt events                  |                     |                     |                     |  |  |  |

| bit 14                |                                                                                                                                          | trigger Enable                                                                       |                |                                 | 1                   |                     |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                | e TRIGEN bit =<br>en the TRIGEN |                     |                     |                     |  |  |  |

| bit 13-12             | <ul> <li>0 = Time base may not be retriggered when the TRIGEN bit = 1</li> <li>Unimplemented: Read as '0'</li> </ul>                     |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

| bit 11-8              | •                                                                                                                                        |                                                                                      |                | cale Select bits <sup>(3</sup>  | 3)                  |                     |                     |  |  |  |

|                       | <b>OPS3&lt;3:0&gt;:</b> CCPx Interrupt Output Postscale Select bits <sup>(3)</sup><br>1111 = Interrupt every 16th time base period match |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

|                       | 1110 = Interro                                                                                                                           | upt every 15th t                                                                     | ime base peri  | od match                        |                     |                     |                     |  |  |  |

|                       | <br>0100 = Intern                                                                                                                        | upt every 5th tir                                                                    | na hasa nario  | d match                         |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      | •              | d match or 4th i                | nput capture e      | event               |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                | d match or 3rd i                |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                | od match or 2nd                 |                     |                     |                     |  |  |  |

| bit 7                 |                                                                                                                                          | -                                                                                    | -              | od match or inpu                | li capiule eve      | i it                |                     |  |  |  |

|                       |                                                                                                                                          | <b>RIGEN:</b> CCPx Trigger Enable bit<br>= Trigger operation of time base is enabled |                |                                 |                     |                     |                     |  |  |  |

|                       | 0 = Trigger operation of time base is disabled                                                                                           |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

| bit 6                 | ONESHOT: C                                                                                                                               | ne-Shot Mode                                                                         | Enable bit     |                                 |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          | t Trigger mode<br>t Trigger mode                                                     |                | igger mode dura                 | ation is set by     | OSCNT<2:0>          |                     |  |  |  |

| bit 5                 | ALTSYNC: C                                                                                                                               | CPx Clock Sele                                                                       | ect bit        |                                 |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          |                                                                                      |                | dule synchroniza                |                     |                     |                     |  |  |  |

|                       |                                                                                                                                          | -                                                                                    |                | gnal is the Time                | Base Reset/re       | ollover event       |                     |  |  |  |

| bit 4-0               | SYNC<4:0>: CCPx Synchronization Source Select bits                                                                                       |                                                                                      |                |                                 |                     |                     |                     |  |  |  |

|                       | See Table 16-                                                                                                                            | 5 for the definit                                                                    | ion of inputs. |                                 |                     |                     |                     |  |  |  |

| Note 1: Th            | is control bit ha                                                                                                                        | is no function ir                                                                    | Input Captur   | e modes.                        |                     |                     |                     |  |  |  |

| 2: Th                 | is control bit ha                                                                                                                        | is no function w                                                                     | hen TRIGEN     | = 0.                            |                     |                     |                     |  |  |  |

|                       | · ·                                                                                                                                      | •                                                                                    | 5 to 1:16 (010 | 00-1111), will re               | sult in a FIFO      | buffer overflow f   | or                  |  |  |  |

| Inr                   | out Canture mo                                                                                                                           | 169                                                                                  |                |                                 |                     |                     |                     |  |  |  |

### REGISTER 16-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

Input Capture modes.

## 17.1 Master Mode Operation

Perform the following steps to set up the SPIx module for Master mode operation:

- 1. Disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- If SPIx interrupts are not going to be used, skip this step. Otherwise, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and sub-priority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Write the Baud Rate register, SPIxBRGL.

- 7. Clear the SPIROV bit (SPIxSTATL<6>).

- 8. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 1.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 10. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL/H registers.

## 17.2 Slave Mode Operation

The following steps are used to set up the SPIx module for the Slave mode of operation:

- 1. If using interrupts, disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- 5. If using interrupts, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and sub-priority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 0.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 9. Transmission (and reception) will start as soon as the master provides the serial clock.

The following additional features are provided in Slave mode:

- Slave Select Synchronization:

- The SSx pin allows a Synchronous Slave mode. If the SSEN bit (SPIxCON1L<7>) is set, transmission and reception are enabled in Slave mode only if the SSx pin is driven to a low state. The port output or other peripheral outputs must not be driven in order to allow the SSx pin to function as an input. If the SSEN bit is set and the SSx pin is driven high, the SDOx pin is no longer driven and will tri-state, even if the module is in the middle of a transmission. An aborted transmission will be tried again the next time the SSx pin is driven low using the data held in the SPIxTXB register. If the SSEN bit is not set, the SSx pin does not affect the module operation in Slave mode.

- SPITBE Status Flag Operation: The SPITBE bit (SPIxSTATL<3>) has a different function in the Slave mode of operation. The following describes the function of SPITBE for various settings of the Slave mode of operation:

- If SSEN (SPIxCON1L<7>) is cleared, the SPITBE bit is cleared when SPIxBUF is loaded by the user code. It is set when the module transfers SPIxTXB to SPIxTXSR. This is similar to the SPITBE bit function in Master mode.

- If SSEN is set, SPITBE is cleared when SPIxBUF is loaded by the user code. However, it is set only when the SPIx module completes data transmission. A transmission will be aborted when the SSx pin goes high and may be retried at a later time. So, each data word is held in SPIxTXB until all bits are transmitted to the receiver.

## 18.2 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 18-1.

# EQUATION 18-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1,2,3)</sup>

$FSCL = \frac{FCY}{(I2CxBRG + 2) * 2}$

or:

$$I2CxBRG = \left[\frac{FCY}{(FSCL * 2)} - 2\right]$$

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various systemlevel parameters. The actual clock rate should be measured in its intended application.

**3:** BRG values of 0 and 1 are forbidden.

## 18.3 Slave Address Masking

The I2CxMSK register (Register 18-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '0010000000', the slave module will detect both addresses, '000000000' and '001000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

**Note:** As a result of changes in the I<sup>2</sup>C protocol, the addresses in Table 18-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required System FSCL | Fox    | I2CxB     | RG Value      |             |

|----------------------|--------|-----------|---------------|-------------|

|                      | FCY    | (Decimal) | (Hexadecimal) | Actual FscL |

| 100 kHz              | 16 MHz | 78        | 4E            | 100 kHz     |

| 100 kHz              | 8 MHz  | 38        | 26            | 100 kHz     |

| 100 kHz              | 4 MHz  | 18        | 12            | 100 kHz     |

| 400 kHz              | 16 MHz | 18        | 12            | 400 kHz     |

| 400 kHz              | 8 MHz  | 8         | 8             | 400 kHz     |

| 400 kHz              | 4 MHz  | 3         | 3             | 400 kHz     |

| 1 MHz                | 16 MHz | 6         | 6             | 1.000 MHz   |

| 1 MHz                | 8 MHz  | 2         | 2             | 1.000 MHz   |

## TABLE 18-1: I2Cx CLOCK RATES<sup>(1,2)</sup>

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

2: These clock rate values are for guidance only. The actual clock rate can be affected by various system-level parameters. The actual clock rate should be measured in its intended application.

| Slave Address | R/W Bit | Description                            |  |  |  |

|---------------|---------|----------------------------------------|--|--|--|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |  |  |  |

| 0000 000      | 1       | Start Byte                             |  |  |  |

| 0000 001      | x       | Cbus Address                           |  |  |  |

| 0000 01x      | х       | Reserved                               |  |  |  |

| 0000 1xx      | x       | HS Mode Master Code                    |  |  |  |

| 1111 0xx      | x       | 10-Bit Slave Upper Byte <sup>(3)</sup> |  |  |  |

| 1111 1xx      | х       | Reserved                               |  |  |  |

Note 1: The address bits listed here will never cause an address match independent of address mask settings.

- 2: This address will be Acknowledged only if GCEN = 1.

- 3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

| R/W-0      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HC, R/W-0                                                                                                                                                                                              | R/W-1                                                                                                                                                                                     | R/W-0                                                                                                                              | R/W-0                                                                                          | R/W-0                                                                    | R/W-0                                      |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|--|

| I2CEN      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I2CSIDL                                                                                                                                                                                                | SCLREL <sup>(1)</sup>                                                                                                                                                                     | STRICT                                                                                                                             | A10M                                                                                           | DISSLW                                                                   | SMEN                                       |  |

| bit 15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                           |                                                                                                                                    |                                                                                                | •                                                                        | bit                                        |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                           |                                                                                                                                    |                                                                                                |                                                                          |                                            |  |

| R/W-0      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                  | HC, R/W-0                                                                                                                                                                                 | HC, R/W-0                                                                                                                          | HC, R/W-0                                                                                      | HC, R/W-0                                                                | HC, R/W-0                                  |  |

| GCEN       | STREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ACKDT                                                                                                                                                                                                  | ACKEN                                                                                                                                                                                     | RCEN                                                                                                                               | PEN                                                                                            | RSEN                                                                     | SEN                                        |  |

| bit 7      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                           |                                                                                                                                    |                                                                                                |                                                                          | bit                                        |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                        |                                                                                                                                                                                           | 4                                                                                                                                  |                                                                                                |                                                                          |                                            |  |

| Legend:    | HC = Hardware Clearable bit<br>lable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                        |                                                                                                                                                                                           |                                                                                                                                    |                                                                                                |                                                                          |                                            |  |

| R = Reada  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                           |                                                                                                                                                                                           | •                                                                                                                                  |                                                                                                |                                                                          |                                            |  |

| -n = Value | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                       |                                                                                                                                                                                           | '0' = Bit is clea                                                                                                                  | ared                                                                                           | x = Bit is unkn                                                          | iown                                       |  |