Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 36                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 14x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256ga704-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                                               | PIC24FJ64GA702                                                                                                                                                 | PIC24FJ128GA702                | PIC24FJ256GA702 |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|--|--|

| Operating Frequency                                                    |                                                                                                                                                                | DC – 32 MHz                    |                 |  |  |

| Program Memory (bytes)                                                 | 64K                                                                                                                                                            | 128K                           | 256K            |  |  |

| Program Memory<br>(instruction words, 24 bits)                         | 22,528                                                                                                                                                         | 45,056                         | 88,064          |  |  |

| Data Memory (bytes)                                                    |                                                                                                                                                                | 16K                            |                 |  |  |

| Interrupt Sources<br>(soft vectors/NMI traps)                          |                                                                                                                                                                | 124                            |                 |  |  |

| I/O Ports                                                              |                                                                                                                                                                | Ports A, B                     |                 |  |  |

| Total I/O Pins                                                         |                                                                                                                                                                | 22                             |                 |  |  |

| Remappable Pins                                                        |                                                                                                                                                                | 18 (18 I/Os, 0 input only)     |                 |  |  |

| DMA                                                                    |                                                                                                                                                                | 1 6-channel                    |                 |  |  |

| 16-Bit Timers                                                          |                                                                                                                                                                | 3(1)                           |                 |  |  |

| Real-Time Clock and Calendar<br>(RTCC)                                 |                                                                                                                                                                | Yes                            |                 |  |  |

| Cyclic Redundancy Check (CRC)                                          |                                                                                                                                                                | Yes                            |                 |  |  |

| Input Capture Channels                                                 |                                                                                                                                                                | 3 <sup>(1)</sup>               |                 |  |  |

| Output Compare/PWM Channels                                            |                                                                                                                                                                | 3(1)                           |                 |  |  |

| Input Change Notification Interrupt                                    |                                                                                                                                                                | 21 (remappable pins)           |                 |  |  |

| Serial Communications:                                                 |                                                                                                                                                                |                                |                 |  |  |

| UART                                                                   |                                                                                                                                                                | 2(1)                           |                 |  |  |

| SPI (3-wire/4-wire)                                                    |                                                                                                                                                                | 3(1)                           |                 |  |  |

| I <sup>2</sup> C                                                       |                                                                                                                                                                | 2                              |                 |  |  |

| Configurable Logic Cell (CLC)                                          |                                                                                                                                                                | 2(1)                           |                 |  |  |

| Parallel Communications<br>(EPMP/PSP)                                  | No                                                                                                                                                             |                                |                 |  |  |

| Capture/Compare/PWM/Timer                                              |                                                                                                                                                                | 4 Multiple CCPs                |                 |  |  |

| Modules                                                                |                                                                                                                                                                | 1 (6-output), 3 (2-output)     |                 |  |  |

| JTAG Boundary Scan                                                     |                                                                                                                                                                | Yes                            |                 |  |  |

| 10/12-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) |                                                                                                                                                                | 10                             |                 |  |  |

| Analog Comparators                                                     |                                                                                                                                                                | 3                              |                 |  |  |

| CTMU Interface                                                         |                                                                                                                                                                | Yes                            |                 |  |  |

| Universal Serial Bus Controller                                        |                                                                                                                                                                | No                             |                 |  |  |

| Resets (and Delays)                                                    | Core POR, VDD POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                                |                 |  |  |

| Instruction Set                                                        | 76 Base Instru                                                                                                                                                 | uctions, Multiple Addressing M | lode Variations |  |  |

| Packages                                                               | 28-Pin (                                                                                                                                                       | QFN, UQFN, SOIC, SSOP an       | d SPDIP         |  |  |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJXXXGA702: 28-PIN DEVICES

**Note 1:** Some peripherals are accessible through remappable pins.

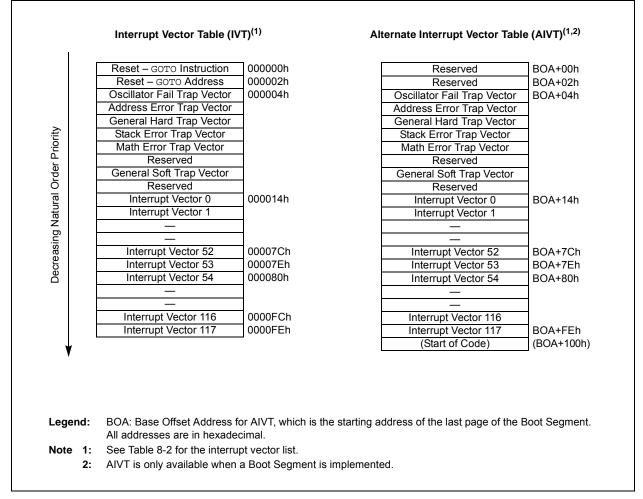

#### FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLES

#### TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source            |  |

|---------------|-------------|--------------|------------------------|--|

| 0             | 000004h     | BOA+04h      | Oscillator Failure     |  |

| 1             | 000006h     | BOA+06h      | Address Error          |  |

| 2             | 000008h     | BOA+08h      | General Hardware Error |  |

| 3             | 00000Ah     | BOA+0Ah      | Stack Error            |  |

| 4             | 00000Ch     | BOA+0Ch      | Math Error             |  |

| 5             | 00000Eh     | BOA+0Eh      | Reserved               |  |

| 6             | 000010h     | BOA+10h      | General Software Error |  |

| 7             | 000012h     | BOA+12h      | Reserved               |  |

**Legend:** BOA = Base Offset Address for AIVT segment, which is the starting address of the last page of the Boot Segment.

## REGISTER 8-2: CORCON: CPU CORE CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | -   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | R/W-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-------|-----|-------|

| —     | —   | —   | _   | IPL3 <sup>(2)</sup> | PSV   | —   | —     |

| bit 7 |     |     |     |                     |       |     | bit 0 |

| Legend:           | C = Clearable bit |                                        |                    |  |

|-------------------|-------------------|----------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | bit U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared                   | x = Bit is unknown |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 2 **PSV:** Not used as part of the interrupt module

bit 1-0 Unimplemented: Read as '0'

**Note 1:** For complete register details, see Register 3-2.

2: The IPL<2:0> Status bits are concatenated with the IPL3 Status bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1. User interrupts are disabled when IPL3 = 1.

| R/W-0        | U-0                                                                                                                      | U-0                                               | U-0                                                   | U-0               | U-0             | U-0             | U-0   |

|--------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| NSTDIS       |                                                                                                                          | —                                                 | —                                                     | —                 | —               | —               | —     |

| bit 15       |                                                                                                                          |                                                   |                                                       |                   |                 |                 | bit 8 |

|              |                                                                                                                          |                                                   |                                                       |                   |                 |                 |       |

| U-0          | U-0                                                                                                                      | U-0                                               | R/W-0                                                 | R/W-0             | R/W-0           | R/W-0           | U-0   |

|              |                                                                                                                          | _                                                 | MATHERR                                               | ADDRERR           | STKERR          | OSCFAIL         |       |

| bit 7        |                                                                                                                          |                                                   |                                                       |                   |                 |                 | bit ( |

|              |                                                                                                                          |                                                   |                                                       |                   |                 |                 |       |

| Legend:      |                                                                                                                          |                                                   |                                                       |                   |                 |                 |       |

| R = Readab   |                                                                                                                          | W = Writable                                      |                                                       | •                 | ented bit, read |                 |       |

| -n = Value a | t POR                                                                                                                    | '1' = Bit is se                                   | et                                                    | '0' = Bit is clea | red             | x = Bit is unkn | own   |

| bit 15       | 1 = Interrupt<br>0 = Interrupt                                                                                           | errupt Nesting<br>nesting is dis<br>nesting is en | abled<br>abled                                        |                   |                 |                 |       |

| bit 14-5     | -                                                                                                                        | nted: Read as                                     |                                                       |                   |                 |                 |       |

| bit 4        | 1 = Math err                                                                                                             | Math Error St<br>or trap has oc<br>or trap has nc | curred                                                |                   |                 |                 |       |

| bit 3        | ADDRERR: Address Error Trap Status bit<br>1 = Address error trap has occurred<br>0 = Address error trap has not occurred |                                                   |                                                       |                   |                 |                 |       |

| bit 2        | STKERR: Stack Error Trap Status bit<br>1 = Stack error trap has occurred<br>0 = Stack error trap has not occurred        |                                                   |                                                       |                   |                 |                 |       |

| bit 1        | 1 = Oscillato                                                                                                            | r failure trap h                                  | re Trap Status bi<br>nas occurred<br>nas not occurred | it                |                 |                 |       |

| bit 0        | Unimpleme                                                                                                                | nted: Read as                                     | <b>s</b> '0'                                          |                   |                 |                 |       |

|              |                                                                                                                          |                                                   |                                                       |                   |                 |                 |       |

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE REGISTER 1

| U-0          | U-0           | R/W-0            | R/W-0       | R/W-0             | U-0            | U-0            | U-0    |

|--------------|---------------|------------------|-------------|-------------------|----------------|----------------|--------|

|              |               | T3MD             | T2MD        | T1MD              | _              | _              |        |

| oit 15       |               |                  |             | 1                 |                |                | bit    |

|              |               |                  |             |                   |                |                |        |

| R/W-0        | R/W-0         | R/W-0            | R/W-0       | R/W-0             | U-0            | U-0            | R/W-0  |

| I2C1MD       | U2MD          | U1MD             | SPI2MD      | SPI1MD            | —              | —              | ADC1MD |

| bit 7        |               |                  |             |                   |                |                | bit    |

| Legend:      |               |                  |             |                   |                |                |        |

| R = Readab   | le bit        | W = Writable     | bit         | U = Unimplem      | ented bit, rea | d as '0'       |        |

| -n = Value a | t POR         | '1' = Bit is set |             | '0' = Bit is clea | ared           | x = Bit is unk | nown   |

| bit 15-14    | Unimplemen    | ted: Read as '   | 0'          |                   |                |                |        |

| bit 13       | -             | 3 Module Disat   |             |                   |                |                |        |

|              | 1 = Module is |                  |             |                   |                |                |        |

|              | -             | ower and clock   |             | enabled           |                |                |        |

| bit 12       | -             | 2 Module Disat   | ole bit     |                   |                |                |        |

|              | 1 = Module is |                  |             |                   |                |                |        |

|              |               | ower and clock   |             | enabled           |                |                |        |

| bit 11       | -             | 1 Module Disat   | ble bit     |                   |                |                |        |

|              | 1 = Module is | s disabled       |             | anabled           |                |                |        |

| bit 10-8     | -             | ted: Read as '   |             |                   |                |                |        |

| bit 7        | -             | 1 Module Disat   |             |                   |                |                |        |

|              | 1 = Module is |                  |             |                   |                |                |        |

|              |               | ower and clock   | sources are | enabled           |                |                |        |

| bit 6        |               | 2 Module Disa    |             |                   |                |                |        |

|              | 1 = Module is | s disabled       |             |                   |                |                |        |

|              | 0 = Module p  | ower and clock   | sources are | enabled           |                |                |        |

| bit 5        | U1MD: UART    | 1 Module Disa    | ble bit     |                   |                |                |        |

|              | 1 = Module is |                  |             |                   |                |                |        |

|              | -             | ower and clock   |             | enabled           |                |                |        |

| bit 4        | SPI2MD: SPI   | 2 Module Disal   | ole bit     |                   |                |                |        |

|              | 1 = Module is |                  |             |                   |                |                |        |

|              |               | ower and clock   |             | enabled           |                |                |        |

| bit 3        |               | 1 Module Disal   | DIE DIT     |                   |                |                |        |

|              | 1 = Module is | s disabled       |             | anabled           |                |                |        |

| bit 2-1      |               | ted: Read as '   |             |                   |                |                |        |

| bit 0        | -             | D Converter M    |             | hit               |                |                |        |

|              |               |                  |             |                   |                |                |        |

|              | 1 = Module is | s disabled       |             |                   |                |                |        |

### REGISTER 11-10: IOCFx: INTERRUPT-ON-CHANGE FLAG x REGISTER<sup>(1,2)</sup>

| R/W-0         | R/W-0                              | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | U-0   |

|---------------|------------------------------------|------------------|-------|-------------------|----------------|-----------------|-------|

|               |                                    |                  | IOCF  | Fx<15:8>          |                |                 |       |

| bit 15        |                                    |                  |       |                   |                |                 | bit 8 |

|               |                                    |                  |       |                   |                |                 |       |

| R/W-0         | R/W-0                              | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|               |                                    |                  | IOC   | Fx<7:0>           |                |                 |       |

| bit 7         |                                    |                  |       |                   |                |                 | bit 0 |

|               |                                    |                  |       |                   |                |                 |       |

| Legend:       |                                    |                  |       |                   |                |                 |       |

| R = Readable  | e bit                              | W = Writable bit |       | U = Unimplem      | ented bit, rea | ad as '0'       |       |

| -n = Value at | -n = Value at POR '1' = Bit is set |                  |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 **IOCFx<15:0>:** Interrupt-on-Change Flag x bits

- 1 = An enabled change was detected on the associated pin; set when IOCPx = 1 and a positive edge was detected on the IOCx pin, or when IOCNx = 1 and a negative edge was detected on the IOCx pin

0 = No change was detected or the user cleared the detected change

- **Note 1:** It is not possible to set the IOCFx register bits with software writes (as this would require the addition of significant logic). To test IOC interrupts, it is recommended to enable the IOC functionality on one or more GPIO pins and then use the corresponding LATx register bit(s) to trigger an IOC interrupt.

- 2: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

#### REGISTER 11-11: IOCPUx: INTERRUPT-ON-CHANGE PULL-UP ENABLE x REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | U-0   |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | IOCPU | x<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | IOCPL | Jx<7:0> |       |       |       |

| bit 7  |       |       |       |         |       |       | bit 0 |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-0 IOCPUx<15:0>: Interrupt-on-Change Pull-up Enable x bits

1 = Pull-up is enabled

0 = Pull-up is disabled

Note 1: See Table 11-3, Table 11-4 and Table 11-5 for individual bit availability in this register.

| U-0                                | U-0 | R/W-1  | R/W-1                                   | R/W-1                              | R/W-1  | R/W-1  | R/W-1  |

|------------------------------------|-----|--------|-----------------------------------------|------------------------------------|--------|--------|--------|

| —                                  | —   | SCK1R5 | SCK1R4                                  | SCK1R3                             | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15                             |     |        |                                         |                                    | •      |        | bit 8  |

|                                    |     |        |                                         |                                    |        |        |        |

| U-0                                | U-0 | R/W-1  | R/W-1                                   | R/W-1                              | R/W-1  | R/W-1  | R/W-1  |

| _                                  | —   | SDI1R5 | SDI1R4                                  | SDI1R3                             | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7                              |     |        |                                         |                                    |        | bit 0  |        |

|                                    |     |        |                                         |                                    |        |        |        |

| Legend:                            |     |        |                                         |                                    |        |        |        |

| R = Readable bit W = Writable bit  |     |        | pit                                     | U = Unimplemented bit, read as '0' |        |        |        |

| -n = Value at POR '1' = Bit is set |     |        | '0' = Bit is cleared x = Bit is unknown |                                    |        | nown   |        |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK1R<5:0>: Assign SPI1 Clock Input (SCK1IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI1R<5:0>: Assign SPI1 Data Input (SDI1) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 11-26: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS1R<5:0>: Assign SPI1 Slave Select Input (SS1IN) to Corresponding RPn or RPIn Pin bits

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP9R5 | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP8R5 | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

|        |     |       |       |       |       |       |       |

#### REGISTER 11-36: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'             |

|-----------|----------------------------------------|

| bit 13-8  | RP9R<5:0>: RP9 Output Pin Mapping bits |

- Peripheral Output Number n is assigned to pin, RP9 (see Table 11-7 for peripheral function numbers).bit 7-6Unimplemented: Read as '0'bit 5-0RP8R<5:0>: RP8 Output Pin Mapping bits

- Peripheral Output Number n is assigned to pin, RP8 (see Table 11-7 for peripheral function numbers).

#### REGISTER 11-37: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | _   | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |        |        |        | •      |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP11 (see Table 11-7 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP10R<5:0>:** RP10 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP10 (see Table 11-7 for peripheral function numbers).

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | —   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

|        |     |                       |                       |                       |          |          |          |

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

| —      | —   | TXELM5 <sup>(3)</sup> | TXELM4 <sup>(2)</sup> | TXELM3 <sup>(1)</sup> | TXELM2   | TXELM1   | TXELM0   |

| bit 7  |     |                       |                       |                       |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                         |  |  |  |  |

|-------------------|---------------------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

**Note 1:** RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

**3:** RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

#### 19.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated, 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 19-1 shows the formula for computation of the baud rate when BRGH = 0.

# EQUATION 19-1: UARTX BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

$UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$

Note 1: FCY denotes the instruction cycle

clock frequency (FOSC/2).

2: Based on FCY = FOSC/2; Doze mo

**2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 19-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 19-2 shows the formula for computation of the baud rate when BRGH = 1.

# EQUATION 19-2: UARTX BAUD RATE WITH BRGH = $1^{(1,2)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{4 \cdot Baud Rate} - 1$

- **Note 1:** FCY denotes the instruction cycle clock frequency.

- 2: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 19-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))Solving for UxBRG Value: **UxBRG** = ((FCY/Desired Baud Rate)/16) - 1**UxBRG** = ((400000/9600)/16) - 1UxBRG = 25 Calculated Baud Rate = 4000000/(16(25+1))= 9615 Error = (Calculated Baud Rate – Desired Baud Rate) Desired Baud Rate = (9615 - 9600)/9600 = 0.16%Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode (4 BRG clock cycles per bit)0 = Standard Speed mode (16 BRG clock cycles per bit)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity10 = 8-bit data, odd parity01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

| R/W-0   | U-0    |  |  |  |

|---------|-----|-----|-----|-----|-----|-----|--------|--|--|--|

| IOCON   | —   | —   | —   | —   | —   | —   |        |  |  |  |

| bit 15  |     |     |     |     |     |     | bit 8  |  |  |  |

|         |     |     |     |     |     |     |        |  |  |  |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |  |  |

| _       | —   | —   | —   | —   | —   | —   | PMPTTL |  |  |  |

| bit 7   |     | •   | •   | •   |     |     | bit 0  |  |  |  |

|         |     |     |     |     |     |     |        |  |  |  |

| Legend: |     |     |     |     |     |     |        |  |  |  |

|         |     |     |     |     |     |     |        |  |  |  |

#### REGISTER 20-9: PADCON: PAD CONFIGURATION CONTROL REGISTER

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as 'O'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 IOCON: Used for Non-PMP functionality

bit 14-1 Unimplemented: Read as '0'

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

| U-0           | U-0                           | R/W-0            | R/W-0          | R/W-0                | R/W-0            | R/W-0              | R/W-0       |

|---------------|-------------------------------|------------------|----------------|----------------------|------------------|--------------------|-------------|

| —             | —                             | HRTEN1           | HRTEN0         | HRONE3               | HRONE2           | HRONE1             | HRONE0      |

| bit 15        |                               | •                |                |                      | •                |                    | bit 8       |

|               |                               |                  |                |                      |                  |                    |             |

| U-0           | R/W-0                         | R/W-0            | R/W-0          | R/W-0                | R/W-0            | R/W-0              | R/W-0       |

|               | MINTEN2                       | MINTEN1          | MINTEN0        | MINONE3              | MINONE2          | MINONE1            | MINONE0     |

| bit 7         |                               | •                | •              | •                    | •                |                    | bit (       |

| -             |                               |                  |                |                      |                  |                    |             |

| Legend:       |                               |                  |                |                      |                  |                    |             |

| R = Readable  | e bit                         | W = Writable     | bit            | U = Unimplem         | nented bit, read | d as '0'           |             |

| -n = Value at | POR                           | '1' = Bit is set |                | '0' = Bit is cleared |                  | x = Bit is unknown |             |

|               |                               |                  |                |                      |                  |                    |             |

| bit 15-14     | Unimplemen                    | ted: Read as '   | o'             |                      |                  |                    |             |

| bit 13-12     | HRTEN<1:0>                    | : Binary Codeo   | I Decimal Valu | e of Hours '10'      | Digit bits       |                    |             |

|               | Contains a va                 | lue from 0 to 2  |                |                      |                  |                    |             |

| bit 11-8      | HRONE<3:0>                    | Binary Code      | d Decimal Valu | e of Hours '1' [     | Digit bits       |                    |             |

|               | Contains a va                 | lue from 0 to 9  |                |                      |                  |                    |             |

| bit 7         | Unimplemen                    | ted: Read as '   | o'             |                      |                  |                    |             |

| bit 6-4       | MINTEN<2:0                    | >: Binary Code   | d Decimal Valu | ue of Minutes '1     | 0' Digit bits    |                    |             |

|               | Contains a value from 0 to 5. |                  |                |                      |                  |                    |             |

| bit 3-0       | MINONE<3:0                    | >: Binary Code   | ed Decimal Val | ue of Minutes 'a     | 1' Digit bits    |                    |             |

|               |                               | lue from 0 to 9  |                |                      | -                |                    |             |

| Note 1: If    | TSAEN = 0, bits               | s<15:0> can be   | used for persi | istence storage      | throughout a r   | 10n-Power-on F     | Reset (MCLR |

## REGISTER 21-16: TSATIMEH: RTCC TIMESTAMP A TIME REGISTER (HIGH)<sup>(1)</sup>

Note 1: If TSAEN = 0, bits<15:0> can be used for persistence storage throughout a non-Power-on Reset (MCLR, WDT, etc.).

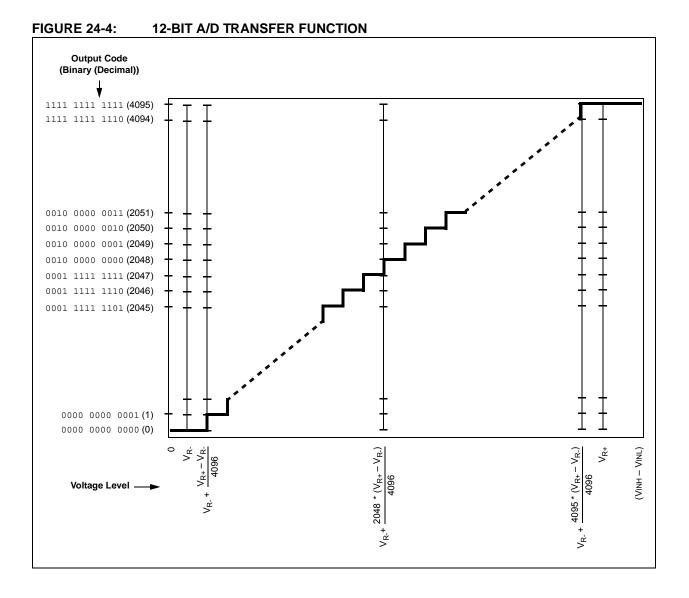

#### REGISTER 24-1: AD1CON1: A/D CONTROL REGISTER 1 (CONTINUED)

- bit 1SAMP: A/D Sample Enable bit1 = A/D Sample-and-Hold amplifiers are sampling0 = A/D Sample-and-Hold amplifiers are holdingbit 0DONE: A/D Conversion Status bit

- 1 = A/D conversion cycle has completed

- 0 = A/D conversion cycle has not started or is in progress

- Note 1: This bit is only available when Extended DMA and buffer features are available (DMAEN = 1).

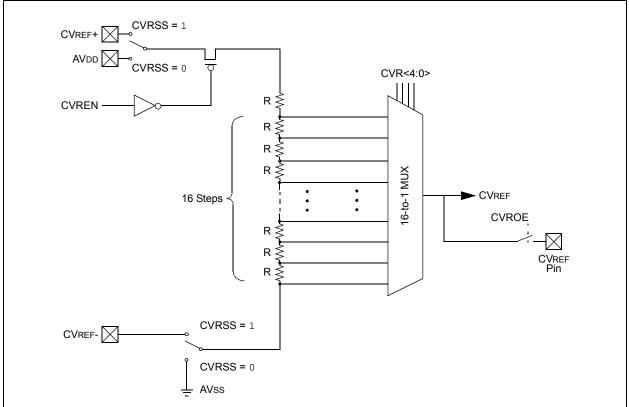

## 26.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Dual Comparator Module" (DS39710), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

#### 26.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 26-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The primary difference between the ranges is the size of the steps selected by the CVREF Value Selection bits (CVR<4:0>), with one range offering finer resolution.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

#### FIGURE 26-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

#### **REGISTER 29-6: FWDT CONFIGURATION REGISTER (CONTINUED)**

- bit 3-0 WDTPS<3:0>: Watchdog Timer Postscale Select bits 1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 = 1:512 1000 = 1:256 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16

- 0011 = 1:8 0010 = 1:4

- 0001 = 1:2

- 0000 = 1:1

#### 32.1 DC Characteristics

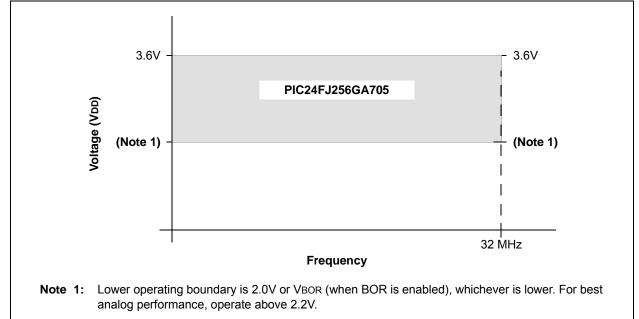

#### FIGURE 32-1: PIC24FJ256GA705 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

#### TABLE 32-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min         | Тур         | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|-----|------|

| PIC24FJ256GA705:                                                                                                                                                                        |        |             |             |     |      |

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40         | —           | +85 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40         | _           | +85 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O |             |     | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                       | PDMAX  | (           | TJ — TA)/θJ | IA  | W    |

#### TABLE 32-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                     | Symbol | Тур  | Max | Unit | Notes    |

|----------------------------------------------------|--------|------|-----|------|----------|

| Package Thermal Resistance, 6x6 mm 28-Pin QFN      | θJA    |      |     | °C/W | (Note 1) |

| Package Thermal Resistance, 4x4x0.6 mm 28-Pin UQFN | θJA    |      |     | °C/W | (Note 1) |

| Package Thermal Resistance, 7.50 mm 28-Pin SOIC    | θJA    |      | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 5.30 mm 28-Pin SSOP    | θJA    |      | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 300 mil 28-Pin SPDIP   | θJA    |      | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 6x6x0.5 mm 48-Pin UQFN | θJA    | 33.7 | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 10x10x1 mm 44-Pin TQFP | θJA    | 28   | _   | °C/W | (Note 1) |

| Package Thermal Resistance, 7x7x1 mm 48-Pin TQFP   | θJA    | 39.3 | —   | °C/W | (Note 1) |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| AC CH        | ARACTER   | ISTICS                                               | Standard Operating Conditions      |          |                                   | : 2.0V to 3.6V (unless otherwise stated) $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                                                                                |  |

|--------------|-----------|------------------------------------------------------|------------------------------------|----------|-----------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol    | Characteristic                                       | Min.                               | Тур      | Max.                              | Units                                                                                          | Conditions                                                                                     |  |

|              |           |                                                      | Devid                              | e Supp   | ly                                |                                                                                                |                                                                                                |  |

| AD01         | AVDD      | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 2.2 |          | Lesser of:<br>VDD + 0.3<br>or 3.6 | V                                                                                              |                                                                                                |  |

| AD02         | AVss      | Module Vss Supply                                    | Vss – 0.3                          |          | Vss + 0.3                         | V                                                                                              |                                                                                                |  |

|              |           |                                                      | Refere                             | nce Inp  | uts                               |                                                                                                |                                                                                                |  |

| AD05         | VREFH     | Reference Voltage High                               | AVss + 1.7                         |          | AVDD                              | V                                                                                              |                                                                                                |  |

| AD06         | VREFL     | Reference Voltage Low                                | AVss                               |          | AVDD – 1.7                        | V                                                                                              |                                                                                                |  |

| AD07         | VREF      | Absolute Reference<br>Voltage                        | AVss – 0.3                         |          | AVDD + 0.3                        | V                                                                                              |                                                                                                |  |

|              |           | •                                                    | Anal                               | og Input | ts                                |                                                                                                |                                                                                                |  |

| AD10         | VINH-VINL | Full-Scale Input Span                                | VREFL                              | _        | VREFH                             | V                                                                                              | (Note 2)                                                                                       |  |

| AD11         | VIN       | Absolute Input Voltage                               | AVss - 0.3                         | _        | AVDD + 0.3                        | V                                                                                              |                                                                                                |  |

| AD12         | Vinl      | Absolute VINL Input<br>Voltage                       | AVss – 0.3                         | _        | AVDD/3                            | V                                                                                              |                                                                                                |  |

| AD13         |           | Leakage Current                                      | —                                  | ±1.0     | ±610                              | nA                                                                                             | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3V$ ,<br>Source Impedance = $2.5 \text{ k}\Omega$ |  |

| AD17         | RIN       | Recommended<br>Impedance of Analog<br>Voltage Source | —                                  |          | 2.5K                              | Ω                                                                                              | 10-bit                                                                                         |  |

|              |           | ·                                                    | A/D /                              | Accurac  | y                                 |                                                                                                | ·                                                                                              |  |

| AD20B        | Nr        | Resolution                                           | —                                  | 12       | —                                 | bits                                                                                           |                                                                                                |  |

| AD21B        | INL       | Integral Nonlinearity                                | —                                  | ±1       | < ±2                              | LSb                                                                                            | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD22B        | DNL       | Differential Nonlinearity                            | —                                  | —        | < ±1                              | LSb                                                                                            | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD23B        | Gerr      | Gain Error                                           | —                                  | ±1       | ±4                                | LSb                                                                                            | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD24B        | EOFF      | Offset Error                                         | —                                  | ±1       | ±2                                | LSb                                                                                            | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |  |

| AD25B        |           | Monotonicity <sup>(1)</sup>                          | _                                  |          | _                                 |                                                                                                | Guaranteed                                                                                     |  |

#### TABLE 32-24: A/D MODULE SPECIFICATIONS

Note 1: The A/D conversion result never decreases with an increase in the input voltage.

2: Measurements are taken with the external VREF+ and VREF- used as the A/D voltage reference.

## APPENDIX A: REVISION HISTORY

#### **Revision A (March 2016)**

Original data sheet for the PIC24FJ256GA705 family of devices.

### **Revision B (October 2016)**

This revision incorporates the following updates:

- · Sections:

- Removes Section 9.5 "FRC Active Clock Tuning".

- Updates the Absolute Maximum Ratings in Section 32.0 "Electrical Characteristics".

- Changes the 48-Lead QFN (7x7 mm) to 48-Lead UQFN (6x6 mm) in Section 33.0 "Packaging Information".

- Registers:

- Updates Register 9-1, Register 9-3, Register 9-6, Register 16-5 and Register 16-6.

- Tables:

- Adds Table 11-3, Table 11-4 and Table 11-5.

- Updates the GPIO column in the Peripheral Features table on Page 2.

- Updates Table 1, Table 2, Table 3, Table 4, Table 5, Table 32-4, Table 32-5, Table 32-6, Table 32-7 and Table 32-25.

- Figures

- Updates Figure 9-1.

- Changes to text and formatting were incorporated throughout the document.