Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT             |

| Number of I/O              | 22                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

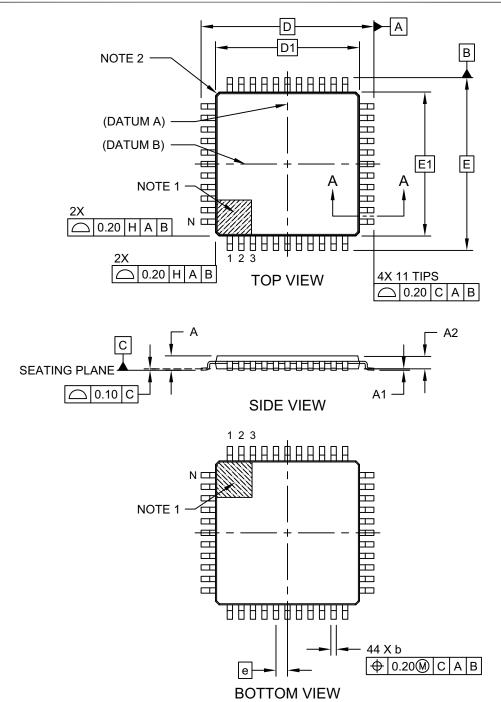

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga702-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

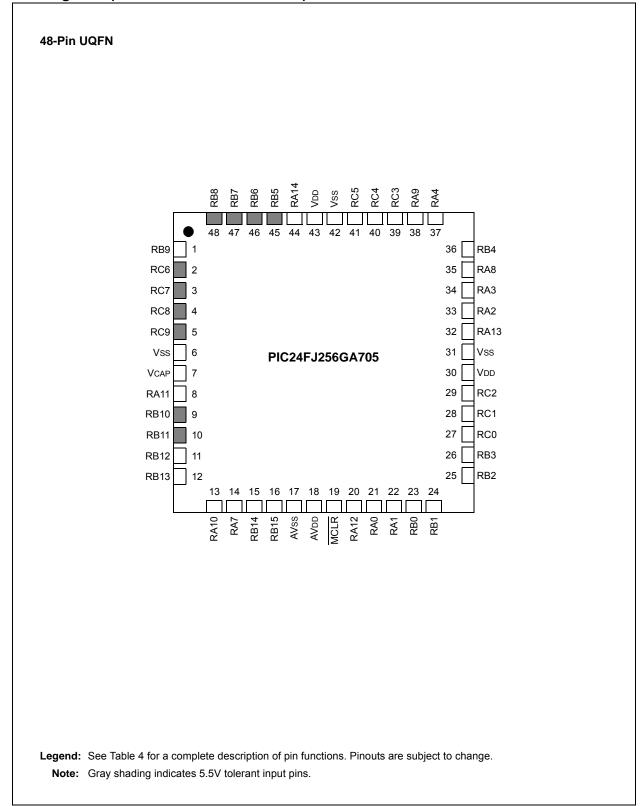

### Pin Diagrams (PIC24FJ256GA705 Devices)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

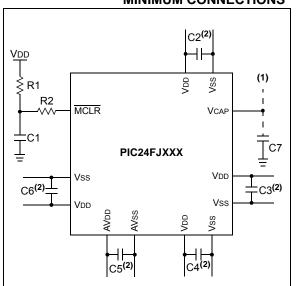

Getting started with the PIC24FJ256GA705 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

VCAP pin (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGCx/PGDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu$ F, 50V ceramic

C7: 10 µF, 16V or greater, ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for an explanation of voltage regulator pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

## 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "PIC24F Flash Program Memory" (DS30009715), which is available from the Microchip web site (www.microchip.com). The information in the this data sheet supersedes information in the FRM.

The PIC24FJ256GA705 family of devices contains internal Flash program memory for storing and executing application code. The program memory is readable, writable and erasable. The Flash memory can be programmed in four ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- JTAG

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ256GA705 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (named PGCx and PGDx, respectively), and three other lines for power (VDD), ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 128 instructions (384 bytes) at a time and erase program memory in blocks of 1024 instructions (3072 bytes) at a time.

The device implements a 7-bit Error Correcting Code (ECC). The NVM block contains a logic to write and read ECC bits to and from the Flash memory. The Flash is programmed at the same time as the corresponding ECC parity bits. The ECC provides improved resistance to Flash errors. ECC single bit errors can be transparently corrected; ECC double-bit errors result in a trap.

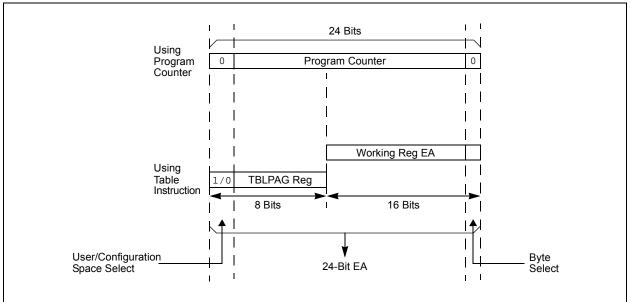

## 6.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 6-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 6-1: ADDRESSING FOR TABLE REGISTERS

#### TABLE 8-2: INTERRUPT VECTOR DETAILS

| Interrupt Course                    | IRQ       | IVT Address       | Interrupt Bit Location |          |                 |  |

|-------------------------------------|-----------|-------------------|------------------------|----------|-----------------|--|

| Interrupt Source                    | #         | IVI Address       | Flag                   | Enable   | Priority        |  |

|                                     | Highest N | atural Order Pric | ority                  |          |                 |  |

| INT0 – External Interrupt 0         | 0         | 000014h           | IFS0<0>                | IEC0<0>  | INT0Interrupt   |  |

| IC1 – Input Capture 1               | 1         | 000016h           | IFS0<1>                | IEC0<1>  | IC1Interrupt    |  |

| OC1 – Output Compare 1              | 2         | 000018h           | IFS0<2>                | IEC0<2>  | OC1Interrupt    |  |

| T1 – Timer1                         | 3         | 00001Ah           | IFS0<3>                | IEC0<3>  | T1Interrupt     |  |

| DMA0 – Direct Memory Access 0       | 4         | 00001Ch           | IFS0<4>                | IEC0<4>  | DMA0Interrupt   |  |

| IC2 – Input Capture 2               | 5         | 00001Eh           | IFS0<5>                | IEC0<5>  | IC2Interrupt    |  |

| OC2 – Output Compare 2              | 6         | 000020h           | IFS0<6>                | IEC0<6>  | OC2Interrupt    |  |

| T2 – Timer2                         | 7         | 000022h           | IFS0<7>                | IEC0<7>  | T2Interrupt     |  |

| T3 – Timer3                         | 8         | 000024h           | IFS0<8>                | IEC0<8>  | T3Interrupt     |  |

| SPI1 – SPI1 General                 | 9         | 000026h           | IFS0<9>                | IEC0<9>  | SPI1Interrupt   |  |

| SPI1TX – SPI1 Transfer Done         | 10        | 000028h           | IFS0<10>               | IEC0<10> | SPI1TXInterrupt |  |

| U1RX – UART1 Receiver               | 11        | 00002Ah           | IFS0<11>               | IEC0<11> | U1RXInterrupt   |  |

| U1TX – UART1 Transmitter            | 12        | 00002Ch           | IFS0<12>               | IEC0<12> | U1TXInterrupt   |  |

| ADC1 – A/D Converter 1              | 13        | 00002Eh           | IFS0<13>               | IEC0<13> | ADC1Interrupt   |  |

| DMA1 – Direct Memory Access 1       | 14        | 000030h           | IFS0<14>               | IEC0<14> | DMA1Interrupt   |  |

| NVM – NVM Program/Erase Complete    | 15        | 000032h           | IFS0<15>               | IEC0<15> | NVMInterrupt    |  |

| SI2C1 – I2C1 Slave Events           | 16        | 000034h           | IFS1<0>                | IEC1<0>  | SI2C1Interrupt  |  |

| MI2C1 – I2C1 Master Events          | 17        | 000036h           | IFS1<1>                | IEC1<1>  | MI2C1Interrupt  |  |

| Comp – Comparator                   | 18        | 000038h           | IFS1<2>                | IEC1<2>  | CompInterrupt   |  |

| IOC – Interrupt-on-Change Interrupt | 19        | 00003Ah           | IFS1<3>                | IEC1<3>  | IOCInterrupt    |  |

| INT1 – External Interrupt 1         | 20        | 00003Ch           | IFS1<4>                | IEC1<4>  | INT1Interrupt   |  |

| _                                   | 21        | _                 |                        | _        | _               |  |

| _                                   | 22        | _                 | _                      | _        | _               |  |

| _                                   | 23        | _                 | _                      | _        | _               |  |

| DMA2 – Direct Memory Access 2       | 24        | 000044h           | IFS1<8>                | IEC1<8>  | DMA2Interrupt   |  |

| OC3 – Output Compare 3              | 25        | 000046h           | IFS1<9>                | IEC1<9>  | OC3Interrupt    |  |

| _                                   | 26        | _                 | _                      | _        | _               |  |

|                                     | 27        | _                 | _                      | _        | _               |  |

| _                                   | 28        | _                 | _                      | _        | —               |  |

| INT2 – External Interrupt 2         | 29        | 00004Eh           | IFS1<13>               | IEC1<13> | INT2Interrupt   |  |

| U2RX – UART2 Receiver               | 30        | 000050h           | IFS1<14>               | IEC1<14> | U2RXInterrupt   |  |

| U2TX – UART2 Transmitter            | 31        | 000052h           | IFS1<15>               | IEC1<15> | U2TXInterrupt   |  |

| SPI2 – SPI2 General                 | 32        | 000054h           | IFS2<0>                | IEC2<0>  | SPI2Interrupt   |  |

| SPI2TX – SPI2 Transfer Done         | 33        | 000056h           | IFS2<1>                | IEC2<1>  | SPI2TXInterrupt |  |

| _                                   | 34        | _                 | _                      | _        | —               |  |

| _                                   | 35        | _                 | _                      | _        | —               |  |

| DMA3 – Direct Memory Access 3       | 36        | 00005Ch           | IFS2<4>                | IEC2<4>  | DMA3Interrupt   |  |

| IC3 – Input Capture 3               | 37        | 00005Eh           | IFS2<5>                | IEC2<5>  | IC3Interrupt    |  |

| · · ·                               | 38        | <u> </u>          |                        | _        | <u>·</u>        |  |

| _                                   | 39        |                   |                        | _        | _               |  |

|                                     | 40        |                   | _                      | _        | _               |  |

| CCT3 – Capture/Compare Timer3       | 43        | 00006Ah           | IFS2<11>               | IEC2<11> | CCT3Interrupt   |  |

### REGISTER 10-5: PMD5: PERIPHERAL MODULE DISABLE REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0    | U-0    |

|--------|-----|-----|-----|--------|--------|--------|--------|

| —      | —   | —   | —   | —      | —      | —      | —      |

| bit 15 |     |     |     |        |        |        | bit 8  |

|        |     |     |     |        |        |        |        |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|        | _   |     |     | CCP4MD | CCP3MD | CCP2MD | CCP1MD |

| bit 7             |                  |                       | b                  | oit 0 |

|-------------------|------------------|-----------------------|--------------------|-------|

|                   |                  |                       |                    |       |

| Legend:           |                  |                       |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |       |

| bit 15-4 | Unimplemented: Read as '0'                     |

|----------|------------------------------------------------|

| bit 3    | CCP4MD: MCCP4 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 2    | CCP3MD: MCCP3 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 1    | CCP2MD: MCCP2 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          | 0 = Module power and clock sources are enabled |

| bit 0    | CCP1MD: MCCP1 Module Disable bit               |

|          | 1 = Module is disabled                         |

|          |                                                |

0 = Module power and clock sources are enabled

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| · ·    |     |        |        |        |        |        |        |

### REGISTER 11-40: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP17R<5:0>: RP17 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP17 (see Table 11-7 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP16R<5:0>: RP16 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP16 (see Table 11-7 for peripheral function numbers). |

### REGISTER 11-41: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP19R<5:0>:** RP19 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP19 (see Table 11-7 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP18R<5:0>:** RP18 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP18 (see Table 11-7 for peripheral function numbers).

| R/W-0           | R/W-0                                                                                                                                                                                                                                             | U-0               | R/W-0          | U-0                            | U-0             | U-0             | U-0   |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------------------------------|-----------------|-----------------|-------|--|

| PWMRSEN         | ASDGM                                                                                                                                                                                                                                             | —                 | SSDG           | —                              | —               | —               | —     |  |

| bit 15          |                                                                                                                                                                                                                                                   |                   |                |                                |                 |                 | bit 8 |  |

|                 |                                                                                                                                                                                                                                                   |                   |                |                                |                 |                 |       |  |

| R/W-0           | R/W-0                                                                                                                                                                                                                                             | R/W-0             | R/W-0          | R/W-0                          | R/W-0           | R/W-0           | R/W-0 |  |

| ASDG7           | ASDG6                                                                                                                                                                                                                                             | ASDG5             | ASDG4          | ASDG3                          | ASDG2           | ASDG1           | ASDG0 |  |

| bit 7           |                                                                                                                                                                                                                                                   |                   |                |                                |                 |                 | bit C |  |

| Legend:         |                                                                                                                                                                                                                                                   |                   |                |                                |                 |                 |       |  |

| R = Readable    | bit                                                                                                                                                                                                                                               | W = Writable      | U = Unimplem   | nented bit, read               | d as '0'        |                 |       |  |

| -n = Value at I | POR                                                                                                                                                                                                                                               | '1' = Bit is set  |                | '0' = Bit is clea              | ared            | x = Bit is unkr | iown  |  |

| bit 14          |                                                                                                                                                                                                                                                   | -                 |                | e to resume PW<br>e Enable bit | M activity on c | output pins     |       |  |

| 511 14          | 1 = Waits uni                                                                                                                                                                                                                                     | til the next Time | e Base Reset o | or rollover for sh             | utdown to occ   | ur              |       |  |

| L:1 40          |                                                                                                                                                                                                                                                   | n event occurs    | ,              |                                |                 |                 |       |  |

| bit 13          | -                                                                                                                                                                                                                                                 | ted: Read as '    |                |                                |                 |                 |       |  |

| DIT 12          | <ul> <li>it 12 SSDG: CCPx Software Shutdown/Gate Control bit</li> <li>1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting of ASDGM bit still applies)</li> <li>0 = Normal module operation</li> </ul> |                   |                |                                |                 |                 |       |  |

| bit 11-8        | Unimplemented: Read as '0'                                                                                                                                                                                                                        |                   |                |                                |                 |                 |       |  |

| bit 7-0         | ASDG<7:0>:                                                                                                                                                                                                                                        | CCPx Auto-Sh      | utdown/Gating  | Source Enable                  | e bits          |                 |       |  |

|                 | ASDG<7:0>: CCPx Auto-Shutdown/Gating Source Enable bits<br>1 = ASDGx Source n is enabled (see Table 16-6 for auto-shutdown/gating sources)<br>0 = ASDGx Source n is disabled                                                                      |                   |                |                                |                 |                 |       |  |

## REGISTER 16-3: CCPxCON2L: CCPx CONTROL 2 LOW REGISTERS

#### TABLE 16-6: AUTO-SHUTDOWN SOURCES

| ASDC .7.0 | Auto-Shutdown Source |          |        |       |  |  |  |  |  |

|-----------|----------------------|----------|--------|-------|--|--|--|--|--|

| ASDG<7:0> | MCCP1                | MCCP2    | МССР3  | MCCP4 |  |  |  |  |  |

| 1xxx xxxx |                      | OCFB     |        |       |  |  |  |  |  |

| x1xx xxxx |                      | OCFA     |        |       |  |  |  |  |  |

| xx1x xxxx | CLC1 CLC2 Not Used   |          |        |       |  |  |  |  |  |

| xxx1 xxxx |                      | Not      | Used   |       |  |  |  |  |  |

| xxxx 1xxx | Not Used             |          |        |       |  |  |  |  |  |

| xxxx x1xx |                      | CMP3 Out |        |       |  |  |  |  |  |

| xxxx xx1x |                      | CMP2 Out |        |       |  |  |  |  |  |

| xxxx xxx1 |                      | CMP      | '1 Out |       |  |  |  |  |  |

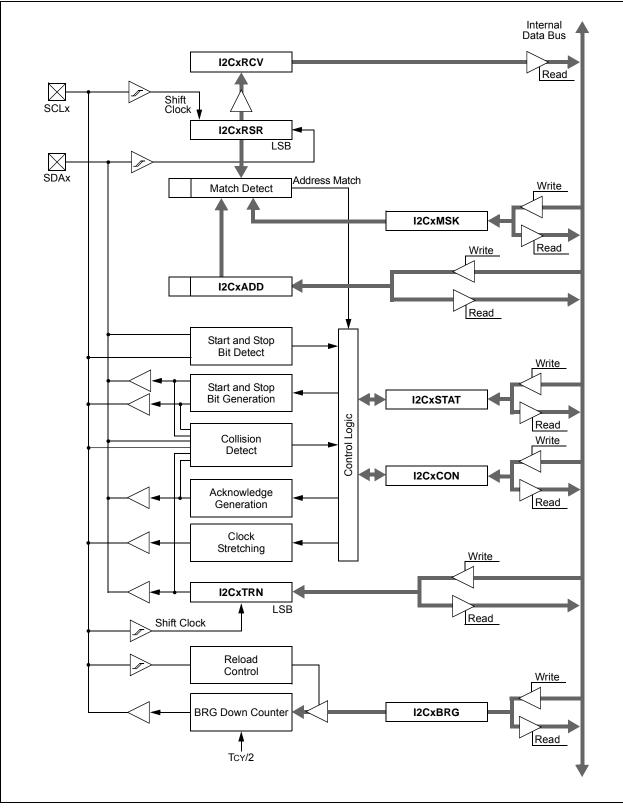

## FIGURE 18-1: I2Cx BLOCK DIAGRAM

| R/W-0                 | U-0                          | R/W-0                                                                                                                                        | R/W-0                                               | R/W-0                        | U-0                       | R/W-0            | R/W-0           |  |

|-----------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|---------------------------|------------------|-----------------|--|

| UARTEN <sup>(1)</sup> | ) _                          | USIDL                                                                                                                                        | IREN <sup>(2)</sup>                                 | RTSMD                        | _                         | UEN1             | UEN0            |  |

| bit 15                |                              |                                                                                                                                              |                                                     | •                            |                           |                  | bit a           |  |

|                       | R/W-0                        |                                                                                                                                              | R/W-0                                               | R/W-0                        | R/W-0                     | R/W-0            | R/W-0           |  |

| R/W-0, HC             |                              | R/W-0, HC                                                                                                                                    |                                                     | -                            | -                         | 1                | -               |  |

| WAKE                  | LPBACK                       | ABAUD                                                                                                                                        | URXINV                                              | BRGH                         | PDSEL1                    | PDSEL0           | STSEL<br>bit    |  |

|                       |                              |                                                                                                                                              |                                                     |                              |                           |                  | DIL             |  |

| Legend:               |                              | HC = Hardwar                                                                                                                                 | e Clearable bi                                      | t                            |                           |                  |                 |  |

| R = Readab            | ole bit                      | W = Writable t                                                                                                                               | oit                                                 | U = Unimplen                 | nented bit, read          | l as '0'         |                 |  |

| -n = Value a          | at POR                       | '1' = Bit is set                                                                                                                             |                                                     | '0' = Bit is clea            | ared                      | x = Bit is unkno | own             |  |

|                       |                              |                                                                                                                                              |                                                     |                              |                           |                  |                 |  |

| bit 15                |                              | ARTx Enable bit                                                                                                                              |                                                     |                              |                           |                  |                 |  |

|                       |                              | enabled; all UA<br>disabled; all UAF                                                                                                         |                                                     |                              |                           |                  | tion is minim   |  |

| bit 14                |                              | ted: Read as '0                                                                                                                              | •                                                   | ,                            | ,                         |                  |                 |  |

| bit 13                | USIDL: UAR                   | Tx Stop in Idle M                                                                                                                            | lode bit                                            |                              |                           |                  |                 |  |

|                       |                              | ues module ope                                                                                                                               |                                                     |                              | e mode                    |                  |                 |  |

| bit 12                |                              | <ul> <li>0 = Continues module operation in Idle mode</li> <li>IREN: IrDA<sup>®</sup> Encoder and Decoder Enable bit<sup>(2)</sup></li> </ul> |                                                     |                              |                           |                  |                 |  |

|                       |                              | 1 = IrDA encoder and decoder are enabled                                                                                                     |                                                     |                              |                           |                  |                 |  |

|                       |                              | oder and decode                                                                                                                              |                                                     |                              |                           |                  |                 |  |

| bit 11                | RTSMD: Mod                   | le Selection for                                                                                                                             | JxRTS Pin bit                                       |                              |                           |                  |                 |  |

|                       |                              | in is in Simplex ı<br>in is in Flow Cor                                                                                                      |                                                     |                              |                           |                  |                 |  |

| bit 10                | Unimplemen                   | ted: Read as '0                                                                                                                              | ,                                                   |                              |                           |                  |                 |  |

| bit 9-8               | UEN<1:0>: L                  | JARTx Enable bi                                                                                                                              | ts                                                  |                              |                           |                  |                 |  |

|                       | 10 = UxTX, U<br>01 = UxTX, U | JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>thes                                                                   | nd $\overline{\text{UxRTS}}$ pins<br>S pins are ena | are enabled a bled and used; | nd used<br>UxCTS pin is o | controlled by po | rt latches      |  |

| bit 7                 | WAKE: Wake                   | e-up on Start Bit                                                                                                                            | Detect During                                       | Sleep Mode Er                | nable bit                 |                  |                 |  |

|                       | in hardw                     | continues to sam<br>are on the follow                                                                                                        |                                                     |                              | generated on              | the falling edge | , bit is cleare |  |

| bit 6                 |                              | -up is enabled                                                                                                                               | Mada Salaat b                                       | i+                           |                           |                  |                 |  |

|                       |                              | ARTx Loopback                                                                                                                                |                                                     | 11                           |                           |                  |                 |  |

|                       |                              | mode is disable                                                                                                                              | ed                                                  |                              |                           |                  |                 |  |

| bit 5                 | ABAUD: Auto                  | o-Baud Enable b                                                                                                                              | pit                                                 |                              |                           |                  |                 |  |

|                       |                              | baud rate meas<br>n hardware upoi                                                                                                            |                                                     | e next characte              | er – requires re          | eception of a Sy | nc field (55h   |  |

|                       | 0 = Baud rat                 | e measurement                                                                                                                                | is disabled or                                      | completed                    |                           |                  |                 |  |

| bit 4                 |                              |                                                                                                                                              |                                                     | -                            |                           |                  |                 |  |

| bit 4                 |                              | e measurement<br>RTx Receive Po                                                                                                              |                                                     | -                            |                           |                  |                 |  |

### REGISTER 19-1: UxMODE: UARTx MODE REGISTER

2: This feature is only available for the 16x BRG mode (BRGH = 0).

| R/W-0         | R/W-0                                                    | R/W-0                                                                                                               | R/W-0            | R/W-0, HC                             | R/W-0                 | R-0, HSC           | R-1, HSC        |  |  |  |

|---------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|-----------------------|--------------------|-----------------|--|--|--|

| UTXISEL1      | UTXINV <sup>(1)</sup>                                    | UTXISEL0                                                                                                            | URXEN            | UTXBRK                                | UTXEN <sup>(2)</sup>  | UTXBF              | TRMT            |  |  |  |

| bit 15        |                                                          |                                                                                                                     |                  | ·                                     |                       | •                  | bit             |  |  |  |

|               |                                                          |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

| R/W-0         | R/W-0                                                    | R/W-0                                                                                                               | R-1, HSC         | R-0, HSC                              | R-0, HSC              | R/C-0, HS          | R-0, HSC        |  |  |  |

| URXISEL1      | URXISEL0                                                 | ADDEN                                                                                                               | RIDLE            | PERR                                  | FERR                  | OERR               | URXDA           |  |  |  |

| bit 7         | •                                                        | •                                                                                                                   |                  | •                                     |                       | L.                 | bit             |  |  |  |

|               |                                                          |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

| Legend:       |                                                          | C = Clearable                                                                                                       | bit              | HSC = Hardw                           | are Settable/C        | learable bit       |                 |  |  |  |

| R = Readable  | e bit                                                    | W = Writable                                                                                                        | oit              | U = Unimplem                          | nented bit, read      | l as '0'           |                 |  |  |  |

| -n = Value at | POR                                                      | '1' = Bit is set                                                                                                    |                  | '0' = Bit is clea                     | ared                  | x = Bit is unkn    | iown            |  |  |  |

| HS = Hardwa   | re Settable bit                                          | HC = Hardwa                                                                                                         | re Clearable b   | it                                    |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

| bit 15,13     | UTXISEL<1:0                                              | <b>0&gt;:</b> UARTx Trar                                                                                            | nsmission Inter  | rrupt Mode Sele                       | ection bits           |                    |                 |  |  |  |

|               | 11 = Reserve                                             |                                                                                                                     |                  | •                                     |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | ed to the Trans                       | mit Shift Regist      | er (TSR), and a    | as a result, th |  |  |  |

|               |                                                          | nit buffer becomes empty<br>upt when the last character is shifted out of the Transmit Shift Register; all transmit |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          | operations are completed                                                                                            |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | ed to the Transn                      | nit Shift Registe     | er (this implies t | here is at leas |  |  |  |

|               |                                                          | racter open in t                                                                                                    |                  |                                       | U                     | Υ Ι                |                 |  |  |  |

| bit 14        | UTXINV: UAF                                              | RTx IrDA <sup>®</sup> Enco                                                                                          | der Transmit I   | Polarity Inversio                     | on bit <sup>(1)</sup> |                    |                 |  |  |  |

|               | IREN = 0:                                                |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

|               | 1 = UxTX Idle state is '0'<br>0 = UxTX Idle state is '1' |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

|               | $\frac{ \text{REN} = 1:}{1 = \text{UxTX}  \text{dle} $   | state is '1'                                                                                                        |                  |                                       |                       |                    |                 |  |  |  |

|               | 0 = UxTX Idle                                            |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

| bit 12        | URXEN: UAF                                               | RTx Receive En                                                                                                      | able bit         |                                       |                       |                    |                 |  |  |  |

|               | 1 = Receive is                                           | s enabled, UxR                                                                                                      | X pin is contro  | lled by UARTx                         |                       |                    |                 |  |  |  |

|               | 0 = Receive is                                           | s disabled, UxF                                                                                                     | X pin is contro  | olled by the port                     | :                     |                    |                 |  |  |  |

| bit 11        |                                                          | ARTx Transmit I                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | n – Start bit, foll                   | owed by twelve        | e '0' bits, follow | ed by Stop bi   |  |  |  |

|               |                                                          | by hardware up<br>ak transmission                                                                                   | •                | r completed                           |                       |                    |                 |  |  |  |

| bit 10        | -                                                        | RTx Transmit Er                                                                                                     |                  | reompieted                            |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | olled by UARTx                        |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | nsmission is at                       |                       | buffer is reset    | t; UxTX pin i   |  |  |  |

|               | controlled                                               | d by the port                                                                                                       |                  |                                       |                       |                    | •               |  |  |  |

| bit 9         | UTXBF: UAR                                               | Tx Transmit Bu                                                                                                      | ffer Full Status | s bit (read-only)                     |                       |                    |                 |  |  |  |

|               | 1 = Transmit                                             |                                                                                                                     |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | more character                        | can be written        |                    |                 |  |  |  |

| bit 8         |                                                          | mit Shift Regist                                                                                                    |                  |                                       |                       |                    |                 |  |  |  |

|               |                                                          |                                                                                                                     |                  | ansmit buffer is e<br>transmission is |                       |                    | as completed    |  |  |  |

|               |                                                          | Shin Register is                                                                                                    | s not empty, a   |                                       | in progress of        | queueu             |                 |  |  |  |

### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

(IREN = 1).

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.5 "Peripheral Pin Select (PPS)".

### REGISTER 19-3: UXRXREG: UARTX RECEIVE REGISTER (NORMALLY READ-ONLY)

| U-0           | U-0                                                                   | U-0            | U-0  | U-0             | U-0            | U-0       | R-0      |

|---------------|-----------------------------------------------------------------------|----------------|------|-----------------|----------------|-----------|----------|

|               |                                                                       | —              | _    | —               | _              | —         | UxRXREG8 |

| bit 15        | ·                                                                     | · · ·          |      | -               |                |           | bit 8    |

|               |                                                                       |                |      |                 |                |           |          |

| R-0           | R-0                                                                   | R-0            | R-0  | R-0             | R-0            | R-0       | R-0      |

|               |                                                                       |                | UxRX | REG<7:0>        |                |           |          |

| bit 7         |                                                                       |                |      |                 |                |           | bit 0    |

|               |                                                                       |                |      |                 |                |           |          |

| Legend:       |                                                                       |                |      |                 |                |           |          |

| R = Readable  | e bit                                                                 | W = Writable b | it   | U = Unimpler    | nented bit, re | ad as '0' |          |

| -n = Value at | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |                |      | x = Bit is unkr | iown           |           |          |

bit 15-9 Unimplemented: Read as '0'

bit 8-0 UxRXREG<8:0>: Data of the Received Character bits

### REGISTER 19-4: UxTXREG: UARTx TRANSMIT REGISTER (NORMALLY WRITE-ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | W-x      |

|--------|-----|-----|-----|-----|-----|-----|----------|

| —      | —   |     |     | —   | —   | _   | UxTXREG8 |

| bit 15 |     |     |     |     |     |     | bit 8    |

| W-x          | W-x | W-x | W-x | W-x | W-x | W-x | W-x   |

|--------------|-----|-----|-----|-----|-----|-----|-------|

| UxTXREG<7:0> |     |     |     |     |     |     |       |

| bit 7        |     |     |     |     |     |     | bit 0 |

|              |     |     |     |     |     |     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8-0 UxTXREG<8:0>: Data of the Transmitted Character bits

| R/W-0         | R/W-0                     | R/W-0                                   | R/W-0          | U-0               | R/W-0            | R/W-0           | R/W-0  |

|---------------|---------------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|--------|

| PTWREN        | PTRDEN                    | PTBE1EN                                 | PTBE0EN        | —                 | AWAITM1          | AWAITM0         | AWAITE |

| bit 15        |                           |                                         |                |                   |                  |                 | bit 8  |

|               |                           |                                         |                |                   |                  |                 |        |

| U-0           | U-0                       | U-0                                     | U-0            | U-0               | U-0              | U-0             | U-0    |

| —             | _                         | —                                       | —              | —                 | —                | —               | —      |

| bit 7         |                           |                                         |                |                   |                  |                 | bit 0  |

|               |                           |                                         |                |                   |                  |                 |        |

| Legend:       |                           |                                         |                |                   |                  |                 |        |

| R = Readable  |                           | W = Writable                            | bit            | •                 | nented bit, read |                 |        |

| -n = Value at | POR                       | '1' = Bit is set                        |                | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

|               |                           |                                         |                |                   |                  |                 |        |

| bit 15        |                           | rite/Enable Stro                        |                | e bit             |                  |                 |        |

|               |                           | MENB port is e<br>MENB port is o        |                |                   |                  |                 |        |

| bit 14        |                           | ad/Write Strobe                         |                | hit               |                  |                 |        |

|               |                           | MWR port is er                          |                |                   |                  |                 |        |

|               |                           | MWR port is di                          |                |                   |                  |                 |        |

| bit 13        | PTBE1EN: Hi               | igh Nibble/Byte                         | Enable Port E  | nable bit         |                  |                 |        |

|               |                           | oort is enabled                         |                |                   |                  |                 |        |

|               | 0 = PMBE1 p               | oort is disabled                        |                |                   |                  |                 |        |

| bit 12        |                           | ow Nibble/Byte                          | Enable Port E  | nable bit         |                  |                 |        |

|               |                           | ort is enabled                          |                |                   |                  |                 |        |

| bit 11        | •                         | oort is disabled<br>ted: Read as 'o     | ،'             |                   |                  |                 |        |

| bit 10-9      | •                         | >: Address Lat                          |                | Stata bita        |                  |                 |        |

| DIL 10-9      | 11 = Wait of 3            |                                         | ch Strobe wait | State bits        |                  |                 |        |

|               | 10 = Wait of 2            |                                         |                |                   |                  |                 |        |

|               | 01 = Wait of 1            | 1½ TCY                                  |                |                   |                  |                 |        |

|               | 00 = Wait of 1            | ∕₂ TCY                                  |                |                   |                  |                 |        |

| bit 8         |                           |                                         | r Address Latc | h Strobe Wait S   | State bits       |                 |        |

|               | 1 = Wait of $1$           | , , , , , , , , , , , , , , , , , , , , |                |                   |                  |                 |        |

| hit 7 0       | $0 = Wait of \frac{1}{4}$ |                                         | <b>,</b>       |                   |                  |                 |        |

| bit 7-0       | Unimplemen                | ted: Read as '                          | J              |                   |                  |                 |        |

|               |                           |                                         |                |                   |                  |                 |        |

### REGISTER 20-3: PMCON3: EPMP CONTROL REGISTER 3

### REGISTER 20-4: PMCON4: EPMP CONTROL REGISTER 4

| U-0              | R/W-0                                                                                                                     | R/W-0                                 | R/W-0         | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|-------------------|-----------------|--------------------|-------|--|

| _                | PTEN14                                                                                                                    |                                       |               | PTEN              | <13:8>          |                    |       |  |

| bit 15           |                                                                                                                           |                                       |               |                   |                 |                    | bit 8 |  |

| R/W-0            | R/W-0                                                                                                                     | R/W-0                                 | R/W-0         | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|                  |                                                                                                                           | PTEN<7:3>                             |               |                   |                 | PTEN<2:0>          |       |  |

| bit 7            |                                                                                                                           |                                       |               |                   | •               |                    | bit 0 |  |

|                  |                                                                                                                           |                                       |               |                   |                 |                    |       |  |

| Legend:          |                                                                                                                           |                                       |               |                   |                 |                    |       |  |

| R = Readable bit |                                                                                                                           | W = Writable                          | bit           | U = Unimplem      | nented bit, rea | d as '0'           |       |  |

| -n = Value at    | t POR                                                                                                                     | '1' = Bit is set                      |               | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

| bit 15           | Unimpleme                                                                                                                 | nted: Read as 'o                      | )'            |                   |                 |                    |       |  |

| bit 14           | PTEN14: PM                                                                                                                | A14 Port Enabl                        | e bit         |                   |                 |                    |       |  |

|                  |                                                                                                                           | functions as eith<br>functions as por |               | ne 14 or Chip S   | elect 1         |                    |       |  |

| bit 13-3         | PTEN<13:3>                                                                                                                | -: EPMP Addres                        | s Port Enable | bits              |                 |                    |       |  |

|                  | <ul> <li>1 = PMA&lt;13:3&gt; function as EPMP address lines</li> <li>0 = PMA&lt;13:3&gt; function as port I/Os</li> </ul> |                                       |               |                   |                 |                    |       |  |

| bit 2-0          | PTEN<2:0>:                                                                                                                | PMALU/PMALH                           | H/PMALL Strol | be Enable bits    |                 |                    |       |  |

|                  | 1 = PMA<2:0> function as either address lines or address latch strobes<br>0 = PMA<2:0> function as port I/Os              |                                       |               |                   |                 |                    |       |  |

| R/W-0   | U-0    |

|---------|-----|-----|-----|-----|-----|-----|--------|

| IOCON   |     | —   | —   | —   | —   | —   | —      |

| bit 15  |     |     |     |     |     |     | bit 8  |

|         |     |     |     |     |     |     |        |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| —       | —   | —   | —   | —   | —   | —   | PMPTTL |

| bit 7   |     | •   | •   | •   |     |     | bit 0  |

|         |     |     |     |     |     |     |        |

| Legend: |     |     |     |     |     |     |        |

|         |     |     |     |     |     | (0) |        |

## REGISTER 20-9: PADCON: PAD CONFIGURATION CONTROL REGISTER

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15 IOCON: Used for Non-PMP functionality

bit 14-1 Unimplemented: Read as '0'

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

# 22.0 32-BIT PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS30009729), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

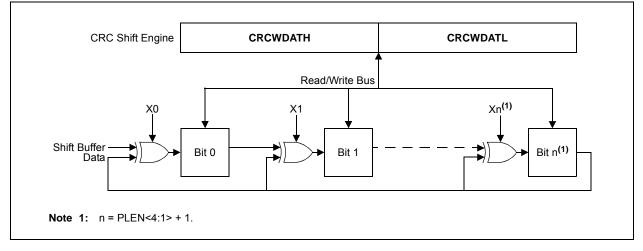

**CRC BLOCK DIAGRAM**

**FIGURE 22-1:**

The 32-bit programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-Programmable CRC Polynomial Equation, up to 32 Bits

- Programmable Shift Direction (little or big-endian)

- Independent Data and Polynomial Lengths

- Configurable Interrupt Output

- Data FIFO

Figure 22-1 displays a simplified block diagram of the CRC generator. A simple version of the CRC shift engine is displayed in Figure 22-2.

#### CRCDATL CRCDATH **FIFO Empty** Variable FIFO (4x32, 8x16 or 16x8) Event CRCISEL CRCWDATH CRCWDATL 1 CRC Interrupt LENDIAN 0 Shift Buffer **CRC Shift Engine** Shift 0 Complete Event Shifter Clock 2 \* FCY

#### FIGURE 22-2: CRC SHIFT ENGINE DETAIL

© 2016 Microchip Technology Inc.

| R/W-0         | U-0                                                                                                                                                                                               | R/W-0                                                                       | R/W-0                                                     | R/W-0                        | R/W-0            | R/W-0                  | R/W-0      |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------|------------------|------------------------|------------|

| ADON          | —                                                                                                                                                                                                 | ADSIDL                                                                      | DMABM <sup>(1)</sup>                                      | DMAEN                        | MODE12           | FORM1                  | FORM0      |

| bit 15        |                                                                                                                                                                                                   |                                                                             |                                                           |                              |                  |                        | bit 8      |

|               |                                                                                                                                                                                                   |                                                                             |                                                           |                              |                  |                        |            |

| R/W-0         | R/W-0                                                                                                                                                                                             | R/W-0                                                                       | R/W-0                                                     | U-0                          | R/W-0            | R/W-0, HSC             | R/C-0, HSC |

| SSRC3         | SSRC2                                                                                                                                                                                             | SSRC1                                                                       | SSRC0                                                     |                              | ASAM             | SAMP                   | DONE       |

| bit 7         |                                                                                                                                                                                                   |                                                                             |                                                           |                              |                  |                        | bit        |

| Legend:       |                                                                                                                                                                                                   | C = Clearable                                                               | e bit                                                     | U = Unimplen                 | nented bit, read | d as 'O'               |            |

| R = Readable  | bit                                                                                                                                                                                               | W = Writable                                                                | bit                                                       | •                            | are Settable/C   |                        |            |

| -n = Value at | POR                                                                                                                                                                                               | '1' = Bit is set                                                            |                                                           | '0' = Bit is clea            | ared             | x = Bit is unkn        | own        |

| bit 15        |                                                                                                                                                                                                   | Operating Mode<br>rerter is operation<br>rerter is off                      |                                                           |                              |                  |                        |            |

| bit 14        | Unimplemen                                                                                                                                                                                        | ted: Read as '                                                              | 0'                                                        |                              |                  |                        |            |

| bit 13        | ADSIDL: A/D                                                                                                                                                                                       | Stop in Idle M                                                              | ode bit                                                   |                              |                  |                        |            |