Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga702t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

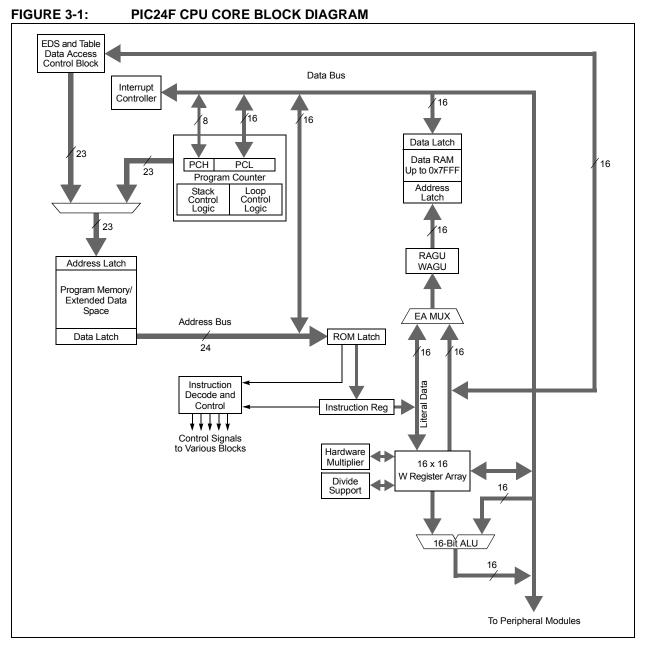

| TABLE 3-1: CPU CORE REGISTER |

|------------------------------|

|------------------------------|

| Register(s) Name | Description                        |  |

|------------------|------------------------------------|--|

| W0 through W15   | Working Register Array             |  |

| PC               | 23-Bit Program Counter             |  |

| SR               | ALU STATUS Register                |  |

| SPLIM            | Stack Pointer Limit Value Register |  |

| TBLPAG           | Table Memory Page Address Register |  |

| RCOUNT           | REPEAT Loop Counter Register       |  |

| CORCON           | CPU Control Register               |  |

| DISICNT          | Disable Interrupt Count Register   |  |

| DSRPAG           | Data Space Read Page Register      |  |

| DSWPAG           | Data Space Write Page Register     |  |

# 8.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the PIC24FJ256GA705 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **"Interrupts"** (DS70000600) in the *"dsPIC33/PIC24 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24FJ256GA705 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24FJ256GA705 family CPU.

The interrupt controller has the following features:

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Fixed Interrupt Entry and Return Latencies

## 8.1 Interrupt Vector Table

The PIC24FJ256GA705 family Interrupt Vector Table (IVT), shown in Figure 8-1, resides in program memory starting at location, 000004h. The IVT contains 6 non-maskable trap vectors and up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The AIVTEN (INTCON2<8>) control bit provides access to the AIVT. If the AIVTEN bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application, and a support environment, without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24FJ256GA705 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"I/O Ports with Peripheral Pin Select (PPS)"* (DS39711), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

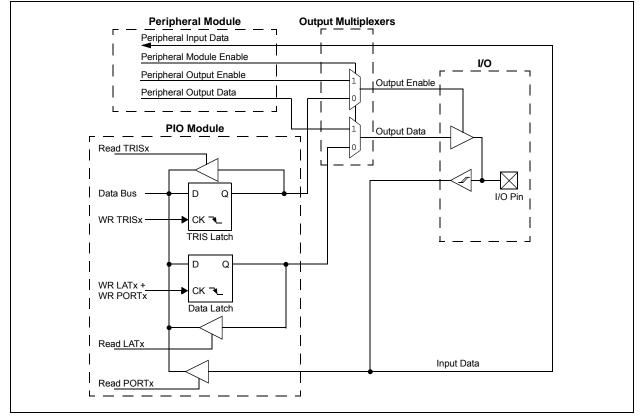

All of the device pins (except VDD, VSS, MCLR and OSCI/CLKI) are shared between the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger (ST) inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/Os and one register associated with their operation as analog inputs. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch register (LATx), read the latch; writes to the latch, write the latch. Reads from the PORTx register, read the port pins; writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers, and the port pin, will read as zeros. Table 11-3 through Table 11-5 show ANSELx bits and ports availability for device variants. When a pin is shared with another peripheral or function that is defined as an input only, it is regarded as a dedicated port because there is no other competing source of inputs.

## FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

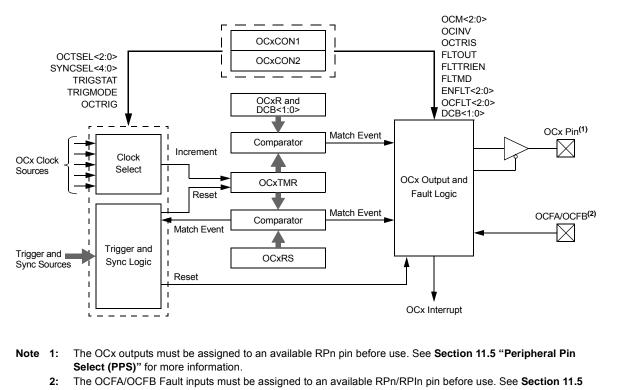

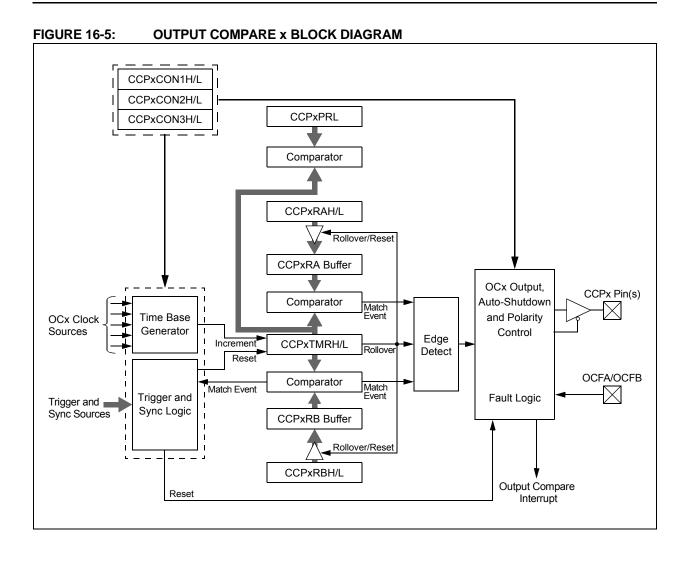

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

"Peripheral Pin Select (PPS)" for more information.

## 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for Single-Shot or Continuous mode pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins if available on the OCx module you are using. Otherwise, configure the dedicated OCx output pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation (= 0xx).

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure Trigger mode operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the Trigger or Sync source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no Sync/Trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a Trigger source event occurs.

| SYNC<4:0> | Synchronization Source                            |

|-----------|---------------------------------------------------|

| 11111     | None; Timer with Rollover on CCPxPR Match or FFFh |

| 11110     | Reserved                                          |

| 11101     | Reserved                                          |

| 11100     | CTMU Trigger                                      |

| 11011     | A/D Start Conversion                              |

| 11010     | CMP3 Trigger                                      |

| 11001     | CMP2 Trigger                                      |

| 11000     | CMP1 Trigger                                      |

| 10111     | Reserved                                          |

| 10110     | Reserved                                          |

| 10101     | Reserved                                          |

| 10100     | Reserved                                          |

| 10011     | Reserved                                          |

| 10010     | Reserved                                          |

| 10001     | CLC2 Out                                          |

| 10000     | CLC1 Out                                          |

| 01111     | Reserved                                          |

| 01110     | Reserved                                          |

| 01101     | Reserved                                          |

| 01100     | Reserved                                          |

| 01011     | INT2 Pad                                          |

| 01010     | INT1 Pad                                          |

| 01001     | INTO Pad                                          |

| 01000     | Reserved                                          |

| 00111     | Reserved                                          |

| 00110     | Reserved                                          |

| 00101     | MCCP4 Sync Out                                    |

| 00100     | MCCP3 Sync Out                                    |

| 00011     | MCCP2 Sync Out                                    |

| 00010     | MCCP1 Sync Out                                    |

| 00001     | MCCPx Sync Out <sup>(1)</sup>                     |

| 00000     | MCCPx Timer Sync Out <sup>(1)</sup>               |

## TABLE 16-5: SYNCHRONIZATION SOURCES

**Note 1:** CCP1 when connected to CCP1, CCP2 when connected to CCP2, etc.

## 17.4 SPI Control Registers

#### REGISTER 17-1: SPIxCON1L: SPIx CONTROL REGISTER 1 LOW

| R/W-0               | U-0                                   | R/W-0               | R/W-0                      | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |

|---------------------|---------------------------------------|---------------------|----------------------------|-------------------------|-------------------------|----------------|--------------------|

| SPIEN               | —                                     | SPISIDL             | DISSDO                     | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP            | CKE <sup>(1)</sup> |

| bit 15              | ·                                     |                     |                            | •                       |                         |                | bit 8              |

|                     |                                       |                     |                            |                         |                         |                |                    |

| R/W-0               | R/W-0                                 | R/W-0               | R/W-0                      | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |

| SSEN <sup>(2)</sup> | CKP                                   | MSTEN               | DISSDI                     | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE          | ENHBUF             |

| bit 7               |                                       |                     |                            |                         |                         |                | bit (              |

| Legend:             |                                       |                     |                            |                         |                         |                |                    |

| R = Readab          | le bit                                | W = Writable        | oit                        | U = Unimplem            | nented bit, read        | as '0'         |                    |

| -n = Value a        | t POR                                 | '1' = Bit is set    |                            | '0' = Bit is clea       | ared                    | x = Bit is unk | nown               |

| bit 15              | SPIEN: SPIX                           | On bit              |                            |                         |                         |                |                    |

|                     | 1 = Enables r                         | nodule              |                            |                         |                         |                |                    |

|                     | 0 = Turns off<br>modificati           |                     | odule, disable             | es clocks, disab        | les interrupt eve       | ent generatio  | n, allows SFF      |

| bit 14              | Unimplement                           | ted: Read as 'd     | )'                         |                         |                         |                |                    |

| bit 13              | SPISIDL: SPI                          | x Stop in Idle M    | lode bit                   |                         |                         |                |                    |

|                     | 1 = Halts in Cl                       | PU Idle mode        |                            |                         |                         |                |                    |

|                     | 0 = Continues                         | to operate in 0     | CPU Idle mod               | е                       |                         |                |                    |

| bit 12              | DISSDO: Disa                          | able SDOx Out       | put Port bit               |                         |                         |                |                    |

|                     |                                       |                     |                            | oin is controlled       | by the port funct       | ion            |                    |

|                     |                                       | is controlled by    |                            | 0                       |                         |                |                    |

| bit 11-10           |                                       | Serial Word         | Length bits <sup>(1,</sup> | 4)                      |                         |                |                    |

|                     | <u>AUDEN = 0:</u>                     |                     |                            |                         |                         |                |                    |

|                     | MODE32                                | 2 MODE16<br>x       | COMMUN<br>32-Bit           | ICATION                 |                         |                |                    |

|                     | 0                                     | 1                   | 16-Bit                     |                         |                         |                |                    |

|                     | 0                                     | 0                   | 8-Bit                      |                         |                         |                |                    |

|                     | AUDEN = 1:                            |                     |                            |                         |                         |                |                    |

|                     | MODE32                                | 2 MODE16            | COMMUN                     | ICATION                 |                         |                |                    |

|                     | 1                                     | 1                   |                            |                         | 2-Bit Channel/6         |                |                    |

|                     | 1                                     | 0                   |                            |                         | 2-Bit Channel/6         |                |                    |

|                     | 0                                     | 1                   |                            |                         | 2-Bit Channel/64        |                |                    |

| hit 0               |                                       | U<br>ata Innut Sama |                            | а, то-dil гіго, т       | 6-Bit Channel/32        |                |                    |

| bit 9               |                                       | ata Input Samp      | ie Fliase bit              |                         |                         |                |                    |

|                     | <u>Master Mode:</u><br>1 = Input data | is sampled at       | the end of dat             | ta output time          |                         |                |                    |

|                     |                                       |                     |                            | data output time        | 9                       |                |                    |

|                     | Slave Mode:                           |                     |                            |                         |                         |                |                    |

|                     |                                       | lways sampled       | at the middle              | e of data output        | time, regardless        | of the SMP s   | setting.           |

|                     | When AUDEN = 1                        |                     |                            | CKE = 0, regard         | dless of its actua      | al value.      |                    |

|                     | Vhen FRMEN = 1                        |                     |                            |                         |                         |                |                    |

|                     | ICLKEN can only                       |                     |                            |                         |                         |                |                    |

| 4: T                | his channel is no                     | ot meaningful fo    | or DSP/PCM r               | node as LRC fo          | llows the FRMS          | YPW bit.       |                    |

4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

| U-0          | U-0                                                                                                                                                                                                                 | U-0              | R/W-0                                 | R/W-0              | U-0   | U-0             | R/W-0    |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|--------------------|-------|-----------------|----------|--|

| —            | —                                                                                                                                                                                                                   | —                | FRMERREN                              | BUSYEN             | —     | —               | SPITUREN |  |

| bit 15       |                                                                                                                                                                                                                     |                  |                                       |                    |       |                 | bit 8    |  |

|              |                                                                                                                                                                                                                     |                  |                                       |                    |       |                 |          |  |

| R/W-0        | R/W-0                                                                                                                                                                                                               | R/W-0            | U-0                                   | R/W-0              | U-0   | R/W-0           | R/W-0    |  |

| SRMTEN       | SPIROVEN                                                                                                                                                                                                            | SPIRBEN          | —                                     | SPITBEN            | —     | SPITBFEN        | SPIRBFEN |  |

| bit 7        |                                                                                                                                                                                                                     |                  |                                       |                    |       |                 | bit C    |  |

|              |                                                                                                                                                                                                                     |                  |                                       |                    |       |                 |          |  |

| Legend:      |                                                                                                                                                                                                                     |                  |                                       |                    |       |                 |          |  |

| R = Readab   |                                                                                                                                                                                                                     | W = Writable     | bit                                   | U = Unimpleme      |       |                 |          |  |

| -n = Value a | t POR                                                                                                                                                                                                               | '1' = Bit is set |                                       | '0' = Bit is clear | red   | x = Bit is unkr | iown     |  |

| bit 15-13    | Unimplomen                                                                                                                                                                                                          | ted. Dood oo '   | 0'                                    |                    |       |                 |          |  |

| bit 12       | -                                                                                                                                                                                                                   | ted: Read as '   | o<br>Ipt Events via FF                |                    |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | in interrupt even                     |                    |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | nerate an interru                     |                    |       |                 |          |  |

| bit 11       | BUSYEN: En                                                                                                                                                                                                          | able Interrupt I | Events via SPIBI                      | JSY bit            |       |                 |          |  |

|              | 1 = SPIBUSY                                                                                                                                                                                                         | generates an     | interrupt event                       |                    |       |                 |          |  |

|              | 0 = SPIBUSY                                                                                                                                                                                                         | does not gene    | erate an interrup                     | t event            |       |                 |          |  |

| bit 10-9     | Unimplemen                                                                                                                                                                                                          | ted: Read as '   | 0'                                    |                    |       |                 |          |  |

| bit 8        |                                                                                                                                                                                                                     |                  | t Events via SPI                      |                    |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | R) generates an<br>not generate ar    |                    |       |                 |          |  |

| bit 7        | SRMTEN: En                                                                                                                                                                                                          | able Interrupt I | Events via SRM                        | T bit              |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | RMT) generates<br>es not generate     |                    |       |                 |          |  |

| bit 6        | SPIROVEN:                                                                                                                                                                                                           | Enable Interrup  | ot Events via SP                      | IROV bit           |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | generates an inte<br>does not genera  |                    | vent  |                 |          |  |

| bit 5        | SPIRBEN: Er                                                                                                                                                                                                         | nable Interrupt  | Events via SPIR                       | BE bit             |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | pty generates ar<br>pty does not ger  |                    |       |                 |          |  |

| bit 4        | Unimplemen                                                                                                                                                                                                          | ted: Read as '   | 0'                                    |                    |       |                 |          |  |

| bit 3        | SPITBEN: Er                                                                                                                                                                                                         | able Interrupt   | Events via SPIT                       | BE bit             |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | npty generates a<br>npty does not ge  |                    |       |                 |          |  |

| bit 2        | Unimplemen                                                                                                                                                                                                          | ted: Read as '   | 0'                                    |                    |       |                 |          |  |

| bit 1        | SPITBFEN: E                                                                                                                                                                                                         | Enable Interrup  | t Events via SPI                      | TBF bit            |       |                 |          |  |

|              |                                                                                                                                                                                                                     |                  | II generates an i<br>II does not gene |                    | event |                 |          |  |

| bit 0        | SPIRBFEN: E                                                                                                                                                                                                         | Enable Interrup  | t Events via SPI                      | RBF bit            |       |                 |          |  |

|              | <ul> <li>0 = SPIx Transmit Buffer Full does not generate an interrupt event</li> <li>SPIRBFEN: Enable Interrupt Events via SPIRBF bit</li> <li>1 = SPIx Receive Buffer Full generates an interrupt event</li> </ul> |                  |                                       |                    |       |                 |          |  |

## REGISTER 17-9: SPIXIMSKL: SPIX INTERRUPT MASK REGISTER LOW

| HSC, R-0      | HSC, R-0                       | HSC, R-0                                   | U-0                         | U-0                                  | HSC, R/C-0                               | HSC, R-0                 | HSC, R-0          |  |  |

|---------------|--------------------------------|--------------------------------------------|-----------------------------|--------------------------------------|------------------------------------------|--------------------------|-------------------|--|--|

| ACKSTAT       | TRSTAT                         | ACKTIM                                     |                             | —                                    | BCL                                      | GCSTAT                   | ADD10             |  |  |

| bit 15        |                                |                                            |                             |                                      |                                          |                          | bit 8             |  |  |

|               |                                |                                            |                             |                                      |                                          |                          |                   |  |  |

| HS, R/C-0     | HS, R/C-0                      | HSC, R-0                                   | HSC, R/C-0                  | HSC, R/C-0                           | HSC, R-0                                 | HSC, R-0                 | HSC, R-0          |  |  |

| IWCOL         | I2COV                          | D/A                                        | Р                           | S                                    | R/W                                      | RBF                      | TBF               |  |  |

| bit 7         |                                |                                            |                             |                                      |                                          |                          | bit 0             |  |  |

|               |                                |                                            |                             |                                      |                                          |                          |                   |  |  |

| Legend:       |                                | C = Clearab                                |                             | HS = Hardware                        |                                          | '0' = Bit is clear       | red               |  |  |

| R = Readable  |                                | W = Writable                               |                             | •                                    | ented bit, read as                       |                          |                   |  |  |

| -n = Value at | POR                            | '1' = Bit is se                            | et                          | HSC = Hardwa                         | re Settable/Cleara                       | ble bit                  |                   |  |  |

| bit 15        | 1 = Acknowle                   |                                            | received fron               | n slave                              | er and Slave moo                         | les)                     |                   |  |  |

| bit 14        |                                | -                                          |                             | _                                    | aster; applicable to                     | o master transm          | it operation)     |  |  |

| DIL 14        | 1 = Master tr                  |                                            |                             | -                                    | aster, applicable t                      |                          |                   |  |  |

|               |                                | ansmit is not i                            | •                           |                                      |                                          |                          |                   |  |  |

| bit 13        | ACKTIM: Ac                     | knowledge Tii                              | ne Status bit               | (valid in I <sup>2</sup> C Sla       | ve mode only)                            |                          |                   |  |  |

|               | 1 = Indicates<br>0 = Not an A  | I <sup>2</sup> C bus is in<br>cknowledge s | an Acknowle<br>equence, cle | dge sequence, s<br>ared on 9th risin | set on 8th falling e<br>g edge of SCLx o | edge of SCLx clo<br>lock | ock               |  |  |

| bit 12-11     | Unimplemented: Read as '0'     |                                            |                             |                                      |                                          |                          |                   |  |  |

| bit 10        | BCL: Bus Co                    | llision Detect                             | bit (Master/S               | Slave mode; clea                     | ired when I <sup>2</sup> C mo            | dule is disabled,        | 12CEN = 0)        |  |  |

|               |                                |                                            |                             | luring a master o                    | or slave transmit o                      | operation                |                   |  |  |

|               |                                | ollision has be                            |                             |                                      |                                          |                          |                   |  |  |

| bit 9         |                                |                                            | •                           | ed after Stop def                    | ection)                                  |                          |                   |  |  |

|               |                                | call address w<br>call address w           |                             | /ed                                  |                                          |                          |                   |  |  |

| bit 8         | ADD10: 10-E                    | Bit Address St                             | atus bit (clea              | red after Stop de                    | etection)                                |                          |                   |  |  |

|               |                                | dress was ma                               |                             |                                      |                                          |                          |                   |  |  |

| 1.11.7        |                                | dress was not                              |                             |                                      |                                          |                          |                   |  |  |

| bit 7         | 1 = An attem                   |                                            |                             | register failed b                    | ecause the I <sup>2</sup> C m            | odule is busy; m         | ust be cleared    |  |  |

|               | in softwa<br>0 = No collis     |                                            |                             |                                      |                                          |                          |                   |  |  |

| bit 6         | 12COV: 12Cx                    |                                            | rflow Flag bit              |                                      |                                          |                          |                   |  |  |

|               | 1 = A byte w<br>care" in       | as received w<br>Transmit mod              | hile the I2Cx               |                                      | still holding the pr<br>e                | evious byte; I2C         | COV is a "don't   |  |  |

|               | 0 = No overflow                |                                            |                             |                                      |                                          |                          |                   |  |  |

| bit 5         | D/A: Data/Ad                   |                                            |                             | -                                    |                                          |                          |                   |  |  |

|               | 1 = Indicates<br>0 = Indicates |                                            |                             | was data<br>or transmitted v         | vas an address                           |                          |                   |  |  |

| bit 4         | P: I2Cx Stop                   |                                            |                             |                                      |                                          |                          |                   |  |  |

|               |                                | that a Stop b                              | it has been d               |                                      | when the I <sup>2</sup> C mo             | dule is disabled,        | <b>I2CEN =</b> 0. |  |  |

### REGISTER 18-3: I2CxSTAT: I2Cx STATUS REGISTER

# 20.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Parallel Master Port (EPMP)" (DS39730), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only) or 8-bit (Master and Slave modes) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD Controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each Chip Select, and then assigning each Chip Select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP. Key features of the EPMP module are:

- Extended Data Space (EDS) Interface Allows

Direct Access from the CPU

- Up to 10 Programmable Address Lines

- · Up to 2 Chip Select Lines

- Up to 2 Acknowledgment Lines (one per Chip Select)

- · 4-Bit or 8-Bit Wide Data Bus

- Programmable Strobe Options (per Chip Select):

- Individual read and write strobes or;

Read/Write strobe with enable strobe

- Programmable Address/Data Multiplexing

- Programmable Address Wait States

- Programmable Data Wait States (per Chip Select)

- Programmable Polarity on Control Signals (per Chip Select)

- · Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

Only the higher pin count packages in the family implement the EPMP. The EPMP feature is not available on 28-pin devices.

#### REGISTER 20-4: PMCON4: EPMP CONTROL REGISTER 4

| U-0                               | R/W-0      | R/W-0                                                                               | R/W-0         | R/W-0                              | R/W-0   | R/W-0              | R/W-0 |  |  |

|-----------------------------------|------------|-------------------------------------------------------------------------------------|---------------|------------------------------------|---------|--------------------|-------|--|--|

| _                                 | PTEN14     |                                                                                     |               | PTEN                               | <13:8>  |                    |       |  |  |

| bit 15                            |            |                                                                                     |               |                                    |         |                    | bit 8 |  |  |

| R/W-0                             | R/W-0      | R/W-0                                                                               | R/W-0         | R/W-0                              | R/W-0   | R/W-0              | R/W-0 |  |  |

|                                   |            | PTEN<7:3>                                                                           |               |                                    |         | PTEN<2:0>          |       |  |  |

| bit 7                             |            |                                                                                     |               |                                    | •       |                    | bit 0 |  |  |

|                                   |            |                                                                                     |               |                                    |         |                    |       |  |  |

| Legend:                           |            |                                                                                     |               |                                    |         |                    |       |  |  |

| R = Readable bit W = Writable bit |            |                                                                                     |               | U = Unimplemented bit, read as '0' |         |                    |       |  |  |

| -n = Value at                     | t POR      | '1' = Bit is set                                                                    |               | '0' = Bit is clea                  | ared    | x = Bit is unknown |       |  |  |

| bit 15                            | Unimpleme  | nted: Read as 'o                                                                    | )'            |                                    |         |                    |       |  |  |

| bit 14                            | PTEN14: PM | A14 Port Enabl                                                                      | e bit         |                                    |         |                    |       |  |  |

|                                   |            | functions as eith<br>functions as por                                               |               | ne 14 or Chip S                    | elect 1 |                    |       |  |  |

| bit 13-3                          | PTEN<13:3> | -: EPMP Addres                                                                      | s Port Enable | bits                               |         |                    |       |  |  |

|                                   |            | 1 = PMA<13:3> function as EPMP address lines<br>0 = PMA<13:3> function as port I/Os |               |                                    |         |                    |       |  |  |

| bit 2-0                           | PTEN<2:0>: | PMALU/PMALH                                                                         | H/PMALL Strol | be Enable bits                     |         |                    |       |  |  |

|                                   |            |                                                                                     |               |                                    |         |                    |       |  |  |

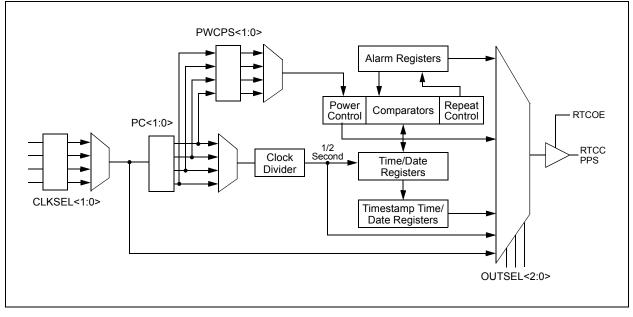

#### FIGURE 21-1: RTCC BLOCK DIAGRAM

#### 29.5 Program Verification and Code Protection

PIC24FJ256GA705 family devices offer basic implementation of CodeGuard<sup>™</sup> Security that supports General Segment (GS) security and Boot Segment (BS) security. This feature helps protect individual intellectual property.

| Note: | For more information on usage, configura-  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | tion and operation, refer to the "dsPIC33/ |  |  |  |  |  |  |  |

|       | PIC24 Family Reference Manual",            |  |  |  |  |  |  |  |

|       | "CodeGuard™ Intermediate Security"         |  |  |  |  |  |  |  |

|       | (DS70005182).                              |  |  |  |  |  |  |  |

#### 29.6 JTAG Interface

PIC24FJ256GA705 family devices implement a JTAG interface, which supports boundary scan device testing.

#### 29.7 In-Circuit Serial Programming

PIC24FJ256GA705 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGCx) and data (PGDx), and three other lines for power (VDD), ground (Vss) and MCLR. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

#### 29.8 Customer OTP Memory

PIC24FJ256GA705 family devices provide 256 bytes of One-Time-Programmable (OTP) memory, located at addresses, 801700h through 8017FEh. This memory can be used for persistent storage of application-specific information that will not be erased by reprogramming the device. This includes many types of information, such as (but not limited to):

- Application checksums

- Code revision information

- Product information

- Serial numbers

- System manufacturing dates

- Manufacturing lot numbers

OTP memory cannot be written by program execution (i.e., TBLWT instructions); it can only be written during device programming. Data is not cleared by a chip erase.

Note: Data in the OTP memory section MUST NOT be programmed more than once.

#### 29.9 In-Circuit Debugger

This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. Debugging functionality is controlled through the PGCx (Emulation/Debug Clock) and PGDx (Emulation/Debug Data) pins.

To use the in-circuit debugger function of the device, the design must implement  $ICSP^{TM}$  connections to  $\overline{MCLR}$ , VDD, Vss and the PGCx/PGDx pin pair, designated by the ICS<1:0> Configuration bits. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

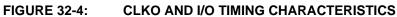

#### TABLE 32-22: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                      | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |            |  |

|--------------------|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                       | Min                                                                                                                          | Typ <sup>(1)</sup> | Мах | Units | Conditions |  |

| DO31               | TIOR   | Port Output Rise Time                | —                                                                                                                            | 10                 | 25  | ns    |            |  |

| DO32               | TIOF   | Port Output Fall Time                | _                                                                                                                            | 10                 | 25  | ns    |            |  |

| DI35               | TINP   | INTx Pin High or Low<br>Time (input) | 1                                                                                                                            | —                  | —   | Тсү   |            |  |

| DI40               | Trbp   | CNx High or Low Time<br>(input)      | 1                                                                                                                            | —                  | —   | Тсү   |            |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

| АС СН        | AC CHARACTERISTICS |                                                                |                                     | Standard Operating Conditions:2.0V to 3.6V (unless otherwise state<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |             |       |                                 |  |  |

|--------------|--------------------|----------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|-------|---------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                                 | Min                                 | Тур                                                                                                                         | Мах         | Units | Conditions                      |  |  |

| SY10         | TMCL               | MCLR Pulse Width (Low)                                         | 2                                   | -                                                                                                                           | _           | μS    |                                 |  |  |

| SY12         | TPOR               | Power-on Reset Delay                                           | _                                   | 2                                                                                                                           | _           | μS    |                                 |  |  |

| SY13         | Tioz               | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | Lesser of:<br>(3 Tcy + 2)<br>or 700 | _                                                                                                                           | (3 Tcy + 2) | μS    |                                 |  |  |

| SY25         | TBOR               | Brown-out Reset Pulse<br>Width                                 | 1                                   |                                                                                                                             | —           | μS    | $V \text{DD} \leq V \text{BOR}$ |  |  |

| SY45         | Trst               | Internal State Reset Time                                      | _                                   | 50                                                                                                                          |             | μS    |                                 |  |  |

| SY71         | Трм                | Program Memory<br>Wake-up Time                                 | —                                   | 20                                                                                                                          | —           | μS    | Sleep wake-up with<br>VREGS = 1 |  |  |

|              |                    |                                                                | —                                   | 1                                                                                                                           | —           | μS    | Sleep wake-up with<br>VREGS = 0 |  |  |

| SY72         | Tlvr               | Low-Voltage Regulator<br>Wake-up Time                          | —                                   | 90                                                                                                                          | —           | μS    | Sleep wake-up with<br>VREGS = 1 |  |  |

|              |                    |                                                                | —                                   | 70                                                                                                                          | —           | μS    | Sleep wake-up with<br>VREGS = 0 |  |  |

#### TABLE 32-23: RESET AND BROWN-OUT RESET REQUIREMENTS

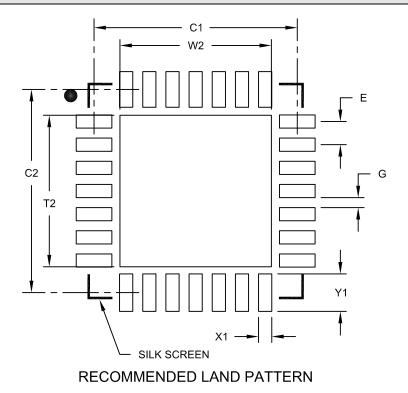

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |                 | MILLIM | ETERS    |      |  |

|----------------------------|-----------------|--------|----------|------|--|

| Dimensio                   | MIN             | NOM    | MAX      |      |  |

| Contact Pitch              | Contact Pitch E |        | 0.65 BSC |      |  |

| Optional Center Pad Width  | W2              |        |          | 4.25 |  |

| Optional Center Pad Length | T2              |        |          | 4.25 |  |

| Contact Pad Spacing        | C1              |        | 5.70     |      |  |

| Contact Pad Spacing        | C2              |        | 5.70     |      |  |

| Contact Pad Width (X28)    | X1              |        |          | 0.37 |  |

| Contact Pad Length (X28)   | Y1              |        |          | 1.00 |  |

| Distance Between Pads      | G               | 0.20   |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

NOTES:

| Product Identification System     | 409 |

|-----------------------------------|-----|

| Program Memory Space              |     |

| Access Using Table Instructions   | 60  |

| Addressing                        | 58  |

| Configuration Bits                |     |

| Code-Protect                      | 44  |

| Overview                          | 43  |

| Configuration Word Addresses      | 43  |

| Customer OTP Memory               | 44  |

| Hard Memory Vectors               |     |

| Memory Map                        | 42  |

| Organization                      |     |

| Reading Data Using EDS            | 61  |

| Sizes and Boundaries              |     |

| Program Verification              | 344 |

| Pulse-Width Modulation (PWM) Mode | 175 |

| Pulse-Width Modulation. See PWM.  |     |

| PWM                               |     |

| Duty Cycle and Period             | 176 |

#### R

| Real-Time Clock and Calendar (RTCC)        | 251   |

|--------------------------------------------|-------|

| Reference Clock Output                     | 109   |

| Referenced Sources                         | 13    |

| Register Summary                           |       |

| Peripheral Module Disable (PMD)            | 116   |

| Registers                                  |       |

| AD1CHITL (A/D Scan Compare Hit, Low Word   |       |

| AD1CHS (A/D Sample Select)                 |       |

| AD1CON1 (A/D Control 1)                    |       |

| AD1CON2 (A/D Control 2)                    |       |

| AD1CON3 (A/D Control 3)                    |       |

| AD1CON4 (A/D Control 4)                    |       |

| AD1CON5 (A/D Control 5)                    |       |

| AD1CSSH (A/D Input Scan Select, High Word) |       |

| AD1CSSL (A/D Input Scan Select, Low Word)  |       |

| AD1CTMENH (A/D CTMU Enable, High Word)     |       |

| AD1CTMENL (A/D CTMU Enable, Low Word)      |       |

| ALMDATEH (RTCC Alarm Date High)            |       |

| ALMDATEL (RTCC Alarm Date Low)             |       |

| ALMTIMEH (RTCC Alarm Time High)            |       |

| ALMTIMEL (RTCC Alarm Time Low)             | 262   |

| ANCFG (A/D Band Gap Reference              |       |

| Configuration)                             |       |

| ANSELx (Analog Select for PORTx)           |       |

| CCPxCON1H (CCPx Control 1 High)            |       |

| CCPxCON1L (CCPx Control 1 Low)             |       |

| CCPxCON2H (CCPx Control 2 High)            |       |

| CCPxCON2L (CCPx Control 2 Low)             |       |

| CCPxCON3H (CCPx Control 3 High)            |       |

| CCPxCON3L (CCPx Control 3 Low)             |       |

| CCPxSTATH (CCPx Status High)               |       |

| CCPxSTATL (CCPx Status Low)                |       |

| CLCxCONH (CLCx Control High)               |       |

| CLCxCONL (CLCx Control Low)                | 280   |

| CLCxGLSH (CLCx Gate Logic Input            |       |

| Select High)                               | 285   |

| CLCxGLSL (CLCx Gate Logic Input            |       |

| Select Low)                                |       |

| CLCxSEL (CLCx Input MUX Select)            |       |

| CLKDIV (Clock Divider)                     |       |

| CMSTAT (Comparator Module Status)          | 313   |

| CMxCON (Comparator x Control,              |       |

| Comparators 1 Through 3)                   | 312   |

| CORCON (CPU Core Control)                  | 9, 92 |

| CRCCON1 (CRC Control 1)                    | 274   |

| CRCCON2 (CRC Control 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRCXORH (CRC XOR Polynomial, High Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CRCXORL (CRC XOR Polynomial, Low Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 276                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CTMUCON1H (CTMU Control 1 High)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CTMUCON1L (CTMU Control 1 Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CTMUCON2L (CTMU Control 2 Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 325                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |