#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT              |

| Number of I/O              | 22                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

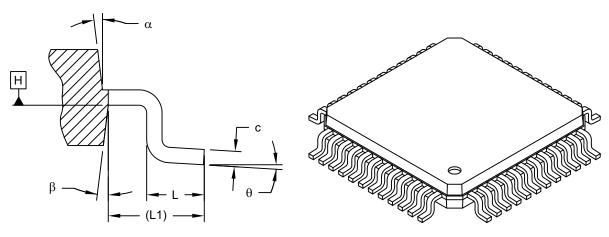

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga702t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin      | F                           | Pin Number/Grid Locator |                |                    |     |                  |                                                               |  |

|----------|-----------------------------|-------------------------|----------------|--------------------|-----|------------------|---------------------------------------------------------------|--|

| Function | 28-Pin SOIC,<br>SSOP, SPDIP | 28-Pin QFN,<br>UQFN     | 44-Pin<br>TQFP | 48-Pin<br>QFN/TQFP | I/O | Input<br>Buffer  | Description                                                   |  |

| SCL1     | 17                          | 14                      | 44             | 48                 | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output                    |  |

| SCL2     | 7                           | 4                       | 24             | 26                 | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output                    |  |

| SDA1     | 18                          | 15                      | 1              | 1                  | I/O | l <sup>2</sup> C | I2C1 Data Input/Output                                        |  |

| SDA2     | 6                           | 3                       | 23             | 25                 | I/O | l <sup>2</sup> C | I2C2 Data Input/Output                                        |  |

| SOSCI    | 11                          | 8                       | 33             | 36                 | Ι   | ANA/ST           | Secondary Oscillator/Timer1 Clock Input                       |  |

| SOSCO    | 12                          | 9                       | 34             | 37                 | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output                      |  |

| T1CK     | 18                          | 15                      | 1              | 1                  | I   | ST               | Timer1 Clock                                                  |  |

| ТСК      | 17                          | 14                      | 13             | 14                 | -   | ST               | JTAG Test Clock/Programming Clock Input                       |  |

| TDI      | 21                          | 18                      | 35             | 38                 | Ι   | ST               | JTAG Test Data/Programming Data Input                         |  |

| TDO      | 18                          | 15                      | 32             | 35                 | 0   | DIG              | JTAG Test Data Output                                         |  |

| TMPRN    | 18                          | 15                      | 1              | 1                  | Ι   | ST               | Tamper Detect Input                                           |  |

| TMS      | 22                          | 19                      | 12             | 13                 | I   | ST               | JTAG Test Mode Select Input                                   |  |

| VCAP     | 20                          | 17                      | 7              | 7                  | Р   | —                | External Filter Capacitor<br>Connection (regulator enabled)   |  |

| Vdd      | 13, 28                      | 10, 25                  | 28, 40         | 30, 43             | Ρ   | —                | Positive Supply for Peripheral Digital Logic and I/O Pins     |  |

| VREF+    | 2                           | 27                      | 19             | 21                 | I   | ANA              | Comparator and A/D Reference Voltage (high) Input             |  |

| VREF-    | 3                           | 28                      | 20             | 22                 | Ι   | ANA              | Comparator and A/D Reference Voltage (low) Input              |  |

| Vss      | 8, 19, 27                   | 5, 16, 24               | 6, 29, 39      | 6, 31, 42          | Р   | —                | Ground Reference for<br>Peripheral Digital Logic and I/O Pins |  |

#### **TABLE 1-3:** PIC24FJ256GA705 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer Legend: ANA = Analog level input/output DIG = Digital input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

# 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| -       -       -       -       -       -         bit 15         R/W-0 <sup>(1)</sup> R/W-0 <sup>(1)</sup> R/W-0 <sup>(1)</sup> R/W-0       R/W-0         IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA       N       OV       Z         bit 7         Legend:       R       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       DC: ALU Half Carry/Borrow bit       1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         110 = CPU Interrupt Priority Level is 5 (13)         100 = CPU Interrupt Priority Level is 4 (12)         011 = CPU Interrupt Priority Level is 3 (11)         010 = CPU Interrupt Priority Level is 1 (9)         000 = CPU Interrupt Priority Level is 0 (8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC<br>bit                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| R/W-0 <sup>(1)</sup> R/W-0 <sup>(1)</sup> R/W-0 <sup>(1)</sup> R-0       R/W-0       R/W-0       R/W-0         IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA       N       OV       Z         bit 7    Legend:        R = Readable bit         W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       DC: ALU Half Carry/Borrow bit       1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred         0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred       0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 6 (14)         101 = CPU Interrupt Priority Level is 6 (14)       101 = CPU Interrupt Priority Level is 6 (13)         100 = CPU Interrupt Priority Level is 3 (11)       010 = CPU Interrupt Priority Level is 3 (11)         010 = CPU Interrupt Priority Level is 1 (9)       001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA       N       OV       Z         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       bit 8       DC: ALU Half Carry/Borrow bit         1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred       0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         110 = CPU Interrupt Priority Level is 5 (13)       100 = CPU Interrupt Priority Level is 5 (13)         101 = CPU Interrupt Priority Level is 3 (11)       010 = CPU Interrupt Priority Level is 2 (10)         011 = CPU Interrupt Priority Level is 2 (10)       001 = CPU Interrupt Priority Level is 2 (10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA       N       OV       Z         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       DC: ALU Half Carry/Borrow bit         1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred       0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         110 = CPU Interrupt Priority Level is 5 (13)       100 = CPU Interrupt Priority Level is 5 (13)         101 = CPU Interrupt Priority Level is 4 (12)       011 = CPU Interrupt Priority Level is 3 (11)         010 = CPU Interrupt Priority Level is 2 (10)       001 = CPU Interrupt Priority Level is 2 (10)         011 = CPU Interrupt Priority Level is 1 (9)       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknowr bit 15-9 Unimplemented: Read as '0' bit 8 DC: ALU Half Carry/Borrow bit 1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred 0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 3 (11) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0<br>C                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       bit 8       DC: ALU Half Carry/Borrow bit         1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-s of the result occurred       0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         110 = CPU Interrupt Priority Level is 6 (14)       101 = CPU Interrupt Priority Level is 5 (13)         100 = CPU Interrupt Priority Level is 3 (11)       010 = CPU Interrupt Priority Level is 2 (10)         001 = CPU Interrupt Priority Level is 1 (9)       011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'         bit 8       DC: ALU Half Carry/Borrow bit         1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-softhe result occurred         0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         100 = CPU Interrupt Priority Level is 5 (13)         100 = CPU Interrupt Priority Level is 4 (12)         011 = CPU Interrupt Priority Level is 3 (11)         010 = CPU Interrupt Priority Level is 2 (10)         001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIL                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Image: n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-9       Unimplemented: Read as '0'       DC: ALU Half Carry/Borrow bit       1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-softher result occurred         0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred       0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bits of the result has occurred         bit 7-5       IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup> 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled         100 = CPU Interrupt Priority Level is 5 (13)         100 = CPU Interrupt Priority Level is 4 (12)         011 = CPU Interrupt Priority Level is 3 (11)         010 = CPU Interrupt Priority Level is 2 (10)         011 = CPU Interrupt Priority Level is 2 (10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <ul> <li>bit 15-9 Unimplemented: Read as '0'</li> <li>bit 8 DC: ALU Half Carry/Borrow bit</li> <li>1 = A carry out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-s of the result occurred</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>bit 7-5 IPL&lt;2:0&gt;: CPU Interrupt Priority Level Status bits<sup>(1,2)</sup></li> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>101 = CPU Interrupt Priority Level is 6 (14)</li> <li>101 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 3 (11)</li> <li>010 = CPU Interrupt Priority Level is 2 (10)</li> <li>001 = CPU Interrupt Priority Level is 1 (9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <ul> <li>bit 8</li> <li>DC: ALU Half Carry/Borrow bit</li> <li>1 = A carry out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-s of the result occurred</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>bit 7-5</li> <li>IPL&lt;2:0&gt;: CPU Interrupt Priority Level Status bits<sup>(1,2)</sup></li> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>100 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 4 (12)</li> <li>011 = CPU Interrupt Priority Level is 3 (11)</li> <li>010 = CPU Interrupt Priority Level is 2 (10)</li> <li>001 = CPU Interrupt Priority Level is 1 (9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| <ul> <li>DC: ALU Half Carry/Borrow bit</li> <li>1 = A carry out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-s of the result occurred</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry/Borrow bit</li> <li>1 = A carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry/Borrow bit</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry/Borrow bit</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>DE: ALU Half Carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of 10<sup>th</sup> low out from the 4<sup>th</sup> low out fro</li></ul> |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <ul> <li>1 = A carry out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-s of the result occurred</li> <li>0 = No carry out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> <li>bit 7-5</li> <li>IPL&lt;2:0&gt;: CPU Interrupt Priority Level Status bits<sup>(1,2)</sup></li> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>110 = CPU Interrupt Priority Level is 6 (14)</li> <li>101 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 4 (12)</li> <li>011 = CPU Interrupt Priority Level is 3 (11)</li> <li>010 = CPU Interrupt Priority Level is 2 (10)</li> <li>001 = CPU Interrupt Priority Level is 1 (9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| of the result occurred<br>0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred<br><b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred<br><b>IPL&lt;2:0&gt;:</b> CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | sized dat                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| bit 7-5<br>IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <pre>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <pre>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| <ul> <li>101 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 4 (12)</li> <li>011 = CPU Interrupt Priority Level is 3 (11)</li> <li>010 = CPU Interrupt Priority Level is 2 (10)</li> <li>001 = CPU Interrupt Priority Level is 1 (9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 001 = CPU Interrupt Priority Level is 1 (9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| bit 4 RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 1 = REPEAT loop is in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                     |  |  |  |  |  |  |  |  |  |