#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u7cvm08ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Modules List**

## 3 Modules List

The i.MX 6Solo/6DualLite processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block Mnemonic                                            | Block Name                                           | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----------------------------------------------------------|------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ARM                                                       | ARM Platform                                         | ARM                           | The ARM Core Platform includes 1x (Solo) Cortex-A9 core for i.MX 6Solo and 2x (Dual) Cortex-A9 cores for i.MX 6DualLite. It also includes associated sub-blocks, such as the Level 2 Cache Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller), private timers, watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                       |  |  |  |

| APBH-DMA                                                  | NAND Flash and BCH<br>ECC DMA controller             | System Control<br>Peripherals | DMA controller used for GPMI2 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ASRC                                                      | Asynchronous Sample<br>Rate Converter                | Multimedia<br>Peripherals     | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                                            |  |  |  |

| AUDMUX                                                    | Digital Audio Mux                                    | Multimedia<br>Peripherals     | The AUDMUX is a programmable interconnect for voice,<br>audio, and synchronous data routing between host<br>serial interfaces (for example, SSI1, SSI2, and SSI3)<br>and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical<br>functionality and programming models. A desired<br>connectivity is achieved by configuring two or more<br>AUDMUX ports.                                                                                                                                                                                           |  |  |  |

| BCH40                                                     | Binary-BCH ECC<br>Processor                          | System Control<br>Peripherals | The BCH40 module provides up to 40-bit ECC for NAND Flash controller (GPMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| CAAM Cryptographic<br>accelerator and<br>assurance module |                                                      | Security                      | CAAM is a cryptographic accelerator and assurance<br>module. CAAM implements several encryption and<br>hashing functions, a run-time integrity checker, and a<br>Pseudo Random Number Generator (PRNG). The<br>pseudo random number generator is certified by<br>Cryptographic Algorithm Validation Program (CAVP) of<br>National Institute of Standards and Technology (NIST).<br>Its DRBG validation number is 94 and its SHS validation<br>number is 1455.<br>CAAM also implements a Secure Memory mechanism.<br>In i.MX 6Solo/6DualLite processors, the security<br>memory provided is 16 KB. |  |  |  |

| ССМ                                                       | Clock Control Module,                                | Clocks, Resets, and           | These modules are responsible for clock and reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| GPC<br>SRC                                                | General Power Controller,<br>System Reset Controller | Power Control                 | distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CSI                                                       | MIPI CSI-2 i/f                                       | Multimedia<br>Peripherals     | The CSI IP provides MIPI CSI-2 standard camera<br>interface port. The CSI-2 interface supports from 80<br>Mbps to 1 Gbps speed per data lane.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

Table 2. i.MX 6Solo/6DualLite Modules List

| Block Mnemonic                | Block Name                                                                          | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|-------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-3<br>uSDHC-4 | SD/MMC and SDXC<br>Enhanced Multi-Media<br>Card / Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6Solo/6DualLite specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Conforms to the SD Host Controller Standard Specification version 3.0.</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4/4.41 including high-capacity (size &gt; 2 GB) cards HC MMC.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB and SDXC cards up to 2 TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v3.0</li> <li>All four ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>However, the SoC level integration and I/O muxing logic restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card detection" and "Write Protection" pads and do not support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve interfaces to embedded MMC memory or interfaces to on-board SDIO devices. These ports do not have "Card detection" and "Write Protection" pads and do support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power domain and port #4 shares power domain with some other interfaces.</li> </ul> |

| FlexCAN-1<br>FlexCAN-2        | Flexible Controller Area<br>Network                                                 | Connectivity<br>Peripherals | The CAN protocol was primarily, but not only, designed<br>to be used as a vehicle serial data bus, meeting the<br>specific requirements of this field: real-time processing,<br>reliable operation in the Electromagnetic interference<br>(EMI) environment of a vehicle, cost-effectiveness and<br>required bandwidth. The FlexCAN module is a full<br>implementation of the CAN protocol specification,<br>Version 2.0 B, which supports both standard and<br>extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 2. i.MX 6Solo/6DualLite Modules List (continued)

| Block Mnemonic | Block Name                       | Subsystem Brief Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------------|----------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IPUv3H         | Image Processing Unit,<br>ver.3H | Multimedia<br>Peripherals   | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation. The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces: <ul> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/CSI-2 receiver</li> </ul> </li> <li>The processing includes: <ul> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> </li> </ul> |  |  |  |

| KPP            | Key Pad Port                     | Connectivity<br>Peripherals | <ul> <li>KPP Supports 8x8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| LDB            | LVDS Display Bridge              | Connectivity<br>Peripherals | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image<br/>Processing Unit) to External LVDS Display Interface.</li> <li>LDB supports two channels; each channel has following<br/>signals: <ul> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad<br/>(PadP, PadM).</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| MMDC           | Multi-Mode DDR<br>Controller     | Connectivity<br>Peripherals | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32-bit DDR3-800 (LV) or LPDDR2-800 in i.MX 6Solo</li> <li>Supports 16/32/64-bit DDR3-800 (LV) or LPDDR2-800 in i.MX 6DualLite</li> <li>Supports 2x32 LPDDR2-800 in i.MX 6DualLite</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Table 2. i.MX 6Solo/6DualLite Module | s List (continued) |

|--------------------------------------|--------------------|

|--------------------------------------|--------------------|

#### **Modules List**

| Block Mnemonic                                 | Block Name                                | Subsystem                     | Brief DescriptionThe SSI is a full-duplex synchronous interface, which is<br>used on the AP to provide connectivity with off-chip<br>audio peripherals. The SSI supports a wide variety of<br>protocols (SSI normal, SSI network, I2S, and AC-97), bit<br>depths (up to 24 bits per word), and clock / frame sync<br>options.The SSI has two pairs of 8x24 FIFOs and hardware<br>support for an external DMA controller in order to<br>minimize its impact on system performance. The<br>second pair of FIFOs provides hardware interleaving of<br>a second audio stream that reduces CPU overhead in<br>use cases where two time slots are being used<br>simultaneously. |  |  |  |

|------------------------------------------------|-------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97 Interface                    | Connectivity<br>Peripherals   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| TEMPMON                                        | Temperature Monitor                       | System Control<br>Peripherals | The Temperature sensor IP is used for detecting die<br>temperature. The temperature read out does not reflect<br>case or ambient temperature. It reflects the temperature<br>in proximity of the sensor location on the die.<br>Temperature distribution may not be uniformly<br>distributed, therefore the read out value may not be the<br>reflection of the temperature value of the entire die.                                                                                                                                                                                                                                                                       |  |  |  |

| TZASC                                          | Trust-Zone Address<br>Space Controller    | Security                      | The TZASC (TZC-380 by ARM) provides security<br>address region control functions required for intended<br>application. It is used on the path to the DRAM<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                            | Connectivity<br>Peripherals   | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 Mbps.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                                                                              |  |  |  |

| USBOH3                                         | USB 2.0 High Speed<br>OTG and 3x HS Hosts | Connectivity<br>Peripherals   | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS<br/>USB PHY</li> <li>One high-speed Host module with integrated HS<br/>USB PHY</li> <li>Two identical high-speed Host modules connected to<br/>HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| VDOA                                           | VDOA                                      | Multimedia<br>Peripherals     | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

### 4.4 PLL's Electrical Characteristics

### 4.4.1 Audio/Video PLL's Electrical Parameters

### Table 15. Audio/Video PLL's Electrical Parameters

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 650 MHz ~1.3 GHz        |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### 4.4.2 528 MHz PLL

#### Table 16. 528 MHz PLL's Electrical Parameters

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 528 MHz PLL output      |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### 4.4.3 Ethernet PLL

### Table 17. Ethernet PLL's Electrical Parameters

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 500 MHz                 |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### 4.4.4 480 MHz PLL

### Table 18. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

| Characteristic      | Min | Тур        | Max    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------|-----|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fosc                | _   | 32.768 KHz | _      | This frequency is nominal and determined mainly by the crystal selected. 32.0 K will work as well.                                                                                                                                                                                                                                                                                                                                              |  |

| Current consumption | _   | 4 μΑ       |        | The 4 $\mu$ A is the consumption of the oscillator alone (OSC32k). Total supply consumption will depend on what the digital portion of the RTC consumes. The ring oscillator consumes 1 $\mu$ A when ring oscillator is inactive, 20 $\mu$ A when the ring oscillator is running. Another 1.5 $\mu$ A is drawn from vdd_rtc in the power_detect block. So, the total current is 6.5 $\mu$ A on vdd_rtc when the ring oscillator is not running. |  |

| Bias resistor       | _   | 14 MΩ      |        | This the integrated bias resistor that sets the amplifier into a high gain<br>state. Any leakage through the ESD network, external board leakage, o<br>even a scope probe that is significant relative to this value will debias th<br>amp. The debiasing will result in low gain, and will impact the circuit's abili<br>to start up and maintain oscillations.                                                                                |  |

|                     |     |            |        | Crystal Properties                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Cload               |     | 10 pF      | _      | Usually crystals can be purchased tuned for different Cloads. This Cload value is typically 1/2 of the capacitances realized on the PCB on either side of the quartz. A higher Cload will decrease oscillation margin, but increases current oscillating through the crystal.                                                                                                                                                                   |  |

| ESR                 | —   | 50 kΩ      | 100 kΩ | Equivalent series resistance of the crystal. Choosing a crystal with a higher value will decrease the oscillating margin.                                                                                                                                                                                                                                                                                                                       |  |

### Table 20. OSC32K Main Characteristics

### 4.6 I/O DC Parameters

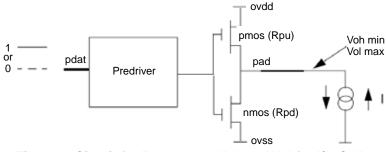

This section includes the DC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3 modes

- LVDS I/O

### NOTE

The term 'OVDD' in this section refers to the associated supply rail of an input or output.

Figure 4. Circuit for Parameters Voh and Vol for I/O Cells

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Max                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.20/3.36<br>1.96/2.07 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 | 115  |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | —   |     | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=101)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 1.70/1.79<br>1.06/1.15 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=011)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.35/2.43<br>1.74/1.77 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=010) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.13/3.29<br>2.46/2.60 | 115  |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=001)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 5.14/5.57<br>4.77/5.15 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | —   | —   | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

### 4.7.2 DDR I/O AC Parameters

Table 28 shows the AC parameters for DDR I/O operating in LPDDR2 mode. For details on supported DDR memory configurations, see Section 4.9.4, "Multi-Mode DDR Controller (MMDC).

Table 28. DDR I/O LPDDR2 Mode AC Parameters<sup>1</sup>

| Parameter                                              | Symbol   | Test Condition   | Min         | Max         | Unit |

|--------------------------------------------------------|----------|------------------|-------------|-------------|------|

| AC input logic high                                    | Vih(ac)  | —                | Vref + 0.22 | OVDD        | V    |

| AC input logic low                                     | Vil(ac)  | —                | 0           | Vref - 0.22 | V    |

| AC differential input high voltage <sup>2</sup>        | Vidh(ac) | —                | 0.44        | _           | V    |

| AC differential input low voltage                      | Vidl(ac) | —                | _           | 0.44        | V    |

| Input AC differential cross point voltage <sup>3</sup> | Vix(ac)  | Relative to Vref | -0.12       | 0.12        | V    |

| Over/undershoot peak                                   | Vpeak    | —                | —           | 0.35        | V    |

| Parameter                                                 | Symbol           | Test Condition                                                               | Min | Max | Unit    |

|-----------------------------------------------------------|------------------|------------------------------------------------------------------------------|-----|-----|---------|

| Over/undershoot area (above OVDD or below OVSS)           | Varea            | 400 MHz                                                                      | _   | 0.3 | V-ns    |

| Single output slew rate, measured between                 | tsr              | 50 $\Omega$ to Vref.<br>5 pF load.<br>Drive impedance = 40 $\Omega$<br>± 30% | 1.5 | 3.5 | V/ns    |

| Vol(ac) and Voh(ac)                                       |                  | 50 $\Omega$ to Vref.<br>5pF load.Drive<br>impedance = 60 $\Omega \pm$<br>30% | 1   | 2.5 | - 0/115 |

| Skew between pad rise/fall asymmetry + skew caused by SSN | t <sub>SKD</sub> | clk = 400 MHz                                                                | _   | 0.1 | ns      |

### Table 28. DDR I/O LPDDR2 Mode AC Parameters<sup>1</sup> (continued)

1 Note that the JEDEC LPDDR2 specification (JESD209\_2B) supersedes any specification in this document.

<sup>2</sup> Vid(ac) specifies the input differential voltage | Vtr - Vcp | required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac) - Vil(ac).

3 The typical value of Vix(ac) is expected to be about 0.5 x OVDD. and Vix(ac) is expected to track variation of OVDD. Vix(ac) indicates the voltage at which differential input signal must cross.

### Table 29 shows the AC parameters for DDR I/O operating in DDR3/DDR3L mode.

| Table 29. DDR I/O DDR3/DDR3L Mode AC Parameters <sup>1</sup>  |                  |                                |              |     |              |      |  |  |

|---------------------------------------------------------------|------------------|--------------------------------|--------------|-----|--------------|------|--|--|

| Parameter                                                     | Symbol           | Test Condition                 | Min          | Тур | Мах          | Unit |  |  |

| AC input logic high                                           | Vih(ac)          | _                              | Vref + 0.175 | —   | OVDD         | V    |  |  |

| AC input logic low                                            | Vil(ac)          | —                              | 0            |     | Vref - 0.175 | V    |  |  |

| AC differential input voltage <sup>2</sup>                    | Vid(ac)          | _                              | 0.35         | —   | _            | V    |  |  |

| Input AC differential cross point voltage <sup>3, 4</sup>     | Vix(ac)          | Relative to Vref               | Vref - 0.15  |     | Vref + 0.15  | V    |  |  |

| Over/undershoot peak                                          | Vpeak            | —                              | _            |     | 0.4          | V    |  |  |

| Over/undershoot area (above OVDD or below OVSS)               | Varea            | 400 MHz                        |              | _   | 0.5          | V-ns |  |  |

| Single output slew rate, measured between Vol(ac) and Voh(ac) | tsr              | Driver impedance = 34 $\Omega$ | 2.5          |     | 5            | V/ns |  |  |

| Skew between pad rise/fall asymmetry + skew caused by SSN     | t <sub>SKD</sub> | clk = 400 MHz                  | _            | —   | 0.1          | ns   |  |  |

1 Note that the JEDEC JESD79\_3C specification supersedes any specification in this document.

<sup>2</sup> Vid(ac) specifies the input differential voltage | Vtr-Vcp | required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac) - Vil(ac).

3 The typical value of Vix(ac) is expected to be about 0.5 x OVDD. and Vix(ac) is expected to track variation of OVDD. Vix(ac) indicates the voltage at which differential input signal must cross.

4 Extended range for Vix is only allowed for the clock and when the single-ended clock input signals CK and CK# are: • monotonic with a single-ended swing VSEL/VSEH of at least VDD/2  $\pm$ 250 mV, and

• the differential slew rate of CK - CK# is larger than 3 V/ns

Table 32 shows the GPIO output buffer impedance (OVDD 3.3 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               |        | 010                  | 75        |      |

|               |        | 011                  | 50        |      |

| Output Driver | Rdrv   | 100                  | 37        | Ω    |

| Impedance     |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

Table 32. GPIO Output Buffer Average Impedance (OVDD 3.3 V)

### 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 33 shows DDR I/O output buffer impedance of i.MX 6Solo/6DualLite processors.

|                            |        |                                               | Тур                                        |                                            |      |

|----------------------------|--------|-----------------------------------------------|--------------------------------------------|--------------------------------------------|------|

| Parameter                  | Symbol | Test Conditions DSE<br>(Drive Strength)       | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11    | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10  | Unit |

| Output Driver<br>Impedance | Rdrv   | 000<br>001<br>010<br>011<br>100<br>101<br>110 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40 | Ω    |

|                            |        | 111                                           | 34                                         | 40<br>34                                   |      |

Table 33. DDR I/O Output Buffer Impedance

### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

2. Calibration is done against 240  $\Omega$  external reference resistor.

3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

### 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, *"Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits"* for details.

### 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Solo/6DualLite processor.

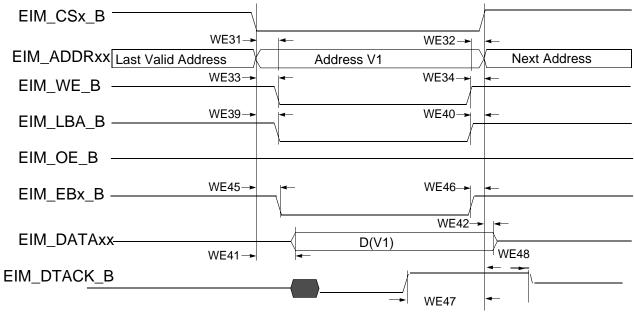

Figure 22. DTACK Mode Write Access (DAP=0)

| Table 38. EIM Asynchronous T | <b>Fiming Parameters</b> | Table Relative Chip to Select |

|------------------------------|--------------------------|-------------------------------|

|                              |                          |                               |

| Ref No. | Parameter                                              | Determination by<br>Synchronous measured<br>parameters <sup>1</sup>               | Min                             | Мах                                       | Unit |

|---------|--------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------|-------------------------------------------|------|

| WE31    | EIM_CSx_B valid to<br>Address Valid                    | WE4 - WE6 - CSA <sup>2</sup>                                                      | _                               | 3 - CSA                                   | ns   |

| WE32    | Address Invalid to<br>EIM_CSx_B invalid                | WE7 - WE5 - CSN <sup>3</sup>                                                      | _                               | 3 - CSN                                   | ns   |

|         | EIM_CSx_B valid to<br>Address Invalid                  | t <sup>4</sup> + WE4 - WE7 + (ADVN <sup>5</sup> +<br>ADVA <sup>6</sup> + 1 - CSA) | -3 + (ADVN +<br>ADVA + 1 - CSA) | _                                         | ns   |

| WE33    | EIM_CSx_B Valid to<br>EIM_WE_B Valid                   | WE8 - WE6 + (WEA - WCSA)                                                          | _                               | 3 + (WEA - WCSA)                          | ns   |

| WE34    | EIM_WE_B Invalid to<br>EIM_CSx_B Invalid               | WE7 - WE9 + (WEN - WCSN)                                                          | _                               | 3 - (WEN_WCSN)                            | ns   |

| WE35    | EIM_CSx_B Valid to<br>EIM_OE_B Valid                   | WE10 - WE6 + (OEA - RCSA)                                                         | _                               | 3 + (OEA - RCSA)                          | ns   |

|         | EIM_CSx_B Valid to<br>EIM_OE_B Valid                   | WE10 - WE6 + (OEA + RADVN<br>+ RADVA + ADH + 1 - RCSA)                            | · ·                             | 3 + (OEA +<br>RADVN+RADVA+ADH<br>+1-RCSA) | ns   |

| WE36    | EIM_OE_B Invalid to<br>EIM_CSx_B Invalid               | WE7 - WE11 + (OEN - RCSN)                                                         | _                               | 3 - (OEN - RCSN)                          | ns   |

| WE37    | EIM_CSx_B Valid to<br>EIM_EBx_B Valid<br>(Read access) | WE12 - WE6 + (RBEA - RCSA)                                                        | —                               | 3 + (RBEA - RCSA)                         | ns   |

| ID   | Parameter                | Symbol           | Tim<br>T = GPMI C                          | 0                                                 | Unit |

|------|--------------------------|------------------|--------------------------------------------|---------------------------------------------------|------|

|      |                          |                  | Min                                        | Мах                                               |      |

| NF1  | NAND_CLE setup time      | tCLS             | (AS + DS) × T - 0.12 [see <sup>2,3</sup> ] |                                                   | ns   |

| NF2  | NAND_CLE hold time       | tCLH             | DH × T - 0.                                | .72 [see <sup>2</sup> ]                           | ns   |

| NF3  | NAND_CE0_B setup time    | tCS              | (AS + DS + 1)                              | )×T [see <sup>3,2</sup> ]                         | ns   |

| NF4  | NAND_CE0_B hold time     | tCH              | (DH+1) × T                                 | - 1 [see <sup>2</sup> ]                           | ns   |

| NF5  | NAND_WE_B pulse width    | tWP              | $DS \times T$ [see <sup>2</sup> ]          |                                                   | ns   |

| NF6  | NAND_ALE setup time      | tALS             | (AS + DS) × T - 0.49 [see <sup>3,2</sup> ] |                                                   | ns   |

| NF7  | NAND_ALE hold time       | tALH             | (DH × T - 0.42 [see <sup>2</sup> ]         |                                                   | ns   |

| NF8  | Data setup time          | tDS              | DS × T - 0.26 [see <sup>2</sup> ]          |                                                   | ns   |

| NF9  | Data hold time           | tDH              | DH × T - 1.                                | .37 [see <sup>2</sup> ]                           | ns   |

| NF10 | Write cycle time         | tWC              | (DS + DH)                                  | × T [see <sup>2</sup> ]                           | ns   |

| NF11 | NAND_WE_B hold time      | tWH              | DH×T                                       | [see <sup>2</sup> ]                               | ns   |

| NF12 | Ready to NAND_RE_B low   | tRR <sup>4</sup> | (AS + 2) × T [see <sup>3,2</sup> ]         | —                                                 | ns   |

| NF13 | NAND_RE_B pulse width    | tRP              | DS × T [see <sup>2</sup> ]                 |                                                   | ns   |

| NF14 | READ cycle time          | tRC              | $(DS + DH) \times T [see 2]$               |                                                   | ns   |

| NF15 | NAND_RE_B high hold time | tREH             | DH × T [see <sup>2</sup> ]                 |                                                   | ns   |

| NF16 | Data setup on read       | tDSR             | —                                          | (DS $\times$ T -0.67)/18.38 [see <sup>5,6</sup> ] | ns   |

| NF17 | Data hold on read        | tDHR             | 0.82/11.83 [see <sup>5,6</sup> ]           | —                                                 | ns   |

### Table 41. Asynchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> GPMI's Async Mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = GPMI clock period -0.075ns (half of maximum p-p jitter).

<sup>4</sup> NF12 is guaranteed by the design.

<sup>5</sup> Non-EDO mode.

<sup>6</sup> EDO mode, GPMI clock ≈ 100 MHz (AS=DS=DH=1, GPMI\_CTL1 [RDN\_DELAY] = 8, GPMI\_CTL1 [HALF\_PERIOD] = 0).

In EDO mode (Figure 26), NF16/NF17 are different from the definition in non-EDO mode (Figure 25). They are called tREA/tRHOH (RE# access time/RE# HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample NAND\_DATAxx at rising edge of delayed NAND\_RE\_B provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). The typical value of this control register is 0x8 at 50 MT/s EDO mode. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

### 4.11.5 Ethernet Controller (ENET) AC Electrical Specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

### 4.11.5.1 ENET MII Mode Timing

This subsection describes MII receive, transmit, asynchronous inputs, and serial management signal timings.

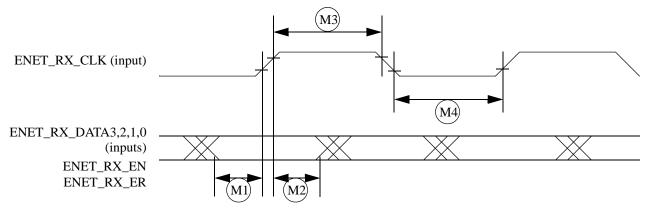

# 4.11.5.1.1 MII Receive Signal Timing (ENET\_RX\_DATA3,2,1,0, ENET\_RX\_EN, ENET\_RX\_ER, and ENET\_RX\_CLK)

The receiver functions correctly up to an ENET\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_RX\_CLK frequency.

Figure 41 shows MII receive signal timings. Table 50 describes the timing parameters (M1–M4) shown in the figure.

Figure 41. MII Receive Signal Timing Diagram

| Table 50. | MII | Receive | Signal | Timing |

|-----------|-----|---------|--------|--------|

|-----------|-----|---------|--------|--------|

| ID | Characteristic <sup>1</sup>                                         | Min | Max | Unit               |

|----|---------------------------------------------------------------------|-----|-----|--------------------|

| M1 | ENET_RX_DATA3,2,1,0, ENET_RX_EN, ENET_RX_ER to<br>ENET_RX_CLK setup | 5   | _   | ns                 |

| M2 | ENET_RX_CLK to ENET_RX_DATA3,2,1,0, ENET_RX_EN,<br>ENET_RX_ER hold  | 5   | _   | ns                 |

| M3 | ENET_RX_CLK pulse width high                                        | 35% | 65% | ENET_RX_CLK period |

| M4 | ENET_RX_CLK pulse width low                                         | 35% | 65% | ENET_RX_CLK period |

<sup>1</sup> ENET\_RX\_EN, ENET\_RX\_CLK, and ENET0\_RXD0 have the same timing in 10 Mbps 7-wire interface mode.

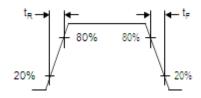

### Figure 56. TMDS Output Signals Rise and Fall Time Definition

| Symbol                      | Parameter                               | Conditions                                                              | Min  | Тур | Max    | Unit            |

|-----------------------------|-----------------------------------------|-------------------------------------------------------------------------|------|-----|--------|-----------------|

| TMDS Drivers Specifications |                                         |                                                                         |      |     |        |                 |

| _                           | Maximum serial data rate                | _                                                                       | _    | —   | 3.4    | Gbps            |

| F<br>TMDSCLK                | TMDSCLK frequency                       | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz             |

| PTMDSCLK                    | TMDSCLK period                          | $RL = 50 \Omega$<br>See Figure 52.                                      | 2.94 | _   | 40     | ns              |

| t<br>CDC                    | TMDSCLK duty cycle                      | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 52. | 40   | 50  | 60     | %               |

| t<br>CPH                    | TMDSCLK high time                       | RL = 50 $\Omega$<br>See Figure 52.                                      | 4    | 5   | 6      | UI <sup>1</sup> |

| t<br>CPL                    | TMDSCLK low time                        | RL = 50 $\Omega$<br>See Figure 52.                                      | 4    | 5   | 6      | UI <sup>1</sup> |

| _                           | TMDSCLK jitter <sup>2</sup>             | RL = 50 Ω                                                               | —    | —   | 0.25   | UI <sup>1</sup> |

| <sup>t</sup> SK(p)          | Intra-pair (pulse) skew                 | $RL = 50 \Omega$<br>See Figure 54.                                      | _    | _   | 0.15   | UI <sup>1</sup> |

| t<br>SK(pp)                 | Inter-pair skew                         | $RL = 50 \Omega$<br>See Figure 55.                                      | _    | _   | 1      | UI <sup>1</sup> |

| t <sub>R</sub>              | Differential output signal rise<br>time | 20–80%<br>RL = 50 Ω<br>See Figure 56.                                   | 75   | _   | 0.4 UI | ps              |

| t <sub>F</sub>              | Differential output signal fall time    | 20–80%<br>RL = 50 Ω<br>See Figure 56.                                   | 75   | —   | 0.4 UI | ps              |

| —                           | Differential signal overshoot           | Referred to $2x V_{SWING}$                                              |      | —   | 15     | %               |

| _                           | Differential signal undershoot          | Referred to 2x V <sub>SWING</sub>                                       | _    | —   | 25     | %               |

#### Table 57. Switching Characteristics

<sup>1</sup> UI means TMDS clock unit.

$^{2}$  Relative to ideal recovery clock, as specified in the HDMI specification, version 1.4a, section 4.2.3.

### 4.11.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent wave form.

There are special physical outputs to provide synchronous controls:

- The IPP\_DISP\_CLK is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

- The IPUx\_DIx\_PIN01—IPUx\_DIx\_PIN07 are general purpose synchronous pins, that can be used to provide HSYNC, VSYNC, DRDY or any other independent signal to a display.

The IPU has a system of internal binding counters for internal events (such as, HSYNC/VSYNC) calculation. The internal event (local start point) is synchronized with internal DI\_CLK. A suitable control starts from the local start point with predefined UP and DOWN values to calculate control's changing points with half DI\_CLK resolution. A full description of the counters system can be found in the IPU chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM).

### 4.11.10.5.2 Asynchronous Controls

The asynchronous control is a data-oriented signal that changes its value with an output data according to additional internal flags coming with the data.

There are special physical outputs to provide asynchronous controls, as follows:

- The IPUx\_DIx\_D0\_CS and IPUx\_DIx\_D1\_CS pins are dedicated to provide chip select signals to two displays.

- The IPUx\_DIx\_PIN11—IPUx\_DIx\_PIN17 are general purpose asynchronous pins, that can be used to provide WR. RD, RS or any other data oriented signal to display.

### NOTE

The IPU has independent signal generators for asynchronous signals toggling. When a DI decides to put a new asynchronous data in the bus, a new internal start (local start point) is generated. The signals generators calculate predefined UP and DOWN values to change pins states with half DI\_CLK resolution.

### 4.11.10.6 Synchronous Interfaces to Standard Active Matrix TFT LCD Panels

### 4.11.10.6.1 IPU Display Operating Signals

The IPU uses four control signals and data to operate a standard synchronous interface:

- IPP\_DISP\_CLK—Clock to display

- HSYNC—Horizontal synchronization

- VSYNC—Vertical synchronization

- DRDY—Active data

All synchronous display controls are generated on the base of an internally generated "local start point". The synchronous display controls can be placed on time axis with DI's offset, up and down parameters.

| Parameter                   | Description                                                                                                                                                       | 1 Mbit/s | 100 Mbit/s | 200 Mbit/s |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|------------|

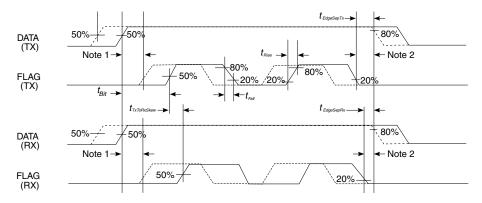

| t <sub>EageSepTx,</sub> min | Minimum allowed separation of signal transitions at transmitter package pins, including all timing defects, for example, jitter and skew, inside the transmitter. | 400 ns   | 4.00 ns    | 2.00 ns    |

| t <sub>EageSepRx,</sub> min | Minimum separation of signal transitions, measured at the receiver package pins, including all timing defects, for example, jitter and skew, inside the receiver. | 350 ns   | 3.5 ns     | 1.75 ns    |

Table 67. DATA and FLAG Timing (continued)

<sup>1</sup> This case shows that the DATA signal has slowed down more compared to the FLAG signal

$^2\,$  This case shows that the FLAG signal has slowed down more compared to the DATA signal.

Figure 79. DATA and FLAG Signal Timing

### 4.11.14 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

### 4.11.14.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

### 4.11.15 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 80 depicts the timing of the PWM, and Table 68 lists the PWM timing parameters.

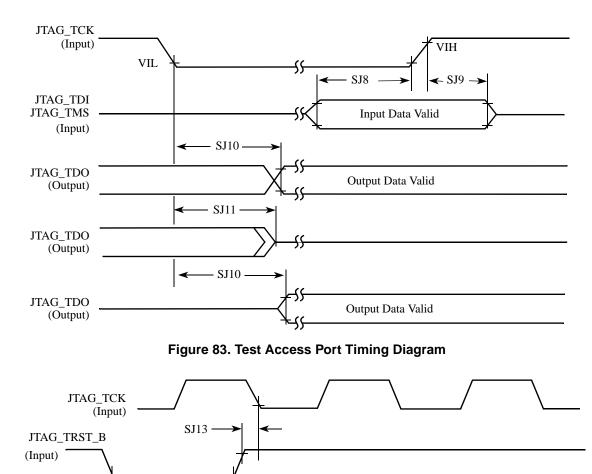

Figure 84. JTAG\_TRST\_B Timing Diagram

SJ12

| Table 69. JTA | G Timing |

|---------------|----------|

|---------------|----------|

| ID  | Parameter <sup>1,2</sup>                                            | All Freq | Unit |     |

|-----|---------------------------------------------------------------------|----------|------|-----|

|     | Falameter                                                           | Min      | Мах  |     |

| SJ0 | JTAG_TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22   | MHz |

| SJ1 | JTAG_TCK cycle time in crystal mode                                 | 45       | _    | ns  |

| SJ2 | JTAG_TCK clock pulse width measured at V <sub>M</sub> <sup>2</sup>  | 22.5     | _    | ns  |

| SJ3 | JTAG_TCK rise and fall times                                        | —        | 3    | ns  |

| SJ4 | Boundary scan input data set-up time                                | 5        | _    | ns  |

| SJ5 | Boundary scan input data hold time                                  | 24       | _    | ns  |

| SJ6 | JTAG_TCK low to output data valid                                   | —        | 40   | ns  |

| SJ7 | JTAG_TCK low to output high impedance                               | —        | 40   | ns  |

| SJ8 | JTAG_TMS, JTAG_TDI data set-up time                                 | 5        | —    | ns  |

| SJ9 | JTAG_TMS, JTAG_TDI data hold time                                   | 25       | _    | ns  |

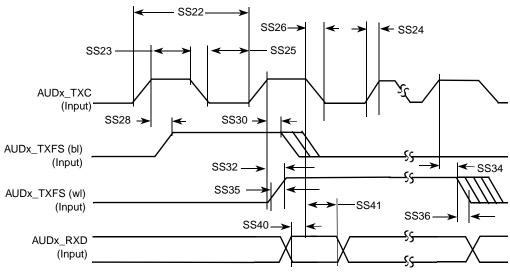

| ID                                  | Parameter                              | Min  | Мах | Unit |

|-------------------------------------|----------------------------------------|------|-----|------|

| Synchronous External Clock Operatio |                                        | tion |     |      |

| SS44                                | AUDx_RXD setup before AUDx_TXC falling | 10.0 | —   | ns   |

| SS45                                | AUDx_RXD hold after AUDx_TXC falling   | 2.0  | _   | ns   |

| SS46                                | AUDx_RXD rise/fall time                | —    | 6.0 | ns   |

### Table 74. SSI Transmitter Timing with External Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

### 4.11.18.4 SSI Receiver Timing with External Clock

Figure 90 depicts the SSI receiver external clock timing and Table 75 lists the timing parameters for the receiver timing with the external clock.

Figure 90. SSI Receiver External Clock Timing Diagram

**Package Information and Contact Assignments**

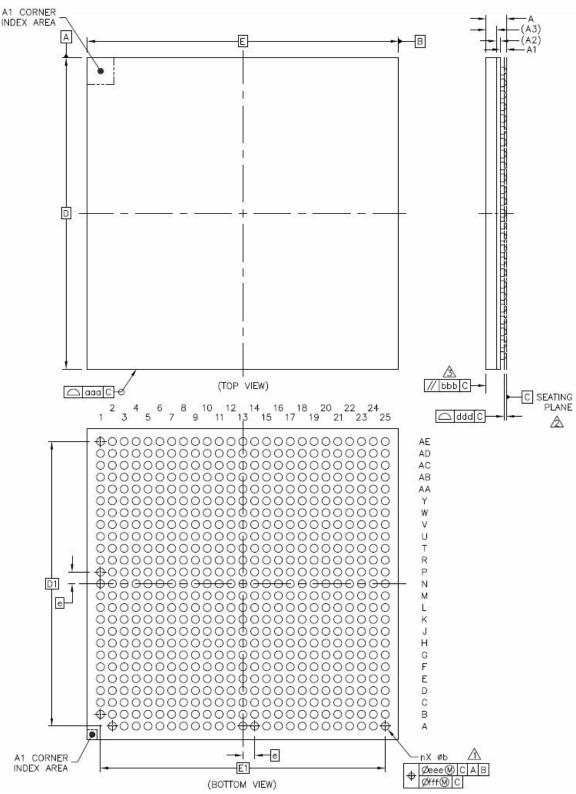

Figure 97. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views

### Package Information and Contact Assignments

| AD                          |              |    | AC          | AB           | AA           |    |

|-----------------------------|--------------|----|-------------|--------------|--------------|----|

| GND DRAM_D5                 | DRAM_D5      |    | DRAM_D4     | LVDS1_TX2_N  | LVDS1_TX1_P  | -  |

| DRAM_D1 DRAM_D0             | DRAM_D0      |    | DRAM_VREF   | LVDS1_TX2_P  | LVDS1_TX1_N  | 7  |

| DRAM_SDQS0 DRAM_SDQS0_B     | DRAM_SDQS0_  | œ. | DRAM_DQM0   | GND          | LVDS1_TX3_N  | S  |

| DRAM_D7 GND                 | GND          |    | DRAM_D2     | DRAM_D6      | LVDS1_TX3_P  | 4  |

| DRAM_D9 DRAM_D8             | DRAM_D8      |    | DRAM_D13    | DRAM_D12     | DRAM_D3      | 5  |

| DRAM_SDQS1_B DRAM_SDQS1     | DRAM_SDQS1   |    | DRAM_DQM1   | DRAM_D14     | DRAM_D10     | 9  |

| DRAM_D11 GND                | GND          |    | DRAM_D15    | DRAM_D16     | GND          | 7  |

| DRAM_SDQS2_B DRAM_SDQS2     | DRAM_SDQS2   |    | DRAM_D22    | DRAM_DQM2    | DRAM_D17     | 8  |

| DRAM_D24 DRAM_D29           | DRAM_D29     |    | DRAM_D28    | DRAM_D18     | DRAM_D23     | 6  |

| DRAM_DQM3 GND               | GND          |    | DRAM_SDQS3  | DRAM_SDQS3_B | GND          | 10 |

| DRAM_D26 DRAM_D30           | DRAM_D30     |    | DRAM_D31    | DRAM_D27     | DRAM_SDCKE1  | 1  |

| DRAM_A9 DRAM_A12            | DRAM_A12     |    | DRAM_A11    | DRAM_SDBA2   | DRAM_A14     | 12 |

| DRAM_A5 GND                 | GND          |    | DRAM_A6     | DRAM_A8      | GND          | 13 |

| DRAM_SDCLK_1_B DRAM_SDCLK_1 | DRAM_SDCLK_1 |    | DRAM_A0     | DRAM_A1      | DRAM_A2      | 14 |

| DRAM_SDCLK_0_B DRAM_SDCLK_0 | DRAM_SDCLK_0 |    | DRAM_SDBA0  | DRAM_RAS     | DRAM_A10     | 15 |

| DRAM_CAS GND                | GNÐ          |    | DRAM_SDODT0 | DRAM_SDWE    | GND          | 16 |

| ZQPAD DRAM_CS1              | DRAM_CS1     |    | DRAM_A13    | DRAM_SDODT1  | DRAM_D32     | 17 |

| DRAM_SDQS4_B DRAM_SDQS4     | DRAM_SDQS4   |    | DRAM_D34    | DRAM_DQM4    | DRAM_D33     | 18 |

| DRAM_D35 GND                | GND          |    | DRAM_D39    | DRAM_D38     | GND          | 19 |

| DRAM_SDQS5_B DRAM_SDQS5     | DRAM_SDQS5   |    | DRAM_DQM5   | DRAM_D41     | DRAM_D45     | 20 |

| DRAM_D46 DRAM_D43           | DRAM_D43     |    | DRAM_D47    | DRAM_D42     | DRAM_D57     | 21 |

| DRAM_D49 GND                | GND          |    | DRAM_D48    | DRAM_D52     | GND          | 22 |

| DRAM_SDQS6_B DRAM_SDQS6     | DRAM_SDQS6   |    | DRAM_D53    | DRAM_D60     | DRAM_D61     | 23 |

| DRAM_D50 DRAM_DQM6          | DRAM_DQM6    |    | DRAM_D51    | GND          | DRAM_SDQS7_B | 24 |

| GND DRAM_D54                | DRAM_D54     | _  | DRAM_D55    | DRAM_D56     | DRAM_SDQS7   | 25 |

| AE AD                       | AD           |    | AC          | AB           | AA           |    |

Table 90. 21 x 21 mm, 0.8 mm Pitch Ball Map i.MX 6DualLite (continued)

#### **Revision History**

| Devi           |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|