Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | e200z0h                                                    |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 64MHz                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART     |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                    |

| Number of I/O              | 105                                                        |

| Program Memory Size        | 512KB (512K x 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 48K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 16x10b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 144-LQFP                                                   |

| Supplier Device Package    | 144-LQFP (20x20)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpxd1005vlq64 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Overview

- As many as 38 frontplane drivers and six backplane drivers

- Stepper Motor Controller (SMC) module with high-current drivers for as many as six stepper motors driven in full dual H-Bridge configuration including full diagnostics for short circuit detection

- Stepper motor return-to-zero and stall detection module

- Sound generation and playback utilizing PWM channels and eDMA; supports monotonic and polyphonic sound

- 24 eMIOS channels providing as many as 16 PWM and 24 input capture / output compare channels

- 10-bit Analog-to-Digital Converter (ADC)

- Maximum conversion time of 1  $\mu$ s

- As many as 16 internal channels, expandable to 23 via external multiplexing

- As many as two Serial Peripheral Interface (DSPI) modules for full-duplex, synchronous, communications with external devices (extendable to include up to 8 multiplexed external channels)

- QuadSPI serial flash memory controller supporting single, dual and quad modes of operation to interface to external serial flash memory. QuadSPI can be configured to function as another DSPI module.

- Two Local Interconnect Network Flexible (LINFlex) controller modules capable of autonomous message handling (master), autonomous header handling (slave mode), and UART support. Compliant with LIN protocol rev 2.1

- Two full CAN 2.0B controllers with 64 configurable buffers each; bit rate programmable as fast as 1 Mbit/s

- As many as four inter-integrated circuit (I<sup>2</sup>C) internal bus controllers with master/slave bus interface

- As many as 133 configurable general purpose pins supporting input and output operations

- Real Time Counter (RTC) with multiple clock sources:

- 128 kHz slow internal RC oscillator or 16 MHz fast internal RC oscillator supporting autonomous wakeup with 1 ms resolution with maximum timeout of 2 seconds

- 32 KHz slow external crystal oscillator, supporting wakeup with 1 s resolution and maximum timeout of one hour

- 4–16 MHz fast external crystal oscillator

- System timers:

- Four-channel 32-bit System Timer Module (STM)—included in processor platform

- Four-channel 32-bit Periodic Interrupt Timer (PIT) module

- Software Watchdog Timer (SWT)

- System Integration Unit (SIU) module to manage resets, external interrupts, GPIO and pad control

- System Status and Configuration Module (SSCM) to provide information for identification of the device, last boot mode, or debug status and provides an entry point for the censorship password mechanism

### **1.6.4** Parallel Data Interface (PDI)

The PDI is a digital interface used to receive external digital video or graphic content into the DCU.

The PDI input is directly injected into the DCU background plane FIFO. When the PDI is activated, all the DCU synchronization is extracted from the external video stream to guarantee the synchronization of the two video sources.

The PDI can be used to:

- Connect a video camera output directly to the PDI

- Connect a secondary display driver as slave with a minimum of extra cost

- Connect a device gathering various Video sources

- Provide flexibility to allow the DCU to be used in slave mode (external synchronization)

The PDI features the following:

- Supported color modes:

- 8-bit mono

- 8-bit color multiplexed

- RGB565

- 16-bit/18-bit RAW color

- Supported synchronization modes:

- Embedded ITU-R BT.656-4 (RGB565 mode 2)

- HSYNC, VSYNC

- Data Enable

- Direct interface with DCU background plane FIFO

- Synchronization generation for the DCU

### 1.6.5 Liquid Crystal Display (LCD) driver

The LCD driver module has two configurations allowing a maximum of 160 or 228 LCD segments:

- As many as 40 frontplane drivers and four backplane drivers

- As many as 38 frontplane drivers and six backplane drivers

Each segment is controlled and can be masked by a corresponding bit in the LCD RAM.

Four to six multiplex modes (1/1, 1/2, 1/3, 1/4, 1/5, 1/6 duty), and three bias (1/1, 1/2, 1/3) methods are available. All frontplane and backplane pins can be multiplexed with other port functions.

The LCD driver module features the following:

- Programmable frame clock generator from different clock sources:

- System clock

- Internal RC oscillator

- Programmable bias voltage level selector

- On-chip generation of all output voltage levels

### 1.6.11 QuadSPI serial flash controller

The QuadSPI module enables use of external serial flash memories supporting single, dual and quad modes of operation. It features the following:

- Memory mapping of external serial flash

- Automatic serial flash read command generation by CPU, DMA or DCU read access on AHB bus

- Supports single, dual and quad serial flash read commands

- Flexible buffering scheme to maximize read bandwidth of serial flash

- 'Legacy' mode allowing QuadSPI to be used as a standard SPI (no DSI or CSI mode)

### 1.6.12 Analog-to-digital converter (ADC)

The ADC features the following:

- 10-bit A/D resolution

- 0 to 5 V common mode conversion range

- Supports conversions speeds of as fast as 1 µs

- 16 internal and 8 external channels support

- As many as 16 single-ended inputs channels

- All channels configured to have alternate function as general purpose input/output pins

- 10-bit ±3 counts accuracy (TUE)

- External multiplexer support to increase as many as 23 channels

- Automatic  $1 \times 8$  multiplexer control

- External multiplexer connected to a dedicated input channel

- Shared register between the 8 external channels

- Result register available for every non-multiplexed channel

- Configurable left- or right-aligned result format

- Supports for one-shot, scan and injection conversion modes

- Injection mode status bit implemented on adjacent 16-bit register for each result

- Supports access to result and injection status with single 32-bit read

- Independently enabling of function for channels:

- Pre-sampling

- Offset error cancellation

- Offset refresh

- Conversion Triggering support

- Internal conversion triggering from periodic interrupt timer (PIT)

- Four configurable analog comparator channels offering range comparison with triggered alarm

- Greater than

- Less than

- Out of range

### 1.6.16 Controller Area Network (CAN) module

The PXD10 contains two CAN modules that offer the following features:

- Compliant with CAN protocol specification, Version 2.0B active

- 64 mailboxes, each configurable as transmit or receive

- Mailboxes configurable while module remains synchronized to CAN bus

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

- Listen only mode capabilities

- CAN Sampler

- Can catch the first message sent on the CAN network while the PXD10 is stopped. This guarantees a clean startup of the system without missing messages on the CAN network.

- The CAN sampler is connected to one of the CAN RX pins.

# 1.6.17 Inter-IC Communications (I<sup>2</sup>C) module

The I<sup>2</sup>C module features the following:

- As many as four I<sup>2</sup>C modules supported

- Two-wire bi-directional serial bus for on-board communications

- Compatibility with I<sup>2</sup>C bus standard

- Multimaster operation

- Software-programmable for one of 256 different serial clock frequencies

- Software-selectable acknowledge bit

- Interrupt-driven, byte-by-byte data transfer

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus-busy detection

| Channel number   |                                 |                                    |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------|---------------------------------|------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8                | 9–15                            | 16                                 | 17–22                                                                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| IC/OC<br>Counter | IC/OC                           | PWM<br>Counter                     | PWM                                                                              | PWM<br>Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Х                | Х                               | Х                                  | Х                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Х                | Х                               | Х                                  | Х                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Х                | Х                               | Х                                  | Х                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Х                |                                 | Х                                  |                                                                                  | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                  |                                 | Х                                  | Х                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                  |                                 | Х                                  | Х                                                                                | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                  | IC/OC<br>Counter<br>X<br>X<br>X | 89–15IC/OC<br>CounterIC/OCXXXXXXXX | 89–1516IC/OC<br>CounterIC/OC<br>CounterPWM<br>CounterXXXXXXXXXXXXXXXXXXXXXXXXXXX | 8         9–15         16         17–22           IC/OC<br>Counter         IC/OC         PWM<br>Counter         PWM           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X           X         X         X         X |  |  |

### Table 2. 16-channel eMIOS module channel configuration

NOTES:

Modulus up and down counters to support driving local and global counter busses

The channel configuration options for the 8-channel eMIOS module are summarized in Table 3.

|                                                      | Channel number    |              |                   |  |  |  |

|------------------------------------------------------|-------------------|--------------|-------------------|--|--|--|

| Channel mode                                         | 16<br>PWM Counter | 17–22<br>PWM | 23<br>PWM Counter |  |  |  |

| General Purpose Input/Output                         | X                 | Х            | Х                 |  |  |  |

| Single Action Input Capture                          | Х                 | Х            | Х                 |  |  |  |

| Single Action Output Compare                         | X                 | Х            | Х                 |  |  |  |

| Modulus Counter Buffered <sup>1</sup>                | X                 |              | Х                 |  |  |  |

| Output Pulse Width and Frequency Modulation Buffered | X                 | Х            | Х                 |  |  |  |

| Output Pulse Width Modulation Buffered               | Х                 | Х            | Х                 |  |  |  |

NOTES:

<sup>1</sup> Modulus up and down counters to support driving local and global counter busses

### 1.6.20 Periodic interrupt timer (PIT) module

The PIT features the following:

- Four general purpose interrupt timers

- As many as two dedicated interrupt timers for triggering ADC conversions

- 32-bit counter resolution

- Clocked by system clock frequency

- 32-bit counter for Real Time Interrupt, clocked from main external oscillator

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority.

- Modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- External non-maskable interrupt directly accessing the main core critical interrupt mechanism

- 32 external interrupts

### 1.6.24 System Integration Unit (SIU)

The SIU controls MCU reset configuration, pad configuration, external interrupt, general purpose I/O (GPIO), internal peripheral multiplexing, and the system reset operation.

The GPIO features the following:

- As many as four levels of internal pin multiplexing, allowing exceptional flexibility in the allocation of device functions for each package

- Centralized general purpose input output (GPIO) control of as many as 132 input/output pins (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins can be alternatively configured as both general purpose input or output pins except ADC channels which support alternative configuration as general purpose inputs

- Direct readback of the pin value supported on all digital output pins through the SIU

- Configurable digital input filter that can be applied to as many as 14 general purpose input pins for noise elimination on external interrupts

- Register configuration protected against change with soft lock for temporary guard or hard lock to prevent modification until next reset.

### 1.6.25 System Clocks and Clock Generation Modules

The system clock on the PXD10 can be derived from an external oscillator, an on-chip FMPLL, or the internal 16 MHz oscillator.

- The source system clock frequency can be changed via an on-chip programmable clock divider (÷1 to ÷32).

- Additional programmable peripheral bus clock divider ratio (÷1 to ÷16)

- The PXD10 has two on-chip FMPLLs—the primary module and an auxiliary module.

- Each features the following:

- Input clock frequency from 4 MHz to 16 MHz

- Lock detect circuitry continuously monitors lock status

- Loss Of Clock (LOC) detection for reference and feedback clocks

- On-chip loop filter (for improved electromagnetic interference performance and reduction of number of external components required)

| c | S |

|---|---|

| č | ö |

| Port  | PCR      | Alternate                                    | Function                | Special               | Peripheral <sup>3</sup> | I/O       | Pad               | RESET                | Pin number |          |

|-------|----------|----------------------------------------------|-------------------------|-----------------------|-------------------------|-----------|-------------------|----------------------|------------|----------|

| pin   | register | function <sup>1</sup>                        | Tunction                | function <sup>2</sup> | renpheral               | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP   | 176 LQFP |

| PC[2] | PCR[32]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[32]<br>—<br>—<br>— | ANS[2]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 70         | 86       |

| PC[3] | PCR[33]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[33]<br>—<br>—<br>— | ANS[3]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 69         | 85       |

| PC[4] | PCR[34]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[34]<br>—<br>—<br>— | ANS[4]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 68         | 84       |

| PC[5] | PCR[35]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[35]<br>—<br>—<br>— | ANS[5]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 67         | 83       |

| PC[6] | PCR[36]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[36]<br>—<br>—<br>— | ANS[6]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 66         | 82       |

| PC[7] | PCR[37]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[37]<br>—<br>—<br>— | ANS[7]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 65         | 81       |

| PC[8] | PCR[38]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[38]<br>—<br>—<br>— | ANS[8]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 62         | 78       |

| PC[9] | PCR[39]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[39]<br>—<br>—<br>— | ANS[9]                | SIUL<br>—<br>—<br>—     | I/O       | J                 | None,<br>None        | 61         | 77       |

| Port             | PCR     | Alternate                                    | Function                                  | Special            | Peripheral <sup>3</sup>         | I/O               | Pad                  | RESET         | Pin number |    |

|------------------|---------|----------------------------------------------|-------------------------------------------|--------------------|---------------------------------|-------------------|----------------------|---------------|------------|----|

| pin register fun |         | Function                                     | function <sup>2</sup>                     | Peripheral         | direction                       | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP      | 176 LQFP   |    |

| PC[10]           | PCR[40] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[40]<br>—<br>SOUND<br>—               | ANS[10]            | SIUL<br>—<br>SGL<br>—           | I/O               | J                    | None,<br>None | 60         | 76 |

| PC[11]           | PCR[41] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[41]<br>—<br>MA0<br>PCS2_1            | ANS[11]            | SIUL<br><br>ADC<br>DSPI_1       | I/O               | J                    | None,<br>None | 59         | 75 |

| PC[12]           | PCR[42] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[42]<br>—<br>MA1<br>PCS1_1            | ANS[12]            | SIUL<br>—<br>ADC<br>DSPI_1      | I/O               | J                    | None,<br>None | 58         | 74 |

| PC[13]           | PCR[43] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[43]<br>—<br>MA2<br>PCS0_1            | ANS[13]            | SIUL<br>—<br>ADC<br>DSPI_1      | I/O               | J                    | None,<br>None | 57         | 73 |

| PC[14]           | PCR[44] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[44]<br>—<br>—<br>—                   | ANS[14]<br>EXTAL32 | SIUL<br>—<br>—<br>—             | I/O               | J                    | None,<br>None | 56         | 72 |

| PC[15]           | PCR[45] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[45]<br>—<br>—<br>—                   | ANS[15]<br>XTAL32  | SIUL<br>—<br>—<br>—             | I/O               | J                    | None,<br>None | 55         | 71 |

| PD[0]            | PCR[46] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[46]<br>M0C0M<br>SSD0_0<br>eMIOSB[23] | _                  | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O               | SMD                  | None,<br>None | 73         | 89 |

| PD[1]            | PCR[47] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[47]<br>M0C0P<br>SSD0_1<br>eMIOSB[22] | _                  | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O               | SMD                  | None,<br>None | 74         | 90 |

PXD10 Microcontroller Data Sheet, Rev. 1

Pinout and signal descriptions

| Port   | PCR      | Alternate                                    | Function                                  | Special               | Peripheral <sup>3</sup>         | I/O       | Pad               | RESET                | Pin number |          |

|--------|----------|----------------------------------------------|-------------------------------------------|-----------------------|---------------------------------|-----------|-------------------|----------------------|------------|----------|

| pin    | register | function <sup>1</sup>                        | Function                                  | function <sup>2</sup> | renpilerai                      | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP   | 176 LQFP |

| PD[10] | PCR[56]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[56]<br>M2C1M<br>SSD2_2<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 85         | 101      |

| PD[11] | PCR[57]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[57]<br>M2C1P<br>SSD2_3<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 86         | 102      |

| PD[12] | PCR[58]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[58]<br>M3C0M<br>SSD3_0<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 89         | 105      |

| PD[13] | PCR[59]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[59]<br>M3C0P<br>SSD3_1<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 90         | 106      |

| PD[14] | PCR[60]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[60]<br>M3C1M<br>SSD3_2<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 91         | 107      |

| PD[15] | PCR[61]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[61]<br>M3C1P<br>SSD3_3<br>—          | _                     | SIUL<br>SMC<br>SSD<br>—         | I/O       | SMD               | None,<br>None        | 92         | 108      |

| PE[0]  | PCR[62]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[62]<br>M4C0M<br>SSD4_0<br>eMIOSA[15] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 93         | 109      |

| PE[1]  | PCR[63]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[63]<br>M4C0P<br>SSD4_1<br>eMIOSA[14] | _                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 94         | 110      |

Table 6. Port pin summary (continued)

PXD10 Microcontroller Data Sheet, Rev. 1

Pinout and signal descriptions

41

#### **Pinout and signal descriptions**

| Abbreviation <sup>1</sup> | Description                                                                                                                                                                                                                                                              |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F                         | Fast (with GPIO and digital alternate function)                                                                                                                                                                                                                          |

| J                         | Slow pads with analog muxing (built for ADC channels)                                                                                                                                                                                                                    |

| M1                        | Medium (with GPIO and digital alternate function)                                                                                                                                                                                                                        |

| M2                        | Programmable medium/slow pad (programmed via the slew rate control in the PCR):<br>Slew rate disabled: Slow driver configuration (AC/DC parameters same as for a slow pad)<br>Slew rate enabled: Medium driver configuration (AC/DC parameters same as for a medium pad) |

| S                         | Slow (with GPIO and digital alternate function)                                                                                                                                                                                                                          |

| SMD                       | Stepper motor driver (with slew rate control)                                                                                                                                                                                                                            |

| X                         | Oscillator                                                                                                                                                                                                                                                               |

### Table 7. Pad type descriptions

NOTES: <sup>1</sup> The pad descriptions refer to the different Pad Configuration Register (PCR) types. Refer to the SIUL chapter in the device reference manual for the features available for each pad type.

#### 2.8.1 Signal details

### Table 8. Signal details

| Signal                                   | Peripheral | Description                                                                                                                                                                                   |

|------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABS[0]                                   | BAM        | Alternate Boot Select. Gives an option to boot by downloading code via CAN or LIN.                                                                                                            |

| ANS[0:15]                                | ADC        | Inputs used to bring into the device sensor-based signals for A/D conversion. ANS[0:15] connect to ATD channels [32:47].                                                                      |

| MA[0:2]                                  | ADC        | These three control bits are output to enable the selection for an external Analog Mux for expansion channels. The available 8 multiplexed channels connect to ATD channels [64:71].          |

| FABM                                     |            | Force Alternate Boot mode. Forces the device to boot from the external bus (Can or LIN). If not asserted, the device boots up from the lowest flash sector containing a valid boot signature. |

| DCU_DE                                   | DCU        | Indicates that valid pixels are present.                                                                                                                                                      |

| DCU_HSYNC                                | DCU        | Horizontal sync pulse for TFT-LCD display                                                                                                                                                     |

| DCU_PCLK                                 | DCU        | Output pixel clock for TFT-LCD display                                                                                                                                                        |

| DCU_R[0:7],<br>DCU_G[0:7],<br>DCU_B[0:7] | DCU        | Red, green and blue color 8-bit Pixel values for TFT-LCD displays                                                                                                                             |

| DCU_TAG                                  | DCU        | Indicates when a tagged pixel is present in safety mode                                                                                                                                       |

| DCU_VSYNC                                | DCU        | Vertical sync pulse for TFT-LCD display                                                                                                                                                       |

| PCS[02]_0,<br>PCS[02]_1                  | DSPI       | Peripheral chip selects when device is in Master mode; not used in slave modes.                                                                                                               |

| SCK_0,<br>SCK_1                          | DSPI       | SPI clock signal—bidirectional                                                                                                                                                                |

# 3.3 NVUSRO register

Portions of the device configuration, such as high voltage supply, oscillator margin, and watchdog enable/disable after reset are controlled via bit values in the Nonvolatile User Options (NVUSRO) register. For a detailed description of the NVUSRO register, please see the chip reference manual.

### 3.3.1 NVUSRO[PAD3V5V] field description

Table 10 shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 10. PAD3V5V field description<sup>1</sup>

| Value <sup>2</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

| NOTES              | ·                            |

NOTES:

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value before Flash initialization is '1' (3.3 V)

The DC electrical characteristics are dependent on the PAD3V5V bit value.

# 3.3.2 NVUSRO[OSCILLATOR\_MARGIN] field description

Table 10 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

Table 11. OSCILLATOR\_MARGIN field description<sup>1</sup>

| Value <sup>2</sup> | Description                                 |

|--------------------|---------------------------------------------|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |

| 1                  | High margin configuration (4 MHz/16 MHz)    |

| NOTES              |                                             |

NOTES:

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value before Flash initialization is '1'

The 4–16 MHz fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value.

# 3.4 Absolute maximum ratings

| <u>Sympho</u>                                                    | .1 | 6 | Desemptor                                                                                    | Conditions           | Va                      | alue                     | 110:4 |

|------------------------------------------------------------------|----|---|----------------------------------------------------------------------------------------------|----------------------|-------------------------|--------------------------|-------|

| Symbol                                                           |    | С | Parameter                                                                                    | Conditions           | Min                     | Мах                      | Unit  |

| V <sub>DDA</sub>                                                 | SR | С | Voltage on VDDA pin (ADC reference) with respect to ground ( $V_{SSA}$ )                     | _                    | -0.3                    | 6.0                      | V     |

| V <sub>SSA</sub>                                                 | SR | С | Voltage on VSSA (ADC reference) pin with respect to $V_{\text{SS}}$                          | —                    | V <sub>SS</sub> - 0.1   | V <sub>SS</sub> + 0.1    | V     |

| V <sub>DDPLL</sub>                                               | СС | С | Voltage on VDDPLL (1.2 V PLL supply) pin with respect to ground ( $V_{SSPLL}$ )              | —                    | -0.1                    | 1.4                      | V     |

| V <sub>SSPLL</sub>                                               | SR | С | Voltage on VSSPLL pin with respect to $\mathrm{V}_{\mathrm{SS12}}$                           |                      | V <sub>SS12</sub> - 0.1 | V <sub>SS12</sub> + 0.1  | V     |

| V <sub>DDR</sub>                                                 | SR | С | Voltage on VDDR pin (regulator supply) with respect to ground (V <sub>SSR</sub> )            | _                    | -0.3                    | 6.0                      | V     |

| V <sub>SSR</sub>                                                 | SR | С | Voltage on VSSR (regulator ground) pin with respect to $V_{SS}$                              |                      | V <sub>SS</sub> - 0.1   | V <sub>SS</sub> + 0.1    | V     |

| V <sub>DD12</sub>                                                | СС | С | Voltage on VDD12 pin with respect to ground (V <sub>SS12</sub> )                             | —                    | -0.1                    | 1.4                      | V     |

| V <sub>SS12</sub>                                                | CC | С | Voltage on VSS12 pin with respect to $V_{SS}$                                                | —                    | V <sub>SS</sub> -0.1    | V <sub>SS</sub> + 0.1    | V     |

| V <sub>DDE_A</sub> 1                                             | SR | С | Voltage on VDDE_A (I/O supply) pin with respect to ground (V <sub>SSE_A</sub> )              | —                    | -0.3                    | 6.0                      | V     |

| V <sub>DDE_B</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_B (I/O supply) pin with respect to ground (V <sub>SSE_B</sub> )              | —                    | -0.3                    | 6.0                      | V     |

| V <sub>DDE_C</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_C (I/O supply) pin with respect to ground (V <sub>SSE_C</sub> )              | —                    | -0.3                    | 6.0                      | V     |

| V <sub>DDE_E</sub> <sup>1</sup>                                  | SR | С | Voltage on VDDE_E (I/O supply) pin with respect to ground (V <sub>SSE_E</sub> )              | —                    | -0.3                    | 6.0                      | V     |

| V <sub>DDMA</sub> 1                                              | SR | С | Voltage on VDDMA (stepper motor supply) pin with respect to ground (V <sub>SSMA</sub> )      | —                    | -0.3                    | 6.0                      | V     |

| V <sub>DDMB</sub> <sup>1</sup><br>V <sub>DDMC</sub> <sup>1</sup> | SR | С | Voltage on VDDMB/C (stepper motor supply)<br>pin with respect to ground (V <sub>SSMB</sub> ) | —                    | -0.3                    | 6.0                      | V     |

| V <sub>SS</sub> <sup>2</sup>                                     | SR | С | I/O supply ground                                                                            | —                    | 0                       | 0                        | V     |

| V <sub>SSOSC</sub>                                               | SR | С | Voltage on VSSOSC (oscillator ground) pin with respect to $V_{SS}$                           | —                    | V <sub>SS</sub> -0.1    | V <sub>SS</sub> + 0.1    | V     |

| V <sub>LCD</sub>                                                 | SR | С | Voltage on VLCD (LCD supply) pin with respect to $\mathrm{V}_{\mathrm{SS}}$                  | —                    | 0                       | V <sub>DDE_A</sub> + 0.3 | V     |

| V <sub>IN</sub>                                                  | SR | С | Voltage on any GPIO pin with respect to ground                                               | —                    | -0.3                    | 6.0                      | V     |

|                                                                  |    | С | (V <sub>SS</sub> )                                                                           | Relative to $V_{DD}$ | -0.3                    | $V_{DD} + 0.3^{3}$       |       |

| Symbol             |    | С | Parameter                                                          | Conditions | Va                 | lue               | Unit |

|--------------------|----|---|--------------------------------------------------------------------|------------|--------------------|-------------------|------|

| Symbo              | 21 | C | Falameter                                                          | Conditions | Min                | Max               | Unit |

| V <sub>SSOSC</sub> | SR | С | Voltage on VSSOSC (oscillator ground) pin with respect to $V_{SS}$ |            | 0                  | 0                 | V    |

| V <sub>LCD</sub>   | SR |   | Voltage on VLCD (LCD supply) pin with respect to $V_{\text{SS}}$   |            | 0                  | $V_{DDE_A} + 0.3$ | V    |

| TV <sub>DD</sub>   | SR | С | V <sub>DD</sub> slope to ensure correct power up                   | _          | 5×10 <sup>-6</sup> | 0.25              | V/µs |

| T <sub>A</sub>     | SR | С | Ambient temperature under bias                                     | _          | -40                | 105               | °C   |

| Τ <sub>J</sub>     | SR | С | Junction temperature under bias                                    |            | -40                | 150               |      |

Table 13. Recommended operating conditions (3.3 V) (continued)

NOTES: <sup>1</sup> 100 nF capacitance needs to be provided between  $V_{DDA}/V_{SSA}$  pair.

$^2~$  At least 10  $\mu F$  capacitance must be connected between V\_{DDR} and V\_{SS}. This is required because of sharp surge due to external ballast.

$^{3}$  V<sub>DD</sub> refers collectively to I/O voltage supplies, i.e., V<sub>DDE\_A</sub>, V<sub>DDE\_B</sub>, V<sub>DDE\_C</sub>, V<sub>DDE\_E</sub>, V<sub>DDMA</sub>, V<sub>DDMB</sub> and V<sub>DDMC</sub>.

<sup>4</sup> 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/O's DC electrical specification may not be guaranteed. When voltage drops below  $V_{\ensuremath{\mathsf{LVDHVL}}}$  device is reset.

<sup>6</sup> V<sub>SS</sub> refers collectively to I/O voltage supply grounds, i.e., V<sub>SSE\_A</sub>, V<sub>SSE\_B</sub>, V<sub>SSE\_C</sub>, V<sub>SSE\_E</sub>, V<sub>SSMA</sub>, V<sub>SSMB</sub> and V<sub>SSMC</sub>) unless otherwise noted.

| Symbol                         |    | с | Parameter                                                                                                                 | Conditions                        | Va                    | lue                   | Unit |

|--------------------------------|----|---|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----------------------|------|

| Symb                           |    |   | Falameter                                                                                                                 | Conditions                        | Min                   | Max                   | Unit |

| V <sub>DDA</sub> <sup>1</sup>  | SR | С | <b>o</b>                                                                                                                  |                                   | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SS</sub> )                                                                                      | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to<br>V <sub>DDE_C</sub> | V <sub>DD</sub> – 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSA</sub>               | SR | С | Voltage on VSSA (ADC reference) pin with respect $\rm V_{SS}$                                                             | —                                 | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>SSPLL</sub>             | SR | С | Voltage on VSSPLL pin with respect to $V_{SS12}$                                                                          | _                                 | 0                     | 0                     | V    |

| V <sub>DDR</sub> <sup>3</sup>  | SR | С | Voltage on VDDR pin (regulator supply) with                                                                               |                                   | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SSR</sub> )                                                                                     | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to V <sub>DD</sub>       | V <sub>DD</sub> - 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSR</sub>               | SR | С | Voltage on VSSR (regulator ground) pin with respect to $\rm V_{SS12}$                                                     |                                   | 0                     | 0                     | V    |

| V <sub>SS12</sub>              | СС | С | Voltage on VSS12 pin with respect to $V_{SS}$                                                                             |                                   | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>DD</sub> <sup>4,5</sup> | SR | С | Voltage on VDD pins (VDDE_A, VDDE_B,<br>VDDE_C, VDDE_E, VDDMA, VDDMB,<br>VDDMC) with respect to ground (V <sub>SS</sub> ) | Voltage drop <sup>2</sup>         | 4.5                   | 5.5                   | V    |

### Table 14. Recommended operating conditions (5.0 V)

### 3.4.2 Connecting power supply pins: What to do and what not to do

- Do:

- Have all power/ground supplies connected on the board from a strong supply source rather than weak voltage divider sources unless there is "NO IO activity" in the section

- Meet the supply specifications for max / typical operating conditions to guarantee correct operation

- Place the decoupling near the supply/ground pin pair for EMI emissions reduction

- Route high-noise supply/ground away from sensitive signals (for example, ADC channels must be away from SMD supply/motor pads)

- Use star routing for the ballast supply from the VDDR supply to avoid ballast startup noise injected to VDDR supply of the device

- Use LC inductive filtering for ADC, OSC, and PLL supplies if these are generated from common board regulators

- Do not:

- Violate injection current limit per IO/All IO pins as per specifications

- Connect sensitive supplies/ground on noisy supplies/ground (that is, ADC, PLL, and OSC)

- Use SMD supply for generation of noise free supply as these are most noisy lines in the system

- Connect different VDD pins (connected together inside the device) to different potentials.

# 3.5 Thermal characteristics

### Table 15. LQFP thermal characteristics

| Symb               | 0  | С | Parameter                                                                                   | Conditions                               | Va | lue     | Unit |

|--------------------|----|---|---------------------------------------------------------------------------------------------|------------------------------------------|----|---------|------|

| Gynnb              | 01 | U | i arameter                                                                                  | 144-                                     |    | 176-pin | Onit |

| $R_{\thetaJA}$     | CC | D | Thermal resistance, junction-to-ambient                                                     | Single layer board—1s                    | 50 | 43      | °C/W |

|                    | CC |   | natural convection <sup>1</sup>                                                             | Four layer board—2s2p                    | 41 | 35      | °C/W |

| R <sub>0JMA</sub>  | СС | D | Thermal resistance, junction-to-moving-air ambient <sup>2</sup>                             | @ 200 ft./min., single layer<br>board—1s | 41 | 35      | °C/W |

|                    | СС |   |                                                                                             | @ 200 ft./min., four layer<br>board—2s2p | 35 | 30      | °C/W |

| $R_{\theta JB}$    | CC | D | Thermal resistance, junction-to-board <sup>2</sup>                                          | _                                        | 29 | 24      | °C/W |

| $R_{\theta JCtop}$ | СС | D | Thermal resistance, junction-to-case (top) <sup>3</sup>                                     | —                                        | 10 | 9       | °C/W |

| Ψ <sub>JT</sub>    | СС | D | Junction-to-package top thermal characterization parameter, natural convection <sup>4</sup> | —                                        | 2  | 2       | °C/W |

NOTES:

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

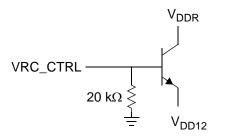

### Figure 5. External NPN ballast connections

### Table 19. Allowed ballast components

| Part  | Manufacturer                      | Recommended derivative |

|-------|-----------------------------------|------------------------|

| BCP68 | ON, IFX, NXP, Fairchild, ST, etc. | BCP68                  |

| BCX68 | IFX                               | BCX68-10<br>BCX68-16   |

| BC817 | ON, IFX, NXP, Fairchild, etc.     | BC817Su<br>BC817-25    |

| BCP56 | ON, IFX, NXP, Fairchild, ST, etc. | BCP68-10<br>BCP68-16   |

#### Table 20. Ballast component parameters

| Parameter                       | Specification                                                                                             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|

| Capacitance on VDDR             | 10 μF (minimum)<br>Place close to NPN collector                                                           |

| Stability capacitance on VDD12  | 40 μF (minimum)<br>Place close to NPN emitter                                                             |

| Decoupling capacitance on VDD12 | 100 nF $\times$ number of pins (minimum) Place on each VDD12/VSS12 pair and on the PLL supply/ground pair |

| Base resistor                   | 20 kΩ                                                                                                     |

The capacitor values listed in Table 20 include a de-rating factor of 40%, covering tolerance, temperature, and aging effects. These factors are taken into account to assure proper operation under worst-case conditions. X7R type materials are recommended for all capacitors, based on ESR characteristics.

Large capacitors are for regulator stability and should be located near the external ballast transistor. The number of capacitors is not important — only the overall capacitance value and the overall ESR value are important.

Small capacitors are for power supply decoupling, although they do contribute to the overall capacitance values. They should be located close to the device pin.

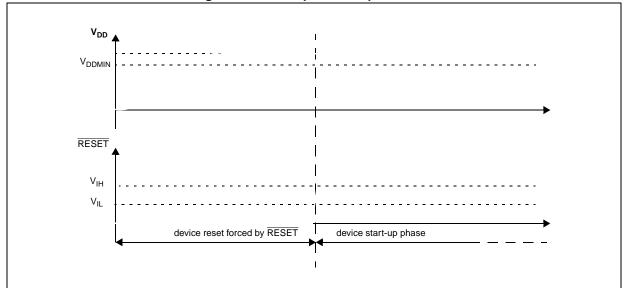

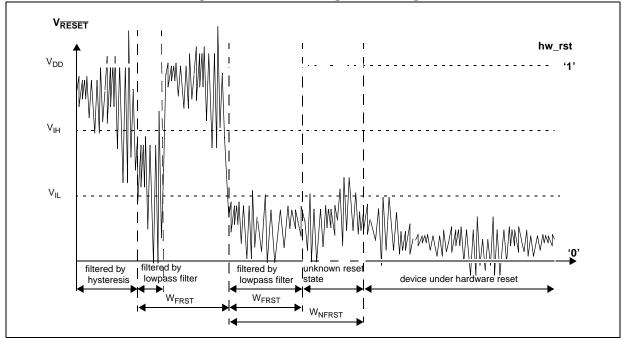

Figure 11. Start-up reset requirements

Figure 12. Noise filtering on reset signal

| No. | Pad                         | Ts  | witchc<br>(ns) | on <sup>1</sup> | R   | ise/Fal<br>(ns) | <sup>2</sup> | Fr  | equen<br>(MHz) | -        |     | rrent s<br>mA/ns |     | Load drive<br>(pF) |

|-----|-----------------------------|-----|----------------|-----------------|-----|-----------------|--------------|-----|----------------|----------|-----|------------------|-----|--------------------|

|     |                             | Min | Тур            | Max             | Min | Тур             | Max          | Min | Тур            | Max      | Min | Тур              | Max | (рі)               |

| 3   | Fast                        | 1   | —              | 6               | 1   | —               | 4            |     | —              | 72       | 3   | —                | 40  | 25                 |

|     |                             | 1   |                | 6               | 1.5 |                 | 7            | _   |                | 55       | 3   |                  | 40  | 50                 |

|     |                             | 1   | —              | 6               | 3   | —               | 12           | _   | —              | 40       | 3   | —                | 40  | 100                |

|     |                             | 1   | —              | 6               | 5   | —               | 18           | _   | —              | 25       | 3   | _                | 40  | 200                |

| 4   | Pull Up/Down<br>(3.6 V max) |     | —              | —               | —   | —               | 7500         | _   | —              | —        | _   | —                | —   | 50                 |

|     | Parameter                   |     | D              |                 |     | С               |              |     | С              | <u>.</u> |     | С                |     | n/a                |

### Table 51. Pad AC specifications $(3.3 \text{ V}, \text{PAD3V5V} = 1)^1$ (continued)

NOTES: <sup>1</sup> Propagation delay from V<sub>DD</sub>/2 of internal signal to Pchannel/Nchannel on condition

<sup>2</sup> Slope at rising/falling edge

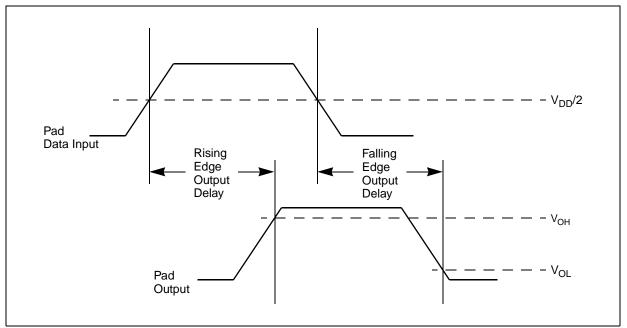

Figure 22. Pad output delay

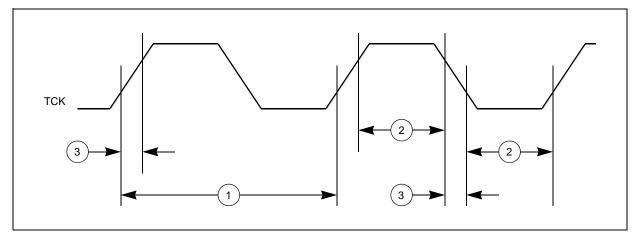

Figure 23. JTAG test clock input timing

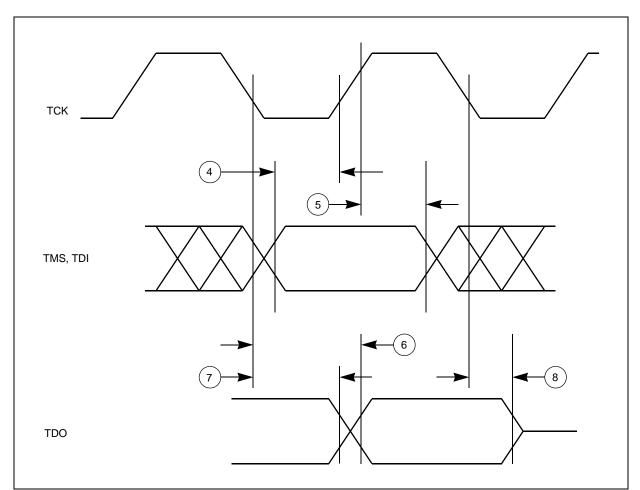

Figure 24. JTAG test access port timing

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

/3. DATUMS B, C AND D TO BE DETERMINED AT DATUM PLANE H.

$\overbrace{}^{4.}$  The top package body size may be smaller than the bottom package size by a maximum of 0.1 mm.

5. THIS DIMENSIONS DO NOT INCLUDE MOLD PROTRUSIONS. THE MAXIMUM ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. THIS DIMENSIONS ARE MAXIMUM BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

6. THIS DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION. PROTRUSIONS SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD SHALL BE 0.07 MM.

7. This dimensions are determined at the seating plane, datum a.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE            | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|-----------|---------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO         | ): 98ASS23177W   | REV: F      |

| 144 LEAD LQFP                                           |           | CASE NUMBER         | 8: 918–03        | 20 MAY 2005 |

| 20 X 20, 0.5 PITCH, 1.4                                 | 4 THICK   | STANDARD: NON-JEDEC |                  |             |

#### Figure 48. LQFP144 mechanical drawing (Part 3 of 3)

NOTES:

- 1 DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2 DIMENSIONS IN MILLIMETERS.

- 3 DATUM PLANE H IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4 DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

- THIS DIMENSIONS TO BE DETERMINED AT SEATING PLANE, DATUM C.

- C THIS DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE. THIS DIMENSIONS INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD 0.07.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                        | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|---------------------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO                     | ): 98ASS23479W   | REV: B      |

| 176 LD TQFP,<br>24 X 24 PKG, 0.5 PITCH, 1               | A THICK   | CASE NUMBER: 1101-01 02 JUN 200 |                  |             |

|                                                         | .+ IIION  | STANDARD: JE                    | DEC MS-026 BGA   |             |

### Figure 51. LQFP176 mechanical drawing (Part 3 of 3)