Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | e200z0h                                                    |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 64MHz                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART     |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                    |

| Number of I/O              | 133                                                        |

| Program Memory Size        | 1MB (1M x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 48K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                  |

| Data Converters            | A/D 16x10b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 176-LQFP                                                   |

| Supplier Device Package    | 176-LQFP (24x24)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpxd1010vlu64 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

### 1.1 Document overview

This document describes the device features and highlights important electrical and physical characteristics. For functional characteristics, see the *PXD10 Microcontroller Reference Manual*.

## 1.2 Description

The PXD10 family of chips is designed to enable the development of industrial HMI applications by providing a single-chip solution capable of hosting real-time applications and driving a TFT display directly using an on-chip color TFT display controller.

PXD10 chips incorporate a cost-efficient host processor core compliant with the Power Architecture<sup>®</sup> embedded category. The processor is 100% user-mode compatible with the Power Architecture and capitalizes on the available development infrastructure of current Power Architecture devices with full support from available software drivers, operating systems and configuration code to assist with users' implementations.

Offering high performance processing at speeds up to 64 MHz, the PXD10 family is optimized for low power consumption and supports a range of on-chip SRAM and internal flash memory sizes. The version with 1 MB of flash memory (PXD1010) features 160 KB of on-chip graphics SRAM.

See Table 1 for specific memory and feature sets of the product family members.

## 1.3 Device comparison

| Feature                        | PXD1005     | PXD1010 |  |  |

|--------------------------------|-------------|---------|--|--|

| CPU                            | e200z       | 0h      |  |  |

| Execution speed                | Static – 64 | 4 MHz   |  |  |

| Flash (ECC)                    | 512 KB      | 1 MB    |  |  |

| EEPROM Emulation Block (ECC)   | 4 × 16      | KB      |  |  |

| RAM (ECC)                      | 48 K        | В       |  |  |

| Graphics RAM                   | No          | 160 KB  |  |  |

| MPU                            | 12 en       | try     |  |  |

| eDMA                           | 16 chan     | nels    |  |  |

| Display Control Unit (DCU)     | No          | Yes     |  |  |

| Parallel Data Interface        | No          | Yes     |  |  |

| Stepper Motor Controller (SMC) | 6 moto      | ors     |  |  |

| Stepper Stall Detect (SSD)     | Yes         |         |  |  |

| Sound Generation Logic (SGL)   | Yes         |         |  |  |

Table 1. PXD10 family feature set

### Overview

## 1.6.3 Display Control Unit (DCU)

The DCU is a display controller designed to drive TFT LCD displays capable of driving up to WQVGA resolution screens with 16 layers and 4 planes with real time alpha-blending.

The DCU generates all the necessary signals required to drive the display: up to 24-bit RGB data bus, Pixel Clock, Data Enable, Horizontal-Sync and Vertical-Sync.

Internal memory resource of the PXD10 allows to easily handle complex graphics contents (pictures, icons, languages, fonts) on a color TFT panel in up to Wide Quarter Video Graphics Array (WQVGA) sizes. All the data fetches from internal and/or external memory are performed by the internal four-channel DMA of the DCU providing a high speed/low latency access to the system backbone.

Control Descriptors (CDs) associated with each layer enable effective merging of different resolutions into one plane to optimize use of internal memory buffers. A layer may be constructed from graphic content of various resolutions including 1bpp, 2bpp, 4bpp, 8bpp, 16bpp, 24bpp and 24bpp+alpha. The ability of the DCU to handle input data in resolutions as low as 1bpp, 2bpp and 4bpp enables a highly efficient use of internal memory resources of the PXD10. A special tiled mode can be enabled on any of the 16 layers to repeat a pattern optimizing graphic memory usage.

A hardware cursor can be managed independently of the layers at blending level increasing the efficient use of the internal DCU resources.

To secure the content of all critical information to be displayed, a safety mode can be activated to check the integrity of critical data along the whole system data path from the memory to the TFT pads.

The DCU features the following:

- Display color depth: up to 24 bpp

- Generation of all RGB and control signals for TFT

- Four-plane blending

- Maximum number of Input Layers: 16 (fixed priority)

- Dynamic look-up table (color and gamma look-up)

- $\alpha$ -blending range: as many as 256 levels

- Transparency Mode

- Gamma Correction

- Tiled mode on all the layers

- Hardware cursor

- Critical display content integrity monitoring for functional safety support

- Internal Direct Memory Access (DMA) module to transfer data from internal and/or external memory.

### 1.6.8 Flash memory

The PXD10 microcontroller has the following flash memory features:

- As much as 1 MB of burst flash memory

- Typical flash memory access time: 0 wait-state for buffer hits, 2 wait-states for page buffer miss at 64 MHz

- Two  $4 \times 128$ -bit page buffers with programmable prefetch control

- One set of page buffers can be allocated for code-only, fixed partitions of code and data, all available for any access

- One set of page buffers allocated to Display Controller Unit and the eDMA

- 64-bit ECC with single-bit correction, double-bit detection for data integrity

- 64 KB data flash memory separate  $4 \times 16$  KB flash block for EEPROM emulation with prefetch buffer and 128-bit data access port

- Small block flash memory arrangement to support features such as boot block, operating system block

- Hardware managed flash memory writes, erase and verify sequence

- Censorship protection scheme to prevent flash memory content visibility

- Separate dedicated 64 KB data flash memory for EEPROM emulation

- Four erase sectors each containing 16 KB of memory

- Offers Read-While-Write functionality from main program space

- Same data retention and program erase specification as main program flash memory array

### 1.6.9 Static random-access memory (SRAM)

The PXD10 microcontrollers have as much as 48 KB general-purpose on-chip SRAM with the following features:

- Typical SRAM access time: 0 wait-state for reads and 32-bit writes; 1 wait-state for 8- and 16-bit writes if back to back with a read to same memory block

- 32-bit ECC with single-bit correction, double bit detection for data integrity

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

- User transparent ECC encoding and decoding for byte, half word, and word accesses

- Separate internal power domain applied to full SRAM block, 8 KB SRAM block during STANDBY modes to retain contents during low power mode.

### 1.6.10 On-chip graphics SRAM

The PXD10 microcontroller has 160 KB on-chip graphics SRAM with the following features:

- Usable as general purpose SRAM

- Typical SRAM access time: 0 wait-state for reads and 32-bit writes

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

### 1.6.16 Controller Area Network (CAN) module

The PXD10 contains two CAN modules that offer the following features:

- Compliant with CAN protocol specification, Version 2.0B active

- 64 mailboxes, each configurable as transmit or receive

- Mailboxes configurable while module remains synchronized to CAN bus

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

- Listen only mode capabilities

- CAN Sampler

- Can catch the first message sent on the CAN network while the PXD10 is stopped. This guarantees a clean startup of the system without missing messages on the CAN network.

- The CAN sampler is connected to one of the CAN RX pins.

## 1.6.17 Inter-IC Communications (I<sup>2</sup>C) module

The I<sup>2</sup>C module features the following:

- As many as four I<sup>2</sup>C modules supported

- Two-wire bi-directional serial bus for on-board communications

- Compatibility with I<sup>2</sup>C bus standard

- Multimaster operation

- Software-programmable for one of 256 different serial clock frequencies

- Software-selectable acknowledge bit

- Interrupt-driven, byte-by-byte data transfer

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus-busy detection

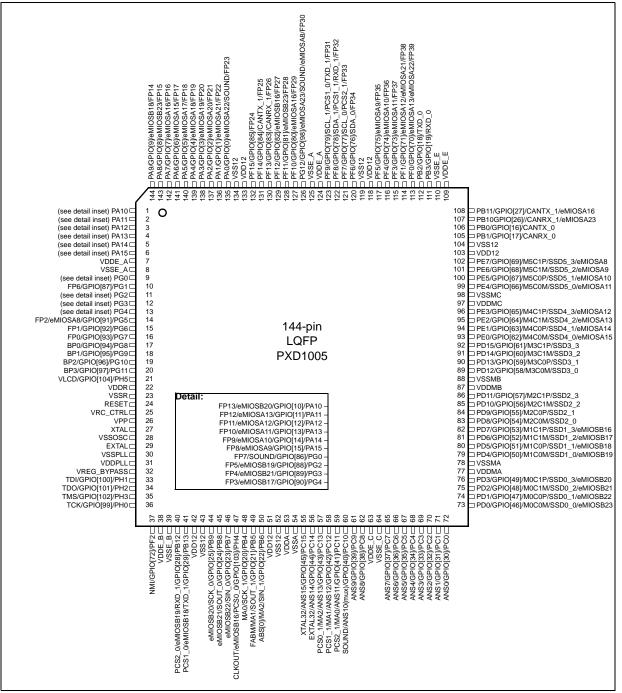

Figure 3. 144-pin LQFP pinout for PXD1005

## 2.3 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

After power-up phase, all pads are floating with the following exceptions:

- PB[5] (FAB) is pull-down. Without external strong pullup the device starts fetching from flash.

- RESET pad is driven low. This is released only after PHASE2 reset completion.

- Main oscillator pads (EXTAL, XTAL) are tristate.

- Nexus output pads (MDO[n], MCKO, EVTO, MSEO) are forced to output.

- The following pads are pullup:

- PB[6]

- PH[0]

- PH[1]

- PH[3]

- EVTI

### 2.4 Voltage supply pins

Voltage supply pins are used to provide power to the device. Two dedicated pins are used for 1.2 V regulator stabilization.

There is a preferred power-up sequence for devices in the PXD10 family. That sequence is described in the following paragraphs.

Broadly, the supply voltages can be grouped as follows:

- VREG HV supply (V<sub>DDR</sub>)

- Generic I/O supply

- $V_{DDA}$

- V<sub>DDE\_A</sub>

- V<sub>DDE\_B</sub>

- $V_{DDE_C}$

- $V_{DDE_E}$

- V<sub>DDMA</sub>

- V<sub>DDMB</sub>

- V<sub>DDMC</sub>

- V<sub>DDPLL</sub>

- LV supply (V<sub>DD12</sub>)

The preferred order of ramp up is as follows:

1. Generic I/O supply

#### **Pinout and signal descriptions**

|           |                               | Pad  | 1/0       | Reset         | Pin number |               |                |  |

|-----------|-------------------------------|------|-----------|---------------|------------|---------------|----------------|--|

| Debug pin | Function                      | type | direction | Configuration | 144 LQFP   | 176 LQFP<br>1 | 208 MAPB<br>GA |  |

| MDO1      | Nexus message clock<br>output | М    | I/O       | None          | _          | 40            | C11            |  |

| MDO2      | Nexus message clock output    | М    | I/O       | None          | _          | 42            | D11            |  |

| MDO3      | Nexus message clock output    | М    | I/O       | None          | _          | 44            | A10            |  |

| MSEO      | Nexus message clock output    | М    | I/O       | None          | —          | 34            | C12            |  |

#### Table 4. Debug pin descriptions (continued)

NOTES:

On the 176 LQFP package options the Nexus pins are multiplexed with other GPIO. On the 208 TEPBGA package, there are additional dedicated Nexus pins.

|           |                               | Pad  | 1/0       | Reset          | Pin number |          |                            |  |

|-----------|-------------------------------|------|-----------|----------------|------------|----------|----------------------------|--|

| Debug pin | Function                      | type | direction | Configuration  | 144 LQFP   | 176 LQFP | TEPBGA2<br>08 <sup>1</sup> |  |

| EVTI      | Nexus event input             | М    | I/O       | Input, Pull Up |            | —        | Т3                         |  |

| EVTO      | Nexus event output            | М    | I/O       | Input, Pull Up | —          | _        | R3                         |  |

| MCKO      | Nexus message clock<br>output | F    | I/O       | Input, Pull Up | _          | —        | T1                         |  |

| MDO0      | Nexus message clock<br>output | М    | I/O       | Input, Pull Up |            | —        | T5                         |  |

| MDO1      | Nexus message clock<br>output | М    | I/O       | Input, Pull Up |            | —        | P5                         |  |

| MDO2      | Nexus message clock<br>output | М    | I/O       | Input, Pull Up | _          | _        | P4                         |  |

| MDO3      | Nexus message clock<br>output | М    | I/O       | Input, Pull Up | _          | _        | L4                         |  |

| MSEO      | Nexus message clock output    | М    | I/O       | Input, Pull Up | —          | —        | T2                         |  |

### Table 5. Debug pin descriptions

NOTES:

The dedicated (208 pin package only) Nexus output pins (Message Data outputs 0:3 [MDO] and Message Start/End outputs 0:1 [MSEO]) may drive an unknown value (high or low) immediately after power up but before-the 1st clock edge propagates through the device (instead of being weakly pulled low). This may cause high currents if the pins are tied directly to a supply/ground or any low resistance-driver (when used as a general purpose input [GPI] in the application).

| 4 |

|---|

| Ń |

| Port   | PCR      | Alternate                                    | Function                                  | Special               | Peripheral <sup>3</sup>         | I/O       | Pad               | RESET                | Pin number |          |

|--------|----------|----------------------------------------------|-------------------------------------------|-----------------------|---------------------------------|-----------|-------------------|----------------------|------------|----------|

| pin    | register | function <sup>1</sup>                        | Function                                  | function <sup>2</sup> | renpilerai                      | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP   | 176 LQFP |

| PE[2]  | PCR[64]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[64]<br>M4C1M<br>SSD4_2<br>eMIOSA[13] | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 95         | 111      |

| PE[3]  | PCR[65]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[65]<br>M4C1P<br>SSD4_3<br>eMIOSA[12] | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 96         | 112      |

| PE[4]  | PCR[66]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[66]<br>M5C0M<br>SSD5_0<br>eMIOSA[11] | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 99         | 115      |

| PE[5]  | PCR[67]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[67]<br>M5C0P<br>SSD5_1<br>eMIOSA[10] | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 100        | 116      |

| PE[6]  | PCR[68]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[68]<br>M5C1M<br>SSD5_2<br>eMIOSA[9]  | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 101        | 117      |

| PE[7]  | PCR[69]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[69]<br>M5C1P<br>SSD5_3<br>eMIOSA[8]  | -                     | SIUL<br>SMC<br>SSD<br>PWM/Timer | I/O       | SMD               | None,<br>None        | 102        | 118      |

| PE[8]  | —        | —                                            | Reserved                                  | —                     | —                               | _         | _                 | —                    | —          | _        |

| PE[9]  | _        | —                                            | Reserved                                  | —                     | —                               | —         |                   | —                    | —          | _        |

| PE[10] | _        | —                                            | Reserved                                  | _                     | _                               | _         |                   | —                    | _          |          |

| PE[11] |          | _                                            | Reserved                                  | _                     | _                               |           |                   |                      |            | _        |

| PE[12] |          | _                                            | Reserved                                  | _                     | _                               |           |                   | —                    |            |          |

| PE[13] | —        | _                                            | Reserved                                  | _                     | _                               | _         | _                 | —                    | —          | _        |

| PE[14] | —        | —                                            | Reserved                                  | _                     | _                               | —         |                   | —                    | —          |          |

| PE[15] | —        | —                                            | Reserved                                  | —                     | —                               | —         | —                 | _                    | —          | _        |

| ົ |

|---|

| Port               | PCR      | Alternate                                    | Function                                     | Special               | Peripheral <sup>3</sup>               | I/O       | Pad               | RESET                | Pin number |          |

|--------------------|----------|----------------------------------------------|----------------------------------------------|-----------------------|---------------------------------------|-----------|-------------------|----------------------|------------|----------|

| pin                | register | function <sup>1</sup>                        | T unotion                                    | function <sup>2</sup> | renpiierai                            | direction | type <sup>4</sup> | config. <sup>5</sup> | 144 LQFP   | 176 LQFP |

| PG[8]              | PCR[94]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[94]<br>DCU_VSYNC<br>—                   | BP0                   | SIUL<br>DCU<br>—                      | I/O       | M2                | Input,<br>None       | 17         | 17       |

| PG[9]              | PCR[95]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[95]<br>DCU_HSYNC<br>—                   | BP1                   | SIUL<br>DCU<br>—                      | I/O       | M1                | Input,<br>None       | 18         | 18       |

| PG[10]             | PCR[96]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[96]<br>DCU_DE<br>—                      | BP2                   | SIUL<br>DCU<br>—                      | I/O       | M2                | None,<br>None        | 19         | 19       |

| PG[11]             | PCR[97]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[97]<br>DCU_PCLK<br>—                    | BP3                   | SIUL<br>DCU<br>—                      | I/O       | M1                | None,<br>None        | 20         | 20       |

| PG[12]             | PCR[98]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[98]<br>eMIOSA[23]<br>SOUND<br>eMIOSA[8] | FP30                  | SIUL<br>PWM/Timer<br>SGL<br>PWM/Timer | I/O       | S                 | None,<br>None        | 126        | 156      |

| PG[13]             | _        | —                                            | Reserved                                     | _                     | _                                     | _         | —                 | —                    | —          |          |

| PG[14]             | _        | —                                            | Reserved                                     | _                     | —                                     | _         | _                 | —                    | —          |          |

| PG[15]             | —        | —                                            | Reserved                                     | —                     | —                                     | —         | _                 | —                    | —          | —        |

| PH[0] <sup>7</sup> | PCR[99]  | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[99]<br>TCK<br>—<br>—                    | -                     | SIUL<br>JTAG<br>—                     | I/O       | S                 | Input,<br>Pullup     | 36         | 43       |

| PH[1] <sup>7</sup> | PCR[100] | Option 0<br>Option 1<br>Option 2<br>Option 3 | GPIO[100]<br>TDI<br>—<br>—                   | -                     | SIUL<br>JTAG<br>—                     | I/O       | S                 | Input,<br>Pullup     | 33         | 36       |

Pinout and signal descriptions

Freescale Semiconductor

## 3.3 NVUSRO register

Portions of the device configuration, such as high voltage supply, oscillator margin, and watchdog enable/disable after reset are controlled via bit values in the Nonvolatile User Options (NVUSRO) register. For a detailed description of the NVUSRO register, please see the chip reference manual.

### 3.3.1 NVUSRO[PAD3V5V] field description

Table 10 shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 10. PAD3V5V field description<sup>1</sup>

| Value <sup>2</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

| NOTES              | ·                            |

NOTES:

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value before Flash initialization is '1' (3.3 V)

The DC electrical characteristics are dependent on the PAD3V5V bit value.

## 3.3.2 NVUSRO[OSCILLATOR\_MARGIN] field description

Table 10 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

Table 11. OSCILLATOR\_MARGIN field description<sup>1</sup>

| Value <sup>2</sup> | Description                                 |

|--------------------|---------------------------------------------|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |

| 1                  | High margin configuration (4 MHz/16 MHz)    |

| NOTES              |                                             |

NOTES:

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value before Flash initialization is '1'

The 4–16 MHz fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value.

| Symbo              | Symbol C Parameter |   | C Parameter Conditions                                             |            | Va                 | Unit              |      |

|--------------------|--------------------|---|--------------------------------------------------------------------|------------|--------------------|-------------------|------|

| Symbo              | 21                 | C | Falameter                                                          | Conditions | Min                | Max               | Unit |

| V <sub>SSOSC</sub> | SR                 | С | Voltage on VSSOSC (oscillator ground) pin with respect to $V_{SS}$ |            | 0                  | 0                 | V    |

| V <sub>LCD</sub>   | SR                 |   | Voltage on VLCD (LCD supply) pin with respect to $V_{\text{SS}}$   |            | 0                  | $V_{DDE_A} + 0.3$ | V    |

| TV <sub>DD</sub>   | SR                 | С | V <sub>DD</sub> slope to ensure correct power up                   | _          | 5×10 <sup>-6</sup> | 0.25              | V/µs |

| T <sub>A</sub>     | SR                 | С | Ambient temperature under bias                                     | _          | -40                | 105               | °C   |

| Τ <sub>J</sub>     | SR                 | С | Junction temperature under bias                                    |            | -40                | 150               |      |

Table 13. Recommended operating conditions (3.3 V) (continued)

NOTES: <sup>1</sup> 100 nF capacitance needs to be provided between  $V_{DDA}/V_{SSA}$  pair.

$^2~$  At least 10  $\mu F$  capacitance must be connected between V\_{DDR} and V\_{SS}. This is required because of sharp surge due to external ballast.

$^{3}$  V<sub>DD</sub> refers collectively to I/O voltage supplies, i.e., V<sub>DDE\_A</sub>, V<sub>DDE\_B</sub>, V<sub>DDE\_C</sub>, V<sub>DDE\_E</sub>, V<sub>DDMA</sub>, V<sub>DDMB</sub> and V<sub>DDMC</sub>.

<sup>4</sup> 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/O's DC electrical specification may not be guaranteed. When voltage drops below  $V_{\ensuremath{\mathsf{LVDHVL}}}$  device is reset.

<sup>6</sup> V<sub>SS</sub> refers collectively to I/O voltage supply grounds, i.e., V<sub>SSE\_A</sub>, V<sub>SSE\_B</sub>, V<sub>SSE\_C</sub>, V<sub>SSE\_E</sub>, V<sub>SSMA</sub>, V<sub>SSMB</sub> and V<sub>SSMC</sub>) unless otherwise noted.

| Symbol                         |    | с | C Parameter                                                                                                               | Conditions                        | Va                    | Unit                  |      |

|--------------------------------|----|---|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-----------------------|------|

| Symbo                          | 01 | C | Falameter                                                                                                                 | Conditions                        | Min Max               |                       | Unit |

| V <sub>DDA</sub> <sup>1</sup>  | SR | С | 5 1 ( )                                                                                                                   | —                                 | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SS</sub> )                                                                                      | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to<br>V <sub>DDE_C</sub> | V <sub>DD</sub> – 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSA</sub>               | SR | С | Voltage on VSSA (ADC reference) pin with respect $\rm V_{SS}$                                                             |                                   | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>SSPLL</sub>             | SR | С | Voltage on VSSPLL pin with respect to $V_{SS12}$                                                                          |                                   | 0                     | 0                     | V    |

| V <sub>DDR</sub> <sup>3</sup>  | SR | С | Voltage on VDDR pin (regulator supply) with                                                                               | _                                 | 4.5                   | 5.5                   | V    |

|                                |    | С | respect to ground (V <sub>SSR</sub> )                                                                                     | Voltage drop <sup>2</sup>         | 3.0                   | 5.5                   |      |

|                                |    | С |                                                                                                                           | Relative to V <sub>DD</sub>       | V <sub>DD</sub> - 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>SSR</sub>               | SR | С | Voltage on VSSR (regulator ground) pin with respect to $\rm V_{SS12}$                                                     |                                   | 0                     | 0                     | V    |

| V <sub>SS12</sub>              | СС | С | Voltage on VSS12 pin with respect to $V_{SS}$                                                                             | _                                 | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>DD</sub> <sup>4,5</sup> | SR | С | Voltage on VDD pins (VDDE_A, VDDE_B,<br>VDDE_C, VDDE_E, VDDMA, VDDMB,<br>VDDMC) with respect to ground (V <sub>SS</sub> ) | Voltage drop <sup>2</sup>         | 4.5                   | 5.5                   | V    |

### Table 14. Recommended operating conditions (5.0 V)

The thermal characterization parameter is measured in compliance with the JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. Position the thermocouple so that the thermocouple junction rests on the package. Place a small amount of epoxy on the thermocouple junction and approximately 1 mm of wire extending from the junction. Place the thermocouple wire flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

References:

Semiconductor Equipment and Materials International 805 East Middlefield Rd. Mountain View, CA 94043 USA (415) 964-5111

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

## 3.6 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### 3.6.1 EMC requirements on board

The following practices help minimize noise in applications.

- Place a 100 nF capacitor between each of the  $V_{DD12}/V_{SS12}$  supply pairs and also between the  $V_{DDPLL}/V_{SSPLL}$  pair. The voltage regulator also requires stability capacitors for these supply pairs.

- Place a 10 µF capacitor on VDDR.

- Isolate VDDR with ballast emitter to avoid voltage droop during STANDBY mode exit.

- Enable pad slew rate only as necessary to eliminate I/O noise:

- Enabling slew rate for SMD pads will reduce noise on motors.

- Disabling slew rate for non-SMD pads will reduce noise on non-SMD IOs.

- Enable PLL modulation  $(\pm 2\%)$  for system clock.

- Place decoupling capacitors for all HV supplies close to the pins.

### 3.6.2 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

• Software recommendations – The software flowchart must include the management of runaway conditions such as:

| Sum               | Symbol |   | Devementer                                              | Conditions <sup>1</sup>                                                                              | ,                     | Value |                    | l Init |

|-------------------|--------|---|---------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|--------|

|                   |        | С | Parameter                                               | Conditions                                                                                           | Min                   | Тур   | Unit               |        |

| V <sub>OH</sub>   | CC     | Ρ | Output high level<br>MEDIUM configuration               | Push Pull, $I_{OH} = -2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | 0.8V <sub>DD</sub>    | -     | _                  | V      |

|                   |        | D |                                                         | Push Pull, $I_{OH} = -1 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>     | 0.8V <sub>DD</sub>    | —     |                    |        |

|                   |        | С |                                                         | Push Pull, $I_{OH} = -1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | V <sub>DD</sub> – 0.8 | —     | —                  | -      |

| V <sub>OL</sub>   | СС     | Ρ | Output low level<br>MEDIUM configuration                | Push Pull, $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended)  | _                     | —     | 0.1V <sub>DD</sub> | V      |

|                   |        | D |                                                         | Push Pull, I <sub>OL</sub> = 1 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>        | _                     | —     | 0.1V <sub>DD</sub> |        |

|                   |        | С |                                                         | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)  | _                     | —     | 0.5                | -      |

| T <sub>tr</sub>   | СС     | Т | Output transition time out-<br>put pin <sup>3</sup>     | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                                | _                     | —     | 10                 | ns     |

|                   |        | Т | MEDIUM configuration                                    | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                                | _                     | —     | 20                 |        |

|                   |        | Т |                                                         | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                               | _                     |       | 40                 |        |

|                   |        | Т |                                                         | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                | _                     |       | 12                 |        |

|                   |        | Т |                                                         | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                | _                     | —     | 25                 |        |

|                   |        | Т |                                                         | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                               | _                     |       | 40                 |        |

| $\Delta I_{tr50}$ | CC     | D | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |                                                                                                      | 7                     | mA/ns |                    |        |

|                   |        | D |                                                         | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1                                                           | _                     | -     | 16                 |        |

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = –40 to 105 °C, unless otherwise specified

<sup>2</sup> This is a transient configuration during power-up. All pads but RESET and NEXUS output (MDOx, EVTO, MCK) are configured in input or in high impedance state.

<sup>3</sup> C<sub>L</sub> includes device and package capacitance ( $C_{PKG} < 5 \text{ pF}$ ).

| Symbol              |    | ~ | Deveneeter                                                  | Conditions                                    |                        | Value |                       | Unit |

|---------------------|----|---|-------------------------------------------------------------|-----------------------------------------------|------------------------|-------|-----------------------|------|

|                     |    | С | Parameter                                                   | Conditions                                    | Min                    | Тур   | Тур Мах               |      |

| V <sub>IL</sub>     | CC | Ρ | Low level input voltage                                     | —                                             | -0.4                   |       | 0.35×V <sub>DDM</sub> | V    |

| V <sub>IH</sub>     | CC | Ρ | High level input voltage                                    | —                                             | $0.65 \times V_{DDM}$  |       | V <sub>DDM</sub> +0.4 |      |

| V <sub>HYST</sub>   | CC | С | Schmitt trigger hysteresis                                  | —                                             | 0.1×V <sub>DDM</sub>   |       | —                     |      |

| V <sub>OL</sub>     | CC | Ρ | Low level output voltage                                    | I <sub>OL</sub> = 20 mA <sup>1</sup>          | —                      |       | 0.32                  |      |

|                     |    |   |                                                             | $I_{OL} = 30 \text{ mA}^2$                    | —                      |       | 0.48                  |      |

| V <sub>OH</sub>     | CC | Ρ | High level output voltage                                   | I <sub>OH</sub> = -20 mA <sup>1</sup>         | V <sub>DDM</sub> -0.32 |       | —                     |      |

|                     |    |   |                                                             | I <sub>OH</sub> = -30 mA <sup>2</sup>         | V <sub>DDM</sub> -0.48 |       | —                     |      |

| I <sub>PU</sub>     | CC | Ρ | Internal pull-up device current                             | V <sub>in</sub> =V <sub>IL</sub>              | -130                   |       | —                     | μA   |

|                     |    |   |                                                             | V <sub>in</sub> =V <sub>IH</sub>              | —                      |       | -10                   |      |

| I <sub>PD</sub>     | СС | Ρ | Internal pull-down device current                           | V <sub>in</sub> =V <sub>IL</sub>              | 10                     | _     | —                     |      |

|                     |    |   |                                                             | V <sub>in</sub> =V <sub>IH</sub>              | —                      |       | 130                   |      |

| I <sub>IN</sub>     | CC | Ρ | Input leakage current                                       | —                                             | -1                     |       | 1                     |      |

| R <sub>DSONH</sub>  | CC | С | SMD pad driver active high impedance                        | $IOH \le -30 \text{ mA}^2$                    | —                      | —     | 16                    | Ω    |

| R <sub>DSONL</sub>  | СС | С | SMD pad driver active low impedance                         | $IOL \le 30 \text{ mA}^2$                     | _                      | —     | 16                    | Ω    |

| V <sub>OMATCH</sub> | СС | Ρ | Output driver matching<br>V <sub>OH</sub> / V <sub>OL</sub> | $I_{OH}$ / $I_{OL}$ $\leq$ 30 mA <sup>2</sup> | —                      | _     | 90                    | mV   |

NOTES:

<sup>1</sup> VDD = 5.0 V  $\pm$ 10%, Tj = -40 to 150 °C.

<sup>2</sup> VDD = 5.0 V  $\pm$ 10%, Tj = -40 to 130 °C.

### 3.8.4 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 34.

Table 35 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{AVGSEG}$  maximum value.

In order to ensure device functionality, the sum of the dynamic and static current of the I/O on a single segment should remain below the  $I_{DYNSEG}$  maximum value.

| Paakaga  |                           |                | Supply segment   |                |                |

|----------|---------------------------|----------------|------------------|----------------|----------------|

| Package  | A <sup>1</sup>            | B <sup>2</sup> | C <sup>3,4</sup> | D <sup>5</sup> | E <sup>6</sup> |

| 144 LQFP | pins 1–21<br>pins 113–144 | pins 22– 52    | pins 53–72       | pins 73–102    | pins 103–112   |

| 176 LQFP | pins 1–21<br>pins 143–176 | pins 22–68     | pins 69–88       | pins 89–118    | pins 119–142   |

### Table 34. I/O supply segment

NOTES:

<sup>1</sup> LCD pad segment containing pad supplies  $V_{DDE_A}$

$^2\,$  Miscellaneous pad segment containing pad supplies V\_{DDE\_B}

$^3\,$  ADC pad segment containing pad supplies  $V_{\text{DDE}\_\text{C}}$

<sup>4</sup> V<sub>DDE\_C</sub> should be the same as V<sub>DDA</sub> with a 100 mV variation, i.e., V<sub>DDE\_C</sub> = V<sub>DDA</sub>  $\pm$ 100 mV.

<sup>5</sup> Stepper Motor pad segment containing I/O supplies  $V_{DDMA}$ ,  $V_{DDMB}$ ,  $V_{DDMC}$

$^{6}$  Miscellaneous pad segment containing pad supplies V<sub>DDE\_E</sub>

### Table 35. I/O consumption

| Symbo               | 1  | с | Parameter                                           | Conditions <sup>1</sup> Value<br>Min Typ                                     |   | Conditions <sup>1</sup> |     | Value |  | Unit |

|---------------------|----|---|-----------------------------------------------------|------------------------------------------------------------------------------|---|-------------------------|-----|-------|--|------|

| Symbol              | 1  | C | Falameter                                           |                                                                              |   | Тур                     | Max | Unit  |  |      |

| I <sub>SWTSLW</sub> | СС | D | Dynamic I/O current for SLOW configuration          | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0        | _ | —                       | 20  | mA    |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1        | _ | _                       | 16  |       |  |      |

| I <sub>SWTMED</sub> | СС | D | Dynamic I/O current for MEDIUM configuration        | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0        | _ | _                       | 29  | mA    |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1        | — |                         | 17  |       |  |      |

| ISWTFST             | СС | D | Dynamic I/O current for FAST configuration          | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0        | — | —                       | 110 | mA    |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1        | _ | —                       | 50  |       |  |      |

| I <sub>RMSSLW</sub> | СС | D | Root mean square I/O current for SLOW configuration | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _ | —                       | 2.3 | mA    |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  |   | —                       | 3.2 |       |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 |   | —                       | 6.6 |       |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  |   |                         | 1.6 |       |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | — | —                       | 2.3 |       |  |      |

|                     |    | D |                                                     | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | — | —                       | 4.7 |       |  |      |

| Cumha                |    | C | Devenueter                                                            | Conditions <sup>1</sup>                                                      | Value | Value |      |      |  |

|----------------------|----|---|-----------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|------|------|--|

| Symbo                |    | C | Parameter                                                             | er Conditions                                                                |       | Тур   | Max  | Unit |  |

| I <sub>RMSMED</sub>  | СС | D | Root mean square I/O current for MEDIUM configuration                 | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _     | —     | 6.6  | mA   |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | —     |       | 13.4 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | —     |       | 18.3 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | —     | —     | 5.0  |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | —     |       | 8.5  |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —     |       | 11.0 |      |  |

| I <sub>RMSFST</sub>  | СС | D | Root mean square I/O current for FAST configuration                   | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | —     |       | 22.0 | mA   |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _     |       | 33.0 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _     | _     | 56.0 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | —     |       | 14.0 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 25 pF, 4 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | —     |       | 20.0 |      |  |

|                      |    | D |                                                                       | C <sub>L</sub> = 100 pF, 2 MHz<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —     |       | 25.0 |      |  |

| I <sub>DYNSEG</sub>  | SR | D | Sum of all the dynamic and static                                     | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                                   | _     |       | 110  | mA   |  |

|                      |    | D | I/O current within a supply seg-<br>ment                              | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                   | _     |       | 65   |      |  |

| I <sub>AVGSEG</sub>  | SR | D | Sum of all the static I/O current                                     | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                       | —     | —     | 70   | mA   |  |

|                      |    | D | within a supply segment                                               | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                   | —     |       | 65   | 1    |  |

| I <sub>DDMxAVG</sub> | SR | D | Sum of currents of two motors assigned to segment V <sub>DDMx</sub> , | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>T <sub>J</sub> = 130 °C        | —     | —     | 90   | ]    |  |

|                      |    |   | V <sub>SSMx</sub> pair                                                | $V_{DD} = 5.0 V \pm 10\%$ , PAD3V5V = 0<br>T <sub>J</sub> = -40 °C           |       | _     | 120  |      |  |

Table 35. I/O consumption (continued)

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = -40 to 105 °C, unless otherwise specified

| Symbol             |    | С | Parameter                                      | Conditions <sup>1</sup>                                                                             |                    | Value |                       |      |

|--------------------|----|---|------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------|-------|-----------------------|------|

|                    |    | C | Farameter                                      | Conditions                                                                                          | Min Typ Max        |       | Max                   | Unit |

| V <sub>IH</sub>    | SR | Ρ | Input high level CMOS<br>Schmitt Trigger       | _                                                                                                   | $0.65V_{DD}$       | —     | V <sub>DD</sub> + 0.4 | V    |

| V <sub>IL</sub>    | SR | Ρ | Input low level CMOS Schmitt<br>Trigger        | _                                                                                                   | -0.4               | —     | 0.35V <sub>DD</sub>   | V    |

| V <sub>HYS</sub>   | СС | D | Input hysteresis CMOS<br>Schmitt Trigger       | _                                                                                                   | 0.1V <sub>DD</sub> | —     | _                     | V    |

| V <sub>OL</sub>    | СС | Ρ | Output low level                               | Push Pull, $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) |                    |       | 0.1V <sub>DD</sub>    | V    |

|                    |    | D |                                                | Push Pull, I <sub>OL</sub> = 1 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>       | _                  | —     | 0.1V <sub>DD</sub>    |      |

|                    |    | С |                                                | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | _                  |       | 0.5                   |      |

| T <sub>tr</sub>    | СС | Т | Output transition time output pin <sup>3</sup> | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                               | _                  | —     | 10                    | ns   |

|                    |    | Т | MEDIUM configuration                           | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                               | _                  | —     | 20                    |      |

|                    |    | Т |                                                | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                              | _                  | —     | 40                    |      |

|                    |    | Т |                                                | C <sub>L</sub> = 25 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                               | _                  | —     | 12                    |      |

|                    |    | Т |                                                | C <sub>L</sub> = 50 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                               | _                  | —     | 25                    |      |

|                    |    | Т |                                                | C <sub>L</sub> = 100 pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                              | _                  | —     | 40                    |      |

| W <sub>FRST</sub>  | SR | Ρ | RESET input filtered pulse                     | —                                                                                                   |                    | —     | 40                    | ns   |

| W <sub>NFRST</sub> | SR | Ρ | RESET input not filtered pulse                 | —                                                                                                   | 1000               | —     | —                     | ns   |

| I <sub>WPU</sub>   | СС | Ρ | Weak pull-up current absolute value            | —                                                                                                   | 10                 | —     | 150                   | μA   |

|                    |    | D | RUN Current during RESET                       | Before Flash is ready                                                                               |                    | 10    | —                     | mA   |

|                    |    |   |                                                | After Flash is ready                                                                                |                    | 20    | —                     | mA   |

| Table 37. R | leset electrical | characteristics |

|-------------|------------------|-----------------|

|-------------|------------------|-----------------|

NOTES: <sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = –40 to 105 °C, unless otherwise specified

<sup>2</sup> This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to reset generation module (RGM) section of the device reference manual).

$^3$  C<sub>L</sub> includes device and package capacitance (C<sub>PKG</sub> < 5 pF).

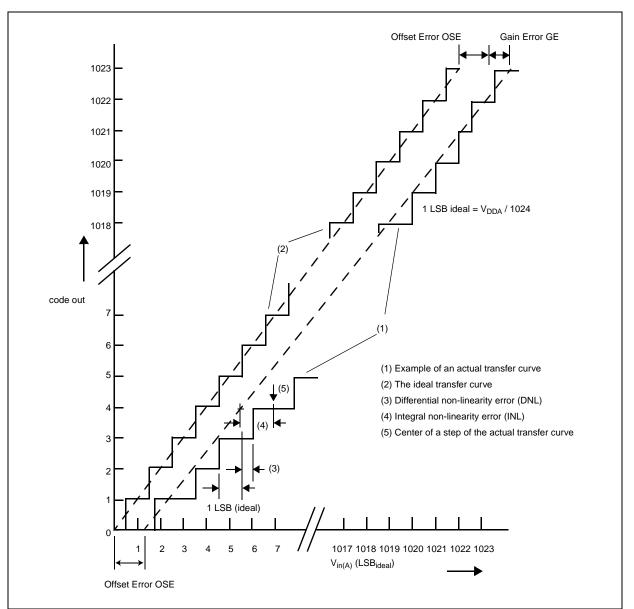

Figure 17. ADC Characteristics and Error Definitions

### 3.17.1 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer

source  $V_A$ ; the time constant  $R_F C_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing.

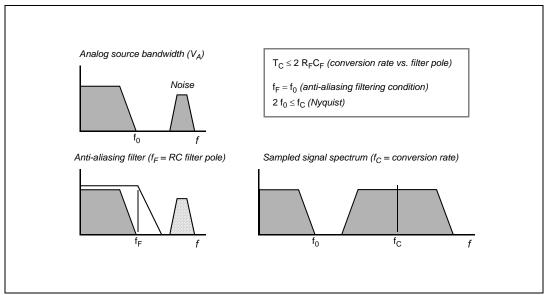

Figure 21. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 14 between the ideal and real sampled voltage on  $C_S$ :

$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

Eqn. 15

Egn. 14

$$C_F > 2048 \bullet C_S$$

# 6 Revision history

#### Table 65. Document revision history

| Revision | Date        | Substantive changes |

|----------|-------------|---------------------|

| 1        | 30 Sep 2011 | Initial release.    |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: PXD10 Rev. 1 09/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011. All rights reserved.